## TIDA-00425

# 12 Gbps SAS-3 Link Extender

Silicon Valley Analog June 2015 **Datapath Solutions**

#### ABSTRACT

Storage applications utilizing the SAS-3 standard often involve physically large systems and long cables. This reference design can be used to compensate for some of the attenuation effects seen in these areas. A critical part of the SAS-3 operation at 12 Gbps is link training. During link training the SAS-3 Transmitter and Receiver communicate with each other to optimize the signal integrity on the channel. With the DS125BR401A in the channel helping to compensate for a portion of the overall channel attenuation, the channel appears "shorter" to the Receiver. This allows a larger range of channels to support SAS-3 communication at 12 Gbps.

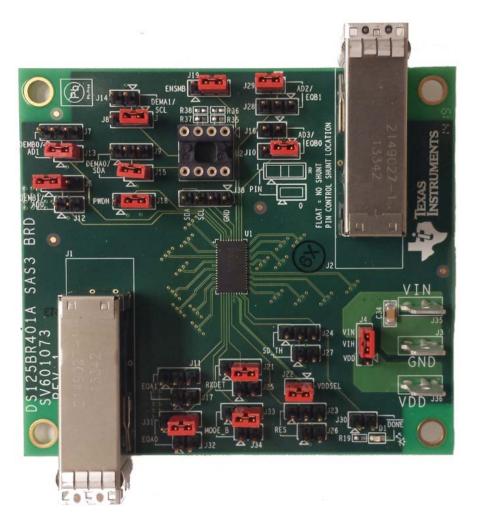

The DS125BR401A SAS-3 reference design provides a high band-width platform which highlights the signal integrity and signal conditioning capabilities of the *DS125BR401A* as it relates to the SAS-3 12 Gbps standard. MiniSAS-HD connectors are used as the input and output connections to this board. This allows standard external miniSAS-HD cables to connect to existing SAS-3 systems. The DS125BR401A SAS-3 board can be controlled via jumpers or via the SMBus with the aid of the graphic user interface based tool SigCon Architect. The 'DS125BR401A' device profile within this GUI can be used to read and write register setting

#### Contents

| 1 | Features                                                  | 2 |

|---|-----------------------------------------------------------|---|

|   | Hardware Description and Setup                            |   |

|   | 4-Level IO Control                                        |   |

|   | Jumper Connection Overview                                | 4 |

| 3 | Type chapter titleSAS3 Test Data and Recommended Settings | 7 |

|   | Layout                                                    |   |

| - |                                                           |   |

#### Figures

| 1: | 12 Gbps SAS-3 Link Extender Board | 2 |

|----|-----------------------------------|---|

|    | Header Pin Description            |   |

|    | SAS-3 Test Setup                  |   |

|    | 12 Gbps SAS-3 Output Waveform     |   |

|    | Top and Bottom PCB Assembly       |   |

#### Tables

| 1: | Jumpers to set the 4-Level Input Control Pins       |

|----|-----------------------------------------------------|

|    | Control Pin Definitions and Jumper Connections4     |

|    | SAS-3 System Test Data with DS125BR401A7            |

|    | Recommended SAS-3 EQ, VOD, and De-Emphasis Settings |

### 1. Features

- 4 Lane Repeater with Equalization up to 12 Gbps

- Linear Equalization allows for Link Training protocol for SAS3

- B-Side: Receive Equalization up to 24 dB at 6 GHz

- B-Side: Transmit de-emphasis driver >10 dB

- B-Side: Transmit voltage control: 700 1300 mV

- A-Side: Receive Equalization up to 10 dB at 6 GHz

- A-Side: Linear output driver

- A-Side: Maximum output voltage range over 1200 mV

- Programmable by Pin selection (Pin Mode) or SMBus interface

- Single supply operation:  $VIN = 3.3V \pm 10\%$  or  $VDD = 2.5V \pm 5\%$

- -40°C to +85°C Operation

- 4 kV HBM ESD rating

- High speed signal flow-thru pin-out package: 54-pin WQFN (10 mm x 5.5 mm, 0.5 mm pitch)

Figure 1: 12 Gbps SAS-3 Link Extender Board

### 2. Hardware Description and Setup

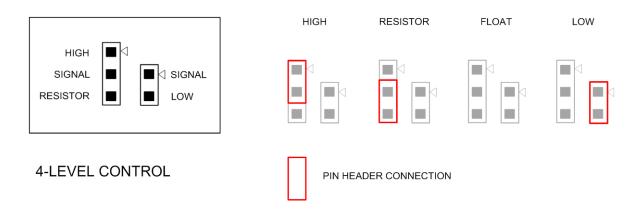

#### 2.1 4-Level IO Control

The 4-level input pins utilize a resistor divider to help set the 4 valid levels and provide a wider range of control settings when ENSMB=0. There is an internal 30K pull-up and a 60K pull-down connected to the pin. These resistors, together with the external resistor connection combine to achieve the desired voltage level. Using the 1K pull-up, 1K pull down, no connect, and 20K pull-down provide the optimal voltage levels for each of the four input states.

#### **Figure 2: Header Pin Description**

#### Table 1: Jumpers to set the 4-Level input control pins

| 4-Level IO Settings |              | Jumper Setting            |  |

|---------------------|--------------|---------------------------|--|

| 0                   | 1K to GND    | Pin 1 – Pin 2 on Header_2 |  |

| R                   | 20K to GND   | Pin 2 – Pin 3 on Header_3 |  |

| F                   | FLOAT (open) | No Jumper                 |  |

| 1                   | 1K to VIH    | Pin 1 – Pin 2 on Header_3 |  |

NOTE: Only 1 of the signal pins at a time should be tied to another pin with a jumper. Using a jumper on both signal pins simultaneously results in an indeterminate voltage level.

### 2.2 Jumper Connection Overview

### **Table 2: Control Pin Definitions and Jumper Connections**

| Component                                                                                           | Name     | Function                                                                                                                                                      |  |  |

|-----------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| J1 IA0+, IA0-, IA1+, IA1-, IA2+, IA2-, IA3+, IA3- OB0+,<br>OB0-, OB1+, OB1-, OB2+, OB2-, OB3+, OB3- |          | High-speed differential inputs/outputs                                                                                                                        |  |  |

| J2 OA0+, OA0-, OA1+, OA1-, OA2+, OA2-, OA3+, OA3-<br>IB0+, IB0-, IB1+, IB1-, IB2+, IB2-, IB3+, IB3- |          | High-speed differential inputs/outputs                                                                                                                        |  |  |

| J4                                                                                                  | VIH      | VIN (3.3V) or VDD (2.5V) to VIH power                                                                                                                         |  |  |

| J22                                                                                                 | VDD_SEL  | F = 2.5V mode (internal LDO disabled)<br>0 = 3.3V mode (internal LDO enabled)                                                                                 |  |  |

| DONE F<br>iii<br>c                                                                                  |          | Valid Register Load Status Output<br>RED = External EEPROM load failed or<br>incomplete<br>GREEN = External EEPROM load<br>passed                             |  |  |

| J24, J27                                                                                            | SD_TH    | SD_TH – Signal detect threshold level<br>for Channel B (F = Default level)                                                                                    |  |  |

| J23, J26                                                                                            | RES      | Reserved – This input must be left<br>Floating                                                                                                                |  |  |

| J21, J25                                                                                            | RX_DET   | RX_DET – Controls the receiver detect<br>function (1 = Default level for SAS)                                                                                 |  |  |

| J33, J34                                                                                            | MODE_B   | MODE_B controls output driver<br>characteristics for channel B<br>0 = SAS 1,2<br>R = SAS3 without De-emphasis (Default<br>level)<br>1 = SAS3 with De-emphasis |  |  |

| J11, J17                                                                                            | EQA1     | PIN MODE – EQ control for channel A inputs                                                                                                                    |  |  |

| J31, J32                                                                                            | EQA0     | PIN MODE – EQ control for channel A inputs                                                                                                                    |  |  |

| J19                                                                                                 | ENSMB    | ENSMB = 0 – PIN MODE<br>ENSMB = 1 – SMBus (Slave Mode)<br>ENSMB = F – SMBus (Master Mode –<br>load configuration from EEPROM)                                 |  |  |

| J18                                                                                                 | PWDN     | 1 = Low power – power down<br>0 = Normal operation (Default level)                                                                                            |  |  |

| J38                                                                                                 | SDA, SCL | Optional SMBus access pins.<br>See the datasheet for additional<br>information on SMBus                                                                       |  |  |

### Jumper Connection Overview (continued)

| Component | Name         | Function                                                                          |  |

|-----------|--------------|-----------------------------------------------------------------------------------|--|

| U2        | EEPROM       | Socket for optional EEPROM                                                        |  |

| J28, J29  | EQB1 or AD2  | PIN MODE – EQ control for channel B inputs<br>SMBus Mode – Device address bit 2   |  |

| J10, J16  | EQB0 or AD3  | PIN MODE – EQ control for channel B inputs<br>SMBus Mode – Device address bit 3   |  |

| J9, J15   | DEMA0 or SDA | PIN MODE – DEM control for channel A outputs<br>SMBus Mode – ENSMB = 1            |  |

| J8, J14   | DEMA1 or SCL | PIN MODE – DEM control for channel A outputs<br>SMBus Mode – ENSMB = 1            |  |

| J6, J12   | DEMB1 or AD0 | PIN MODE – DEM control for channel B outputs<br>SMBus Mode – Device address bit 0 |  |

| J7, J13   | DEMB0 or AD1 | PIN MODE – DEM control for channel B outputs<br>SMBus Mode – Device address bit 1 |  |

#### Jumper Connection Overview

#### 1. Connect J22 (VDD\_SEL):

- FOR 3.3V MODE: Tie pin 1 to pin 2 (VDD SEL tied to GND) on J22.

- FOR 2.5V MODE:

Do not connect a jumper (VDD\_SEL left OPEN).

- 2. Connect J4 (VIH):

- FOR 3.3V MODE:

Tie pin 2 to pin 3 (VIH tied to VIN).

• FOR 2.5V MODE:

Tie pin 1 to pin 2 (VIH tied to VDD).

- 3. Set the control jumpers for normal operation:

- J33 MODE\_B = R (SAS3 without de-emphasis)

- J21 RXDET = 1 (Input termination always 50Ω)

- J18 PWDN = 0 (Tie pin 2 to pin 3 for normal operation)

- 4. Pin Mode Set the input equalization level:

- For external pin mode control of the equalization level:

- J19 Set ENSMB = 0 (Tie pin 2 to pin 3)

- J10, J16, J28, J29 EQB Refer to Table 5 in the DS125BR401A datasheet.

- J11, J17, J31, J32 EQA Refer to Table 6 in the DS125BR401A datasheet.

- Refer to Table 1 for information on the 4 level settings.

5. Pin Mode - Set the output VOD and De-emphasis level:

- For external pin mode control for the VOD and De-emphasis level:

- J19 Set ENSMB = 0 (Tie pin 2 to pin 3)

- J11, J17, J31, J32 EQA Refer to Table 6 in the DS125BR401A datasheet.

- J6, J7, J12, J13 DEMB Refer to Table 7 in the DS125BR401A datasheet.

- J8, J9, J14, J15 DEMA Refer to Table 8 in the DS125BR401A datasheet.

- Refer to Table 1 for information on the 4 level settings.

6. SMBus Slave Mode - Set the EQ, VOD, De-emphasis level:

- For SMBus mode control of the EQ, VOD and DEM level:

- J19 Set ENSMB = 1 (Tie pin 1 to pin 2)

- J8 Set SCL = 1 (Tie pin 1 to pin 2)

- J9 Set SDA = 1 (Tie pin 1 to pin 2)

- Connect SDA, SCL and GND to J38. Refer to datasheet EQ, VOD and DEM register information.

### 3. Test Data and Recommended SAS-3 Settings

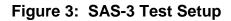

The following EQ, VOD, and DEM settings have been tested for SAS-3 12 Gbps compliance with a SAS-3 expander ASIC. The cable lengths tested ranged from 1 - 12 meters with no more than 7 meters on one side of the DS125BR401A. Refer to Table 3 for recommended settings over the specified cable length. A portion of the test data is shown below in Table 4.

### Table 3: SAS-3 System Test Data with DS125BR401A

| Cable L | engths  | DS125BR401A Settings |             |             |            |             | BER         |                   |

|---------|---------|----------------------|-------------|-------------|------------|-------------|-------------|-------------------|

| Cable1  | Cable 2 | CH-A<br>EQ           | CH-A<br>VOD | CH-A<br>DEM | CH-B<br>EQ | CH-B<br>VOD | CH-B<br>DEM | Testing<br>Result |

| 2m      | 7m      | 0x03'h               | 110'b       | 0x00'h      | 0x03'h     | 1.4Vpp      | 0x00'h      | Pass              |

| 3m      | 7m      | 0x03'h               | 110'b       | 0x00'h      | 0x03'h     | 1.4Vpp      | 0x00'h      | Pass              |

| 5m      | 7m      | 0x03'h               | 110'b       | 0x00'h      | 0x03'h     | 1.4Vpp      | 0x00'h      | Pass              |

| 7m      | 2m      | 0x03'h               | 110'b       | 0x00'h      | 0x00'h     | 1.4Vpp      | 0x00'h      | Pass              |

| 7m      | 3m      | 0x03'h               | 110'b       | 0x00'h      | 0x00'h     | 1.4Vpp      | 0x00'h      | Pass              |

| 7m      | 5m      | 0x03'h               | 110'b       | 0x00'h      | 0x00'h     | 1.4Vpp      | 0x00'h      | Pass              |

NOTE: Channel-A DEM is listed as VOD\_DB in the device datasheet

NOTE: The mini-SAS HD cable running from the system ASIC to the DS125BR401A

(Table 4, Column 2) connects to the top connector on the DS125BR401A SAS board given the orientation shown in Figure 1. The mini-SAS HD cable running from the DS125BR401A to the system ASIC (Table 4, Column 4) connects to the bottom connector.

| Table 4: | Recommended | SAS-3 EQ, | , VOD, and | <b>De-Emphasis</b> | Settings |

|----------|-------------|-----------|------------|--------------------|----------|

|----------|-------------|-----------|------------|--------------------|----------|

|                    | A Channels              | B Channels      |

|--------------------|-------------------------|-----------------|

| Equalization Level | 0x01'h – 0x03'h         | 0x00'h – 0x03'h |

| VOD Level          | 110'b (1:1 ratio Vi/Vo) | 1.4 Vpp         |

| De-Emphasis Level  | 0x00'h                  | 0x00'h          |

Although testing was completed with DS125BR401A CTLE = 0x03'h for Channel A, lower equalization levels are often used if the attenuation between SAS-3 Tx and the DS125BR401A is less than -8 dB.

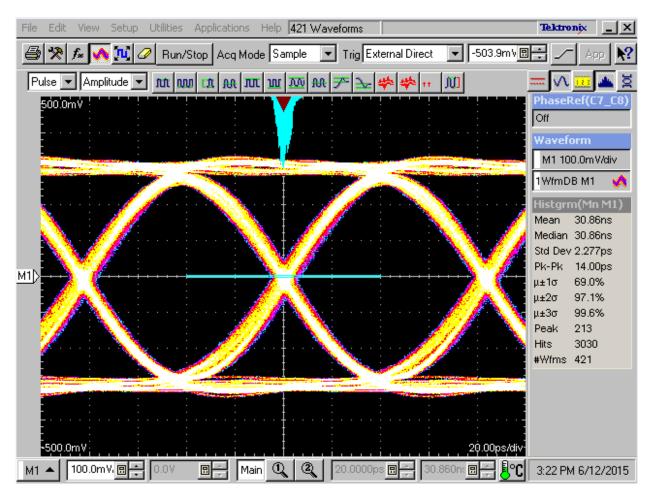

With the miniSAS-HD cables removed and the "SAS-3 Link Extender" design is tested directly, high quality waveforms are observed on the output ports.

Figure 4: 12 Gbps SAS-3 Output Waveform

### 4. Layout

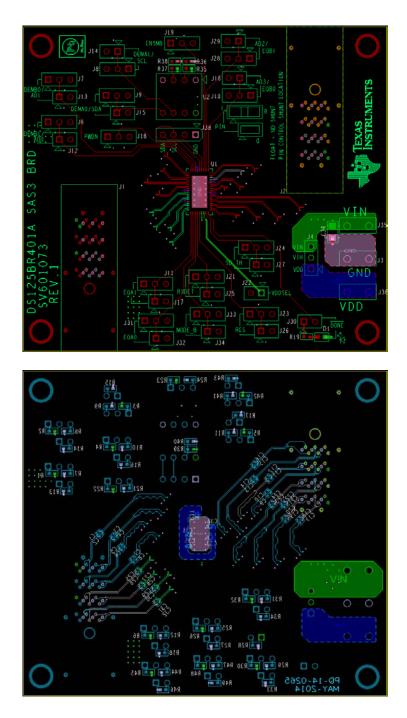

The following Figures show the DS125BR401A SAS3 board layout. The evaluation board controls signal integrity functions via jumpers. The DS125BR401A is very compact and low power. The WQFN package offers an exposed thermal pad to enhance electrical and thermal performance. This must be soldered to the copper landing on the PCB.

### Figure 5: Top and Bottom PCB Assembly

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated