## TI Designs Small Solution Size Multi Rail Reference Design for Server Line Card

#### **TI Designs**

TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help **you** accelerate your time to market.

#### **Design Resources**

TIDA-00596 LP8758 Design Folder Product Folder

| 8              |        |

|----------------|--------|

| TI E2I<br>Comn | nunity |

- <u>Ask The Analog Experts</u>

Linear Regulators Forum

- WEBENCH<sup>®</sup> Design Center

- WEBEINCH\* Design Cente

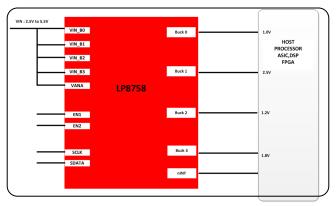

#### **High level Block Diagram**

# 🤴 Texas Instruments

#### **Design Features**

- Output voltage ranges from 0.6V to 3.36V

- Four output voltage adjustable via I2C interface

- Startup & Shutdown Programmable delays

- Maximum output current 4A per phase

- Output voltage Enable/Disable control

#### **Featured Applications**

- Server Line card ASIC Power

- SSD Power Rails

- General DC-DC replacement

- Battery operated devices

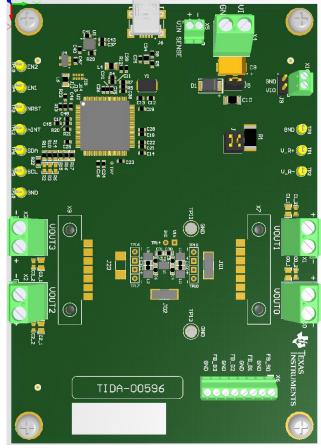

#### **Board Image**

## 1 System Description

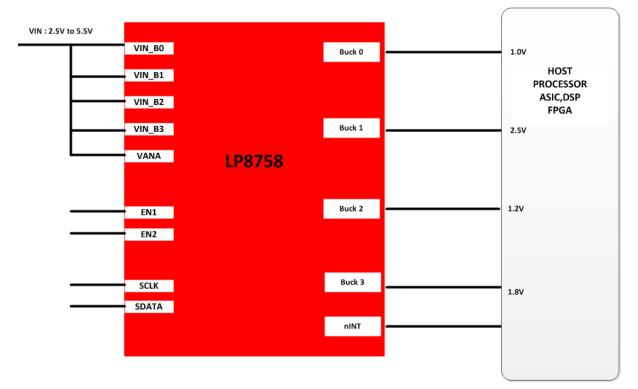

This document features a highly configurable power management buck converter (LP8758) showing the power rails for ASIC control on server line cards. The multi-buck solution shown can be easily reconfigured for other applications which need high output voltage accuracy and high peak currents.

The LP8758 also allows startup and shutdown sequencing which is critical in terms of requirements from the processors or the ASIC/FPGA/DSP/SoC devices

In this design the output voltage is programmed for default output voltages of 1.0V, 1.2V, 1.8V and 2.5V which are can be used to power different rails on the ASIC such as SERDES, DDR memory, ASIC IO components. The maximum load current per rail can be as high as 4A each.

| ASIC VOLTAGE | CURRENT LIMIT |

|--------------|---------------|

| 1.0V         | 2.5A          |

| 1.2V         | 3.5A          |

| 1.8V         | 4.5A          |

| 2.5V         | 4.5A          |

#### Table 1 ASIC Voltages & Load Current Example

## 1.1 TI Design Overview

This TI Design covers the ease of use power management solution for ASIC/FPGA/processor which needs multiple rails and has very tight requirements on the output voltage accuracy and ripple voltage. Also the power rails require DVS method to reduce the average power consumption in embedded systems (i.e. ASICs, SoCs, processors/DSPs, FPGAs) this is accomplished by reducing the switching losses of the system by selectively reducing the core voltage based on the need of the system.

#### Table 2 Design Parameters

| DESIGN PARAMETERS        | VALUE               |

|--------------------------|---------------------|

| Input voltage            | 3.3V                |

| Multiple Output voltages | 1.0V,1.2V,1.8V,2.5V |

## **Block Diagram**

Figure 1 Comprehensive block diagram

## 2 Component Selection

This TI design has the following components

Power Management Buck Converter: <u>LP8758</u> Four Output Step down DC-DC Regulator

- Parameters taken into account when selecting the buck regulator:

- Low Iq in Shutdown mode

- High accuracy in steady state

- Startup & Shutdown sequencing capability.

- Vout Range with DVS Control

- Small Solution Size

Alternative parts with similar functionality

• <u>LP8754</u> similar functionality with additional phases

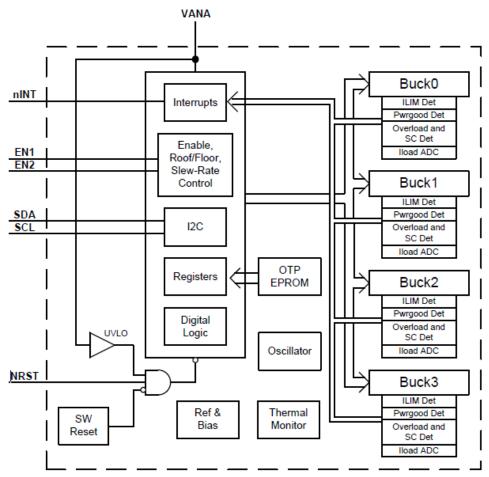

## 2.1 LP8758

The LP8758 is a high-efficiency, high-performance power supply device with four step-down DC-DC converter cores. The cores are configured for a four single-phase configuration. The device delivers 0.5-V to 3.36-V regulated voltage rails from 2.5-V to 5.5-V battery.

There are two modes of operation for the converter, depending on the output current required: Pulse-Width Modulation (PWM) and Pulse-Frequency Modulation (PFM). The converter operates in PWM mode at high load currents of approximately 400 mA or higher. Lighter output current loads will cause the converter to automatically switch into PFM mode for reduced current consumption and a longer battery life when Forced PWM mode is disabled.

Additional features include soft-start, under voltage lockout, overload protection, thermal warning, and thermal shutdown.

Figure 2: LP8758 Functional Block Diagram

## 3 System design and component selection

The following system considerations apply only for the conditions of this design. For different conditions it is essential to verify the ratings and operating conditions on the datasheets of the parts mentioned in this design. If the parameters does not fit the application consider one of the alternative parts on section 3 or perform and easy parametric search at <a href="http://www.ti.com">http://www.ti.com</a>

#### 3.1 Input voltage consideration

The device is designed to operate from an input voltage supply range between 2.5 V and 5.5 V. This input supply should be well-regulated and able to withstand maximum input current and maintain stable voltage without voltage drop even at load transition condition. The resistance of the input supply rail should be low enough that the input current transient does not cause too high drop in the LP8758 supply voltage that can cause false UVLO fault triggering. If the input supply is located more than a few inches from the LP8758 additional bulk capacitance may be required in addition to the ceramic bypass capacitors.

## 3.2 Inductor & Input/output Capacitor selection consideration

#### 3.2.1 Inductor Selection

DC bias current characteristics of inductors must be considered. Different manufacturers follow different saturation current rating specifications, so attention must be given to details. DC bias curves should be requested from them as part of the inductor selection process. Minimum effective value of inductance to ensure good performance is 0.22  $\mu$  H at 4 A bias current over the inductor's operating temperature range. The inductor's DC resistance should be less than 0.05  $\Omega$  for good efficiency at high current condition. The inductor AC loss (resistance) also affects conversion efficiency. Higher Q factor at switching frequency usually gives better efficiency at light load to middle loads

| MANUFACTURER | PART NUMBER       | VALUE   | DIMENSIONS LxWxH<br>(mm) | DCR (mΩ)           |

|--------------|-------------------|---------|--------------------------|--------------------|

| токо         | DFE252010F-R33M   | 0.33 µH | 2.5 x 2.0 x 1.0          | 16 (typ), 21 (max) |

| TDK          | VLS252010HBX-R33M | 0.33 µH | 2.5 x 2.0 x 1.0          | 25 (typ), 31 (max) |

| TDK          | VLS252010HBX-R47M | 0.47 µH | 2.5 x 2.0 x 1.0          | 29 (typ), 35 (max) |

| TDK          | TFM2016GHM-0R47M  | 0.47 µH | 2.0 x 1.6 x 1.0          | 46 (max)           |

| токо         | DFE322512C R47    | 0.47 µH | 3.2 x 2.5 x 1.2          | 21 (typ), 31 (max) |

#### **Table 3 Recommended Inductors**

## 3.2.2 Input Capacitor Selection

A ceramic input capacitor of 10  $\mu$ F, 6.3 V is sufficient for most applications. Place the power input capacitor as close as possible to the VIN\_Bx pin and PGND\_Bx pin of the device. A larger value or higher voltage rating may be used to improve input voltage filtering. Use X7R or X5R types, do not use Y5V or F. DC bias characteristics of ceramic capacitors must be considered when selecting case sizes like 0402. Minimum effective input capacitance to ensure good performance is 1.9  $\mu$ F per buck input at maximum input voltage DC bias including tolerances and over ambient temp range, assuming that there are at least 22  $\mu$ F of additional capacitance common for all the power input pins on the system power rail.

#### Table 4 Recommended Power Input Capacitors (X5R Dielectric)

| MANUFACTURER | PART NUMBER       | VALUE       | CASE SIZE | DIMENSIONS LxWxH<br>(mm) | VOLTAGE<br>RATING |

|--------------|-------------------|-------------|-----------|--------------------------|-------------------|

| Murata       | GRM188R60J106ME47 | 10 µF (20%) | 0603      | 1.6 x 0.8 x 0.8          | 6.3 V             |

The input filter capacitor supplies current to the high-side FET switch in the first half of each cycle and reduces voltage ripple imposed on the input power source. A ceramic capacitor's low equivalent series resistance (ESR) provides the best noise filtering of the input voltage spikes due to this rapidly changing current. Select an input filter capacitor with sufficient ripple current rating.

The VANA input is used to supply analog and digital circuits in the device. See recommended components from table below for VANA input supply filtering

|   | Table 5 Recommended VANA Supply Filtering Components |  |  |  |  |  |  |

|---|------------------------------------------------------|--|--|--|--|--|--|

|   |                                                      |  |  |  |  |  |  |

| _ |                                                      |  |  |  |  |  |  |

| MANUFACTURER | PART NUMBER       | VALUE        | CASE SIZE | DIMENSIONS LxWxH<br>(mm) | VOLTAGE RATING |

|--------------|-------------------|--------------|-----------|--------------------------|----------------|

| Samsung      | CL03A104KP3NNNC   | 100 nF (10%) | 0201      | 0.6 x 0.3 X 0.3          | 10 V           |

| Murata       | GRM033R61A104KE84 | 100 nF (10%) | 0201      | 0.6 x 0.3 x 0.3          | 6.3 V          |

## 3.2.3 Output capacitors

Use ceramic capacitors, X7R or X5R types; do not use Y5V or F. DC bias voltage characteristics of ceramic capacitors must be considered. DC bias characteristics vary from manufacturer to manufacturer, and DC bias curves should be requested from them as part of the capacitor selection process. The output filter capacitor smooth's out current flow from the inductor to the load, helps maintain a steady output voltage during transient load changes and reduces output voltage ripple. These capacitors must be selected with sufficient capacitance and sufficiently low ESR and ESL to perform these functions. Minimum effective output capacitance to ensure good performance is 10  $\mu$  F per phase at the output voltage DC bias including tolerances and over ambient temp range. The output voltage ripple is caused by the charging and discharging of the output capacitor and also due to its R<sub>ESR</sub>. The R<sub>ESR</sub> is frequency dependent (as well as temperature dependent); make sure the value used for selection process is at the switching frequency of the part.

A higher output capacitance improves the load step behavior and reduces the output voltage ripple as well as decreases the PFM switching frequency. For most 4-phase applications  $4 \times 22 \ \mu$  F 0603 capacitors for COUT are suitable. Although a converter's loop compensation can be programmed to adapt to virtually several hundreds of microfarads Cout, it is preferable for Cout to be < 200  $\mu$ F (4-phase configuration). Choosing higher than that is not necessarily of any benefit. Note that the output capacitor may be the limiting factor in the output voltage ramp, especially for very large (> 100  $\mu$ F) output capacitors. For large output capacitors, the output voltage might be slower than the programmed ramp rate at voltage transitions, because of the higher energy stored on the output capacitance. Also at start-up, the time required to charge the output capacitor to target value might be

longer. At shutdown, if the output capacitor is discharged by the internal discharge resistor, more time is required to settle  $V_{OUT}$  down as a consequence of the increased time constant.

| MANUFACTURER | PART NUMBER       | VALUE       | CASE SIZE | DIMENSIONS LxWxH<br>(mm) | VOLTAGE<br>RATING |

|--------------|-------------------|-------------|-----------|--------------------------|-------------------|

| Samsung      | CL10A226MP8NUNE   | 22 µF (20%) | 0603      | 1.6 x 0.8 x 0.8          | 10 V              |

| Murata       | GRM188R60J226MEA0 | 22 µF (20%) | 0603      | 1.6 x 0.8 x 0.8          | 6.3 V             |

#### Table 6: Recommended Output Capacitors (X5R Dielectric)

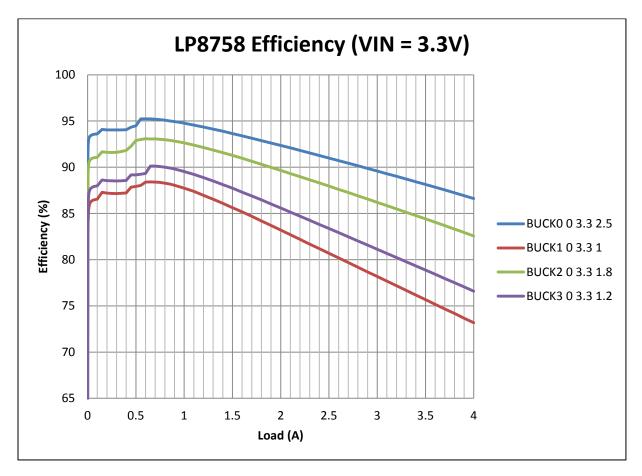

## 3.3 Output voltage configuration

The LP8758 is configured as 4 single phase buck regulator and the default output voltages are 1.0V, 2.5V, 1.2V and 1.8V.There is a startup delay of 0 msec set from the EN pin and this is for the following buck regulator 0 & 1 and 5 msec delay is set for buck regulator 2 & 3.The shutdown delay is set as 5 msec for buck regulator 0 & 1 and 0 msec for buck regulator 2 & 3.

The startup slew rate for the output voltage is set as 10mV/usec and the current limits can be set from 1.5A to 5.0A according to the requirements from the SoC/Processor.

## 4 Power up Sequence

The power-up sequence for the LP8758 is as follows:

- VANA (and VIN\_Bx) reach min recommended levels (V(VANA) > VANAUVLO).

- NRST is set to high level. This initiates Power-On-Reset (POR), OTP reading and enables the system I/O interface. The I2C host should allow at least 700 μs before writing or reading data to the LP8758.

- Device enters STANDBY-mode.

- > The host can change the default register setting by I2C if needed.

- The regulator can be enabled/disabled by ENx pin(s) and by I2C interface

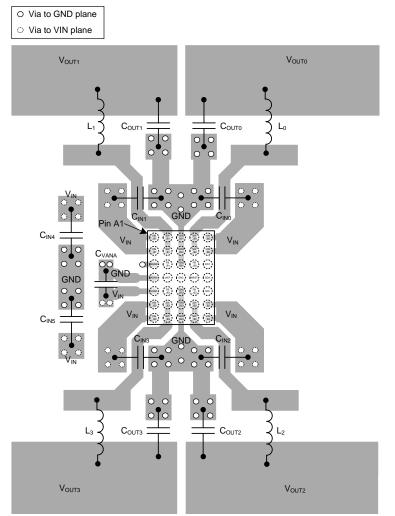

## 5 Layout guidelines

The high frequency and large switching currents of the LP8758 make the choice of layout important. Good power supply results will only occur when care is given to proper design and layout. Layout will affect noise pickup and generation and can cause a good design to perform with less-than-expected results. With a range of output currents from milliamps to 10A and over, good power supply layout is much more difficult than most general PCB design. The following steps should be used as a reference to ensure the device is stable and maintains proper voltage and current regulation across its intended operating voltage and current range.

- Place CIN as close as possible to the VIN\_Bx pin and the PGND\_Bxx pin. Route the VIN trace wide and thick to avoid IR drops. The trace between the input capacitor's positive node and LP8758's VIN\_Bx pin(s) as well as the trace between the input capacitor's negative node and power PGND\_Bxx pin(s) must be kept as short as possible. The input capacitance provides a low-impedance voltage source for the switching converter. The inductance of the connection is the most important parameter of a local decoupling capacitor parasitic inductance on these traces must be kept as tiny as possible for proper device operation.

- The output filter, consisting of Lx and COUTx, converts the switching signal at SW\_Bx to the noiseless output voltage. It should be placed as close as possible to the device keeping the switch node small, for best EMI behavior. Route the traces between the LP8758's output capacitors and the load's input capacitors direct and wide to avoid losses due to the IR drop.

- Input for analog blocks (VANA and AGND) should be isolated from noisy signals. Connect VANA directly to a quiet system voltage node and AGND to a quiet ground point where no IR drop occurs. Place the decoupling capacitor as close to the VANA pin as possible. VANA must be connected to the same power node as VIN\_Bx pins.

- If the processor load supports remote voltage sensing, connect the LP8758's feedback pins FB\_Bx to the respective sense pins on the processor. The sense lines are susceptible to noise. They must be kept away from noisy signals such as PGND\_Bxx, VIN\_Bx, and SW\_Bx, as well as high bandwidth signals such as the I2C. Avoid both capacitive as well as inductive coupling by keeping the sense lines short, direct and close to each other. Run the lines in a quiet layer. Isolate them from noisy signals by a voltage or ground plane if possible. Running the signal as a differential pair is recommended.

- PGND\_Bxx, VIN\_Bx and SW\_Bx should be routed on thick layers. They must not surround inner signal layers which are not able to withstand interference from noisy PGND\_Bxx, VIN\_Bx and SW\_Bx.

- Due to the small package of this converter and the overall small solution size, the thermal performance of the PCB layout is important. Many system-dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power dissipation limits of a given component. Proper PCB layout, focusing on thermal performance, results in lower die temperatures. Wide power traces come with the ability to sink dissipated heat. This can be improved further on multi-layer PCB designs with vias to different planes. This results in reduced junction-to-ambient (R0JA) and junction-to-board (R0JB) thermal resistances and thereby reduces the device junction temperature, TJ. Performing a careful system level 2D or full 3D dynamic thermal analysis at the beginning product design process is strongly recommended, using a thermal modeling analysis software

## 6 Test Results

## 6.1 Equipment used

Table 5 is a list of the test equipment used in the preceding sections.

#### Table 7 Test equipment

| TEST EQUIPMENT | PART NUMBER      |

|----------------|------------------|

| Oscilloscope   | Agilent DPO4014B |

| Voltage supply | Agilent E3631A   |

| Multimeters    | Agilent E34401A  |

## 6.2 Default output voltage at power up

Table 6 shows the power up default settings of the system.

#### Table 8 Default output voltage settings

| BUCK OUTPUT | V <sub>OUT</sub> | STARTUP DELAY | SHUTDOWN DELAY |

|-------------|------------------|---------------|----------------|

| Buck 0      | 1.0V             | 0 msec        | 5 msec         |

| Buck 1      | 2.5V             | 0 msec        | 5 msec         |

| Buck 2      | 1.2V             | 5 msec        | 0 msec         |

| Buck 3      | 1.8V             | 5 msec        | 0 msec         |

## 6.3 Efficiency

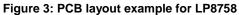

The regulated output voltage remains stable at various input voltage levels. **Figure 4** shows the system output voltage efficiency at VIN of 3.3V

Figure 4: Output Voltage Efficiency in Auto Mode

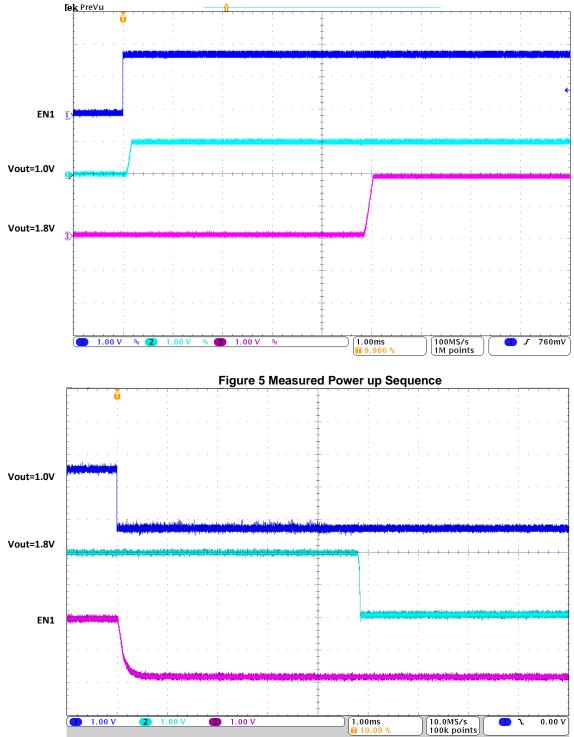

## 6.4 Power up and Shutdown Sequence

**Figure 5 & 6** show examples of the power up and power down sequence needed for the ASIC voltages of 1.0V and 1.8V. This can be controlled using the EN1 Pin on the LP8758. The delays are programmable from Omsec to 15msec in steps size of 1msec.

With the following design no external sequencer is needed and it reduces the overall BOM cost for the design.

Figure 6 Measured Power down Sequence

## 6.5 Voltage Output accuracy

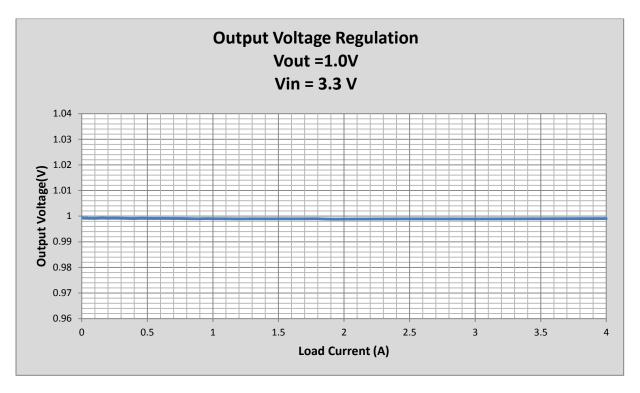

**Figure 7** is a graphical representation of the computational results of the output voltage vs the load current to show that output voltage variation is within the 2% of the nominal expected voltage. The data shown below is in Forced PWM mode.

Figure 7 Output voltage vs Load Current

## 7 Design Files

## 7.1 Schematics

To download the Schematics, see the design files at <a href="http://www.ti.com/tool/TIDA-00596">http://www.ti.com/tool/TIDA-00596</a>

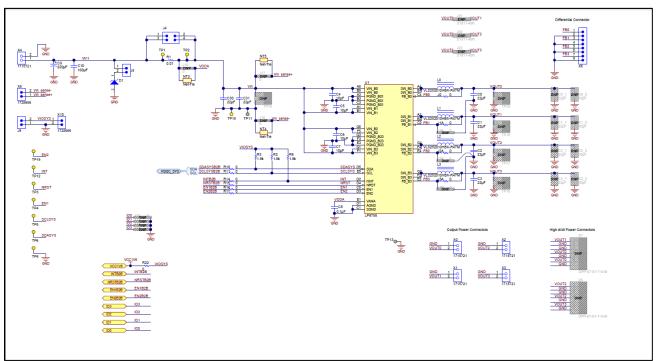

Figure 8: TIDA-00596 Schematic Sheet 1

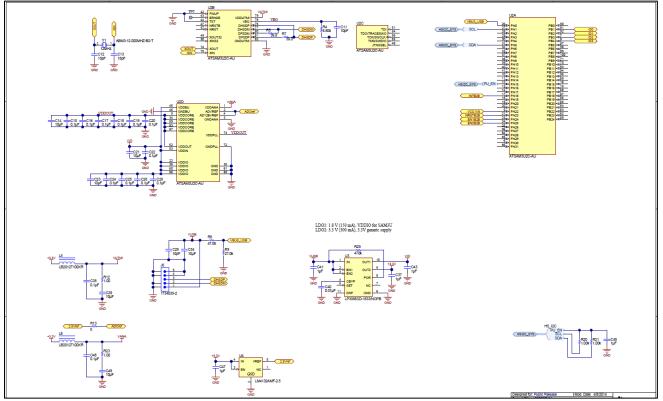

#### Figure 9: TIDA-00596 Schematic USB interface

## 7.2 Design Files

To download the design files, see the design files at <u>http://www.ti.com/tool/TIDA-00596</u>

- Bill of Materials

- Gerber Files

- Layout Prints

## 8 Terminology

TI Glossary: <u>SLYZ022</u> This glossary lists and explains terms, acronyms, and definition

## 9 About the Author

**Chintan Parekh** Is an Applications & Systems Engineering Manager at Texas Instruments; he brings to this role experience in system-level analog, mixed-signal, and power management design. Chintan earned his Bachelor of Engineering from University of Mumbai & Master of Science in Electrical Engineering from University of Southern California (USC).

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated