# CMOS MMIC Ready for Road – A Technology Overview

Venkatesh Srinivasan

While solving the challenges of integrating high frequency front ends on CMOS process, TI has leveraged the traditional advantages of CMOS solutions in terms of higher transistor density and low power to create a compelling family of mmWave devices. This application report enumerates some of these challenges, respective solutions and advantages of CMOS as leveraged in TI mmWave Sensing devices.

#### Contents

| 1 |

|---|

| 1 |

| 3 |

| 4 |

| 5 |

| 5 |

|   |

#### List of Figures

| 1 | Scaling Trends of $f_{\tau}$ in CMOS | 2 |

|---|--------------------------------------|---|

|   |                                      |   |

2 Block Diagram of TI's Single-Chip Transceiver for Automotive Radar ...... 4

#### Trademarks

*Bluetooth* is a registered trademark of Bluetooth SIG, Inc. All other trademarks are the property of their respective owners.

#### 1 Introduction

Over the years, complementary metal-oxide semiconductor (CMOS) technology has been popular for wireless transceiver chips with integrated radios, as evidenced by multiple chipsets in volume production. These integrated circuits (ICs) enable a variety of applications such as *Bluetooth*<sup>®</sup>, wireless local area networks (LAN), GPS and, 4G Long Term Evolution (LTE) operating in a range of frequencies up to 6 GHz. However, circuits in the millimeter-wave (mmWave) regime (30-300GHz) have been the domain of heterojunction technologies such as silicon germanium (SiGe) bipolar CMOS (BiCMOS), as operation in themmWave regime requires faster transistors and high-quality passives.

Given technology scaling and Moore's Law, transistors using ultra-deep submicron CMOS technology now boast high-enough unity current gain frequency ( $f_T$ ) and maximum oscillation frequency ( $f_{MAX}$ ) numbers (metrics of transistor speed). Coupled with innovations at the circuit/architecture level, CMOS is now well-positioned to be the key technology that enables volume production in the mmWave frequency range.

## 2 MMICs Using CMOS Technology

Several factors are critical to designing and ramping a high-performance fully integrated millimeter-wave integrated circuit (MMIC) to production. From a radio frequency (RF)/mmWave perspective, the transistor speed as characterized by  $f_T/f_{MAX}$  – and the passives and metallization offered by the process – are vital to enabling benchmark performance numbers in key RF modules such as low-noise amplifiers (LNAs), power amplifiers (PAs) and voltage-controlled oscillators (VCOs).

#### MMICs Using CMOS Technology

The benefits of integration are well-known from both a cost and features perspective. Therefore, in addition to RF capabilities, the process node should also be conducive to the design and integration of high-performance analog/mixed-signal modules such as data converters and digital IPs that enable differentiated signal-processing capabilities. capabilities. In markets such as automotive, where safety is paramount, it is imperative that designers understand the reliability aspects of the process. In this document, current state-of-the-art CMOS technology is reviewed against these metrics to demonstrate readiness to ramp high-performance MMICs.

# 2.1 Scaling With CMOS

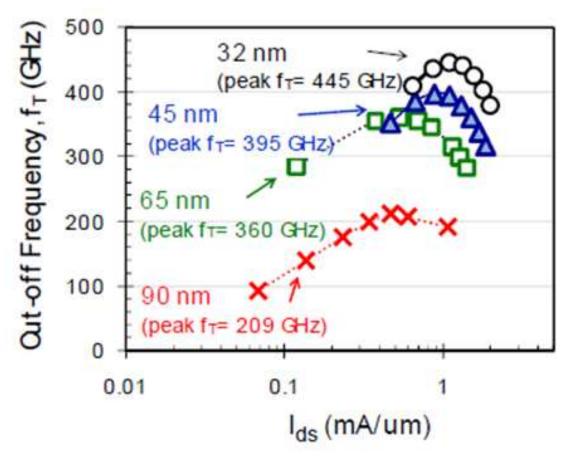

CMOS scaling from the perspective of digital circuits has resulted in a steady decrease in transistor channel length ( $L_g$ ). This reduction in channel length has resulted in an increase in raw transistor speeds, as measured by the  $f_T$  and  $f_{MAX}$ . The parameters  $f_T$  and  $f_{MAX}$  are inversely proportional to  $L_g$  and have been steadily increasing with technology scaling, as shown in Figure 1 [1].  $f_T$  is a good metric for analog/mixed-signal circuits.

Figure 1. Scaling Trends of  $f_T$  in CMOS

However, the parameter  $f_{MAX}$  is a more relevant metric with which to understand transistor capabilities in mmWave frequencies. Although  $f_T$  is more a function of process technology,  $f_{MAX}$  is highly dependent on layout techniques that minimize gate and source/drain resistance and parasitic losses. Consequently, it's possible to achieve an  $f_{MAX}$  higher than  $f_T$  [2].

Another key consideration, especially in the design of LNAs, is the minimum achievable noise figure (NF<sub>min</sub>). With NF<sub>min</sub> inversely proportional to f<sub>T</sub>, technology scaling results in a lowering of NF<sub>min</sub> as well. Like f<sub>MAX</sub>, NF<sub>min</sub> also depends on good layout techniques. Using layout optimization techniques and best practices developed at Texas Instruments (TI), devices with f<sub>MAX</sub> = ~300 GHz and NF<sub>min</sub> <4dB at 77 GHz in TI's 45 nm CMOS technology node are able to be demonstrated. TI's mmWave sensor portfolio leverages these devices.

www.ti.com

## 2.2 Synthesizing Data Converters and Passive Elements in CMOS

Aside from device speeds, the next key consideration in the design of high-performance mmWave circuits is the quality of passives: inductors, transformers, transmission lines and capacitors. These are highly dependent on the metallization offered by the process. Technology scaling from a digital perspective drives thinner interconnects and metal stacks closer to the substrate – two trends that result in lossy passives. However, with minimal cost impact, most mixed-mode CMOS processes offer access to one to two layers of thicker higher-level metals. Using these metals, along with techniques to reduce substrate losses, inductors with quality factors in excess of 15 are achievable. have been demonstrated. Also achievable using vertical coupling, are low-loss transformers with coupling factors >0.7 in mmWave frequencies.

Using the available metal layers, high-density and high-Q capacitors are commonly implemented as metalinsulator-metal (MIM) capacitors. The inherent MOS capacitor serves as a tunable capacitor for VCOs if you address the issue of lower Q at mmWave frequencies using proper frequency planning with the choice of VCOs and multipliers.

CMOS technology scaling results in reduced supply voltage and self-gain (gm/gds) in transistors, trends that are a challenge for analog/mixed-signal circuits. But given the push for integration, innovations have resulted in architectures that take advantage of the benefits of CMOS. Examples range from the popular switched-capacitor technique of the past to more recent examples of digitally assisted analog [3] where taking advantage of easy access to digital signal processing (DSP) corrects unavoidable analog impairments in CMOS, thereby creating high-performance circuits.

## 3 RF performance

In the data-converter context, the research focus in the past decade has been on architectures attractive to CMOS implementation such as delta-sigma modulators and successive approximation register (SAR) analog-to-digital converters (ADCs). These converters now boast bandwidths in excess of 100 MHz with superior power efficiency and are consequently the data-converter architecture of choice for integrated transceivers [4].

## 3.1 Challenges

It is not possible to avoid mentioning flicker noise (1/f noise) in the context of CMOS technology. Flicker noise is a low-frequency noise mechanism that occurs because of imperfections in the silicon-silicon dioxide (Si-SiO2) interface. Flicker noise and its dependence on total device area have been well documented, and there are a number of techniques to mitigate/reduce flicker noise, such as chopping and correlated double sampling. Technology scaling results in an improvement in the control of the Si-SiO2 interface, thereby leading to a reduction in flicker noise (normalized to unit area) with process scaling [1] [5].

Operating under a reduced supply voltage and remaining within supply ratings are also necessary to mitigate long-term reliability issues brought about by degradation mechanisms such as negative-bias temperature instability (NBTI), positive-bias temperature instability (PBTI) and channel hot-carrier injection (CHCI). There are many studies behind the fundamental physics of these degradation mechanisms, and models and simulation techniques exist to predict their impact [6]. It might appear that circuits such as PAs, which benefit from an increased supply voltage, would be at a disadvantage in CMOS technology. However, using impedance transformation and on-chip power combining have resulted in CMOS PA designs that reliably deliver >12dBm of output power at mmWave frequencies [7].

CMOS Enables Integration of More Digital Content

## 4 CMOS Enables Integration of More Digital Content

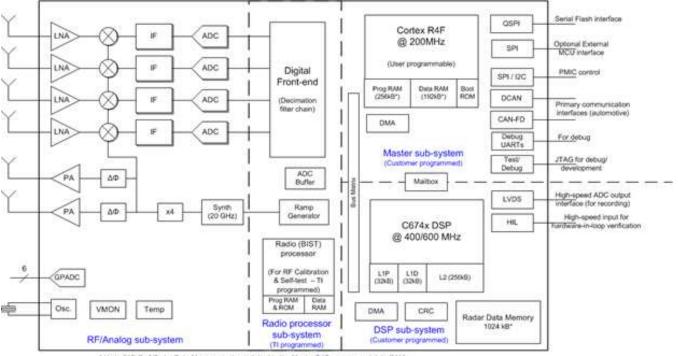

The numerous benefits of scaling in the digital context are self-evident and are the key drivers for technology scaling. These have enabled integrated transceivers with increased digital content, including microcontrollers and even dedicated DSPs. TI's single-chip solution for automotive radar in the 76 GHz – 81 GHz band, the AWR1642, is one such example.

Figure 2 shows a block-level representation of the AWR1642 chipset. The level of integration that CMOS enables is clearly evident. From an analog signal-chain perspective, the chip includes four receiver chains (LNA to ADC), two transmitter chains with an integrated PA, a synthesizer capable of delivering fast ramps for frequency-modulated continuous wave (FMCW) radar operation, integrated references and temperature sensors. The digital content on the chip includes the necessary digital processing for the ADCs, TI's custom DSP for radar processing, an Arm® Cortex®-R4F microcontroller and a host of interface protocols such as Camera Serial Interface (CSI) and low-voltage differential signaling (LVDS).

In addition to the rich feature set that such a high level of integration provides, having mmWave, analog and digital circuits on the same die allows for built-in self-test (BIST) and monitoring capabilities. For example, the AWR1642 has circuits that communicate seamlessly between mmWave/analog/digital boundaries, and can detect and warn in the event that a receiver chain experiences a saturation event or a transmitter encounters a ball-break at its output. These are key differentiating features in the safety-critical automotive market.

\* Up to 512x8 of Radar Data Memory can be switched to the Master R4F program and data RAMs

www.ti.com

#### 5 Summary

In summary, digital scaling has resulted in high-speed transistors that make mmWave circuits feasible in CMOS technology. Sustained innovations have resulted in analog circuits and architectures uniquely suited for CMOS technology that deliver high performance by amplifying the advantages of scaling. The integration benefit of CMOS technology enables the co-existence of multiple classes of circuits, and itself offers a platform for further innovation.

# 6 References

- 1. C.-H. Jan, M. Agostinelli, H. Deshpande, M.A. El-Tanani, W. Hafez, U. Jalen, L. Janbay et al., *RF CMOS Technology Scaling in High-k/Metal Gate Era for RF SoC (System on Chip) Applications*, IEEE International Electron Devices Meeting (December 2010): 27.2.1-27.2.4.

- 2. Ali M. Niknejad, S. Emami, B. Heydari, M. Bohsali, and E. Adabi, *Nanoscale CMOS for mm-Wave Applications*, IEEE Compound Semiconductor Integrated Circuit Symposium (October 2007): 135-138.

- 3. B. Murmann, "Digitally Assisted Analog Circuits," IEEE Micro 26, Issue 2 (March-April 2006): 38-47.

- 4. B. Murmann, ADC Performance Survey 1997-2017.

- Han-Su Kim, Chulho Chung, Joohyun Jeong, Seung-Jae Jung, Jinsung Lim, JinHyoun Joe, Jaehoon Park et al., "Effect of Technology Scaling on RF Performance of the Transistors Fabricated by Standard CMOS Technology," Radio Frequency Integrated Circuits Symposium (June 2008): 555-558.

- Wenping Wang, Vijay Reddy, Anand T. Krishnan, Rakesh Vattikonda, Srikanth Krishnan and Yu Cao, *Compact Modeling and Simulation of Circuit Reliability for 65-nm CMOS Technology*, IEEE Transactions on Device and Materials Reliability 7, Issue 4 (December 2007): 509-517.

- 7. Jiashu Chen and Ali M. Niknejad, *A Compact 1V 18.6dBm 60GHz Power Amplifier in 65nm CMOS*, 2011 IEEE International Solid-State Circuits Conference Digest of Technical Papers (February 2011).

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated