# Technical Article Maintain a Constant Phase Margin in a Synchronous Buck Converter

#### Kit Nguyen

When designing a step-down buck converter, converter stability should be a top priority. The converter is stable when the phase margin of the loop gain is greater than 0 degrees, with an acceptable minimum phase margin of 45 degrees. Maintaining a constant phase margin when the power-stage components vary as much as 50% from their original values can be a challenge for circuit designers. For example, the values of the inductor and capacitors change with their bias operating conditions and temperature range.

Using the new advanced current mode (ACM) control topology in TI's TPS543C20 synchronous step-down SWIFT<sup>™</sup> converter, I compared the shape of the phase in three separate cases. In each case, I change the value of the output capacitor, inductor and both the output capacitor and inductor without making any other modifications to the circuit. I used the single-phase TPS543C20EVM-799 evaluation module (EVM) to perform the comparison under these test conditions:

- Input voltage = 5V, output voltage = 0.9V, switching frequency = 500kHz.

- Original inductor value = 470nH (0.165mΩ direct current resistance [DCR]).

- Original output capacitor = 2 x 330µF (3mΩ equivalent series resistance [ESR]) + 3 x 100µF (1206 size ceramic capacitor).

- Output load configured as a 10A resistive power resistor.

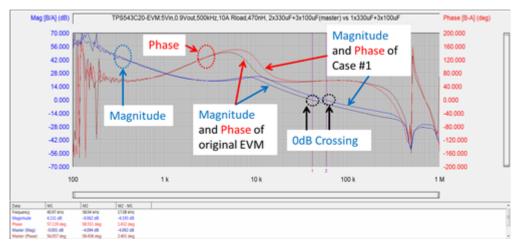

## Case No. 1, Illustrated in Figure 1

I compared the phase from the original default EVM to a new output capacitance value of  $1 \times 330 \mu F$  ( $3m\Omega ESR$ ) +  $3 \times 100 \mu F$  while keeping other conditions the same. As you can see, the shape of the phase very much stays the same as the original values. The phase is also basically staying constant over a decade of frequency after the double-pole frequency of inductor and output capacitor.

Figure 1. Bode Plot Comparison between Original Configurations versus Case No. 1

1

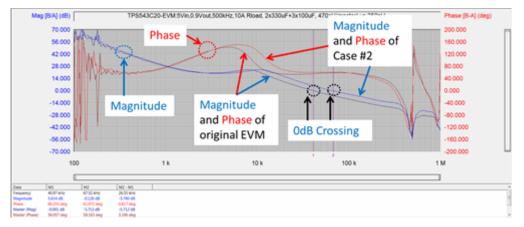

#### Case No. 2, Illustrated in Figure 2

I compared the phase of the original default EVM to a new inductor value -250nH (0.165m $\Omega$  DCR) - while keeping the other conditions the same. Again, the shape of the phase is very much the same as the default configuration. The phase is basically staying constant over a decade of frequency.

Figure 2. Bode Plot Comparison between Original Configurations versus Case No. 2

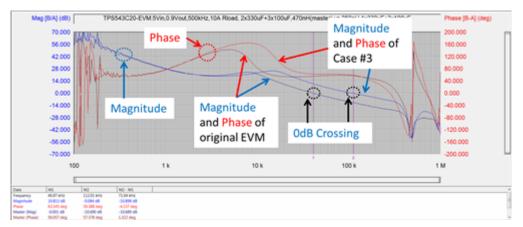

## Case No. 3, Illustrated in Figure 3

I compared the phase of the original default EVM to a combination of case Nos. 1 and 2 – 250nH (0.165m $\Omega$  DCR) and 1 x 330 $\mu$ F (3m $\Omega$  ESR) + 3 x 100 $\mu$ F – while keeping the other conditions the same. Again, the shape of the phase stays constant at 0dB.

The shape of the phase in the ACM topology stays constant over a decade frequency range when the power component changes its value, such as a 53% inductor reduction from 470nH to 250nH. However, you still need to pay attention to the changing value of power-stage components so that the phase margin of your converter meets the minimum requirement.

Additional resources:

2

- Read the white paper, "Internally Compensated Advanced Current Mode."

- Read a blog post about the effects of gate-driver strength in synchronous buck converters.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated