# KeyStone Architecture II Gigabit Ethernet (GbE) Switch Subsystem for K2E and K2L Devices

# **User's Guide**

Literature Number: SPRUHZ3A August 2014–Revised April 2015

# **Contents**

| Pref | ace   |                                                                                                                  | 2 |

|------|-------|------------------------------------------------------------------------------------------------------------------|---|

| 1    | Intro | uction 23                                                                                                        | 3 |

|      | 1.1   | Purpose of the Peripheral 24                                                                                     | 4 |

|      | 1.2   | Features 24                                                                                                      | 4 |

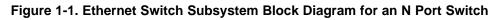

|      | 1.3   | Gigabit Ethernet Switch Subsystem Functional Block Diagram                                                       | 5 |

|      | 1.4   | Industry Standard(s) Compliance Statement                                                                        | 6 |

| 2    | Arch  | ecture                                                                                                           | 7 |

|      | 2.1   | Clock Control                                                                                                    | 8 |

|      |       | 2.1.1 Gigabit Switch Subsystem Clock 28                                                                          | 8 |

|      |       | 2.1.2 SGMII SerDes Reference Clock                                                                               |   |

|      |       | 2.1.3 MDIO Clock                                                                                                 | 8 |

|      |       | 2.1.4 IEEE 1588 Time Synchronization Clock 28                                                                    | 8 |

|      |       | 2.1.5 GMII Clock 28                                                                                              | 8 |

|      | 2.2   | Memory Map                                                                                                       | 9 |

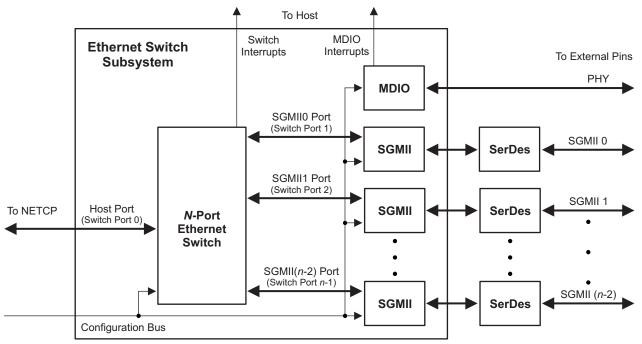

|      | 2.3   | Gigabit Ethernet Switch Architecture 29                                                                          | 9 |

|      |       | 2.3.1 Streaming Packet Interface 30                                                                              | 0 |

|      |       | 2.3.1.1 Transmit Streaming Packet Interface (Host Port 0 Switch Egress) 30                                       | 0 |

|      |       | 2.3.1.2 Receive Streaming Packet Interface (Host Port 0 Switch Ingress) 32                                       | 2 |

|      |       | 2.3.2 Media Access Controller Submodule Architecture                                                             |   |

|      |       | 2.3.2.1 Data Receive Operations 36                                                                               | 6 |

|      |       | 2.3.2.2 Data Transmission 42                                                                                     | 2 |

|      |       | 2.3.3 MAC Receive FIFO Architecture 47                                                                           |   |

|      |       | 2.3.4 Priority Mapping and Transmit VLAN Priority 47                                                             |   |

|      |       | 2.3.5 Statistics Submodule Architecture 49                                                                       |   |

|      |       | 2.3.5.1 Accessing Statistics Registers 49                                                                        |   |

|      |       | 2.3.5.2 Statistics Interrupts 49                                                                                 |   |

|      |       | 2.3.5.3 Receive Statistics Descriptions                                                                          |   |

|      |       | 2.3.5.4 Transmit (Only) Statistics Descriptions                                                                  |   |

|      |       | 2.3.5.5 Receive and Transmit (Shared) Statistics Descriptions                                                    |   |

|      |       | 2.3.6 Time Synchronization Submodule Architecture                                                                |   |

|      |       | 2.3.6.1 Time Synchronization Submodule Components                                                                |   |

|      |       | 2.3.6.2 Time Synchronization Events                                                                              |   |

|      |       | 2.3.6.3 Time Synchronization Initialization                                                                      |   |

|      |       | 2.3.6.4 Detecting and Processing Time Synchronization Events                                                     |   |

|      |       | 2.3.7       Address Lookup Engine (ALE) Submodule Architecture       72         2.3.7.1       ALE Table       73 |   |

|      |       |                                                                                                                  | - |

|      |       | 2.3.7.2 Reading Entries from the ALE Table                                                                       |   |

|      |       | 2.3.7.3 Writing Entries to the ALE Table                                                                         |   |

|      |       | 2.3.7.4       ALE Table Entry Types       74         2.3.7.5       ALE Packet Forwarding Process       75        |   |

|      |       |                                                                                                                  |   |

|      |       | 2.3.7.6       ALE Learning Process                                                                               |   |

|      |       | 2.3.8 End Correction Code (ECC) Submodule Architecture                                                           |   |

|      |       | 2.3.8.2 Packet Protect CRC                                                                                       |   |

|      |       | 2.3.8.3 ECC Submodule RAM Control                                                                                |   |

|      |       |                                                                                                                  | 1 |

|   |       | 2.3.8.4 ECC Submodule Registers                                                                |

|---|-------|------------------------------------------------------------------------------------------------|

|   | 2.4   | erial Gigabit Media Independent Interface (SGMII) Architecture                                 |

|   |       | 4.1 SGMII Receive Interface                                                                    |

|   |       | 4.2 SGMII Transmit Interface                                                                   |

|   |       | 4.3 Modes of Operation                                                                         |

|   |       | 2.4.3.1 Digital Loopback                                                                       |

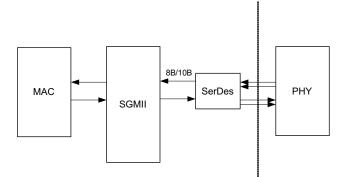

|   |       | 2.4.3.2 SGMII to PHY Configuration                                                             |

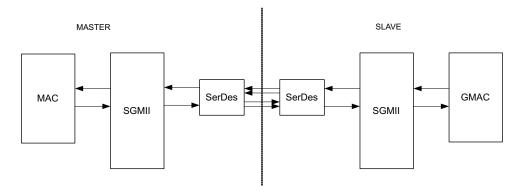

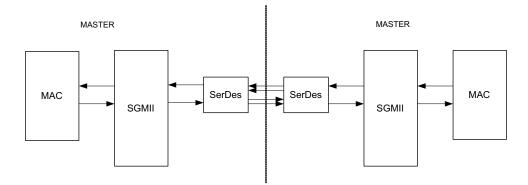

|   |       | 2.4.3.3 SGMII to SGMII with Auto-Negotiation Configuration                                     |

|   |       | 2.4.3.4 SGMII to SGMII with Forced Link Configuration                                          |

|   | 2.5   | anagement Data Input/Output (MDIO) Architecture                                                |

|   |       | 5.1 Global PHY Detection and Link State Monitoring                                             |

|   |       | 5.2 PHY Register User Access                                                                   |

|   |       | 2.5.2.1 Writing Data to a PHY Register                                                         |

|   |       | 2.5.2.2 Reading Data from a PHY Register                                                       |

|   |       | 5.3 MDIO Interrupts                                                                            |

|   |       | 2.5.3.1 MDIO Link Status Interrupts                                                            |

|   |       | 2.5.3.2 MDIO User Access Interrupts                                                            |

|   |       | 5.4 Initializing the MDIO Module                                                               |

|   | 2.6   | erializer/Deserializer (SerDes) Architecture                                                   |

|   | 2.7   | eset Considerations                                                                            |

|   | 2.8   | itialization                                                                                   |

|   |       | 8.1 GbE Switch Subsystem Initialization Procedure                                              |

|   | 2.9   | terrupt Support                                                                                |

|   |       | 9.1 Interrupt Events                                                                           |

|   | 2.10  | ower Management                                                                                |

| 3 | Regis | rs                                                                                             |

| • | 3.1   | ummary of Modules                                                                              |

|   | 3.2   | igabit Ethernet (GbE) Switch Subsystem Module                                                  |

|   |       | 2.1 Ethernet Switch Subsystem Identification and Version Register (ES_SS_IDVER)                |

|   |       | 2.2 Ethernet Switch Subsystem Synchronous Ethernet Count Register (ES_SS_SYNCE_COUNT) 122      |

|   |       | 2.3 Ethernet Switch Subsystem Synchronous Ethernet Clock Select Register (ES_SS_SYNCE_MUX) 123 |

|   | 3.3   | erial Gigabit Media Independent Interface (SGMII) module                                       |

|   |       | 3.1 SGMII Identification and Version Register (SGMII_IDVER) 125                                |

|   |       | 3.2 SGMII Software Reset Register (SGMII_SOFT_RESET) 126                                       |

|   |       | 3.3 SGMII Control Register (SGMII_CONTROL)                                                     |

|   |       | 3.4 SGMII Status Register (SGMIL STATUS)                                                       |

|   |       | 3.5 SGMII Advertised Ability Register (SGMII_MR_ADV_ABILITY)                                   |

|   |       | 3.3.5.1 SGMII MODE                                                                             |

|   |       | 3.6 SGMII Next Page Transmit Register (SGMII_MR_NP_TX)                                         |

|   |       | 3.7 SGMII Link Partner Advertised Ability Register (SGMII_MR_LP_ADV_ABILITY)                   |

|   |       | 3.8 SGMII Link Partner Next Page Received Register (SGMII_MR_LP_NP_RX)                         |

|   | 3.4   | anagement Data Input/Output (MDIO) module                                                      |

|   |       | 4.1 MDIO Version Register (MDIO_VERSION)                                                       |

|   |       | 4.2 MDIO Control Register (MDIO_CONTROL)                                                       |

|   |       | 4.3 PHY Alive Status Register (MDIO_ALIVE)                                                     |

|   |       | 4.4 PHY Link Status Register (MDIO_LINK)                                                       |

|   |       | 4.5 MDIO Link Status Change Interrupt (Unmasked) Register (MDIO_LINKINTRAW)                    |

|   |       | 4.6 MDIO Link Status Change Interrupt (Masked) Register (MDIO_LINKINTMASKED)                   |

|   |       | 4.7 MDIO Link Status Change Interrupt (Masked) Set Register (MDIO_LINKINTMASKSET) 140          |

|   |       | 4.8 MDIO Link Status Change Interrupt (Masked) Clear Register (MDIO_LINKINTMASKCLR) 141        |

|   |       | 4.9 MDIO User Command Complete Interrupt (Unmasked) Register (MDIO_USERINTRAW)                 |

|   |       | 4.10 MDIO User Command Complete Interrupt (Masked) Register (MDIO_USERINTMASKED) 143           |

|   |       | 4.11 MDIO User Command Complete Interrupt Mask Set Register (MDIO_USERINTMASKSET) 144          |

|   |       |                                                                                                |

|     | 3.4.12 MD   | IO User Command Complete Interrupt Mask Clear Register (MDIO_USERINTMASKCLEAR) .                            | 145 |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|-----|

|     |             | IO Manual Interface Register (MDIO_MANUAL_IF)                                                               |     |

|     |             | IO Control 2 Register (MDIO_CONTROL2)                                                                       |     |

|     |             | IO Poll Enable Register (MDIO_POLL_EN)                                                                      |     |

|     |             | IO Clause Mode Register (MDIO_CLAUSE)                                                                       |     |

|     |             | IO User Address Register 0 (MDIO_USERADDRESS0)                                                              |     |

|     |             | IO User Address Register 1 (MDIO_USERADDRESS1)                                                              |     |

|     | 3.4.19 MD   | IO User Access Register 0 (MDIO_USERACCESS0)                                                                | 152 |

|     |             | IO User PHY Select Register 0 (MDIO_USERPHYSEL0)                                                            |     |

|     | 3.4.21 MD   | IO User Access Register 1 (MDIO_USERACCESS1)                                                                | 154 |

|     |             | IO User PHY Select Register 1 (MDIO_USERPHYSEL1)                                                            |     |

| 3.5 | Ethernet Sw | vitch Module                                                                                                | 156 |

|     | 3.5.1 Giga  | bit Ethernet (GbE) Switch Module                                                                            | 157 |

|     | 3.5.1.1     | GbE Switch Identification and Version Register (CPSW_IDVER)                                                 | 158 |

|     | 3.5.1.2     | GbE Switch Control Register (CPSW_CONTROL)                                                                  | 159 |

|     | 3.5.1.3     | Emulation Control Register (CPSW_EM_CONTROL)                                                                | 161 |

|     | 3.5.1.4     | Statistics Port Enable Register (CPSW_STAT_PORT_EN)                                                         | 162 |

|     | 3.5.1.5     | Priority Type Register (CPSW_PTYPE)                                                                         | 163 |

|     | 3.5.1.6     | Software Idle Register (CPSW_SOFT_IDLE)                                                                     | 164 |

|     | 3.5.1.7     | Through Rate Register (CPSW_THRU_RATE)                                                                      | 165 |

|     | 3.5.1.8     | Ethernet Port Short Gap Threshold Register (CPSW_GAP_THRESH)                                                | 166 |

|     | 3.5.1.9     | FIFO Packet Transmit (Egress) Start Words Register (CPSW_TX_START_WDS)                                      | 167 |

|     | 3.5.1.10    | Priority Based Flow Control Global Outflow Usage Threshold Set Register<br>(CPSW_TX_OUTFLOW_THRESH_SET)     | 168 |

|     | 3.5.1.11    | Priority Based Flow Control Global Outflow Usage Threshold Clear Register<br>(CPSW_TX_OUTFLOW_THRESH_CLR)   | 169 |

|     | 3.5.1.12    | Priority Based Flow Control Global Buffer Usage Threshold Set Low Register (CPSW_TX_BUFFER_THRESH_SET_L).   | 170 |

|     | 3.5.1.13    | Priority Based Flow Control Global Buffer Usage Threshold Set High Register (CPSW_TX_BUFFER_THRESH_SET_H)   | 171 |

|     | 3.5.1.14    | Priority Based Flow Control Global Buffer Usage Threshold Clear Low Register (CPSW_TX_BUFFER_THRESH_CLR_L)  | 172 |

|     | 3.5.1.15    | Priority Based Flow Control Global Buffer Usage Threshold Clear High Register (CPSW_TX_BUFFER_THRESH_CLR_H) | 173 |

|     | 3.5.2 Swite | ch Port Submodules                                                                                          |     |

|     | 3.5.2.1     | Port n Control Register (Pn_CONTROL)                                                                        |     |

|     | 3.5.2.2     | Port n FIFO Block Usage Count Register (Pn_BLK_CNT)                                                         | 180 |

|     | 3.5.2.3     | Port n VLAN Register (Pn_PORT_VLAN)                                                                         | 181 |

|     | 3.5.2.4     | Port n Transmit Priority Mapping Register (Pn_TX_PRI_MAP)                                                   | 182 |

|     | 3.5.2.5     | Port n Priority Control Register (Pn_PRI_CTL)                                                               | 183 |

|     | 3.5.2.6     | Port n Receive Priority Mapping Register (Pn_RX_PRI_MAP)                                                    | 185 |

|     | 3.5.2.7     | Port n Receive Frame Maximum Length Register (Pn_RX_MAXLEN)                                                 | 186 |

|     | 3.5.2.8     | Port n Transmit Blocks Priority Register (Pn_TX_BLKS_PRI)                                                   | 187 |

|     | 3.5.2.9     | Port n Receive IPv4/IPv6 DSCP Priority Mapping Register 0 (Pn_RX_DSCP_MAP0)                                 | 188 |

|     | 3.5.2.10    | Port n Receive IPv4/IPv6 DSCP Priority Mapping Register 1 (Pn_RX_DSCP_MAP1)                                 | 189 |

|     | 3.5.2.11    | Port n Receive IPv4/IPv6 DSCP Priority Mapping Register 2 (Pn_RX_DSCP_MAP2)                                 | 190 |

|     | 3.5.2.12    | Port n Receive IPv4/IPv6 DSCP Priority Mapping Register 3 (Pn_RX_DSCP_MAP3)                                 | 191 |

|     | 3.5.2.13    | Port n Receive IPv4/IPv6 DSCP Priority Mapping Register 4 (Pn_RX_DSCP_MAP4)                                 | 192 |

|     | 3.5.2.14    | Port n Receive IPv4/IPv6 DSCP Priority Mapping Register 5 (Pn_RX_DSCP_MAP5)                                 | 193 |

|     | 3.5.2.15    | Port n Receive IPv4/IPv6 DSCP Priority Mapping Register 6 (Pn_RX_DSCP_MAP6)                                 | 194 |

|     | 3.5.2.16    | Port n Receive IPv4/IPv6 DSCP Priority Mapping Register 7 (Pn_RX_DSCP_MAP7)                                 | 195 |

|     | 3.5.2.17    | Port n Receive Priority 0 Send Count Value Register (Pn_PRI0_SEND)                                          | 196 |

|     | 3.5.2.18    | Port n Receive Priority 1 Send Count Value Register (Pn_PRI1_SEND)                                          | 197 |

|     | 3.5.2.19    | Port n Receive Priority 2 Send Count Value Register (Pn_PRI2_SEND)                                          | 198 |

|     | 3.5.2.20    | Port n Receive Priority 3 Send Count Value Register (Pn_PRI3_SEND)                                          | 199 |

| 3.5.2.21                                                                                                                                                                         | Port n Receive Priority 4 Send Count Value Register (Pn_PRI4_SEND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 200                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.5.2.22                                                                                                                                                                         | Port n Receive Priority 5 Send Count Value Register (Pn_PRI5_SEND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 201                                                                                                                                                                                                                                     |

| 3.5.2.23                                                                                                                                                                         | Port n Receive Priority 6 Send Count Value Register (Pn_PRI6_SEND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 202                                                                                                                                                                                                                                     |

| 3.5.2.24                                                                                                                                                                         | Port n Receive Priority 7 Send Count Value Register (Pn_PRI7_SEND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 203                                                                                                                                                                                                                                     |

| 3.5.2.25                                                                                                                                                                         | Port n Receive Priority 0 Idle Count Value Register (Pn_PRI0_IDLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 204                                                                                                                                                                                                                                     |

| 3.5.2.26                                                                                                                                                                         | Port n Receive Priority 1 Idle Count Value Register (Pn_PRI1_IDLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                         |

| 3.5.2.27                                                                                                                                                                         | Port n Receive Priority 2 Idle Count Value Register (Pn_PRI2_IDLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 206                                                                                                                                                                                                                                     |

| 3.5.2.28                                                                                                                                                                         | Port n Receive Priority 3 Idle Count Value Register (Pn_PRI3_IDLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                         |

| 3.5.2.29                                                                                                                                                                         | Port n Receive Priority 4 Idle Count Value Register (Pn_PRI4_IDLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                         |

| 3.5.2.30                                                                                                                                                                         | Port n Receive Priority 5 Idle Count Value Register (Pn_PRI5_IDLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                         |

| 3.5.2.31                                                                                                                                                                         | Port n Receive Priority 6 Idle Count Value Register (Pn_PRI6_IDLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                         |

| 3.5.2.32                                                                                                                                                                         | Port n Receive Priority 7 Idle Count Value Register (Pn_PRI7_IDLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                         |

| 3.5.2.33                                                                                                                                                                         | Port n Transmit Destination Threshold Set Low Register (Pn_TX_DEST_THRESH_SET_L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |

| 3.5.2.34                                                                                                                                                                         | Port n Transmit Destination Threshold Set High Register (Pn_TX_DEST_THRESH_SET_H).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                         |

| 3.5.2.35                                                                                                                                                                         | Port n Transmit Destination Threshold Clear Low Register<br>(Pn_TX_DEST_THRESH_CLR_L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                         |

| 3.5.2.36                                                                                                                                                                         | Port n Transmit Destination Threshold Clear High Register<br>(Pn_TX_DEST_THRESH_CLR_H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                         |

| 2 5 2 27                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 215                                                                                                                                                                                                                                     |

| 3.5.2.37                                                                                                                                                                         | Port n Global Transmit Buffer Threshold Set Low Register<br>(Pn_TX_BUFFER_THRESH_SET_L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 216                                                                                                                                                                                                                                     |

| 3.5.2.38                                                                                                                                                                         | Port n Global Transmit Buffer Threshold Set High Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.0                                                                                                                                                                                                                                     |

| 0.0.2.00                                                                                                                                                                         | (Pn_TX_BUFFER_THRESH_SET_H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 217                                                                                                                                                                                                                                     |

| 3.5.2.39                                                                                                                                                                         | Port n Global Transmit Buffer Threshold Clear Low Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                         |

|                                                                                                                                                                                  | (Pn_TX_BUFFER_THRESH_CLR_L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 218                                                                                                                                                                                                                                     |

| 3.5.2.40                                                                                                                                                                         | Port n Global Transmit Buffer Destination Threshold Clear High Register<br>(Pn_TX_BUFFER_THRESH_CLR_H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 219                                                                                                                                                                                                                                     |

| 3.5.2.41                                                                                                                                                                         | Host Port 0 Source ID A Register (P0_SRC_ID_A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 220                                                                                                                                                                                                                                     |

| 3.5.2.42                                                                                                                                                                         | Host Port 0 Source ID B Register (P0_SRC_ID_B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 221                                                                                                                                                                                                                                     |

| 3.5.2.43                                                                                                                                                                         | Host Port 0 Host Blocks Priority Register (P0_HOST_BLKS_PRI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 222                                                                                                                                                                                                                                     |

|                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                         |

| 3.5.2.44                                                                                                                                                                         | Ethernet Port n Transmit Destination Out Flow Add Values Low Register<br>(Pn_TX_DEST_OUTFLOW_ADDVAL_L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                         |

| 3.5.2.44<br>3.5.2.45                                                                                                                                                             | Ethernet Port n Transmit Destination Out Flow Add Values Low Register<br>(Pn_TX_DEST_OUTFLOW_ADDVAL_L)<br>Ethernet Port n Transmit Destination Out Flow Add Values High Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 223                                                                                                                                                                                                                                     |

|                                                                                                                                                                                  | Ethernet Port n Transmit Destination Out Flow Add Values Low Register<br>(Pn_TX_DEST_OUTFLOW_ADDVAL_L)<br>Ethernet Port n Transmit Destination Out Flow Add Values High Register<br>(Pn_TX_DEST_OUTFLOW_ADDVAL_H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 223<br>224                                                                                                                                                                                                                              |

| 3.5.2.45                                                                                                                                                                         | Ethernet Port n Transmit Destination Out Flow Add Values Low Register<br>(Pn_TX_DEST_OUTFLOW_ADDVAL_L)<br>Ethernet Port n Transmit Destination Out Flow Add Values High Register<br>(Pn_TX_DEST_OUTFLOW_ADDVAL_H)<br>Ethernet Port n Pause Frame Source Address Low Register (Pn_PAUSE_SA_L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 223<br>224<br>225                                                                                                                                                                                                                       |