# TMS320C6452 DSP Peripheral Component Interconnect (PCI)

# **User's Guide**

Literature Number: SPRUF86 October 2007

# Contents

| Pref | face    |                                                  | . 8 |

|------|---------|--------------------------------------------------|-----|

| 1    | Introdu | uction                                           | 11  |

|      | 1.1     | Purpose of the Peripheral                        | 11  |

|      | 1.2     | Features                                         | 11  |

|      | 1.3     | Features Not Supported                           | 12  |

|      | 1.4     | Functional Block Diagram                         | 12  |

|      | 1.5     | Supported Use Case Statement                     | 13  |

|      | 1.6     | Industry Standard(s) Compliance Statement        | 13  |

| 2    | Archite | ecture                                           | 14  |

|      | 2.1     | Clock Control                                    | 14  |

|      | 2.2     | Memory Map                                       | 14  |

|      | 2.3     | Signal Descriptions                              |     |

|      | 2.4     | Pin Multiplexing                                 | 15  |

|      | 2.5     | Byte Addressing                                  | 15  |

|      | 2.6     | PCI Error Detection                              | 15  |

|      | 2.7     | Status Reporting                                 | 17  |

|      | 2.8     | Reset Considerations                             | 17  |

|      | 2.9     | Interrupt Support                                | 19  |

|      | 2.10    | DMA Event Support                                |     |

|      | 2.11    | Emulation Considerations                         | 20  |

|      | 2.12    | PCI Configuration                                | 20  |

|      | 2.13    | Connecting a Local PCI to an External PCI Device | 24  |

| 3    | PCI SI  | ave Operation                                    |     |

|      | 3.1     | Slave Memory Map                                 |     |

|      | 3.2     | Configuring Slave Window Registers               |     |

|      | 3.3     | Slave Access Address Translations                |     |

|      | 3.4     | Slave Configuration Operations                   |     |

|      | 3.5     | Slave Memory Operations                          |     |

| 4    |         | aster Operation                                  |     |

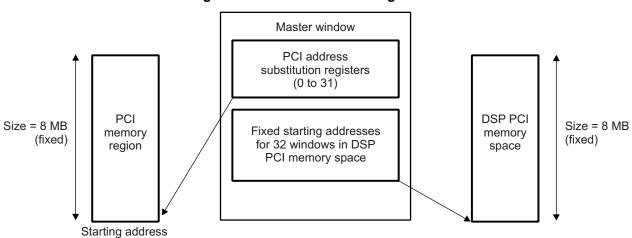

| •    | 4.1     | Master Memory Map                                |     |

|      | 4.2     | Configuring Master Windows                       |     |

|      | 4.3     | Master Address Translation                       |     |

|      | 4.4     | Master Configuration Operations                  |     |

|      | 4.5     | Master I/O Operations                            |     |

|      | 4.6     | Master Memory Operations                         |     |

| 5    |         | gisters                                          |     |

| •    | 5.1     | PCI Configuration Registers                      |     |

|      | 5.2     | PCI Memory-Mapped Registers                      |     |

|      | 5.3     | PCI Configuration Hook Registers                 |     |

|      | 0.0     |                                                  | 13  |

# List of Figures

| 1        | PCI Block Diagram                                                                        |    |

|----------|------------------------------------------------------------------------------------------|----|

| 2        | PCI Signals                                                                              | 14 |

| 3        | Internal and External Reset Inputs of the PCI Module                                     | 18 |

| 4        | Signal Connections for I2C EEPROM Boot Mode                                              | 23 |

| 5        | PCI to External PCI Device                                                               | 24 |

| 6        | Slave Window Configuration                                                               | 27 |

| 7        | PCI-to-DSP Address Translation                                                           | 29 |

| 8        | Master Window Configuration                                                              | 34 |

| 9        | PCI Address Substitution Register (0 to 31)                                              | 34 |

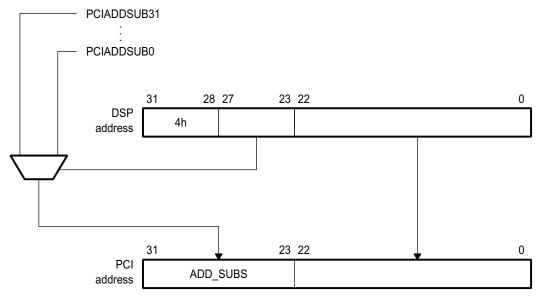

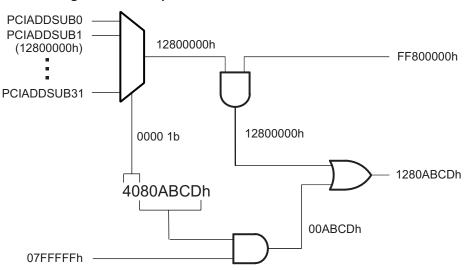

| 10       | DSP-to-PCI Address Translation                                                           | 35 |

| 11       | Example of DSP-to-PCI Address Translation                                                | 35 |

| 12       | Vendor Identification Register                                                           |    |

| 13       | Device Identification Register                                                           |    |

| 14       | PCI Command Register                                                                     |    |

| 15       | PCI Status Register                                                                      |    |

| 16       | Revision Identification Register                                                         |    |

| 17       | Class Code Register                                                                      |    |

| 18       | Cache Line Size Register                                                                 |    |

| 19       | Latency Timer Register                                                                   |    |

| 20       | Header Type Register                                                                     |    |

| 21       | Built-In Self-Test Register                                                              |    |

| 22       | Base Address 0 Register                                                                  |    |

| 23       | Base Address 1 Register                                                                  |    |

| 24       | Base Address 2 Register                                                                  |    |

| 25       | Base Address 3 Register                                                                  |    |

| 26       | Base Address 4 Register                                                                  |    |

| 27       | Base Address 5 Register                                                                  |    |

| 28       | Subsystem Identification Register                                                        |    |

| 29       | Subsystem Vendor Identification Register                                                 |    |

| 30       | Capabilities Pointer Register                                                            |    |

| 31       | Interrupt Line Register                                                                  |    |

| 32       | Interrupt Pin Register                                                                   |    |

| 33       | Minimum Grant Register                                                                   |    |

| 34       | Maximum Latency Register                                                                 |    |

| 35       | Status Set and Status Clear Registers (PCISTATSET/PCISTATCLR)                            |    |

| 36       | Host Interrupt Enable Set and Clear Registers (PCIHINTSET/PCIHINTCLR)                    |    |

| 37       | DSP Interrupt Enable Set and Clear Registers (PCIDINTSET/PCIDINTCLR)                     |    |

| 38       | Vendor ID/Device ID Mirror Register (PCIVENDEVMIR)                                       |    |

| 39       | Command/Status Mirror Register (PCICSRMIR)                                               |    |

| 40       | Class Code/Revision Identification Mirror Register (PCICLREVMIR)                         |    |

| 40<br>41 | BIST/Header Type/Latency Timer/Cacheline Size Mirror Register (PCICLINEMIR)              |    |

| 42       | Base Address 0 Mask Register (PCIBAR0MSK)                                                |    |

| 43       | Base Address 1 Mask Register (PCIBAR1MSK)                                                |    |

| 43<br>44 | Base Address 2Mask Register (PCIBAR1MISK)                                                |    |

| 44<br>45 | Base Address 3 Mask Register (PCIBAR3MSK)                                                |    |

| 45<br>46 | Base Address 4 Mask Register (PCIBAR3MSK)                                                |    |

|          | Base Address 5 Mask Register (PCIBAR5MSK)                                                |    |

| 47<br>48 | Subsystem Vendor Identification/Subsystem Identification Mirror Register (PCISUBIDMIR)   |    |

| 48<br>40 |                                                                                          |    |

| 49<br>50 | Capabilities Pointer Mirror Register (PCICPBPTRMIR)                                      |    |

| 50       | Maximum Latency/Minimum Grant/Interrupt Pin/Interrupt Line Mirror Register (PCILGINTMIR) |    |

| 51<br>52 | Slave Control Register (PCISLVCNTL)                                                      |    |

| 52       | Slave Base Address 0 Translation Register (PCIBAR0TRL)                                   | 11 |

| 53 | Slave Base Address 1 Translation Register (PCIBAR1TRL)                                          | 71 |

|----|-------------------------------------------------------------------------------------------------|----|

| 54 | Slave Base Address 2 Translation Register (PCIBAR2TRL)                                          | 71 |

| 55 | Slave Base Address 3 Translation Register (PCIBAR3TRL)                                          | 71 |

| 56 | Slave Base Address 4 Translation Register (PCIBAR4TRL)                                          | 72 |

| 57 | Slave Base Address 5 Translation Register (PCIBAR5TRL)                                          | 72 |

| 58 | Base Address 0 Mirror Register (PCIBAR0MIR)                                                     | 73 |

| 59 | Base Address 1 Mirror Register (PCIBAR1MIR)                                                     | 73 |

| 60 | Base Address 2 Mirror Register (PCIBAR2MIR)                                                     | 73 |

| 61 | Base Address 3 Mirror Register (PCIBAR3MIR)                                                     | 73 |

| 62 | Base Address 4 Mirror Register (PCIBAR4MIR)                                                     | 74 |

| 63 | Base Address 5 Mirror Register (PCIBAR5MIR)                                                     | 74 |

| 64 | Master Configuration/IO Access Data Register (PCIMCFGDAT)                                       | 75 |

| 65 | Master Configuration/IO Access Address Register (PCIMCFGADR)                                    | 75 |

| 66 | Master Configuration/IO Access Command Register (PCIMCFGCMD)                                    | 76 |

| 67 | Master Configuration Register (PCIMSTCFG)                                                       | 77 |

| 68 | PCI Address Substitution <i>n</i> Registers (PCIADDSUB0-PCIADDSUB31)                            | 78 |

| 69 | PCI Vendor Identification and Device Identification Program Register (PCIVENDEVPRG)             | 79 |

| 70 | PCI Class Code and Revision Identification Program Register (PCICLREVPRG)                       | 80 |

| 71 | PCI Subsystem Vendor Identification and Subsystem Identification Program Register (PCISUBIDPRG) | 80 |

| 72 | Maximum Latency and Minimum Grant Program Register (PCIMAXLGPRG)                                | 81 |

| 73 | Configuration Done Register (PCICFGDONE)                                                        | 81 |

| 1  | PCI Pin Description                                                                                          |    |

|----|--------------------------------------------------------------------------------------------------------------|----|

| 2  | PCI Exceptions                                                                                               | 15 |

| 3  | Device-Level Global Reset Sources When Using the PCI Module                                                  | 18 |

| 4  | PCI Interrupts                                                                                               |    |

| 5  | PCI Configuration Register Default Values                                                                    |    |

| 6  | I2C EEPROM Memory Layout                                                                                     |    |

| 7  | PCI Base Addresses                                                                                           | 26 |

| 8  | PCI Master Windows                                                                                           | 33 |

| 9  | Byte Enables and AD[1-0] Encodings                                                                           | 37 |

| 10 | PCI Configuration Registers                                                                                  | 39 |

| 11 | Vendor Identification Register Field Descriptions                                                            | 40 |

| 12 | Device Identification Register Field Descriptions                                                            | 40 |

| 13 | PCI Command Register Field Descriptions                                                                      | 41 |

| 14 | PCI Status Register Field Descriptions                                                                       | 42 |

| 15 | Revision Identification Register Field Descriptions                                                          | 43 |

| 16 | Class Code Register Field Descriptions                                                                       | 43 |

| 17 | Cache Line Size Register Field Descriptions                                                                  | 44 |

| 18 | Latency Timer Register Field Descriptions                                                                    | 44 |

| 19 | Header Type Register Field Descriptions                                                                      | 45 |

| 20 | Built-In Self-Test Register Field Descriptions                                                               | 45 |

| 21 | Base Address <i>n</i> Registers Field Descriptions                                                           | 47 |

| 22 | Subsystem Identification Register Field Descriptions                                                         | 48 |

| 23 | Subsystem Vendor Identification Register Field Descriptions                                                  | 48 |

| 24 | Capabilities Pointer Register Field Descriptions                                                             | 48 |

| 25 | Interrupt Line Register Field Descriptions                                                                   | 49 |

| 26 | Interrupt Pin Register Field Descriptions                                                                    | 49 |

| 27 | Minimum Grant Register Field Descriptions                                                                    | 50 |

| 28 | Maximum Latency Register Field Descriptions                                                                  | 50 |

| 29 | PCI Memory-Mapped Registers                                                                                  | 51 |

| 30 | Status Set and Status Clear Registers (PCISTATSET/PCISTATCLR) Field Descriptions During Reads                | 54 |

| 31 | Status Set Register (PCISTATSET) Field Descriptions During Writes                                            | 55 |

| 32 | Status Clear Register (PCISTATCLR) Field Descriptions During Writes                                          | 56 |

| 33 | Host Interrupt Enable Set Register (PCIHINTSET) Field Descriptions                                           | 58 |

| 34 | Host Interrupt Enable Clear Register (PCIHINTCLR) Field Descriptions                                         | 59 |

| 35 | DSP Interrupt Enable Set Register (PCIDINTSET) Field Descriptions                                            | 61 |

| 36 | DSP Interrupt Enable Clear Register (PCIDINTCLR) Field Descriptions                                          | 62 |

| 37 | Vendor ID/Device ID Mirror Register (PCIVENDEVMIR) Field Descriptions                                        | 62 |

| 38 | Command/Status Mirror Register (PCICSRMIR) Field Descriptions                                                | 63 |

| 39 | Class Code/Revision Identification Mirror Register (PCICLREVMIR) Field Descriptions                          | 64 |

| 40 | BIST/Header Type/Latency Timer/Cacheline Size Mirror Register (PCICLINEMIR) Field Descriptions               | 65 |

| 41 | Base Address n Mask Registers (PCIBAR0MSK-PCIBAR5MSK) Field Descriptions                                     | 67 |

| 42 | Subsystem Vendor Identification/Subsystem Identification Mirror Register (PCISUBIDMIR) Field<br>Descriptions | 68 |

| 43 | Capabilities Pointer Mirror Register (PCICPBPTRMIR) Field Descriptions                                       |    |

| 44 | Maximum Latency/Minimum Grant/Interrupt Pin/Interrupt Line Mirror Register (PCILGINTMIR) Field Descriptions  | 69 |

| 45 | Slave Control Register (PCISLVCNTL) Field Descriptions                                                       |    |

| 46 | Slave Base Address <i>n</i> Translation Registers (PCIBAR0TRL-PCIBAR5TRL) Field Descriptions                 |    |

| 47 | Base Address <i>n</i> Mirror Registers (PCIBAR0MIR-PCIBAR5MIR) Field Descriptions                            |    |

| 48 | Master Configuration/IO Access Data Register (PCIMCFGDAT) Field Descriptions                                 |    |

|    |                                                                                                              |    |

# List of Tables

| 49 | Master Configuration/IO Access Address Register (PCIMCFGADR) Field Descriptions                                       | 75 |

|----|-----------------------------------------------------------------------------------------------------------------------|----|

| 50 | Master Configuration/IO Access Command Register (PCIMCFGCMD) Field Descriptions                                       | 76 |

| 51 | Master Configuration Register (PCIMSTCFG) Field Descriptions                                                          | 77 |

| 52 | PCI Address Substitution <i>n</i> Registers (PCIADDSUB0-PCIADDSUB31) Field Descriptions                               | 78 |

| 53 | PCI Configuration Hook Registers                                                                                      | 79 |

| 54 | PCI Vendor Identification and Device Identification Program Register (PCIVENDEVPRG) Field Descriptions                | 79 |

| 55 | PCI Class Code and Revision Identification Program Register (PCICLREVPRG) Field Descriptions                          | 80 |

| 56 | PCI Subsystem Vendor Identification and Subsystem Identification Program Register (PCISUBIDPRG)<br>Field Descriptions | 80 |

| 57 | Maximum Latency and Minimum Grant Program Register (PCIMAXLGPRG) Field Descriptions                                   | 81 |

| 58 | Configuration Done Register (PCICFGDONE) Field Descriptions                                                           | 81 |

Preface SPRUF86–October 2007

# About This Manual

Describes the peripheral component interconnect (PCI) module in the TMS320C6452 Digital Signal Processor (DSP).

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

- **Note:** Acronyms 3PSW, CPSW, CPSW\_3G, and 3pGSw are interchangeable and all refer to the 3 port gigabit switch.

#### TMS320C6452 DSP

#### **Related Documents From Texas Instruments**

The following documents describe the TMS320C6452 Digital Signal Processor (DSP). Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at <u>www.ti.com</u>.

#### Data Manual—

<u>SPRS371</u> — *TMS320C6452 Digital Signal Processor Data Manual* describes the signals, specifications and electrical characteristics of the device.

#### CPU—

SPRU732 — TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

#### Reference Guides—

SPRUF85 — TMS320C6452 DSP DDR2 Memory Controller User's Guide describes the DDR2 memory controller in the TMS320C6452 Digital Signal Processor (DSP). The DDR2/mDDR memory controller is used to interface with JESD79D-2A standard compliant DDR2 SDRAM devices and standard Mobile DDR SDRAM devices.

- SPRUF86 TMS320C6452 Peripheral Component Interconnect (PCI) User's Guide describes the peripheral component interconnect (PCI) port in the TMS320C6452 Digital Signal Processor (DSP). The PCI port supports connection of the C642x DSP to a PCI host via the integrated PCI master/slave bus interface. The PCI port interfaces to the DSP via the enhanced DMA (EDMA) controller. This architecture allows for both PCI master and slave transactions, while keeping the EDMA channel resources available for other applications.

- SPRUF87 TMS320C6452 DSP Host Port Interface (UHPI) User's Guide describes the host port interface (HPI) in the TMS320C6452 Digital Signal Processor (DSP). The HPI is a parallel port through which a host processor can directly access the CPU memory space. The host device functions as a master to the interface, which increases ease of access. The host and CPU can exchange information via internal or external memory. The host also has direct access to memory-mapped peripherals. Connectivity to the CPU memory space is provided through the enhanced direct memory access (EDMA) controller.

- SPRUF89 TMS320C6452 DSP VLYNQ Port User's Guide describes the VLYNQ port in the TMS320C6452 Digital Signal Processor (DSP). The VLYNQ port is a high-speed point-to-point serial interface for connecting to host processors and other VLYNQ compatible devices. It is a full-duplex serial bus where transmit and receive operations occur separately and simultaneously without interference.

- SPRUF90 TMS320C6452 DSP 64-Bit Timer User's Guide describes the operation of the 64-bit timer in the TMS320C6452 Digital Signal Processor (DSP). The timer can be configured as a general-purpose 64-bit timer, dual general-purpose 32-bit timers, or a watchdog timer.

- <u>SPRUF91</u> *TTMS320C6452 DSP Multichannel Audio Serial Port (McASP) User's Guide* describes the multichannel audio serial port (McASP) in the TMS320C6452 Digital Signal Processor (DSP). The McASP functions as a general-purpose audio serial port optimized for the needs of multichannel audio applications. The McASP is useful for time-division multiplexed (TDM) stream, Inter-Integrated Sound (I2S) protocols, and intercomponent digital audio interface transmission (DIT).

- SPRUF92 TMS320C6452 DSP Serial Port Interface (SPI) User's Guide discusses the Serial Port Interface (SPI) in the TMS320C6452 Digital Signal Processor (DSP). This reference guide provides the specifications for a 16-bit configurable, synchronous serial peripheral interface. The SPI is a programmable-length shift register, used for high speed communication between external peripherals or other DSPs.

- SPRUF93 TMS320C6452 DSP Universal Asynchronous Receiver/Transmitter (UART) User's Guide describes the universal asynchronous receiver/transmitter (UART) peripheral in the TMS320C6452 Digital Signal Processor (DSP). The UART peripheral performs serial-to-parallel conversion on data received from a peripheral device, and parallel-to-serial conversion on data received from the CPU.

- <u>SPRUF94</u> *TMS320C6452 DSP Inter-Integrated Circuit (I2C) Module User's Guide* describes the inter-integrated circuit (I2C) peripheral in the TMS320C6452 Digital Signal Processor (DSP). The I2C peripheral provides an interface between the DSP and other devices compliant with the I2C-bus specification and connected by way of an I2C-bus. External components attached to this 2-wire serial bus can transmit and receive up to 8-bit wide data to and from the DSP through the I2C peripheral. This document assumes the reader is familiar with the I2C-bus specification.

- SPRUF95 TMS320C6452 DSP General-Purpose Input/Output (GPIO) User's Guide describes the general-purpose input/output (GPIO) peripheral in the TMS320C6452 Digital Signal Processor (DSP). The GPIO peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an input, you can detect the state of the input by reading the state of an internal register. When configured as an output, you can write to an internal register to control the state driven on the output pin.

- <u>SPRUF96</u> TMS320C6452 DSP Telecom Serial Interface Port (TSIP) User's Guide is a multi-link serial interface consisting of a maximum of two transmit data signals (or links), two receive data signals (or links), two frame sync input signals, and two serial clock inputs. Internally the TSIP offers single channel of timeslot data management and single DMA capability that allow individual timeslots to be selectively processed.

- SPRUF97 TMS320C6452 DSP 3 Port Switch (3PSW) Ethernet Subsystem User's Guide describes the operation of the 3 port switch (3PSW) ethernet subsystem in the TMS320C6452 Digital Signal Processor (DSP). The 3 port switch gigabit ethernet subsystem provides ethernet packet communication and can be configured as an ethernet switch. It provides the serial gigabit media independent interface (SGMII), the management data input output (MDIO) for physical layer device (PHY) management.

# Peripheral Component Interconnect (PCI)

#### 1 Introduction

This document describes the peripheral component interconnect (PCI) module in the TMS320C6452 Digital Signal Processor (DSP). The C6452 PCI is compliant to the *PCI Local Bus Specification* (revision 2.3). See that document for details on the protocol, electrical, and mechanical specifications of the PCI.

# 1.1 Purpose of the Peripheral

The C6452 PCI module allows communication with devices complaint to the *PCI Local Bus Specification* (revision 2.3) via a 32-bit address/data bus operating at speeds up to 66 MHZ.

# 1.2 Features

The PCI module supports the following features:

- PCI Local Bus Specification (revision 2.3) compliant

- Single function PCI interface provided

- 32-bit address/data bus width

- Operation up to 66 MHZ

- Optimized burst behavior supported for system cache line sizes of 16, 32, 64 and 128 bytes

As a slave, the PCI module includes the following features:

- Response to accesses as a 32-bit agent with medium device select (PDEVSEL) timing (single wait state)

- Direct support of the Memory Read, Memory Read Multiple, Memory Read Line, Memory Write, Configuration Read and Configuration Write transactions

- Aliases Memory Write and Invalidate to the Memory Write command

- Support of variable length burst transfers up to a cache line for Memory Read Line transactions

- Support of unlimited length burst transfers for Memory Read Multiple and Memory Write transactions

- Support of single data phase transfers with disconnect for Memory Read, Configuration Read, and Configuration Write transactions

- Support of both immediate or timeout forced delayed transactions for Memory Read, Memory Read Line, and Memory Read Multiple transactions

- Support of posting of Memory Write transactions

- Support of up to six base address registers for host-to-DSP transactions

- Support of programmable cache line size of 4, 8, 16, 32, 64, or 128 bytes

- Auto-initialization sequence provided to set configuration space registers to custom values after reset

As a master, the PCI module includes the following features:

- Transaction initiation as a 32-bit agent

- Support of the Configuration Read, Configuration Write, IO Read, IO Write, Memory Read, Memory Read Line, Memory Read Multiple, Memory Write, and Memory Write and Invalidate PCI Bus commands

- Support of bursts transfers of up to 256 data phases for Memory Read Line, Memory Read Multiple, and Memory Write transactions

- Support of single data phase transfers for Memory Read transactions

Introduction

- Automatic selection between Memory Read, Memory Read Line, and Memory Read Multiple based on the requested transaction length and the cache line size

- Assertion of the **PIRDY** signal one clock cycle after the **PFRAME** signal is asserted.

# 1.3 Features Not Supported

The PCI module does not support:

- PCI special cycles

- PCI interrupt acknowledge cycles

- PCI lock

- 64-bit bus operation

- Operation at frequencies greater than 66 MHZ

- Address/data stepping

- Combining (for write posting)

- Collapsing

- Merging

- Cache line wrap accesses

- Reserved accesses

- Message signaled interrupts

- Vital product data

- Slave IO Read and IO Write Transactions

- Internal Arbitration

- Power Management

# 1.4 Functional Block Diagram

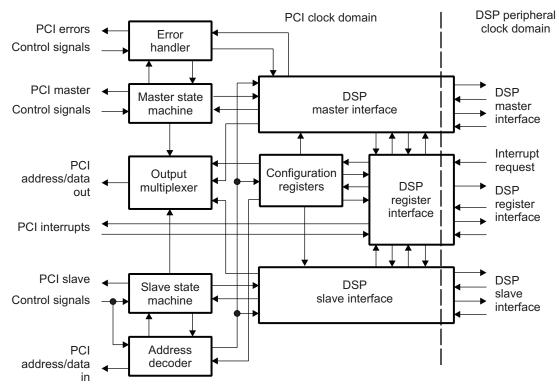

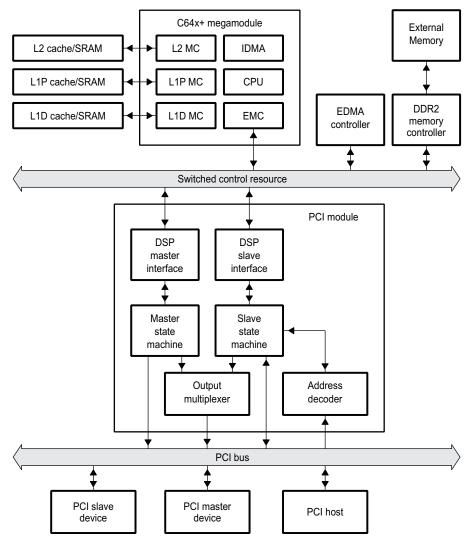

Figure 1 shows a block diagram of the PCI module.

#### Figure 1. PCI Block Diagram

The PCI module consists of the following blocks:

- Address Decoder: This block latches transaction control information from the PCI bus and decodes that information to determine if the transaction was targeted to the PCI. This block instructs the slave state machine to either accept or ignore slave transactions as they are presented on the PCI bus.

- Slave State Machine: This block generates and monitors all of the PCI signals necessary for accepting transactions on the bus. All of the slave PCI protocols handling functions are split between the address decoder and slave state machine blocks.

- **DSP Slave Interface:** This block accepts transactions from the slave state machine and passes those transactions to the targeted DSP resource (for example, DDR2 memory controller). This block performs the asynchronous decoupling between the PCI clock domain and the peripheral clock domain for slave transactions. It also implements the address translation control registers and performs address translation for slave transactions.

- **DSP Master Interface:** This block accepts bus transactions from DSP masters (for example, EDMA transfer controllers) and passes those transactions on to the master state machine. It performs the asynchronous decoupling between the peripheral clock domain and the PCI clock domain for master transactions. This block implements the address translation control registers and also performs the address translation for master transactions.

- **Master State Machine:** This block generates and monitors all of the PCI signals necessary for initiating transactions on the bus. The majority of the master PCI protocols handling functions are implemented in this block. This block responds to transfer requests that are presented to it from the DSP master block.

- **Output Multiplexer:** This block multiplexes the master address, master write data, slave configuration read data, and slave memory read data on to the AD pins at the appropriate times. This block is controlled by several of the other blocks in the PCI.

- **Configuration Registers:** This block implements the required PCI configuration registers and some of the DSP registers. These registers control the modes and options in the PCI and provide vital information to the PCI host.

- Error Handler: This block monitors for error conditions that may occur on the PCI bus.

- **DSP Register Interface:** This block implements the asynchronous bridging function that allows DSP masters to access select PCI configuration registers, the address translation registers, and other miscellaneous PCI control/status registers. This block also implements some PCI control/status registers that reside in the peripheral clock domain.

# 1.5 Supported Use Case Statement

The device allows communication with devices complaint to the *PCI Local Bus Specification* (revision 2.3) via a 32-bit address/data bus operating at speeds up to 66 MHZ.

The PCI module can operate simultaneously as a PCI slave and a PCI master. As a PCI slave, the PCI module accepts configuration cycles and memory accesses from other devices. As a PCI master, the PCI module can generate configuration cycles, IO cycles, and memory accesses to other devices.

# 1.6 Industry Standard(s) Compliance Statement

The PCI module is compliant with the PCI Local Bus Specification (revision 2.3).

#### 2 Architecture

#### 2.1 Clock Control

The PCI module uses the following clocks:

- External PCI clock

- Sourced by an external device through the PCLK pin.

- Maximum clock frequency supported is 66 MHZ.

- Internal peripheral clock

- Corresponds to SYSCLK3 of the DSP PLL Controller 1.

- The frequency of this clock is equal to the CPU clock divided by 6.

- **Note:** The peripheral clock frequency must not be less than the external PCI clock frequency to ensure PCI electrical timings are met.

#### 2.2 Memory Map

The PCI can be used by an external host to access the following processor resources:

- L2 memory

- Chip level memory mapped registers

- GEM memory mapped registers

- Asyncronous EMIF memory

- DDR2 memory

Consult the *Memory Map Summary* section in the device-specific data manual for the memory address ranges of the above resources.

#### 2.3 Signal Descriptions

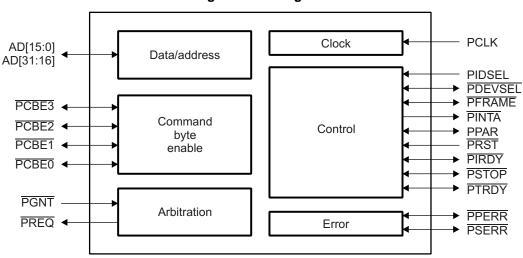

Figure 2 shows the PCI signals that are used by the PCI. Table 1 shows the PCI pin name with the signal direction and description.

Figure 2. PCI Signals

| Pin Name  | Type <sup>(1)</sup> | Description                    |  |

|-----------|---------------------|--------------------------------|--|

| PFRAME    | I/O/Z               | PCI Frame                      |  |

| PDEVSEL   | I/O/Z               | PCI Device Select              |  |

| PSTOP     | I/O/Z               | PCI Transaction Stop Indicator |  |

| PCLK      | I                   | PCI Clock                      |  |

| PCBE[3:0] | I/O/Z               | PCI Command/Byte Enables       |  |

| PPAR      | I/O/Z               | PCI Parity                     |  |

| PPERR     | I/O/Z               | PCI Parity Error               |  |

| PSERR     | I/O/Z               | PCI System Error               |  |

| PIRDY     | I/O/Z               | PCI Initiator Ready            |  |

| PINTA     | O/Z                 | PCI Interrupt A                |  |

| PRST      | I                   | PCI Reset                      |  |

| PIDSEL    | I                   | PCI Initialization Select      |  |

| PTRDY     | I/O/Z               | PCI Transmitter Ready          |  |

| AD[31:16] | I/O/Z               | PCI Data/Address bus [31:16]   |  |

| AD[15:0]  | I/O/Z               | PCI Data/Address bus [16:0]    |  |

| PREQ      | O/Z                 | PCI Bus Request                |  |

| PGNT      | I                   | PCI Bus Grant                  |  |

#### Table 1. PCI Pin Description

(1) I = Input, O = Output, Z = High impedance

#### 2.4 Pin Multiplexing

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in the smallest possible package. Pin multiplexing is controlled using a combination of hardware configuration at device reset and software programmable register settings. Refer to the device-specific data sheet to determine how pin multiplexing affects the PCI module.

#### 2.5 Byte Addressing

The PCI interface is byte-addressable. It can read and write 8-bit bytes, 16-bit half words, 24-bit words, and 32-bit words. Words are aligned on an even four-byte boundary, and always start at a byte address where the two LSBs are 00. Halfwords always start at a byte address where the last LSB is 0. PCI slave transactions are fully byte-addressable, but PCI master transactions must start on a word-aligned address.

#### 2.6 PCI Error Detection

The PCI supports the detection of the error conditions listed in Table 2. The PCI can generate an interrupt to the Host and DSP for a particular set of error conditions. The PCISTATSET, PCIHINTSET, and PCIBINTSET registers enable interrupts to the Host and DSP. The PCI also provides the status of these PCI errors, as described in section Section 2.7.

| Exception Name                                                                                                                                                              | Description                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PERR_DET                                                                                                                                                                    | Data parity error. A parity error is detected when the PCI is the master during a read transaction and when the PCI is a slave during a write transaction. |

| SERR_DET System error. A system error is detected when the PCI has received a target abort while master<br>bus, or when an address parity error is detected on the PCI bus. |                                                                                                                                                            |

| MS_ABRT_DET Master Abort. Generated when the PCI is a master to indicate that it terminated a master transa with a master abort.                                            |                                                                                                                                                            |

| TGT_ABRT_DET                                                                                                                                                                | Target Abort. Generated when the PCI is a slave to indicate it has initiated a target abort.                                                               |

Table 2. PCI Exceptions

#### 2.6.1 Parity Error

If the PCI module is mastering the bus, the master data parity error (MS\_DPAR\_ERR) bit in the PCI command/status register (PCICSR) is set under either of the following conditions:

- If a parity error has been detected during the data phase of a read transaction.

- If PPERR has been asserted by the target during the data phase of a write transaction.

The detected parity error (DET\_PAR\_ERR) bit in PCICSR is set under any of the following conditions:

- If the PCI is acting as a bus master and it detects a data parity error during a read transaction.

- If the PCI is acting as a bus target and it detects a data parity error during a write transaction.

- If the PCI detects an address parity error.

The PCI will assert PPERR if the parity error response (PAR\_ERR\_RES) bit in PCICSR is set and the DET\_PAR\_ERR bit is set. The assertion of PPERR remains valid until the second clock after the cycle in which the error occurred.

If a parity error is detected during a transfer involving the PCI, the transaction is allowed to complete unless the PCI is the master and a target disconnect is detected (that is, the PCI does not generate a master abort condition due to a parity error).

#### 2.6.2 System Error

The PCI sets an internal system error flag under any of the following conditions:

- If an address parity error is detected on the PCI bus (even if the PCI is not the target of the transaction) and the parity error response (PAR\_ERR\_RES) bit in the PCI command/status register (PCICSR) is set.

- If the PCI detected PPERR asserted while mastering the bus.

- If the PCI received a target abort (disconnect without retry) while mastering the bus.

The PCI asserts **PSERR** if the system error pin enable (SERR\_EN) bit in PCICSR is set and the internal system error flag is set. The PCI halts and waits for software or hardware reset after **PSERR** has been asserted. The PCI sets the signaled system error (SIG\_SYS\_ERR) bit in PCICSR whenever **PSERR** is asserted.

#### 2.6.3 Master Abort Protocol

If a master abort occurs while the PCI is the master, the current transfer will be gracefully terminated on both the PCI bus (by de-asserting PFRAME and asserting PIRDY) and the peripheral bus (by supplying ready signals through the DSP master interface until the burst is completed). Both the received master abort (RCV\_MS\_ABRT) bit in the PCI command/status register (PCICSR) and the received master abort (RCV\_MS\_ABRT) bit in the PCI command/status mirror register (PCICSRMIR) are set.

#### 2.6.4 Target Abort Protocol

If a target abort occurs while the PCI is the master, the current transfer will be gracefully terminated on both the PCI bus and the peripheral bus (in the same way as for the master abort). Both the received target abort (RCV\_TGT\_ABRT) bit in the PCI command/status register (PCICSR) and the received target abort (RCV\_TGT\_ABRT) bit in the PCI command/status mirror register (PCICSRMIR) are set.

#### 2.6.5 Retry/Disconnect Protocol

If a transaction is disconnected or retried, the master will unconditionally repeat the transaction starting at the location of the first remaining uncompleted word. The DSP has no knowledge of retry or disconnections on the bus.

# 2.7 Status Reporting

The PCI module provides the status of various PCI errors generated or detected by it in the command/status register (PCICSR) and an internal status register.

The PCICSR is in the PCI configuration register space. An external host can access this register through the TYPE0 configuration space access. The DSP can access this register through the command/status mirror register (PCICSRMIR).

The PCICSR provides the status of the following error conditions:

- Detected Parity Error (DET\_PAR\_ERR)

- Signaled System Error (SIG\_SYS\_ERR)

- Received Master Abort Error (RCV\_MS\_ABRT)

- Received Target Abort Error (RCV\_TGT\_ABRT)

- Signaled Target Abort (SIG\_TGT\_ABRT)

- Master Data Parity Reported (MS\_DPAR\_REP)

Status bits in PCICSR cannot be set manually. They are set only by the PCI module. A status bit in this register can be cleared by writing a 1 to that bit.

The internal status register provides the status of the following PCI interrupt and errors:

- Software interrupts (SOFT\_INT)

- Parity Error Detected (PERR\_DET)

- System Error Detected (SERR\_DET)

- Master Abort Error Detected (MS\_ABRT\_DET)

- Target Abort Error Detected (TGT\_ABRT\_DET)

The PCI provides the status set register (PCISTATSET) and the status clear register (PCISTATCLR) to set and clear the bits in the internal status register. Reading of both these registers returns the value of the internal status register. The internal status register is internal to the PCI module and is not directly accessible to an external host. It is also not directly accessible to the DSP.

To clear an error bit in the command/status register the corresponding bit in the internal status register also needs to be cleared first. The bits in the internal status register can be cleared through the status clear register (PCISTATCLR).

Setting or clearing a bit in the internal status register does not affect the corresponding bit in the command/status register. Similarly, clearing the command/status register does not affect the corresponding bit in the internal status register.

An interrupt can be generated to an external host (through the PINTA pin) and to the DSP through the bits of the internal status register provided the corresponding bit is enabled in the internal host/DSP interrupt enable register. See Section 2.9 for more details on interrupt support.

#### 2.8 Reset Considerations

#### 2.8.1 PCI Reset Sources

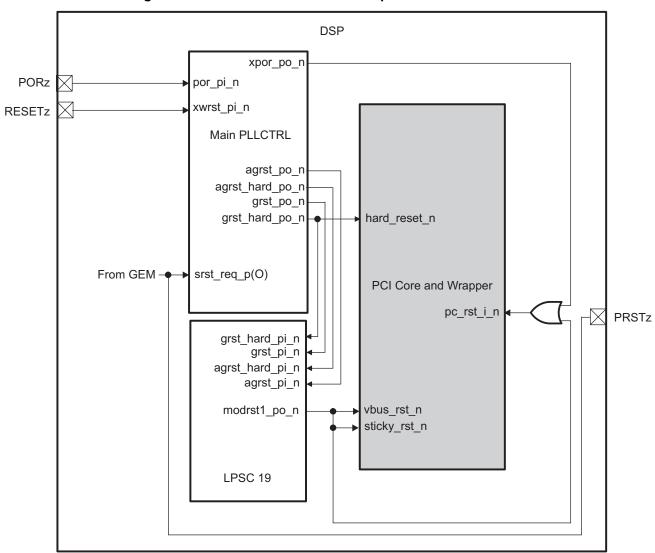

The device has both an internal and external reset source (see Figure 3).

The external reset is asserted through either the PCI reset pin (PRST) or the device power-on reset pin (POR). The PRST pin is the main PCI hardware reset. This resets most of the PCI logic within the external PCI clock domain. This reset brings PCI-specific registers, sequencers, and signals to a consistent state. The POR pin is one of the main device hardware reset pins. This reset affects the entire device, not just the PCI module.

The internal reset is controlled by the power and sleep controller (PSC). The PSC asserts the internal reset of the PCI module after a device-level global reset or when the DSP code programs the PSC to do so. A device-level global reset is generated through the power-on reset pin (POR) or the warm reset pin (RESET); however, there are other methods to generate a device-level global reset. See Table 3 for these methods and use conditions for different reset sources when using the PCI on the device.

Figure 3. Internal and External Reset Inputs of the PCI Module

| Reset Name                                  | Description                                                                                                                                                                                                                                                                  |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power on Reset through PORz Pin             | <ul> <li>Entire chip is reset during a power-on reset</li> <li>The external reset on the PCI is asserted internally and the PSC asserts the internal PCI reset until programmed</li> </ul>                                                                                   |

| Warm reset generated through RESET<br>Pin   | <ul><li>Entire chip minus on-chip emulation logic is reset</li><li>The PSC asserts the internal PCI reset until programmed</li></ul>                                                                                                                                         |

| System Reset generated through PRSTz<br>Pin | <ul> <li>Entire chip minus on-chip emulation logic is reset</li> <li>The PSC asserts the internal PCI reset until programmed</li> <li>The PSC should be programmed to only de-assert the internal PCI reset after the external PCI reset PRSTz has been asserted.</li> </ul> |

| Reset Name | Description                                                                                                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSC Reset  | <ul> <li>DSP code configures the PSC of the PCI to assert the internal PCI reset.</li> <li>The PSC of the PCI should not be used to place the PCI in reset after it has taken the PCI out of reset.</li> </ul> |

#### Table 3. Device-Level Global Reset Sources When Using the PCI Module (continued)

#### 2.8.2 PCI Register Reset Values

Some of the PCI memory-mapped registers (Section 5.2) are connected to configuration hook registers. See Table 9 for the list of configuration hook registers supported. The values in these configuration hook registers are latched to the actual PCI registers on PCI reset. The default values in these configuration hook registers can be overwritten by software. These registers are implemented mainly to support PCI I2C EEPROM auto-initialization, as discussed in Section 2.12.3.

#### 2.9 Interrupt Support

The PCI can generate an interrupt for the status conditions listed in Table 4. When a status condition is set, the PCI can raise an interrupt to the DSP or PCI host or both based on what interrupts have been enabled for host and DSP. See Section 2.9.1 and Section 2.9.2 for enabling interrupts to host and DSP for a particular set of status conditions.

| Interrupt Name | Description                                                                                                                                              |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parity Error   | A parity error is detected when the PCI is the master during a read transaction and when the PCI is a slave during a write transaction.                  |

| System Error   | A system error is detected when the PCI has received a target abort while mastering the bus, or when an address parity error is detected on the PCI bus. |

| Master Abort   | Generated when the PCI is a master to indicate that it terminated a master transaction with a master abort.                                              |

| Target Abort   | Generated when the PCI is a slave to indicate it has initiated a target abort.                                                                           |

#### **Table 4. PCI Interrupts**

#### 2.9.1 DSP-to-Host Interrupts

The PCI can raise an interrupt to an external host for various status conditions, as described in Table 4. The PCI includes an internal host interrupt enable register that specifies which status conditions will generate interrupts to a host. The PCI host interrupt enable register is not directly accessible by a host or the DSP. Two registers are provided to set or clear bits in the internal host interrupt enable register: the host interrupt enable set register (PCIHINTSET) and the host interrupt enable clear register (PCIHINTCLR).

An interrupt for a particular status condition can be enabled by setting the corresponding bit in PCIHINTSET. Interrupt generation through the PINTA pin is enabled by default when PCI is in D0 power state. Reading PCIHINTSET returns the contents of the internal host interrupt enable register.

An interrupt for a particular status condition can be disabled by setting the corresponding bit in PCIHINTCLR. Reading PCIHINTCLR returns the bitwise ANDing of the internal status register and the internal host interrupt enable register. PCIHINTCLR is typically read by the host to determine the source of an interrupt when PINTA is asserted.

A level-sensitive active-low interrupt is generated to an external host on PINTA if a bit in the internal status register is asserted and the corresponding bit in the internal host interrupt enable register is also asserted. When an interrupt is raised on PINTA, a host can read PCIHINTCLR to determine the status condition that caused the interrupt. The host can indirectly access PCIHINTCLR through the base address registers.

Software can also use the SOFT\_INT bits to interrupt a host via PINTA. Software interrupts are enabled and disabled by writing to the host interrupt enable register. Setting the corresponding bit in the internal status register will assert a level sensitive active low interrupt on PINTA. The DSP or a host can clear this interrupt condition by clearing applicable bit in the internal status register.

#### 2.9.2 Host-to-DSP Interrupts

The PCI can raise an interrupt to the DSP for various status conditions described in Table 4. The PCI includes an internal DSP interrupt enable register that specifies which status conditions will generate interrupts to the DSP. The DSP interrupt enable register is not directly accessible by an external host or the DSP. Two registers are provided to set or clear bits in the internal DSP interrupt enable register: the DSP interrupt enable set register (PCIDINTSET) and the DSP interrupt enable clear register (PCIDINTCLR).

An interrupt for a particular status condition can be enabled by setting the corresponding bit in PCIDINTSET. Reading PCIDINTSET returns the contents of the internal DSP interrupt enable register.

An interrupt for a particular status condition can be disabled by setting the corresponding bit in PCIDINTCLR. Reading PCIDINTCLR returns the bitwise ANDing of the internal PCI status register and the internal DSP interrupt enable register. PCIDINTCLR is typically read by the DSP to determine the source of an interrupt.

An interrupt request is generated to the DSP if a bit in the internal status register (PCISTATSET) is asserted and the corresponding bit in the internal DSP interrupt enable register (PCIDINTSET) is also asserted. When an interrupt is raised to the DSP, the DSP can read PCIDINTCLR to know the status condition that caused the interrupt.

The interrupt request to the DSP is generated through the CPU PCI interrupt (PCIINT). This interrupt can also be forced by setting the SOFT\_INT bits in the status set register (PCISTATSET).

#### 2.9.3 Interrupt Multiplexing

The PCI has a single interrupt source (PCIINT) to the DSP CPU. This interrupt source is not multiplexed with any other interrupt on the CPU.

#### 2.10 DMA Event Support

The PCI module does not generate any EDMA events.

#### 2.11 Emulation Considerations

The PCI is not directly affected by emulation accesses. However, please note that other resources which the PCI has access to can be affected by emulation accesses.

#### 2.12 PCI Configuration

The operation of PCI is configured through the PCI configuration registers and memory-mapped registers.

#### 2.12.1 Programming the PCI Configuration Registers

The PCI configuration registers can be programmed by an external host and the DSP. Normally, a host programs a part of configuration registers and DSP programs the remaining part.

A host can control modes and options in PCI by programming the configuration registers. For example, a host can program the command/status register (PCICSR) to enable PCI bus master capability and to enable the memory access to DSP. It can program the base address registers (PCIBAR0 to PCIBAR5) to map the DSP memory regions into the PCI address space.

The DSP needs to program a set of configuration registers before the PCI host system software scans the PCI, as part of enumerating the PCI devices. For example, it needs to program the vendor ID/device ID register (PCIVENDEV) and the class code/revision ID register (PCICLREV) so that the PCI host system software can identify the device and load the respective host driver if required. This can be done automatically using the I2C EEPROM auto-initialization method, as described in Section 2.12.3.

A host can access the configuration registers by performing a TYPE 0 access in the PCI bus. The DSP cannot access the configuration registers directly. To facilitate access to the configuration registers, mirror registers are defined in the PCI memory-mapped register space. Updating the mirror registers updates the corresponding configuration registers.

# 2.12.2 Programming the PCI Memory-Mapped Registers

The memory-mapped registers include configuration mirror registers, master and slave address translation registers, and other miscellaneous control registers. Memory-mapped registers can be programmed by an external host and the DSP.

A host can access the memory-mapped registers through the slave interface supported by the PCI, provided the DSP has mapped those registers to the PCI memory space through the slave window base address registers. The DSP may directly program the configuration mirror registers, slave and master address translation registers, and other miscellaneous configuration registers.

# 2.12.3 PCI I2C EEPROM Auto-Initialization

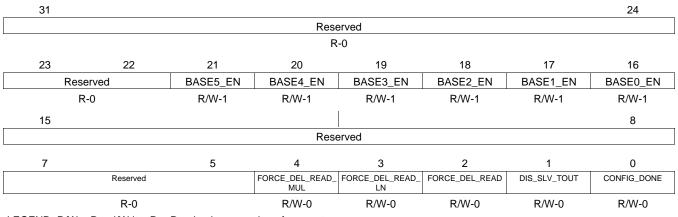

The PCI can be configured using the default values in the PCI Module registers or a select set of registers may be programmed via an EEPROM. The device treats any PCI boot as an internal ROM boot. The device has two separate boot modes to distinguish if it's a PCI boot with or without auto-initialization—i.e. if the PCI defaults need to be modified. If PCI Boot Mode With Auto-Initialization is selected (BOOTMODE[3:0] = 0010,PCI I2C EEPROM Auto-Initialization), the boot-loader software will copy some PCI parameters from an I2C ROM, and store them in the PCI Wrapper MMRs. The values from these PCI Wrapper MMRs will be latched by PCI as defaults to the PCI's MMRs at PCI reset de-assertion (pc\_rst\_i\_n). Meanwhile, because CONFIG\_DONE=0 (indicating Configuration Registers can be being loaded), PCI interface does not accept accesses. Once the initialization is complete, the sw will pulse the CONFIG\_DONE bit in the PCI Wrapper allowing PCI interface to accept accesses.

This will be the boot-loader software sequence to accommodate the above PCI peripheral requirements:

- Take the PCI out of reset through PSC- CONFIG\_DONE should be 0 at this point.

- If it's PCI boot without auto-initialization, skip this step.

- If it's PCI boot with auto-initialization

- Initialize both the PCI back end registers and PCI Wrapper registers

- Enable the I2C through PSC

- Read the default values from I2C

- Set CONFIG\_DONE=1 so that PCI interface can accept accesses

If auto-initialization is not enabled, the PCI configuration registers are left with their default values and the I2C EEPROM is not accessed for PCI configuration purposes. The values in the PCI Wrapper registers will not get latched into the PCI back end registers until the next time the host resets the PCI peripheral through the PRSTn pin (which may not occur until much later in operation). This is not an issue because the boot-loader is initializing both the PCI Wrapper registers and the PCI Back End Registers directly. As far as the external host is concerned, it doesn't know when the boot-loader is done. The external host may begin transaction as soon as it is out of reset (or it may also check RESETOUTn to see that the device is internally released from reset). During a PCI transaction, after the PCI arbiter grants access of the bus to the host, they host will assert FRAME and IRDY and wait for the device to assert PTRDY and DEVSEL to continue the transfer. If the boot-loader hasn't set CONFIG\_DONE=1, the device doesn't give PTRDY and DEVSEL. As a result the host will restart the transfer. As soon as the boot-loader is done (CONFIG\_DONE=1), the host will eventually get PTRDY. Table 5 lists the default values for some of the PCI configuration registers. These default values can be changed by enabling PCI I2C EEPROM auto-initialization.

| PCI Configuration Register | Default Value |

|----------------------------|---------------|

| Vendor ID                  | 104Ch         |

| Device ID                  | B003h         |

| Revision ID                | 01h           |

| Class Code                 | 11 8000h      |

| Subsystem Vendor ID        | 0000h         |

| Subsystem ID               | 0000h         |

| Interrupt Pin              | 00h           |

| Interrupt Line             | 00h           |

| Minimum Grant              | 00h           |

| Maximum Latency            | 00h           |

#### 2.12.3.1 PCI Auto-Initialization from I2C EEPROM

When auto-initialization is used, the PCI configuration registers are programmed by the on-chip ROM Boot Loader (RBL) with the values stored in an I2C EEPROM.

PCI I2C EEPROM auto-initialization is enabled when BOOTMODE[3:0] = 0010b, PCIEN = 1, and FASTBOOT = 1. If auto-initialization is not enabled, the PCI configuration registers are left with their default values and the I2C EEPROM is not accessed for PCI configuration purposes. The function of the BOOTMODE[3:0], PCIEN, and FASTBOOT pins is fully described in the device data manual, refer to that document for more details.

When auto-initialization is enabled, the CONFIG\_DONE bit in the configuration done register (PCICFGDONE) takes a default value of 0. This prevents the PCI from responding to any requests. When auto-initialization is completed, the RBL sets the CONFIG\_DONE bit to 1 to allow the PCI to respond to requests.

#### 2.12.3.2 I2C EEPROM Memory Map

The on-chip ROM Boot Loader requires big-endian format for the data stored in the I2C EEPROM. Byte addresses 400h through 41Bh of the I2C EEPROM are reserved for auto-initialization of PCI configuration registers. The remaining locations are not used for auto-initialization and can be used for storing other data. Table 6 summarizes the I2C EEPROM memory layout, as required for PCI auto-initialization.

| Byte Address | Contents                   |

|--------------|----------------------------|

| 400h         | Vendor ID [15:8]           |

| 401h         | Vendor ID [7:0]            |

| 402h         | Device ID [15:8]           |

| 403h         | Device ID [7:0]            |

| 404h         | Class code [7:0]           |

| 405h         | Revision ID [7:0]          |

| 406h         | Class code [23:16]         |

| 407h         | Class code [15:8]          |

| 408h         | Subsystem vendor ID [15:8] |

| 409h         | Subsystem vendor ID [7:0]  |

| 40Ah         | Subsystem ID [15:8]        |

| 40Bh         | Subsystem ID [7:0]         |

| 40Ch         | Max_Latency                |

| 40Dh         | Min_Grant                  |

#### Table 6. I2C EEPROM Memory Layout

| Byte Address | Contents           |

|--------------|--------------------|

| 40Eh-418h    | Reserved (use 00h) |

| 419h         | Checksum [15:8]    |

| 41Ah         | Checksum [7:0]     |

#### Table 6. I2C EEPROM Memory Layout (continued)

#### 2.12.3.3 I2C EEPROM Checksum

The PCI configuration data contained in the I2C EEPROM is checked against a checksum. The configuration data bytes are treated as an array of 16-bit words (little-endian format). The checksum is a 16-bit cumulative exclusive-OR (XOR) of the configuration data words, starting with an initial value of AAAAh. You must ensure that the proper 16-bit checksum value is written to address 419h and 41Ah when programming the I2C EEPROM.

Checksum = AAAAh XOR Word0(401h:400h) XOR Word1(403h:402)... XOR Word12(418h:417h)

If the I2C EEPROM is not accessed for PCI configuration purposes (that is, PCI\_EEAI = 0 at reset), then the checksum is not performed. If the checksum fails, the on-chip ROM bootloader defaults to the UART boot and it does not set the CONFIG\_DONE bit in the configuration done register (PCICFGDONE).

#### 2.12.3.4 DSP I2C EEPROM Interface

For PCI auto-initialization, the DSP supports I2C EEPROMs or devices operating as I2C slaves with the following features:

- The memory device complies with Philips I2C Bus Specification v 2.1

- The memory device uses two bytes for internal addressing; that is, the read/write bit followed by two bytes for addressing

- The memory device has the capability to auto-increment its internal address counter such that the contents of the memory device can be read sequentially

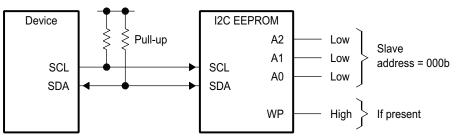

During PCI auto-initialization, the DSP acts as the master and the I2C EEPROM acts as the slave. Figure 4 shows the minimum connection required between the DSP and one I2C EEPROM. The required pull-ups must be placed on SDA and SCL to ensure that the I2C EEPROM interface works correctly. The slave address of the I2C EEPROM slave address must be set to 50h.

#### Figure 4. Signal Connections for I2C EEPROM Boot Mode

Some I2C EEPROMs have a write-protect (WP) feature that prevents unauthorized writes to memory. This feature is not needed for auto-initialization because the DSP will only read data from the I2C EEPROM. The write protect feature can be enabled or disabled.

For PCI auto-initialization purposes only byte address 400-401h are used. The remaining locations in the I2C EEPROM can be used for other purposes.

For detailed information on the I2C, see the Inter-Integrated Circuit (I2C) Module User's Guide.

#### 2.13 Connecting a Local PCI to an External PCI Device

Figure 5 shows a simplified block diagram of how the PCI module interfaces local DSP master modules (EDMA controller, CPU, etc.) and other DSP resources (DDR2 memory controller, DSP internal memory, etc.) to external PCI memory and external PCI masters.

#### Figure 5. PCI to External PCI Device

EDMA: Enhanced Direct Memory Access Controller EMC: Extended Memory Controller L1P MC: L1 P Memory Controller L1D MC: L1D Memory Controller L2 MC: L1 Memory Controller IDMA: Internal Direct Memory Access Controller The following steps show how the PCI module interfaces local DSP master modules (EDMA controller, CPU, etc.) to external PCI memory:

- 1. A DSP master initiates a transaction aimed at external PCI memory through the DSP switched central resource.

- 2. The address is decoded by the DSP master interface.

- 3. The DSP master interface claims the transaction if the DSP address falls within the master memory map (described in Section 4.1).

- 4. DSP master interface translates the DSP address into a PCI address and generates a request to the master state machine.

- 5. The master state machine initiates a transaction on the PCI bus using the PCI address.

- 6. The request is received by the external PCI host, which responds accordingly.

The following steps show how the PCI module interfaces external PCI masters to DSP resources (DDR2 memory controller, DSP internal memory, etc.):

- 1. External PCI master initiates a transaction on the PCI bus.

- 2. The address decoder decodes the PCI address of the transaction and instructs the PCI slave state machine to claim the transaction if the PCI address falls within the slave memory map (described in Section 3.1) assigned to the DSP.

- 3. The slave state machine forwards the request to the DSP slave interface.

- 4. The DSP slave interface translates the PCI address into a DSP address and places the DSP address on the DSP switched central resource.

- 5. All DSP slaves decode the address to determine if they are being accessed. If so, they respond accordingly. For example, in the case of an external memory access, the DDR2 memory controller accesses external memory using the DSP address.

#### 3 PCI Slave Operation

The PCI slave operates in response to transfer requests that are presented on the PCI bus. The PCI slave was intended to enable high performance read and write performance through the use of delayed transactions combined with prefetching for reads and posting for writes. The PCI slave supports two FIFOs/buffers (a read and write) for efficient data transfer. Each buffer holds 16 32-bit words of read or write data.

# 3.1 Slave Memory Map

The PCI module provides full visibility for an external host into DSP memory through six sets of PCI slave base address translation registers (PCIBAR0TRL, PCIBAR1TRL, PCIBAR2TRL, PCIBAR3TRL, PCIBAR4TRL, and PCIBAR5TRL) and PCI base address mask registers (PCIBAR0MSK, PCIBAR1MSK, PCIBAR2MSK, PCIBAR3MSK, PCIBAR4MSK, and PCIBAR5MSK). The DSP can use any of these sets of registers to map any DSP memory region to the PCI memory map. These registers can be configured by software at any time. The default values of these registers provide the mapping shown in Table 7.

Section 3.2 and Section 3.3 explain how to map a region in the PCI host address space to a region in the DSP memory space by setting up a slave window.

| Base Address | Window Size | Prefetchable | Memory Space            |

|--------------|-------------|--------------|-------------------------|

| 0            | 8MB         | Yes          | L2 RAM memory space     |

| 1            | 4MB         | No           | GEM MMRs                |

| 2            | 4MB         | No           | Chip-level MMRs         |

| 3            | 8MB         | Yes          | EMIF3B CE2 memory space |

| 4            | 8MB         | Yes          | EMIF3B CE3 memory space |

| 5            | 8MB         | Yes          | DDR2 CE0 memory space   |

Table 7. PCI Base Addresses

# 3.2 Configuring Slave Window Registers

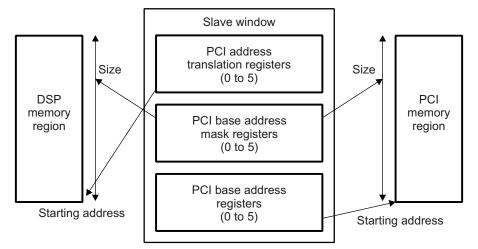

A slave window maps a region in the DSP memory space to a region in the PCI address space. This allows a PCI host to access the DSP memory through the PCI address space. A slave window is configured with the following registers:

- PCI slave base address translation register: Configures the starting address of the window in the DSP address space.

- PCI base address register: Configures the starting address of the slave window in the PCI address space.

- PCI base address mask register: Configures the size of the window and prefetchability of the DSP memory region being mapped.

PCI supports six slave window configurations with the support of these registers. For more information on slave access address translation, see Section 3.3. A slave window configuration is shown in Figure 6.

#### Figure 6. Slave Window Configuration

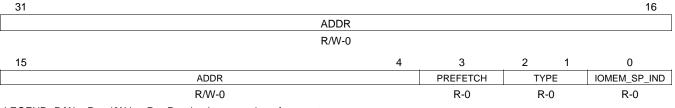

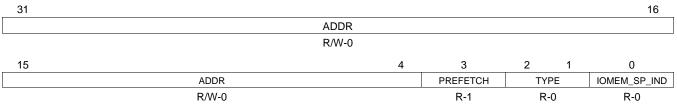

#### 3.2.1 Configuration of Base Address Registers 0 to 5 (PCIBARn) by PCI Host

The base address registers (PCIBAR*n*) allow an external host to map the DSP's address space into the host memory or I/O address space.

The base address registers reside in PCI configuration space and a host normally configures them. A host can access base address registers 0 to 5 (PCIBAR0, PCIBAR1, PCIBAR2, PCIBAR3, PCIBAR4 and PCIBAR5) by performing a TYPE 0 access in the PCI bus.

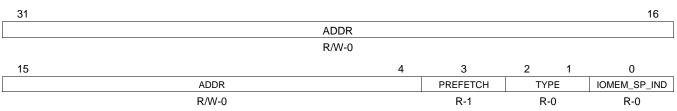

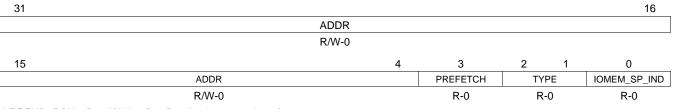

The base address registers contain the following bit fields:

- ADDR (31-4): These bits specify the base address of the slave window on the PCI address space.

- PREFETCH (3): This bit specifies the prefetchablity of the memory space controlled by the base address register.

- TYPE (2-1): These bits specify whether the base address maps to PCI I/O address space or memory address space. The device supports only mapping into PCI memory space.

- IOMEM\_SP\_IND (0): The size of the base address register, either 32 or 64 bits. The device only supports 32-bit addressing.

Normally, a host configures the ADDR bits of the base address registers during its boot time when it enumerates all the PCI devices. The write-access of a host to each of the ADDR bits is determined by the corresponding bit in the address mask (ADDRMASK) bits of the base address mask registers (PCIBAR*n*MSK). A bit in ADDR is read-only to a host when its corresponding bit in ADDRMASK is cleared. Conversely, a bit in ADDR can be both read and written by a host when its corresponding bit in ADDRMASK is set. The DSP is required to complete the configuration of the base address mask registers before the host attempts to configure the base address registers.

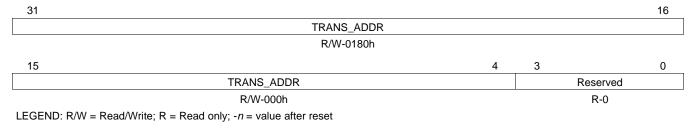

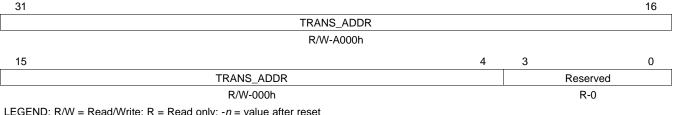

#### 3.2.2 Configuration of Slave Base Address Translation Registers 0 to 5 (PCIBARnTRL) by DSP

A slave base address translation register (PCIBAR*n*TRL) configures the DSP side parameters of a slave window. There are six slave base address translation registers (PCIBAR0TRL, PCIBAR1TRL, PCIBAR2TRL, PCIBAR3TRL, PCIBAR4TRL, and PCIBAR5TRL) that allow six slave windows to be set up. The slave base address translation registers are usually configured by the DSP; however, they can also be programmed by an external host. PCI slave base address translation registers control the translation of transaction addresses as they flow from the external PCI bus to the DSP. Section 3.3 explains the translation of PCI addresses to DSP addresses.

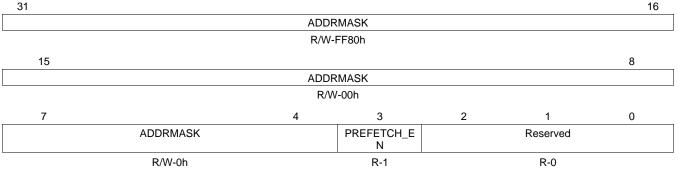

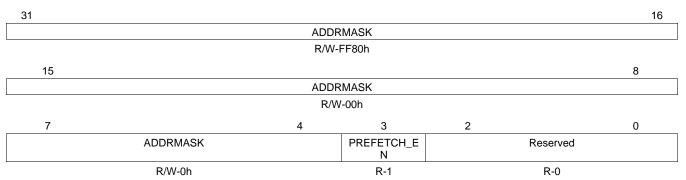

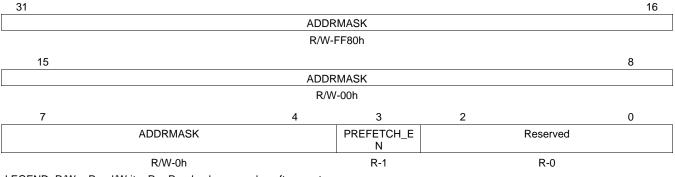

#### 3.2.3 Configuration of Base Address Mask Registers 0 to 5 (PCIBAR nMSK) by DSP

A base address mask register (PCIBAR*n*MSK) configures the size and prefetchablity of a slave window. There are six slave base address translation registers (PCIBAR0MSK, PCIBAR1MSK, PCIBAR2MSK, PCIBAR3MSK, PCIBAR4MSK, and PCIBAR5MSK) available in the PCI to support six slave windows. The base address mask registers are usually configured by the DSP, however they can also be programmed by an external host. The DSP can access the base address mask registers directly, as they are mapped to the DSP memory space.

The base address mask registers contain the following bit fields:

- ADDRMASK: These bits control the PCI host write access of the corresponding bits in the PCI configuration base address registers (0 to 5).

- PREFETCH\_EN: This bit specifies whether or not the memory space controlled by the corresponding configuration base address register is prefetchable. This bit is reflected in bit 3 of the corresponding configuration base address register.

The DSP is required to complete the configuration of the base address mask registers before the host attempts to configure the base address registers.

#### 3.3 Slave Access Address Translations

Window configurations control the translation of transaction addresses as they flow from the external PCI bus to the DSP. This translation process uses the contents of the corresponding base address mask register (PCIBAR0MSK, PCIBAR1MSK, PCIBAR2MSK, PCIBAR3MSK, PCIBAR4MSK, and PCIBAR5MSK) to determine which of the bits in the PCI address should be modified. Bits 31-4 (ADDRMASK) are replaced in the address where the corresponding bit in the base address mask register is set by the corresponding bit in the slave base address translation register (PCIBAR*n*TRL).

The following steps occur during a PCI-to-DSP address translation:

- 1. During the address phase, an external PCI master places the PCI address on the address bus AD[31-0].

- 2. The PCI finds the appropriate slave window for the address by comparing the address bits given on AD[31-n] with the corresponding bits in the base address register of all the slave windows one by one. The value of n is the number of bits set in the corresponding base address mask register of the slave window. The minimum value of n is 4. The value of n indicates the number of significant bits in the PCI address that needs to be decoded. If the address on AD[31-n] matches the corresponding bits of the base address register of any one of the slave windows, the PCI claims the PCI transaction. Otherwise, it ignores the transaction.

- 3. If the PCI claims the transaction, it generates a DSP address by replacing bits 31-*n* in the PCI address with the corresponding bits in the base address translation register of the previously selected slave window.

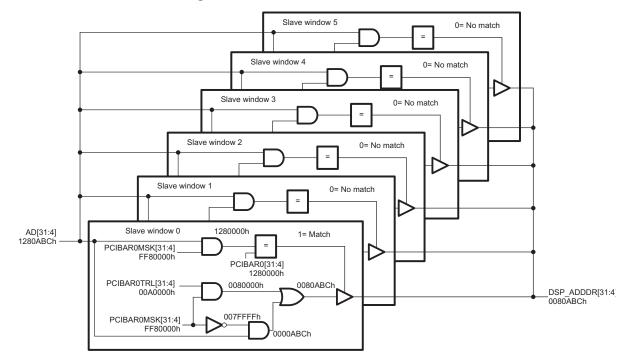

Figure 7 gives an example of a PCI-to-DSP address translation using a PCI address of 1280 ABC0h. In this example, slave window 0 is created using this configuration:

PCIBAR0 = 1280 0000h, PCIBAR0MSK = FF80 0008h, and PCIBAR0TRL = 00A00 000h.

With these settings, slave window 0 translates PCI addresses from 1280 0000h to 12FF FFFFh (8 MB) to DSP addresses 0080 0000h to 00FF FFFFh. The following is the sequence of events for generating the DSP address:

- 1. The external PCI master places the PCI address 1280 ABC0h on the address bus AD[31-0].

- 2. The PCI finds the slave window corresponding to the PCI address by comparing the address given on AD[31-4], 128 0ABCh, with the corresponding bits in the PCI base address registers. The PCI base address mask registers indicate bits in the PCI address that need to be compared.

- 3. Slave window 0 has PCIBAR0[31-4] set to 128 0000h and PCIBAR0MSK[31-4] = FF8 0000h. Therefore, the PCI matches the PCI address with slave window 0 and claims transaction.

- 4. The value of the PCIBAR0MSK[31-4] bits is inverted and ANDed with the PCI address AD[31-4]. The PCIBAR0TRL[31-4] bits are also ANDed with the value of the PCIBAR0MSK[31-4] bits. The resulting values are ORed to form the DSP address (0080 ABCh).

#### Figure 7. PCI-to-DSP Address Translation

# 3.4 Slave Configuration Operations

#### 3.4.1 Configuration Write Transactions

The decoding of and response to a configuration write transaction by the PCI depends on the following:

- PCBE[3-0] must be Bh during the address phase.

- PIDSEL must be asserted during the address phase.

- AD[1-0] must be 00b during the address phase.