## TMS320DM646x DMSoC Transport Stream Interface (TSIF) Module

# **User's Guide**

Literature Number: SPRUEQ2E July 2008

## Contents

| Pref | ace     |                                                                           | 8  |

|------|---------|---------------------------------------------------------------------------|----|

| 1    | Introdu | iction                                                                    | 9  |

|      | 1.1     | Purpose of the Peripheral                                                 | 9  |

|      | 1.2     | Features                                                                  | 9  |

|      | 1.3     | Functional Block Diagram                                                  | 10 |

|      | 1.4     | Terminology Used in This Document                                         | 10 |

| 2    | Archite | ecture                                                                    | 11 |

|      | 2.1     | Clock Control                                                             | 11 |

|      | 2.2     | Signal Descriptions                                                       | 11 |

|      | 2.3     | Pin Multiplexing                                                          | 11 |

|      | 2.4     | General Architecture                                                      | 12 |

|      | 2.5     | Hardware Reset Considerations                                             | 22 |

|      | 2.6     | Interrupt Support                                                         | 22 |

|      | 2.7     | Emulation Suspend Mode                                                    | 22 |

| 3    | Use Ca  | ISES                                                                      | 23 |

|      | 3.1     | Input and Output Interface Structure                                      | 23 |

|      | 3.2     | Packet Data Configuration                                                 | 26 |

|      | 3.3     | Transfer/Receiver Interface Configuration                                 | 26 |

|      | 3.4     | PID Control                                                               | 26 |

|      | 3.5     | Ring Buffer Control                                                       | 33 |

| 4    | Registe | ers                                                                       | 35 |

|      | 4.1     | TSIF Peripheral Identification Register (PID)                             |    |

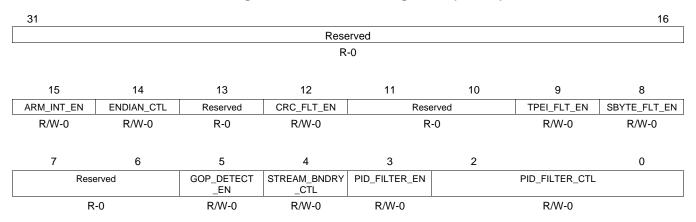

|      | 4.2     | TSIF Control Register 0 (CTRL0)                                           |    |

|      | 4.3     | TSIF Control Register 1 (CTRL1)                                           | 41 |

|      | 4.4     | TSIF Interrupt Enable Register (INTEN)                                    | 43 |

|      | 4.5     | TSIF Interrupt Enable Set Register (INTEN_SET)                            |    |

|      | 4.6     | TSIF Interrupt Enable Clear Register (INTEN_CLR)                          | 47 |

|      | 4.7     | TSIF Interrupt Status Register (INTSTAT)                                  |    |

|      | 4.8     | TSIF Interrupt Status Clear Register (INTSTAT_CLR)                        |    |

|      | 4.9     | TSIF Emulation Control Register (EMU_CTRL)                                |    |

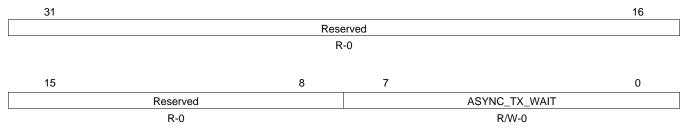

|      | 4.10    | Asynchronous Transmit Wait Register (ASYNC_TX_WAIT)                       |    |

|      | 4.11    | PAT Sense Configuration Register (PAT_SEN_CFG)                            | 56 |

|      | 4.12    | 5 ( ,                                                                     | 56 |

|      | 4.13    | PMT Sense Configuration Register (PMT_SEN_CFG)                            |    |

|      | 4.14    | PMT Store Address Register (PMT_STR_ADDR)                                 |    |

|      | 4.15    | BSP Input Register (BSP_IN)                                               |    |

|      | 4.16    | BSP Input Store Address Register (BSP_STORE_ADDR)                         |    |

|      | 4.17    | PCR Sense Configuration Register (PCR_SENSE_CFG)                          |    |

|      | 4.18    | PID <i>n</i> Filter Configuration Registers (PID0_FILT_CFG-PID6_FILT_CFG) |    |

|      | 4.19    | Bypass Mode Configuration Register (BYPASS_CFG)                           |    |

|      | 4.20    | Transmit ATS Initialization Register (TX_ATS_INIT)                        | 63 |

| 4.21       | Transmit ATS Monitor Register (TX_ATS_MON)                                                 | 64 |

|------------|--------------------------------------------------------------------------------------------|----|

| 4.22       | Receive Packet Status (RX_PKT_STAT)                                                        | 65 |

| 4.23       | STC Initialization Control Register (STC_INIT_CTRL)                                        | 66 |

| 4.24       | STC Initialization Value Register (STC_INIT_VAL)                                           | 66 |

| 4.25       | STC Interrupt Entry <i>n</i> Registers (STC_INT0-STC_INT7)                                 | 67 |

| 4.26       | Write Ring Buffer Channel Control Register (WRB_CTRL)                                      | 67 |

| 4.27       | Write Ring Buffer Channel <i>n</i> Start Address Registers (WRB0_STRT_ADDR-WRB7_STRT_ADDR) | 69 |

| 4.28       | Write Ring Buffer Channel <i>n</i> End Address Registers (WRB0_END_ADDR-WRB7_END_ADDR)     | 69 |

| 4.29       | Write Ring Buffer Channel <i>n</i> Read Pointer Registers (WRB0_RDPTR-WRB7_RDPTR)          | 70 |

| 4.30       | Write Ring Buffer Channel <i>n</i> Subtraction Registers (WRB0_SUB-WRB7_SUB)               | 70 |

| 4.31       | Write Ring Buffer Channel <i>n</i> Write Pointer Registers (WRB0_WRPTR-WRB7_WRPTR)         | 71 |

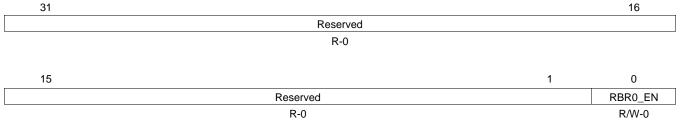

| 4.32       | Read Ring Buffer Channel Control Register (RRB_CTRL)                                       | 71 |

| 4.33       | Read Ring Buffer Channel Start Address Register (RRB_STRT_ADDR)                            | 72 |

| 4.34       | Read Ring Buffer Channel End Address Register (RRB_END_ADDR)                               | 72 |

| 4.35       | Read Ring Buffer Channel Write Pointer Register (RRB_WRPTR)                                | 73 |

| 4.36       | Read Ring Buffer Channel Subtraction Register (RRB_SUB)                                    | 73 |

| 4.37       | Read Ring Buffer Channel Read Pointer Register (RRB_RDPTR)                                 | 74 |

| 4.38       | Packet Counter Value Register (PKT_CNT)                                                    | 74 |

| Appendix A | Revision History                                                                           | 75 |

|            |                                                                                            |    |

### List of Figures

| 1  | TSIF Block Diagram                                                                  |    |

|----|-------------------------------------------------------------------------------------|----|

| 2  | Seamless Trans-Coding on Plural Programs                                            | 13 |

| 3  | Logical Format of Boundary Sensing Packet                                           | 14 |

| 4  | ATS Control with Receive Case                                                       | 16 |

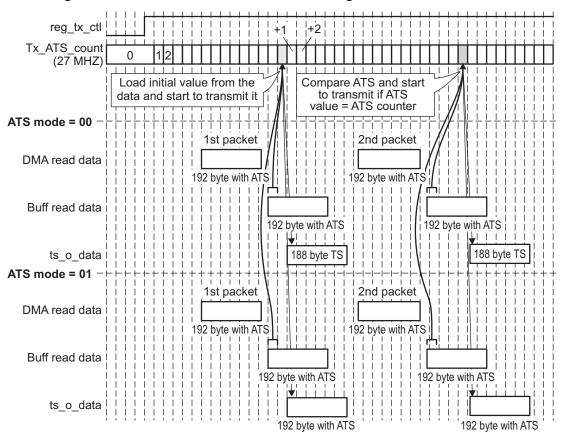

| 5  | ATS Control with Transfer Case using Packet Data Initial Value                      | 17 |

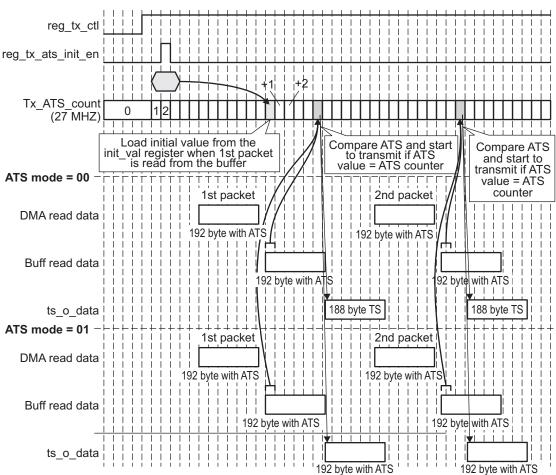

| 6  | ATS Control with Transfer Case using Module Initial Value                           |    |

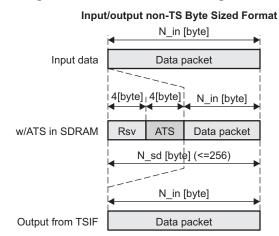

| 7  | Variable Packet Sizing in non-TS Mode                                               | 19 |

| 8  | Data Storage Format of 32-Bit Little-Endian Mode on SDRAM                           | 20 |

| 9  | Data Storage Format of 64-Bit Big-Endian Mode on SDRAM                              | 21 |

| 10 | Bit-Level Endian Format in SDRAM Format                                             | 21 |

| 11 | Serial Interface Format in Synchronous Mode                                         | 23 |

| 12 | Serial Interface Input Format in Asynchronous Mode                                  | 24 |

| 13 | Serial Interface Output Format in Asynchronous Mode                                 | 25 |

| 14 | Parallel Interface Format                                                           | 25 |

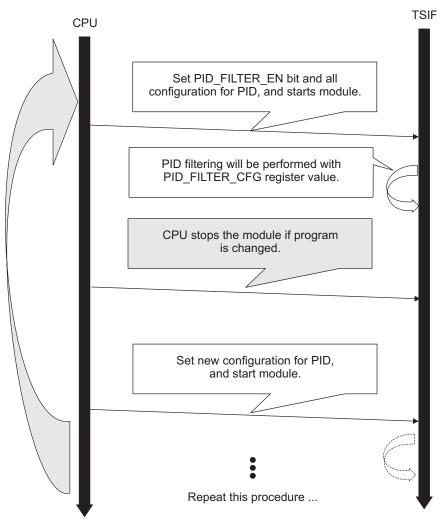

| 15 | Processing on Full Manual Mode of PID Filter                                        | 27 |

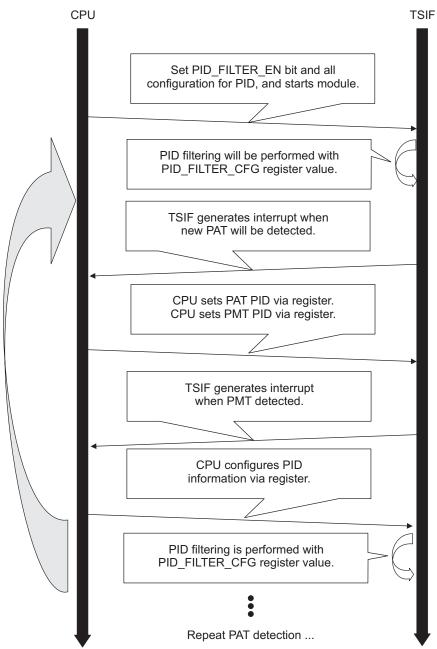

| 16 | Processing on Semi-Automatic Mode-A of PID Filter                                   | 29 |

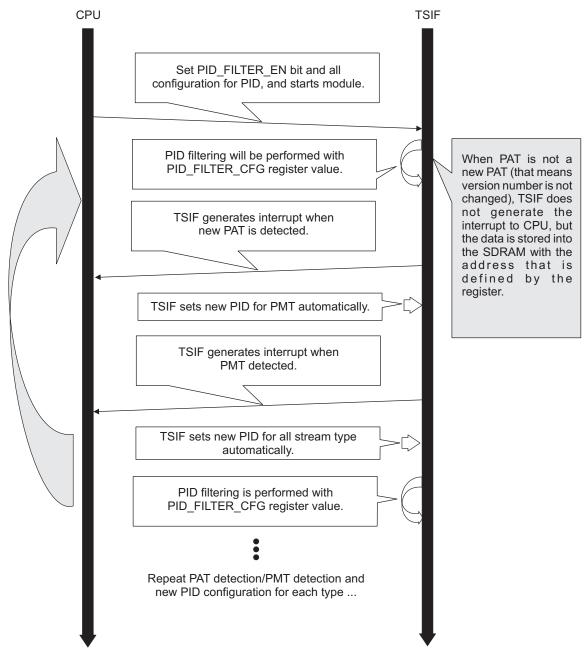

| 17 | Processing on Semi-Automatic Mode-B of PID Filter                                   | 31 |

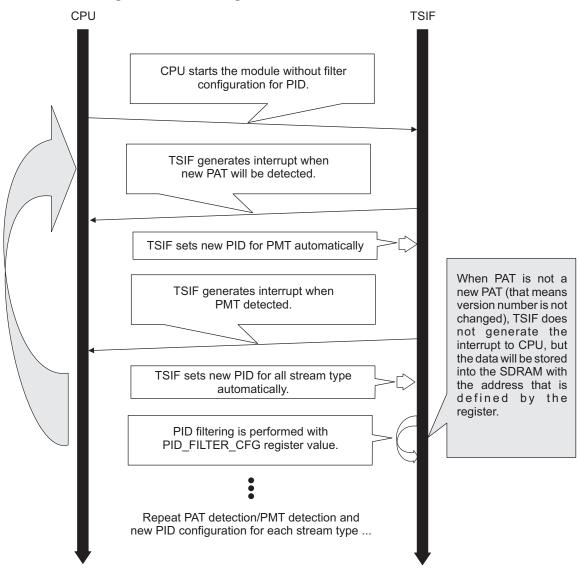

| 18 | Processing on Full Automatic Mode of PID Filter                                     | 33 |

| 19 | Ring Buffer Controller                                                              | 34 |

| 20 | TSIF Peripheral Identification Register (PID)                                       | 37 |

| 21 | TSIF Control Register 0 (CTRL0)                                                     | 38 |

| 22 | TSIF Control Register 1 (CTRL1)                                                     |    |

| 23 | TSIF Interrupt Enable Register (INTEN)                                              |    |

| 24 | TSIF Interrupt Enable Set Register (INTEN_SET)                                      |    |

| 25 | TSIF Interrupt Enable Clear Register (INTEN_CLR)                                    |    |

| 26 | TSIF Interrupt Status Register (INTSTAT)                                            |    |

| 27 | TSIF Interrupt Status Clear Register (INTSTAT_CLR)                                  |    |

| 28 | TSIF Emulation Control Register (EMU_CTRL)                                          |    |

| 29 | Asynchronous Transmit Wait Register (ASYNC_TX_WAIT)                                 |    |

| 30 | PAT Sense Configuration Register (PAT_SEN_CFG)                                      |    |

| 31 | PAT Store Address Register (PAT_STR_ADDR)                                           | 56 |

| 32 | PMT Sense Configuration Register (PMT_SEN_CFG)                                      | 57 |

| 33 | PMT Store Address Register (PMT_STR_ADDR)                                           |    |

| 34 | Boundary Sensing Packet Input Register (BSP_IN)                                     |    |

| 35 | Boundary Sensing Packet Input Store Address Register (BSP_STORE_ADDR)               |    |

| 36 | PCR Sense Configuration Register (PCR_SENSE_CFG)                                    |    |

| 37 | PID <i>n</i> Filter Configuration Register (PID <i>n</i> _FILT_CFG)                 |    |

| 38 | Bypass Mode Configuration Register (BYPASS_CFG)                                     |    |

| 39 | Transmit ATS Initialization Register (TX_ATS_INIT)                                  |    |

| 40 | Transmit ATS Monitor Register (TX_ATS_MON)                                          |    |

| 41 | Receive Packet Status (RX_PKT_STAT)                                                 |    |

| 42 | STC Initialization Control Register (STC_INIT_CTRL)                                 |    |

| 43 | STC Initialization Value Register (STC_INIT_VAL).                                   |    |

| 44 | STC Interrupt Entry <i>n</i> Register (STC_INT_ENTRY_ <i>n</i> )                    |    |

| 45 | Write Ring Buffer Channel Control Register (WRB_CTRL)                               |    |

| 46 | Write Ring Buffer Channel <i>n</i> Start Address Register (WRB <i>n</i> _STRT_ADDR) |    |

| 47 | Write Ring Buffer Channel <i>n</i> End Address Register (WRB <i>n</i> _END_ADDR)    |    |

| 48 | Write Ring Buffer Channel <i>n</i> Read Pointer Register (WRB <i>n</i> _RDPTR)      |    |

| 49 | Write Ring Buffer Channel <i>n</i> Subtraction Register (WRB <i>n</i> _SUB)         |    |

| 50 | Write Ring Buffer Channel <i>n</i> Write Pointer Register (WRB <i>n</i> _WRPTR)     |    |

| 51 | Read Ring Buffer Channel Control Register (RRB_CTRL)                                |    |

| 52 | Read Ring Buffer Channel Start Address Register (RRB_STRT_ADDR)                     |    |

|    |                                                                                     |    |

| 53 | Read Ring Buffer Channel End Address Register (RRB_END_ADDR) | 72 |

|----|--------------------------------------------------------------|----|

| 54 | Read Ring Buffer Channel Write Pointer Register (RRB_WRPTR)  | 73 |

| 55 | Read Ring Buffer Channel Subtraction Register (RRB_SUB)      | 73 |

|    | Read Ring Buffer Channel Read Pointer Register (RRB_RDPTR)   |    |

|    | Packet Counter Value Register (PKT_CNT)                      |    |

|    | <b>o</b> ( <u> </u>                                          |    |

### List of Tables

| 1   | TSIF Signal Descriptions                                                                               | 11 |

|-----|--------------------------------------------------------------------------------------------------------|----|

| 2   | ATS Control with Receive Case                                                                          | 15 |

| 3   | TSIF Module Interrupts                                                                                 | 22 |

| 4   | Transport Stream Interface (TSIF) Module Registers                                                     | 35 |

| 5   | TSIF Peripheral Identification Register (PID) Field Descriptions                                       | 37 |

| 6   | TSIF Control Register 0 (CTRL0) Field Descriptions                                                     | 38 |

| 7   | TSIF Control Register 1 (CTRL1) Field Descriptions                                                     | 41 |

| 8   | TSIF Interrupt Enable Register (INTEN) Field Descriptions                                              | 43 |

| 9   | TSIF Interrupt Enable Set Register (INTEN_SET) Field Descriptions                                      | 45 |

| 10  | TSIF Interrupt Enable Clear Register (INTEN_CLR) Field Descriptions                                    | 48 |

| 11  | TSIF Interrupt Status Register (INTSTAT) Field Descriptions                                            | 50 |

| 12  | TSIF Interrupt Status Clear Register (INTSTAT_CLR) Field Descriptions                                  | 53 |

| 13  | TSIF Emulation Control Register (EMU_CTRL) Field Descriptions                                          | 55 |

| 14  | Asynchronous Transmit Wait Register (ASYNC_TX_WAIT) Field Descriptions                                 | 56 |

| 15  | PAT Sense Configuration Register (PAT_SEN_CFG) Field Descriptions                                      | 56 |

| 16  | PAT Store Address Register (PAT_STR_ADDR) Field Descriptions                                           | 57 |

| 17  | PMT Sense Configuration Register (PMT_SEN_CFG) Field Descriptions                                      | 57 |

| 18  | PMT Store Address Register (PMT_STR_ADDR) Field Descriptions                                           | 58 |

| 19  | Boundary Sensing Packet Input Register (BSP_IN) Field Descriptions                                     | 58 |

| 20  | Boundary Sensing Packet Input Store Address Register (BSP_STORE_ADDR) Field Descriptions               | 59 |

| 21  | PCR Sense Configuration Register (PCR_SENSE_CFG) Field Descriptions                                    | 60 |

| 22  | PID <i>n</i> Filter Configuration Register (PID <i>n</i> _FILT_CFG) Field Descriptions                 | 61 |

| 23  | Bypass Mode Configuration Register (BYPASS_CFG) Field Descriptions                                     | 62 |

| 24  | Transmit ATS Initialization Register (TX_ATS_INIT) Field Descriptions                                  | 63 |

| 25  | Transmit ATS Monitor Register (TX_ATS_MON) Field Descriptions                                          | 64 |

| 26  | Receive Packet Status (RX_PKT_STAT) Field Descriptions                                                 | 65 |

| 27  | STC Initialization Control Register (STC_INIT_CTRL) Field Descriptions                                 | 66 |

| 28  | STC Initialization Value Register (STC_INIT_VAL) Field Descriptions                                    | 66 |

| 29  | STC Interrupt Entry <i>n</i> Register (STC_INT_ENTRY_ <i>n</i> ) Field Descriptions                    | 67 |

| 30  | Write Ring Buffer Channel Control Register (WRB_CTRL) Field Descriptions                               | 67 |

| 31  | Write Ring Buffer Channel <i>n</i> Start Address Register (WRB <i>n</i> _STRT_ADDR) Field Descriptions | 69 |

| 32  | Write Ring Buffer Channel <i>n</i> End Address Register (WRB <i>n</i> _END_ADDR) Field Descriptions    | 69 |

| 33  | Write Ring Buffer Channel <i>n</i> Read Pointer Register (WRB <i>n</i> _RDPTR) Field Descriptions      | 70 |

| 34  | Write Ring Buffer Channel <i>n</i> Subtraction Register (WRB <i>n</i> _SUB) Field Descriptions         | 70 |

| 35  | Write Ring Buffer Channel <i>n</i> Write Pointer Register (WRB <i>n</i> _WRPTR) Field Descriptions     | 71 |

| 36  | Read Ring Buffer Channel Control Register (RRB_CTRL) Field Descriptions                                | 71 |

| 37  | Read Ring Buffer Channel Start Address Register (RRB_STRT_ADDR) Field Descriptions                     | 72 |

| 38  | Read Ring Buffer Channel End Address Register (RRB_END_ADDR) Field Descriptions                        | 72 |

| 39  | Read Ring Buffer Channel Write Pointer Register (RRB_WRPTR) Field Descriptions                         | 73 |

| 40  | Read Ring Buffer Channel Subtraction Register (RRB_SUB) Field Descriptions                             | 73 |

| 41  | Read Ring Buffer Channel Read Pointer Register (RRB_RDPTR) Field Descriptions                          |    |

| 42  | Packet Counter Value Register (PKT_CNT) Field Descriptions                                             |    |

| A-1 | Document Revision History                                                                              | 75 |

|     |                                                                                                        |    |

Preface SPRUEQ2E-July 2008

#### About This Manual

Describes the operation of the transport stream interface (TSIF) module in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320DM646x Digital Media System-on-Chip (DMSoC). Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the DM646x DMSoC, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <u>www.ti.com/c6000</u>.

<u>SPRUEP8</u> — *TMS320DM646x DMSoC DSP Subsystem Reference Guide.* Describes the digital signal processor (DSP) subsystem in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

- SPRUEP9 TMS320DM646x DMSoC ARM Subsystem Reference Guide. Describes the ARM subsystem in the TMS320DM646x Digital Media System-on-Chip (DMSoC). The ARM subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In general, the ARM is responsible for configuration and control of the device; including the DSP subsystem and a majority of the peripherals and external memories.

- SPRUEQ0 TMS320DM646x DMSoC Peripherals Overview Reference Guide. Provides an overview and briefly describes the peripherals available on the TMS320DM646x Digital Media System-on-Chip (DMSoC).

- SPRAA84 TMS320C64x to TMS320C64x+ CPU Migration Guide. Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) to the TMS320C64x+ DSP. The objective of this document is to indicate differences between the two cores. Functionality in the devices that is identical is not included.

- SPRU732 TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

- <u>SPRU871</u> *TMS320C64x+ DSP Megamodule Reference Guide.* Describes the TMS320C64x+ digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

8

## Transport Stream Interface (TSIF) Module

#### 1 Introduction

This document describes the operation of the transport stream interface (TSIF) module in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

#### 1.1 Purpose of the Peripheral

The purpose of the transport stream interface (TSIF) module is to parser stream including TS (Time Stamp) header, adaptation field, payload and packet ID (PID) table, and to input and output stream with a parallel and serial interface. The DM646x DMSoC includes two independent transport stream interface (TSIF0 and TSIF1) modules with corresponding clock reference generator (CRGEN) modules for system time-clock recovery.

#### 1.2 Features

The TSIF consists of the following features.

- Simple I/O section that consists of serial and parallel interface (I/F) with both synchronous and asynchronous modes.

- Stream Parser and PID filter (TS header parser, adaptation field parser, payload parser, and PID table).

- Absolute time stamp (ATS) generator and checker for time management by CPU and video codec.

- Ring buffer controller prepared for SDRAM access.

- Input and output ping-pong buffer (one buffer has 256 byte (64 bit × 32 word)).

- Serial and parallel I/F with both synchronous and asynchronous modes.

- Data bus width is 1 bit on serial I/F (using MSB of parallel I/F) and 8 bits on parallel I/F.

- Stream input/output (I/O) speed rate is configurable by I/O clock speed.

- Input data is stored into SDRAM in 32-bit little-endian mode only with 192 byte/unit format or 256 byte/unit format.

- ATS detection, correction, and addition mode are implemented.

- Automatically detect program association table (PAT) and program map table (PMT) and reflect to PID table assignment in itself (partial TS only; stream type and PID should be one-to-one mapping).

- PID filter with 7 PID filter tables and stream type assignments.

- Bypass mode is implemented so that not only TS data but also any other data can be received or transmitted by this module.

- Ring buffer control for both write (8 channels) and read (1 channel) control for SDRAM.

- Specific packet support which is prepared for indicating boundary of plural program on TS.

- Full-TS can be supported in one mode (semiautomatic A mode) with communication to the CPU. Mainly, TS-related functions are available only in partial TS (semiautomatic B mode and full automatic mode can support only partial TS whose stream type and PID is one-to-one mapping).

#### 1.3 Functional Block Diagram

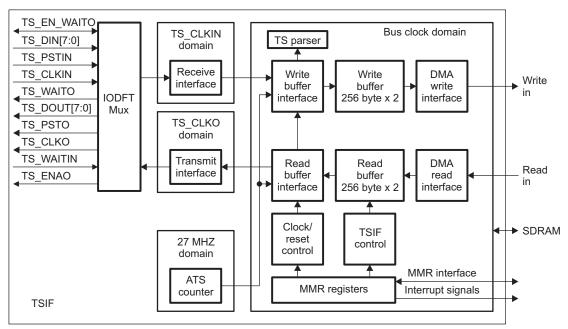

The TSIF functional block diagram is shown in Figure 1.

#### Figure 1. TSIF Block Diagram

#### 1.4 Terminology Used in This Document

The following is a brief explanation of some terms used in this document:

| Term | Meaning                                        |

|------|------------------------------------------------|

| ARIB | Association of Radio Industries and Businesses |

| ATS  | absolute time stamp                            |

| DIT  | discontinuity information table                |

| PAT  | program association table                      |

| PES  | packetized elementary stream                   |

| PID  | packet ID                                      |

| PMT  | program map table                              |

| PS   | program stream                                 |

| STC  | system time clock                              |

| TS   | time stamp                                     |

| TSIF | transport stream interface                     |

#### 2 Architecture

This section describes the architecture of the transport stream interface (TSIF) module.

#### 2.1 Clock Control

The TSIF module receives and transfers video packet data. In receive mode, the source of the driving clock comes from an external device (host device). In transfer mode, the source of the driving clock is the internal clock of the DM646x DMSoC. See the device-specific data manual for detailed information about clock control.

From the standpoint of controlling the stream clock, the most applicable way to use the TSIF module is:

- 1. Start providing the stream clock to the TSIF module (but do not start sending data).

- 2. Activate the TSIF module via the register configuration.

- 3. Start sending the stream data from the data initiator to the TSIF.

- 4. After the data is finished sending, inactivate the TSIF module via the register configuration.

- 5. Stop providing the stream clock to the TSIF module.

#### 2.2 Signal Descriptions

The TSIF provides the I/O signals listed in Table 1.

|                        |     | Ser              | ial |                  | Parallel       |                    |              |                  |  |  |  |

|------------------------|-----|------------------|-----|------------------|----------------|--------------------|--------------|------------------|--|--|--|

|                        | S   | Synchronous      | Α   | synchronous      | S              | Synchronous        | Asynchronous |                  |  |  |  |

| Port Name              | I/O | Function         | I/O | Function         | I/O            | Function           | I/O          | Function         |  |  |  |

| TSn_CLKO               | 0   | Transmit clock   | 0   | Transmit clock   | 0              | Transmit clock     | 0            | Transmit clock   |  |  |  |

| TS <i>n_</i> ENAO      | 0   | Data enable      | 0   | Data enable      | 0              | Data enable        | 0            | Data enable      |  |  |  |

| TS <i>n_</i> WAITIN    | Т   | Not used         | I   | Wait in          | I              | Not used           | Ι            | Wait in          |  |  |  |

| TSn_PSTO               | 0   | Packet start out | 0   | Packet start out | 0              | O Packet start out |              | Packet start out |  |  |  |

| TSn_DOUT7              | 0   | Data out         | 0   | Data out         | 0              | Data[7] out        | 0            | Data[7] out      |  |  |  |

| TS <i>n_</i> DOUT[6:0] | 0   | Not used         | 0   | Not used         | 0              | Data[6:0] out      | 0            | Data[6:0] out    |  |  |  |

| TS <i>n_</i> CLKIN     | Т   | Receive clock    | I   | Receive clock    | I              | Receive clock      | I            | Receive clock    |  |  |  |

| TS <i>n_</i> EN_WAITO  | Т   | Data enable      | 0   | Wait out         | I              | Data enable        | 0            | Wait out         |  |  |  |

| TS <i>n_</i> WAITO     | 0   | Not used         | 0   | Not used         | 0              | Not used           | 0            | Wait out         |  |  |  |

| TS <i>n_</i> PSTIN     | Ι   | Packet start in  | Ι   | Packet start in  | I              | Packet start in    | Ι            | Packet start in  |  |  |  |

| TS <i>n_</i> DIN7      | Т   | Data in          | I   | Data in          | I              | Data[7] in         | I            | Data[7] in       |  |  |  |

| TS <i>n_</i> DIN[6:0]  | Т   | Not used         | I   | Not used         | I Data[6:0] in |                    | I            | Data[6:0] in     |  |  |  |

Table 1. TSIF Signal Descriptions

#### 2.3 Pin Multiplexing

On the DM646x DMSoC, extensive pin multiplexing is used to accommodate the largest number of peripheral functions in the smallest possible package. Pin multiplexing is controlled using a combination of hardware configuration at device reset and software programmable register settings. Refer to the device-specific data manual to determine how pin multiplexing affects the TSIF.

#### 2.4 General Architecture

This section describes the internal architecture of the TSIF module. The DM646x DMSoC has two TSIF modules. The TSIF0 module is able to use the parallel interface and serial interface. The TSIF1 module is able to use only the serial interface.

#### 2.4.1 PID Filter Control

Four types of PID filter methods are supported and are controlled by the PID\_FILTER\_CTL and PID\_FILTER\_EN bits in the TSIF control register 1 (CTRL1).

#### 2.4.1.1 Bypass Mode

This mode does not use the PID\_FILTER\_CTL bit in CTRL1. When the PID\_FILTER\_EN bit in CTRL1 is cleared to 0, input data is stored directly to ring buffer channel 7.

#### 2.4.1.2 Full Manual Mode

In this mode, the CPU configures all PID of packets to be filtered and stored into SDRAM. The CPU is required to know information such as stream type of each category (video, audio, etc.) and PID of targeted category before stream data comes from the host device. The hardware does not have to detect PAT and PMT data.

#### 2.4.1.3 Semi-automatic Mode-A

In this mode, the TSIF module detects PAT and PMT and stores in SDRAM. Then, the CPU reads PAT and PMT stored in SDRAM, and configures the PID filter assignments with the stream type.

**Note:** In some cases, the CPU asserts an interrupt to the Host device and the Host device stalls to assert the source stream data, if PAT/PMT (which has updated version number) detect an interrupt asserted by the TSIF module.

#### 2.4.1.4 Semi-automatic Mode-B

Semi-automatic mode-B is prepared for partial TS reception. At first, the CPU is required to configure the PID filter assignments to be filtered. Then any change of PAT and PMT of the incoming TS data is automatically detected and reflected into the PID filter assignment table. In this case, the following restrictions exist so that this mode performs correctly and effectively.

- The TSIF module holds the configuration of the stream type on the PID filter assignment table as first configured by the CPU and the TSIF module automatically changes only the PID value, if PAT and PMT are changed.

- The incoming TS data can include only one program. This means that only one type of program number on the PAT loop part can be detected.

- When a new PMT comes, the TSIF module automatically changes the PID value, whose stream type is the same as the first configured value by the CPU. So, in this mode, each stream type and each PID value should be one-to-one mapping.

#### 2.4.1.5 Full Automatic Mode

Full automatic mode is prepared for partial TS reception. The CPU enables the TSIF module without any configuration, except the stream type on the PID filter table assignment. After the first configuration, all changes of PAT and PMT are detected and reflected into the PID filter table assignment automatically. In this case, similar restrictions exist as for semi-automatic mode-B (Section 2.4.1.4).

**Note:** The TSIF module does not detect PAT/PMT nor aware of what stream each PID carries in this mode. The TSIF module only PID filters based on the PID filter settings.

#### 2.4.2 Seamless Trans-Coding on Plural Program

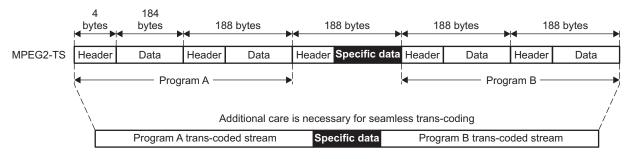

In the case where some plural programs exist consecutively in one TS data, a specific data is inserted at the boundary of two programs (see Figure 2). In ARIB format, DIT is defined as such a boundary indicator. DIT needs the main engine to be reset. In order to change the program configuration without any reset action, this specific code is necessary. This specific code is called a boundary sensing packet.

The functional protocol and format is shown in Figure 2.

#### Figure 2. Seamless Trans-Coding on Plural Programs

Data processing flow on seamless playback for plural TS programs (below stream case)

#### Processing flow: host handshake is only once

In this plan, host has to select one program and one video stream to be processed (and transferred)

| Host (outside device)                                                    | ARM (insi     | de device)                                                    | Stream | am I/O module SDRAI                                                              | N |

|--------------------------------------------------------------------------|---------------|---------------------------------------------------------------|--------|----------------------------------------------------------------------------------|---|

| Stream transfer request (v                                               | ia HPI)<br>►  | Address definition                                            |        | Program number "x" is already selected to be one in whole of the transfer stream |   |

| Ready interrupt (HPI)                                                    |               | Kick the H/W modu<br>Stream data transf                       |        | Parse PAT/PMT     Store stream data with PID filter                              |   |

| If program will change<br>from next packet<br>Stream data transfer (spec | cific packet) |                                                               |        | Buffer address management (ring buffer)                                          |   |

| No specific wait is requir<br>during this period                         | ed            | Detect interrupt<br>Stream data transf<br>(first 2 packets mu |        |                                                                                  |   |

| If program will change<br>from next packet                               |               |                                                               |        |                                                                                  |   |

#### 2.4.2.1 Detecting Boundary Sensing Packet

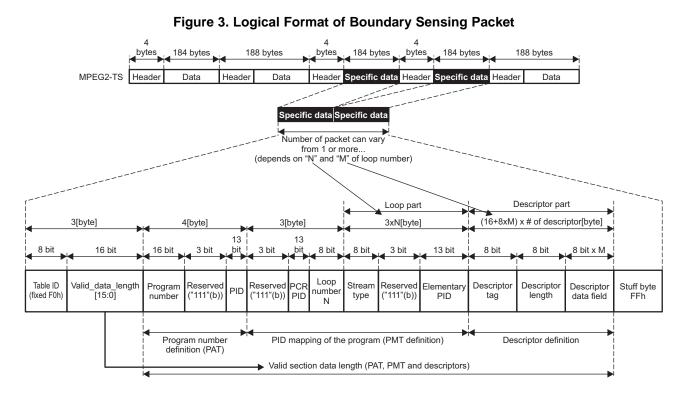

The boundary sensing packet is based on the private section format. This packet is inserted at the boundary position of plural TS programs. The logical packet format is shown in Figure 3.

The PID of the packet can be configured by the SEAMLESS\_BOUNDARY\_INPUT\_PID bit in the boundary sensing packet input register (BSP\_IN). Once the hardware module senses this packet, an interrupt pulse is asserted to the CPU and stores the packet data in SDRAM from the start address defined by the SEAMLESS\_BOUNDARY\_PKT\_STRT\_ADD bit in the boundary sensing packet store address register (BSP\_STORE\_ADDR). When the CPU detects the interrupt from the TSIF module, the CPU accesses the defined address in SDRAM and parses data to process it.

The procedure of processing this packet is:

- 1. When the TSIF module detects a boundary sensing packet, the TSIF module asserts an interrupt pulse to the CPU. In addition, the TSIF module clears all configurations on the PID filter table.

- 2. After sending a boundary sensing packet, the host device needs to stall sending the stream data to the TSIF module.

- 3. The CPU detects the interrupt pulse on step 1, and reads the packet data from SDRAM.

- 4. The CPU parses the packet data and reflects the results of parsing in the configuration of the PID filter table (including PAT and PMT). The module registers related to the PID filter table are configured.

- 5. The CPU asserts an interrupt to the host device, and the host device starts to assert stream data to be processed in the TSIF module.

This procedure is common in all 4 modes.

#### 2.4.2.2 Detecting DIT

DIT is defined in ARIB standard format. DIT and boundary sensing is similar, except DIT needs the receiver and transmitter devices to be reset. The procedure of processing this packet is:

- 1. When the TSIF module detects DIT packets, the TSIF module asserts an interrupt pulse to the CPU. In addition, the TSIF module clears all configurations on the PID filter table including PAT and PMT sensing table.

- 2. After stage 1, the normal PID filter process is re-started in accordance with the definition of modes for the PID filter method.

This procedure is common in all 4 modes.

#### 2.4.3 Ring Buffer Control

After demultiplexing of the source incoming stream and before assertion of the outgoing stream, the TSIF module accesses SDRAM. Then, the TSIF module is required to know the read or write address to be accessed. The TSIF module has an address management tool known as the ring buffer controller, which helps address management by the CPU to avoid buffer overrun and underrun.

#### 2.4.4 ATS Control

The TSIF module supports ATS. This section describes the ATS control with receive case and transfer case.

#### 2.4.4.1 ATS Control with Receive Case

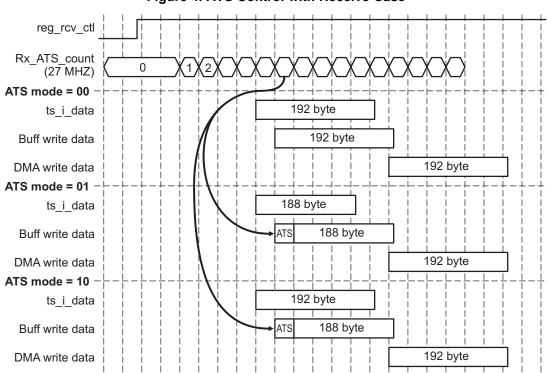

ATS control with receive case has 3 modes (Table 2). It is configured by the RCV\_ATS\_MODE bit in the TSIF control register 0 (CTRL0). The format is shown in Figure 4.

| RCV_ATS_MODE | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| 0            | Do nothing mode. ATS value is stored as 192-byte packet data into SDRAM without any change. |

| 1h           | Add ATS mode. ATS value is added to the incoming 188-byte packet data.                      |

| 2h           | Replace ATS mode. ATS value is replaced in the incoming 192-byte packet data.               |

#### Table 2. ATS Control with Receive Case

Figure 4. ATS Control with Receive Case

#### 2.4.4.2 ATS Control with Transfer Case

TS transfer with ATS has 2 cases and each case has 2 modes.

#### 2.4.4.2.1 ATS Control with Packet Data Initial Value

In this case, the 1st packet uses the packet data initial value when the 1st packet data is transferred. The TX\_ATS\_INIT\_EN bit in the transmit ATS initialization register (TX\_ATS\_INIT) is cleared 0. The format is shown in Figure 5.

Figure 5. ATS Control with Transfer Case using Packet Data Initial Value

#### 2.4.4.2.2 ATS Control with Module Initial Value

In this case, the 1st packet uses the TX\_ATS\_INIT bits in the transmit ATS initialization register (TX\_ATS\_INIT) when the 1st packet data is transferred. The TX\_ATS\_INIT\_EN bit in TX\_ATS\_INIT is set to 1. The format is shown in Figure 6.

#### Figure 6. ATS Control with Transfer Case using Module Initial Value

#### 2.4.5 Variable Packet Sizing for non-TS mode

Variable packet sizing is supported for non-TS mode. Supported unit size is 200-256 bytes with 8-byte aligned. Packet size configuration in non-TS mode and data format when ATS timing control is enabled is shown in Figure 7.

#### Figure 7. Variable Packet Sizing in non-TS Mode

#### TSIF supports non-TS Byte Size Format

| N_in [byte/packet]            | 200 | 208 | 216 | 224 | 232 | 240 | 248 | 256      |

|-------------------------------|-----|-----|-----|-----|-----|-----|-----|----------|

| Mode of timestamp             |     |     |     |     |     |     |     |          |

| Timestamp enable inside TSIF  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | $\times$ |

| Timestamp disable inside TSIF | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0        |

#### 2.4.6 **SDRAM Data Storage Format**

The TSIF module supports two formats for stroing data in SDRAM. The TSIF module can receive and transmit any format of stream data in by-pass mode and can parse MPEG transport stream data. Each data transfer is handled as 192 bytes for one unit access in TS transfer mode and is stored in SDRAM. In non-TS transfer mode, each data transfer is handled as 256 bytes for one unit access (the reason is the unit data size of PS is 2048 bytes/pack). The DMA data bus width is 64 bits (16-bit DDR  $\times$  2 with 300 MHZ).

#### 2.4.6.1 32-Bit Little-Endian Mode

The CPU has to process data inside the SDRAM in 32-bit little-endian mode, the TSIF module can store the stream data in 32-bit little-endian format. The format is shown in Figure 8.

As shown in Figure 8, the input data is stored into the MSB side of each 32-bit word as input order. Number *n* of data byte[*n*] is input and output byte order on MPEG-TS data.

|                                                         |     | 63                                         | 56  | 55                     | 48   | 47                     | 40               | 39                     | 32             | 31                     | 24               | 23                     | 16            | 15                     | 8             | 7                      | 0               |

|---------------------------------------------------------|-----|--------------------------------------------|-----|------------------------|------|------------------------|------------------|------------------------|----------------|------------------------|------------------|------------------------|---------------|------------------------|---------------|------------------------|-----------------|

| With                                                    | 00  | TS header<br>byte[00]<br>(sync)            |     | TS header<br>byte[01]  |      | TS header<br>byte[02]  |                  | TS header<br>byte[03]  |                | ATS[31:24]             |                  | ATS[23:16]             |               | ATS[15:8]              |               | ATS[7:0]               |                 |

| ATS case                                                | 01  | Data byte[04]<br>[7:0]                     |     | Data byte[05]<br>[7:0] |      | Data byte[06]<br>[7:0] |                  | Data byte[07]<br>[7:0] |                | Data byte[00]<br>[7:0] |                  | Data byte[01]<br>[7:0] |               | Data byte[02]<br>[7:0] |               | Data byte[03]<br>[7:0] |                 |

|                                                         |     | <u></u>                                    | 50  |                        | 40   | 47                     | 40               | 20                     | 20             | 24                     | 04               | 00                     | 10            | 45                     | 0             | 7                      | 0               |

|                                                         |     | 63                                         |     | 55                     | 48   | 47                     | 40               | 39                     | 32             | 31                     | 24               | 23                     | 16            | 15                     | 8             | 7                      | 0               |

| Without                                                 | 00  | TS hea<br>byte[<br>(syn                    | 00] | TS he<br>byte          |      |                        | neader<br>e[02]  |                        | eader<br>e[03] | Re                     | eserved<br>[7:0] |                        | erved<br>7:0] |                        | erved<br>':0] |                        | erved<br>:0]    |

| ATS case                                                | 01  | Data byte[04] Data byte[05]<br>[7:0] [7:0] |     |                        |      |                        | byte[06]<br>7:0] |                        | yte[07]<br>:0] | Data byte[00]<br>[7:0] |                  | Data byte[01]<br>[7:0] |               | Data byte[02]<br>[7:0] |               |                        | oyte[03]<br>:0] |

|                                                         |     |                                            |     |                        |      |                        |                  |                        |                |                        |                  |                        |               |                        |               |                        |                 |

| Byte address assignment Byte incoming order SDRAM store |     |                                            |     |                        |      |                        |                  |                        |                |                        | orage            | format                 |               |                        |               |                        |                 |

| 63                                                      |     |                                            | 0   | _                      |      |                        |                  |                        | i              |                        |                  |                        |               | <b>i∢</b> —            | - 64          | 4 bit -                |                 |

| 765                                                     | 4 3 | 2 1                                        | 0   |                        | TS   | ATS                    |                  |                        | ATS            | 47                     |                  |                        | ·             |                        |               |                        |                 |

| b                                                       |     | а                                          | 4   | [3]                    | :24] | [23:16                 | ] [15:           | 8] [                   | 7:0]           | (syn                   | ic)              | 2                      | <br>4 word    |                        | 10'           | 2 byte                 |                 |

| d                                                       | c   |                                            | T   |                        |      |                        |                  |                        |                | Time                   | 2                | 4 WOIU                 |               | 134                    | 2 Dyte        |                        |                 |

| :                                                       |     | :                                          |     | Start                  |      |                        |                  |                        |                |                        |                  |                        | . 🗶           |                        |               |                        |                 |

#### Figure 8. Data Storage Format of 32-Bit Little-Endian Mode on SDRAM

#### 2.4.6.2 64-Bit Big-Endian Mode

The TSIF module can support 64-bit big endian format for SDRAM storage mode. The format is shown in Figure 9.

As shown in Figure 9, the first input data is stored in LSB-sided byte position, and consecutive bytes are stored from LSB-side of the current memory word (1 word = 64 bits). Number n of data\_byte[n] is input and output byte order on MPEG-TS data.

In both 32-bit little-endian mode and 64-bit big-endian mode, bit-level order inside a byte is MSB-first regardless of the storage mode, as shown in Figure 10. In both modes, each byte data is stored in SDRAM in MSB-first order.

| Input<br>order | ATS<br>[3124] |                |    | ATS<br>[70] | 0x47<br>(sync)           | TS<br>header<br>byte[01] | TS<br>header<br>byte[02] | TS<br>header<br>byte[03]        | Data<br>byte[00]<br>[70] | Data<br>byte[01]<br>[70] | Data<br>byte[02]<br>[70] | Data<br>byte[03]<br>[70] | Data<br>byte[04]<br>[70] |     |    |

|----------------|---------------|----------------|----|-------------|--------------------------|--------------------------|--------------------------|---------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|-----|----|

| St             | art           |                |    |             | 63 56                    | 55 48                    | 47 40                    | 39 32                           | 31 24                    | 23 16                    | 15 8                     | 70                       |                          | Tin | ne |

|                |               | SDRA<br>storag |    | 00          | TS header<br>byte[03]    | TS header<br>byte[02]    | TS header<br>byte[01]    | TS header<br>byte[00]<br>(sync) | ATS[70]                  | ATS[158]                 | ATS[2316]                | ATS[3124]                |                          |     |    |

|                |               | form           | at | 01          | Data<br>byte[07]<br>[70] | Data<br>byte[06]<br>[70] | Data<br>byte[05]<br>[70] | Data<br>byte[04]<br>[70]        | Data<br>byte[03]<br>[70] | Data<br>byte[02]<br>[70] | Data<br>byte[01]<br>[70] | Data<br>byte[00]<br>[70] |                          |     |    |

Figure 9. Data Storage Format of 64-Bit Big-Endian Mode on SDRAM

|                        |      | 63                           | 56   | 55                     | 48  | 47                   | 40              | 39   | 32                  | 31        | 24                    | 23        | 16                     | 15       |                | 8       | 7                 | 0 |

|------------------------|------|------------------------------|------|------------------------|-----|----------------------|-----------------|------|---------------------|-----------|-----------------------|-----------|------------------------|----------|----------------|---------|-------------------|---|

| SDRAM<br>storage       | 00   | TS head<br>byte[00<br>(sync) | )]   | TS hea<br>byte[0       |     | TS hea<br>byte[      |                 |      | eader<br>e[03]      | ATS[3124] |                       | ATS[2316] |                        | ATS[158] |                | ATS[70] |                   |   |

| format                 | 01   | Data Byte<br>[70]            | [04] | Data Byte<br>[70]      |     | Data By<br>[7(       |                 |      | 8yte[07]<br>0]      |           | Byte[00]<br>70]       |           | Byte[01]<br>70]        |          | Byte[0<br>[70] | 2]      | Data Byte<br>[70] |   |

|                        |      |                              |      |                        |     |                      |                 |      |                     |           |                       |           |                        |          |                |         |                   |   |

| Data<br>Byte[04<br>[7] | i] I | Data<br>Byte[04]<br>[6]      |      | Data<br>/te[04]<br>[5] | Byt | eata<br>e[04]<br>[4] | Da<br>Byte<br>[ | [04] | Dat<br>Byte[<br>[2] | 04]       | Data<br>Byte[0<br>[1] |           | Data<br>Byte[04<br>[0] | 4]       |                |         |                   |   |

#### Figure 10. Bit-Level Endian Format in SDRAM Format

The TSIF hardware reset is controlled by the DM646x DMSoC. See the device-specific data manual for more information.

#### 2.6 Interrupt Support

The TSIF module outputs two interrupts that are routed to the CPU (Table 3). The TSIF interrupt request is generated by the following events:

- Ring Buffer status: SDRAM writing/reading address on Ring Buffer write/read channel has reached to a subtracted pointer address. There are 8 status register bits (RBWn\_STATUS) for each write Ring Buffer and 1 status register bit (RBR0\_FULL\_STATUS) for read Ring Buffer.

- STC status: STC counter value has reached the configured value in the STC interrupt entry *n* register (STC\_INT*n*). There are 8 status registers for STC interrupts.

- Receive packet error status: Status for receive packet error (RCV\_PKT\_ERR\_STATUS bit).

- PMT detect status: Detection of new PMT data (PMT\_DETECT\_STATUS bit).

- PAT detect status: Detection of new PAT data (PAT\_DETECT\_STATUS).

- GOP start status: Detection of GOP start packet (GOP\_START\_STATUS bit).

- Boundary specific status: Detection of specific word (BOUNDARY\_SPECIFIC\_STATUS bit) that is implemented at dividing pointer (boundary) of program data in transferred TS data.

See the TSIF interrupt status register (INTSTAT) for interrupt events and the receive packet status register (RX\_PKT\_STAT) for receive packet status events.

**Note:** The Ring Buffer Write interrupt is generated when the DMA transfer is completed for the packet that includes the address with subtract value.

The Ring Buffer Read interrupt is generated when the current address reaches the address that is indicated with the subtract address.

| Table 5. TSIF Module Interrupts |         |        |  |  |  |  |

|---------------------------------|---------|--------|--|--|--|--|

| ARM Event                       | Acronym | Source |  |  |  |  |

| 10                              | TSINT0  | TSIF 0 |  |  |  |  |

| 11                              | TSINT1  | TSIF 1 |  |  |  |  |

Table 2 TOLE Madula Interrupte

#### 11 TSINT1

#### 2.7 Emulation Suspend Mode

The TSIF module does support the emulation suspend signal from the CPU. The emulation suspend signal (high indicates that the CPU is suspended) is asserted by the CPU when the CPU is halted with a breakpoint or any other reason during debug.

**Note:** The emulation suspend signal is multiplexed with CPU signals. When emulation suspend mode is used, it is required to select the ARM or DSP.

#### 3 Use Cases

#### 3.1 Input and Output Interface Structure

The TSIF module has the following three physical and logical interfaces:

- serial interface (data, clock, enable/wait and packet/byte start)

- parallel interface (data, clock, enable/wait, packet/byte start and 8-bit data bus width)

- consequential interface (source and result data of the TSIF shall be stored in SDRAM)

The serial and parallel interfaces are interfaced directly to the host device, and the consequential interface is used to store/read source stream data into/from SDRAM with HPI or PCI modules. In consequential interface, all data paths are driven in same clock (SDRAM clock).

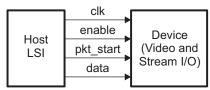

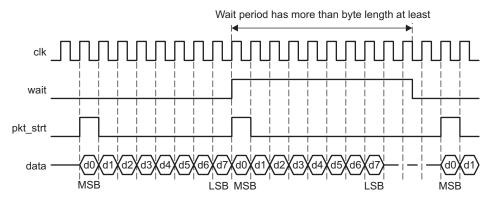

#### 3.1.1 Serial Interface

The serial interface is used to stream directly to/from the external host device with a 1-bit data line and control lines. Two types of interface protocol exist: non-real time (handshake:asynchronous) mode and real time (pushingsynchronous) mode. In the interface protocol, asynchronous means that the transmitted data by the initiator is not always detected by the receiver with zero wait.

#### 3.1.1.1 Serial Interface Format in Synchronous Mode

In synchronous format, all initiated data is detected by the receiver. Therefore, the host device and the DM646x DMSoC are regarded as synchronous to each other. All signals are generated by a data initiator with a packet start pulse and an enable signal. The enable signal is inactive during data transfer of a packet. In addition, the enable signal sometimes stays active during consecutive packets.

When incoming (outgoing) stream data is not TS data (for example, PES or PS data), then the packet start signal is also asserted similar to the TS case, so that the receiver detects the number of bytes/packets in the received data by counting the start signal pulses and clocks in between.

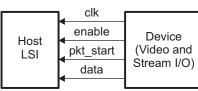

The physical and logical format of the serial interface in real time (synchronous) mode is shown in Figure 11

#### Figure 11. Serial Interface Format in Synchronous Mode

Receiver mode (real-time mode)

Transmitter mode (real-time mode)

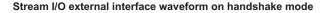

Stream I/O external interface waveform on real-time mode

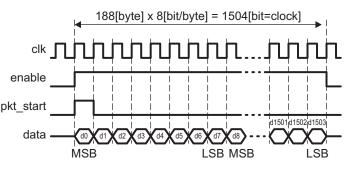

#### 3.1.1.2 Serial Interface Format in Asynchronous Mode

In asynchronous format, the receiver mode and the transmitter mode of the DM646x DMSoC have different formats. In receiver mode, three signals (clock, data, and byte start pulse) are initiated by the external host device while the wait signal is generated by the DM646x DMSoC. Figure 12 shows the logical interface of the receiver mode. When the ring buffer is filled with data, the TSIF module asserts a data write request but is waiting for an acknowledge and when the internal cache is full of data, the wait signal is asserted. The asserted wait signal is detected by the host processor, the host processor stalls data assertion during an activated period of the wait signal.

The physical and logical format of the serial interface input in non-real time (asynchronous) mode is shown in Figure 12.

#### Figure 12. Serial Interface Input Format in Asynchronous Mode

TSIF receiver mode (handshake mode)

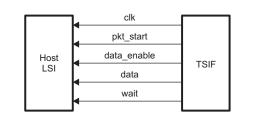

In transmitter mode, the wait signal from the external host device is detected by the TSIF module. The wait signal is latched by the pulse signal that indicates the start of a byte data (byte\_start signal for internal use). If the signal is detected by the TSIF module, the module stalls the output after a byte transfer is finished. The minimum unit of data transfer is a byte. All data with a data\_enable signal is detected by the external host device.

If you pull down the wait input, the interface format is the same as the synchronous mode. Note that you have to keep the distance between the end of a packet to the start of the next packet as  $0/32/64/128 \times 8$  clocks.

The physical and logical format of the serial interface output in non-real time (asynchronous) mode is shown in Figure 13.

#### Figure 13. Serial Interface Output Format in Asynchronous Mode

Non real-time data transfer mode (serial output)

#### Serial interface format

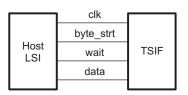

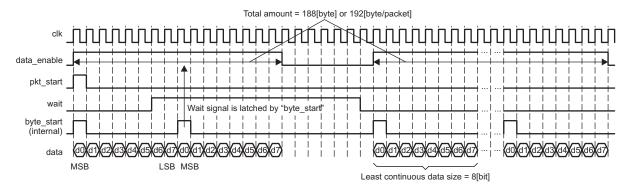

#### 3.1.2 Parallel Interface

The protocol of the parallel interface format is similar to the serial interface. One difference from the serial interface is the data bus width, the serial interface has 1 bit for data but the parallel interface has 8 bits for data.

The physical format of the parallel interface is shown in Figure 14.

#### Synchronous data transfer mode Asynchronous data transfer mode clk clk data enable wait Device Device Host Host (Video and pkt\_start byte\_start (Video and LSI LSI Stream I/O) Stream I/O) data [7:0] data [7:0] clk clk data enable enable Device Device Host Host pkt\_start (Video and pkt\_start (Video and LSI LSI Stream I/O) Stream I/O) data [7:0] data [7:0]

Figure 14. Parallel Interface Format

Use Cases

#### 3.2 Packet Data Configuration

Packet data configuration is set in the TSIF control register 0 (CTRL0). Transfer/receiver packet data is required to select the TS mode and ATS mode.

- The TS mode configuration is set by the TX\_STREAM\_MODE and the RCV\_STREAM\_MODE bits.

- In TS mode, the packet data ATS mode configuration is set by the TX\_ATS\_MODE and the RCV\_ATS\_MODE bits.

- In non-TS mode, the packet data size and ATS mode configuration is required to be set.

- Packet data size is set by the TX\_PKT\_SIZE and the RCV\_PKT\_SIZE bits.

- ATS mode is set by the TX\_ATS\_EN and the RCV\_ATS\_EN bits.

Note: When ATS mode is enabled, the non-TS packet size cannot be set to 256 bytes  $(TX_PKT_SIZE = 7h)$ .

#### 3.3 Transfer/Receiver Interface Configuration

The transfer/receiver interface configuration is set in the TSIF control register 0 (CTRL0).

- Transfer interface and synchronous mode is set by the TX\_IF\_MODE bit.

- Receiver interface and synchronous mode is set by the RCV\_IF\_MODE bit.

#### 3.4 PID Control

In order to parse input stream data and divide into data with each PID, the TSIF module can perform PID filter in four modes. Bypass mode is enabled when the PID\_FILTER\_EN bit in the TSIF control register 1 (CTRL1) is cleared to 0. Full manual, semi-automatic mode-A, semi-automatic mode-B, and full automatic mode is enabled when in TS mode and when the PID\_FILTER\_EN bit is set to 1.

- In manual mode, all PIDs are set with the CPU. PAT/PMTdetection isnotavailable in this mode.

- In semi-automatic mode-A, all PIDs are set with the CPU. PAT/PMTis detected when the program is changed.

- In semi-automatic mode-B, PIDs are set with the CPU and then all PIDs are updated automatically when receiving new PAT/PMT. This mode is supported for partial TS only.

- In full automatic mode, all PIDs are set automatically by detecting PAT/PMT1. This mode is supported for partial TS only.

#### 3.4.1 Bypass Mode

In bypass mode, input data from the host device is stored directory to ring buffer channel 7.

- The PID\_FILTER\_EN bit in the TSIF control register 1 (CTRL1) is cleared to 0.

- Ring buffer write channel 7 registers (RING\_BUF\_WR\_CH7) require configuration.

NSTRUMENTS

#### 3.4.2 Full Manual Mode

The processing and hardware control flow chart for full manual mode of the PID filter configuration including communication between CPU and TSIF is shown in Figure 15.

The following configurations related to the PID filter are necessary to accomplish full manual mode:

- 1. PID\_FILTER\_EN bit in the TSIF control register 1 (CTRL1) is set to 1.

- 2. PID\_FILTER\_CTL bit in CTRL1 is cleared to 0.

- 3. PAT\_SENSE\_EN bit in the PAT sense configuration register (PAT\_SEN\_CFG) is cleared to 0.

- 4. PMT\_SENSE\_EN bit in the PMT sense configuration register (PMT\_SEN\_CFG) is cleared to 0.

- 5. PID*n*\_FILTER\_EN bit in the PID*n* filter configuration register (PID*n*\_FILT\_CFG) is set to 1.

- 6. STREAM\_TYPE*n* bit in PID*n*\_FILT\_CFG is set to stream type number.

- 7. Set ring buffer control.

In this mode, PCR-PID is defined by the register configuration as PMT parsing is done by the CPU. When using the TSIF module in real time mode, this process is mandatory.

#### Figure 15. Processing on Full Manual Mode of PID Filter

Use Cases

#### 3.4.3 Semi-Automatic Mode-A

The processing and hardware control flow chart for semi-automatic mode-A of the PID filter configuration including communication between CPU and TSIF is shown in Figure 16.

The following configurations related to the PID filter are necessary to accomplish semi-automatic mode-A:

- 1. PID\_FILTER\_EN bit in the TSIF control register 1 (CTRL1) is set to 1.

- 2. PID\_FILTER\_CTL bit in CTRL1 is set to 1.

- 3. CPU sets PAT\_SENSE\_EN bit in the PAT sense configuration register (PAT\_SEN\_CFG) to 1 to detect PAT.

- 4. PAT\_STORE\_ADD bit in the PAT store address register (PAT\_STR\_ADDR) is set to store address for PAT.

- 5. TSIF module generates an interrupt when PAT is detected.

- 6. CPU sets PMT\_SENSE\_EN bit in the PMT sense configuration register (PMT\_SEN\_CFG) to 1 to detect PMT.

- 7. PMT\_PID bit in PMT\_SEN\_CFG is configured.

- PMT\_STORE\_ADD bit in the PMT store address register (PMT\_STR\_ADDR) is set to store address for PMT.

- 9. TSIF module generates an interrupt when PMT is detected.

- 10. CPU sets all PID*n*\_FILTER\_EN bits in the PID*n* filter configuration registers (PID*n*\_FILT\_CFG) to 1.

- 11. STREAM\_TYPE*n* bit in PID*n*\_FILT\_CFG is set to stream type number.

- 12. Set ring buffer control.

- 13. TSIF module continues to monitor PAT. When TSIF module detects new PAT, all of the enables for PMT and other PID are automatically cleared. Then the TSIF module generates an interrupt to the CPU.

- 14. Procedure repeats from step 6.

Figure 16. Processing on Semi-Automatic Mode-A of PID Filter

Use Cases

#### 3.4.4 Semi-Automatic Mode-B

The processing and hardware control flow chart for semi-automatic mode-B of the PID filter configuration including communication between CPU and TSIF is shown in Figure 17.

The following configurations related to the PID filter are necessary to accomplish semi-automatic mode-B:

- 1. PID\_FILTER\_EN bit in the TSIF control register 1 (CTRL1) is set to 1.

- 2. PID\_FILTER\_CTL bit in CTRL1 is set to 2h.

- 3. PID*n*\_FILTER\_EN bit in the PID*n* filter configuration register (PID*n*\_FILT\_CFG) is set to 1.

- 4. STREAM\_TYPEn bit in PIDn\_FILT\_CFG is set to stream type number.

- 5. PAT\_SENSE\_EN bit in the PAT sense configuration register (PAT\_SEN\_CFG) is set to 1.

- PAT\_STORE\_ADD bit in the PAT store address register (PAT\_STR\_ADDR) is set to store address for PAT.

- 7. PMT\_SENSE\_EN bit in the PMT sense configuration register (PMT\_SEN\_CFG) is set to 1.

- 8. PMT\_STORE\_ADD bit in the PMT store address register (PMT\_STR\_ADDR) is set to store address for PMT.

- 9. TSIF module continues to monitor PAT. When TSIF module detects new PAT:

- a. PMT\_PID bit in PMT\_SEN\_CFG is set to detect PMT.

- b. All of the enables for PMT are automatically cleared.

- c. TSIF module generates an interrupt to the CPU.

- 10. TSIF module continues to monitor PMT. When TSIF module detects new PMT:

- a. All STREAM\_TYPEn bits in PIDn\_FILT\_CFG are set to stream type number.

- b. All PIDn\_FILTER\_EN bits in PIDn\_FILT\_CFG are set to 1.

- c. TSIF module generates an interrupt to the CPU.

- 11. TSIF module continues to monitor PAT. When TSIF module detects new PAT, procedure repeats from step 9.

Figure 17. Processing on Semi-Automatic Mode-B of PID Filter

Use Cases

#### 3.4.5 Full Automatic Mode

The processing and hardware control flow chart for full automatic mode of the PID filter configuration including communication between CPU and TSIF is shown in Figure 18.

The following configurations related to the PID filter are necessary to accomplish full automatic mode:

- 1. PID\_FILTER\_EN bit in the TSIF control register 1 (CTRL1) is set to 1.

- 2. PID\_FILTER\_CTL bit in CTRL1 is set to 3h.

- 3. CPU sets PAT\_SENSE\_EN bit in the PAT sense configuration register (PAT\_SEN\_CFG) to 1 to detect PAT.

- PAT\_STORE\_ADD bit in the PAT store address register (PAT\_STR\_ADDR) is set to store address for PAT.

- 5. TSIF module continues to monitor PAT. When TSIF module detects new PAT:

- a. PMT\_PID bit in the PMT sense configuration register (PMT\_SEN\_CFG) is set to detect PMT.

- b. All of the enables for PMT are automatically cleared.

- c. TSIF module generates an interrupt to the CPU.

- 6. TSIF module continues to monitor PMT. When TSIF module detects new PMT:

- a. All STREAM\_TYPE*n* bits in PID*n*\_FILT\_CFG are set to stream type number.

- b. All PIDn\_FILTER\_EN bits in PIDn\_FILT\_CFG are set to 1.

- c. TSIF module generates an interrupt to the CPU.

- 7. TSIF module continues to monitor PAT. When TSIF module detects new PAT, procedure repeats from step 5.

EXAS

**NSTRUMENTS**

Figure 18. Processing on Full Automatic Mode of PID Filter

#### 3.5 Ring Buffer Control

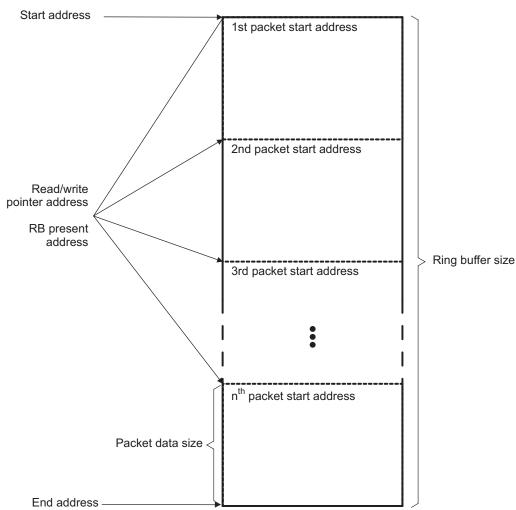

The configuration for the ring buffer controller is shown in Figure 19.

The TSIF module is required to configure the buffer area and the ring buffer interrupt timing for each channel.

- Buffer area configuration requires setting the buffer start address and end address. Then the buffer size should be set to multiples of the packet size.

- The start address is set by the RBWn\_STRT\_ADD bit in the write ring buffer channel n start address register (RING\_BUF\_WR\_CHn\_START\_ADDR).

- The end address is set by the RBWn\_END\_ADD bit in the write ring buffer channel n end address register (RING\_BUF\_WR\_CHn\_END\_ADDR).

- When start address and end address are set, the TSIF module is required to stop.

- Ring buffer interrupt timing configuration requires setting the pointer address and subtraction bytes from pointer address.

- The pointer address is set by the RBWn\_RP\_ADD bit in the write ring buffer channel n read pointer address register (RING\_BUF\_WR\_CHn\_RD\_POINT\_ADDR).

- Subtraction bytes are set by the RBWn\_SUB\_ADD bit in the write ring buffer channel n subtraction register (RING\_BUF\_WR\_CHn\_SUB).

- The subtraction bytes value is required to be less than the total buffer size (end address start address).

- Note: The address registers and subtraction registers should be set for an 8-byte boundary.

Figure 19. Ring Buffer Controller

#### 4 Registers

Table 4 lists the memory-mapped registers for the transport stream interface (TSIF) module. See the device-specific data manual for the memory address of these registers. The module base address is 01C1 3000h for TSIF0 and 01C1 3400h for TSIF1.

| Offset | Acronym        | Register Description                               | Section      |

|--------|----------------|----------------------------------------------------|--------------|

| 0h     | PID            | TSIF Peripheral Identification Register            | Section 4.1  |

| 4h     | CTRL0          | Control Register 0                                 | Section 4.2  |

| 8h     | CTRL1          | Control Register 1                                 | Section 4.3  |

| Ch     | INTEN          | Interrupt Enable Register                          | Section 4.4  |

| 10h    | INTEN_SET      | Interrupt Enable Set Register                      | Section 4.5  |

| 14h    | INTEN_CLR      | Interrupt Enable Clear Register                    | Section 4.6  |

| 18h    | INTSTAT        | Interrupt Status Register                          | Section 4.7  |

| 1Ch    | INTSTAT_CLR    | Interrupt Status Clear Register                    | Section 4.8  |

| 20h    | EMU_CTRL       | Emulation Control Register                         | Section 4.9  |

| 24h    | ASYNC_TX_WAIT  | Asynchronous Transmit Wait Time Register           | Section 4.10 |

| 28h    | PAT_SEN_CFG    | PAT Sense Configuration Register                   | Section 4.11 |

| 2Ch    | PAT_STR_ADDR   | PAT Store Address Register                         | Section 4.12 |

| 30h    | PMT_SEN_CFG    | PMT Sense Configuration Register                   | Section 4.13 |

| 34h    | PMT_STR_ADDR   | PMT Store Address Register                         | Section 4.14 |

| 38h    | BSP_IN         | BSP Input Register                                 | Section 4.15 |

| 3Ch    | BSP_STORE_ADDR | BSP Input Store Address Register                   | Section 4.16 |

| 40h    | PCR_SENSE_CFG  | PCR Sense Configuration Register                   | Section 4.17 |

| 44h    | PID0_FILT_CFG  | PID0 Filter Configuration Register                 | Section 4.18 |

| 48h    | PID1_FILT_CFG  | PID1 Filter Configuration Register                 | Section 4.18 |

| 4Ch    | PID2_FILT_CFG  | PID2 Filter Configuration Register                 | Section 4.18 |

| 50h    | PID3_FILT_CFG  | PID3 Filter Configuration Register                 | Section 4.18 |

| 54h    | PID4_FILT_CFG  | PID4 Filter Configuration Register                 | Section 4.18 |

| 58h    | PID5_FILT_CFG  | PID5 Filter Configuration Register                 | Section 4.18 |

| 5Ch    | PID6_FILT_CFG  | PID6 Filter Configuration Register                 | Section 4.18 |

| 60h    | BYPASS_CFG     | Bypass Mode Configuration Register                 | Section 4.19 |

| 64h    | TX_ATS_INIT    | Transmit ATS Initialization Register               | Section 4.20 |

| 68h    | TX_ATS_MON     | Transmit ATS Monitor Register                      | Section 4.21 |

| 70h    | RX_PKT_STAT    | Receive Packet Status Register                     | Section 4.22 |

| 80h    | STC_INIT_CTRL  | STC Initialization Control Register                | Section 4.23 |

| 84h    | STC_INIT_VAL   | STC Initialization Value Register                  | Section 4.24 |

| 88h    | STC_INT0       | STC Interrupt Entry 0 Register                     | Section 4.25 |

| 8Ch    | STC_INT1       | STC Interrupt Entry 1 Register                     | Section 4.25 |

| 90h    | STC_INT2       | STC Interrupt Entry 2 Register                     | Section 4.25 |

| 94h    | STC_INT3       | STC Interrupt Entry 3 Register                     | Section 4.25 |

| 98h    | STC_INT4       | STC Interrupt Entry 4 Register                     | Section 4.25 |

| 9Ch    | STC_INT5       | STC Interrupt Entry 5 Register                     | Section 4.25 |

| A0h    | STC_INT6       | STC Interrupt Entry 6 Register                     | Section 4.25 |

| A4h    | STC_INT7       | STC Interrupt Entry 7 Register                     | Section 4.25 |

| C0h    | WRB_CTRL       | Write Ring Buffer Channel Control Register         | Section 4.26 |

| C4h    | WRB0_STRT_ADDR | Write Ring Buffer Channel 0 Start Address Register | Section 4.27 |

### Table 4. Transport Stream Interface (TSIF) Module Registers

\_\_\_\_

www.ti.com

### Table 4. Transport Stream Interface (TSIF) Module Registers (continued)

| Offset | Acronym        | Register Description                               | Section      |

|--------|----------------|----------------------------------------------------|--------------|

| C8h    | WRB0_END_ADDR  | Write Ring Buffer Channel 0 End Address Register   | Section 4.28 |

| CCh    | WRB0_RDPTR     | Write Ring Buffer Channel 0 Read Pointer Register  | Section 4.29 |

| D0h    | WRB0_SUB       | Write Ring Buffer Channel 0 Subtraction Register   | Section 4.30 |

| D4h    | WRB0_WRPTR     | Write Ring Buffer Channel 0 Write Pointer Register | Section 4.31 |

| E0h    | WRB1_STRT_ADDR | Write Ring Buffer Channel 1 Start Address Register | Section 4.27 |

| E4h    | WRB1_END_ADDR  | Write Ring Buffer Channel 1 End Address Register   | Section 4.28 |

| E8h    | WRB1_RDPTR     | Write Ring Buffer Channel 1 Read Pointer Register  | Section 4.29 |

| ECh    | WRB1_SUB       | Write Ring Buffer Channel 1 Subtraction Register   | Section 4.30 |

| F0h    | WRB1_WRPTR     | Write Ring Buffer Channel 1 Write Pointer Register | Section 4.31 |

| 100h   | WRB2_STRT_ADDR | Write Ring Buffer Channel 2 Start Address Register | Section 4.27 |

| 104h   | WRB2_END_ADDR  | Write Ring Buffer Channel 2 End Address Register   | Section 4.28 |

| 108h   | WRB2_RDPTR     | Write Ring Buffer Channel 2 Read Pointer Register  | Section 4.29 |

| 10Ch   | WRB2_SUB       | Write Ring Buffer Channel 2 Subtraction Register   | Section 4.30 |

| 110h   | WRB2_WRPTR     | Write Ring Buffer Channel 2 Write Pointer Register | Section 4.31 |

| 120h   | WRB3_STRT_ADDR | Write Ring Buffer Channel 3 Start Address Register | Section 4.27 |

| 124h   | WRB3_END_ADDR  | Write Ring Buffer Channel 3 End Address Register   | Section 4.28 |

| 128h   | WRB3_RDPTR     | Write Ring Buffer Channel 3 Read Pointer Register  | Section 4.29 |

| 12Ch   | WRB3_SUB       | Write Ring Buffer Channel 3 Subtraction Register   | Section 4.30 |

| 130h   | WRB3_WRPTR     | Write Ring Buffer Channel 3 Write Pointer Register | Section 4.31 |

| 140h   | WRB4_STRT_ADDR | Write Ring Buffer Channel 4 Start Address Register | Section 4.27 |

| 144h   | WRB4_END_ADDR  | Write Ring Buffer Channel 4 End Address Register   | Section 4.28 |

| 148h   | WRB4_RDPTR     | Write Ring Buffer Channel 4 Read Pointer Register  | Section 4.29 |

| 14Ch   | WRB4_SUB       | Write Ring Buffer Channel 4 Subtraction Register   | Section 4.30 |

| 150h   | WRB4_WRPTR     | Write Ring Buffer Channel 4 Write Pointer Register | Section 4.31 |

| 160h   | WRB5_STRT_ADDR | Write Ring Buffer Channel 5 Start Address Register | Section 4.27 |

| 164h   | WRB5_END_ADDR  | Write Ring Buffer Channel 5 End Address Register   | Section 4.28 |

| 168h   | WRB5_RDPTR     | Write Ring Buffer Channel 5 Read Pointer Register  | Section 4.29 |

| 16Ch   | WRB5_SUB       | Write Ring Buffer Channel 5 Subtraction Register   | Section 4.30 |

| 170h   | WRB5_WRPTR     | Write Ring Buffer Channel 5 Write Pointer Register | Section 4.31 |

| 180h   | WRB6_STRT_ADDR | Write Ring Buffer Channel 6 Start Address Register | Section 4.27 |

| 184h   | WRB6_END_ADDR  | Write Ring Buffer Channel 6 End Address Register   | Section 4.28 |

| 188h   | WRB6_RDPTR     | Write Ring Buffer Channel 6 Read Pointer Register  | Section 4.29 |

| 18Ch   | WRB6_SUB       | Write Ring Buffer Channel 6 Subtraction Register   | Section 4.30 |

| 190h   | WRB6_WRPTR     | Write Ring Buffer Channel 6 Write Pointer Register | Section 4.31 |

| 1A0h   | WRB7_STRT_ADDR | Write Ring Buffer Channel 7 Start Address Register | Section 4.27 |

| 1A4h   | WRB7_END_ADDR  | Write Ring Buffer Channel 7 End Address Register   | Section 4.28 |

| 1A8h   | WRB7_RDPTR     | Write Ring Buffer Channel 7 Read Pointer Register  | Section 4.29 |

| 1ACh   | WRB7_SUB       | Write Ring Buffer Channel 7 Subtraction Register   | Section 4.30 |

| 1B0h   | WRB7_WRPTR     | Write Ring Buffer Channel 7 Write Pointer Register | Section 4.31 |

| 1C0h   | RRB_CTRL       | Read Ring Buffer Channel Control Register          | Section 4.32 |

| 1C4h   | RRB_STRT_ADDR  | Read Ring Buffer Channel Start Address Register    | Section 4.33 |

| 1C8h   | RRB_END_ADDR   | Read Ring Buffer Channel End Address Register      | Section 4.34 |

| 1CCh   | RRB_WRPTR      | Read Ring Buffer Channel Write Pointer Register    | Section 4.35 |

| 1D0h   | RRB_SUB        | Read Ring Buffer Channel Subtraction Register      | Section 4.36 |