# OMAP5912 Multimedia Processor Universal Serial Bus (USB) Reference Guide

Literature Number: SPRU761A March 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from TI under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

St Office Box 055505 Dallas, Texas 75205

Copyright © 2004, Texas Instruments Incorporated

# **Preface**

# **Read This First**

#### About This Manual

This document describes the universal serial bus (USB) host on the OMAP5912 multimedia processor.

#### Notational Conventions

This document uses the following conventions.

Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

#### **Related Documentation From Texas Instruments**

The following documents describe the OMAP5910 device and related peripherals. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

- **OMAP5912** Multimedia Processor Device Overview and Architecture Reference Guide (literature number SPRU748) introduces the setup, components, and features of the OMAP5912 multimedia processor and provides a high-level view of the device architecture.

- OMAP5912 Multimedia Processor OMAP 3.2 Subsystem Reference Guide (literature number SPRU749) introduces and briefly defines the main features of the OMAP3.2 subsystem of the OMAP5912 multimedia processor.

- **OMAP5912** Multimedia Processor DSP Sybsystem Reference Guide (literature number SPRU750) describes the OMAP5912 multimedia processor DSP subsystem. The digital signal processor (DSP) subsystem is built around a core processor and peripherals that interface with: 1) The ARM926EJS via the microprocessor unit interface (MPUI); 2) Various standard memories via the external memory interface (EMIF); 3) Various system peripherals via the TI peripheral bus (TIPB) bridge.

- **OMAP5912** Multimedia Processor Clocks Reference Guide (literature number SPRU751) describes the clocking mechanisms of the OMAP5912 multimedia processor. In OMAP5912, various clocks are created from special components such as the digital phase locked loop (DPLL) and the analog phase-locked loop (APLL).

- **OMAP5912** Multimedia Processor Initialization Reference Guide (literature number SPRU752) describes the reset architecture, the configuration, the initialization, and the boot ROM of the OMAP5912 multimedia processor.

- **OMAP5912 Multimedia Processor Power Management Reference Guide** (literature number SPRU753) describes power management in the OMAP5912 multimedia processor. The ultralow-power device (ULPD) generates and manages clocks and reset signals to OMAP3.2 and to some peripherals. It controls chip-level power-down modes and handles chip-level wake-up events. In deep sleep mode, this module is still active to monitor wake-up events. This book describes the ULPD module and outline architecture.

- **OMAP5912 Multimedia Processor Security Features Reference Guide** (literature number SPRU754) describes the security features of teh OMAP5912 multimedia processor. The OMAP5912 security scheme relies on the OMAP3.2 secure mode. The distributed security on the OMAP3.2 platform is a Texas Instruments solution to address m-commerce and security issues within a mobile phone environment. The OMAP3.2 secure mode was developed to bring hardware robustness to the overall OMAP5912 security scheme.

- OMAP5912 Multimedia Processor Direct Memory Access (DMA) Support Reference Guide (literature number SPRU755) describes the direct memory access support of the OMAP5912 multimedia processor. The OMAP5912 processor has three DMAs:

- The system DMA is embedded in OMAP3.2. It handles DMA transfers associated with MPU and shared peripherals.

- The DSP DMA is embedded in OMAP3.2. It handles DMA transfers associated with DSP peripherals.

- The generic distributed DMA (GDD) is an OMAP5912 resource attached to the SSI peripheral. It handles only DMA transfers associated with the SSI peripheral.

4 OMAP5912

OMAP5912 Multimedia Processor Memory Interfaces Reference Guide

(literature number SPRU756) describes the memory interfaces of the OMAP5912 multimedia processor.

- SDRAM (external memory interface fast, or EMIFF)

- Asynchronous and synchronous burst memory (external memory interface slow, or EMIFS)

- NAND flash (hardware controller or software controller)

- CompactFlash on EMIFS interface

- Internal static RAM

**OMAP5912** Multimedia Processor Interrupts Reference Guide (literature number SPRU757) describes the interrupts of the OMAP5912 multimedia processor. Three level 2 interrupt controllers are used in OMAP5912:

- One MPU level 2 interrupt handler (also referred to as MPU interrupt level 2) is implemented outside of OMAP3.2 and can handle 128 interrupts.

- One DSP level 2 interrupt handler (also referred to as DSP interrupt level 2.1) is instantiated outside of OMAP3.2 and can handle 64 interrupts.

- One OMAP3.2 DSP level 2 interrupt handler (referenced as DSP interrupt level 2.0) can handle 16 interrupts.

- OMAP5912 Multimedia Processor Peripheral Interconnects Reference Guide (literature number SPRU758) describes various periperal interconnects of the OMAP5912 multimedia processor.

- **OMAP5912** *Multimedia Processor Timers Reference Guide* (literature number SPRU759) describes various timers of the OMAP5912 multimedia processor.

- **OMAP5912 Multimedia Processor Serial Interfaces Reference Guide** (literature number SPRU760) describes the serial interfaces of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor Universal Serial Bus (USB) Reference Guide (literature number SPRU761) describes the universal serial bus (USB) host on the OMAP5912 multimedia processor. The OMAP5912 processor provides several varieties of USB functionality. Flexible multiplexing of signals from the OMAP5912 USB host controller, the OMAP5912 USB function controller, and other OMAP5912 peripherals allow a wide variety of system-level USB capabilities. Many of the OMAP5912 pins can be used for USB-related signals or for signals from other OMAP5912 peripherals. The OMAP5912 top-level pin multiplexing

controls each pin individually to select one of several possible internal pin signal interconnections. When these shared pins are programmed for use as USB signals, the OMAP5912 USB signal multiplexing selects how the signals associated with the three OMAP5912 USB host ports and the OMAP5912 USB function controller can be brought out to OMAP5912 pins.

- OMAP5912 Multimedia Processor Multi-channel Buffered Serial Ports (McBSPs) Reference Guide (literature number SPRU762) describes the three multi-channel buffered serial ports (McBSPs) available on the OMAP5912 device. The OMAP5912 device provides multiple highspeed multichannel buffered serial ports (McBSPs) that allow direct interface to codecs and other devices in a system.

- **OMAP5912** Multimedia Processor Camera Interface Reference Guide (literature number SPRU763) describes two camera inerfaces implemented in the OMAP5912 multimedia processor: compact serial camera port and camera parallel interface.

- **OMAP5912** Multimedia Processor Display Interface Reference Guide (literature number SPRU764) describes the display interface of the OMAP5912 multimedia processor.

- LCD module

- LCD data conversion module

- LED pulse generator

- Display interface

- **OMAP5912 Multimedia Processor Multimedia Card (MMC/SD/SDIO)** (literature number SPRU765) describes the multimedia card (MMC) interface of the OMAP5912 multimedia processor. The multimedia card/secure data/secure digital IO (MMC/SD/SDIO) host controller provides an interface between a local host, such as a microprocessor unit (MPU) or digital signal processor (DSP), and either an MMC or SD memory card, plus up to four serial flash cards. The host controller handles MMC/SD/SDIO or serial port interface (SPI) transactions with minimal local host intervention.

- **OMAP5912 Multimedia Processor Keyboard Interface Reference Guide** (literature number SPRU766) describes the keyboard interface of the OMAP5912 multimedia processor. The MPUIO module enables direct I/O communication between the MPU (through the public TIPB) and external devices. Two types of I/O can be used: specific I/Os dedicated for 8 x 8 keyboard connection, and general-purpose I/Os.

- OMAP5912 Multimedia Processor General-Purpose Interface Reference Guide (literature number SPRU767) describes the general-purpose in-

terface of the OMAP5912 multimedia processor. There are four GPIO modules in the OMAP5912. Each GPIO peripheral controls 16 dedicated pins configurable either as input or output for general purposes. Each pin has an independent control direction set by a programmable register. The two–edge control registers configure events (rising edge, falling edge, or both edges) on an input pin to trigger interrupts or wake–up requests (depending on the system mode). In addition, an interrupt mask register masks out specified pins. Finally, the GPIO peripherals provide the set and clear capabilities on the data output registers and the interrupt mask registers. After detection, all event sources are merged and a single synchronous interrupt (per module) is generated in active mode, whereas a unique wake–up line is issued in idle mode. Eight data output lines of the GPIO3 are ORed together to generate a global output line at the OMAP5912 boundary. This global output line can be used in conjunction with the SSI to provide a CMT–APE interface to the OMAP5912.

OMAP5912 Multimedia Processor VLYNQ Serial Communications Interface Reference Guide (literature number SPRU768) describes the VLYNQ of the OMAP5912 multimedia processor.

VLYNQ is a serial communications interface that enables the extension of an internal bus segment to one or more external physical devices. The external devices are mapped into local, physical address space and appear as if they are on the internal bus of the OMAP 5912. The external devices must also have a VLYNQ interface. The VLYNQ module serializes bus transactions in one device, transfers the serialized data between devices via a VLYNQ port, and de-serializes the transaction in the external device.

OMAP5912 includes one VLYNQ module connected on OCPT2 target port and OCPI initiator port. These connections are configured via a static switch, which selects either SSI or VLYNQ module. This switch, forbids the simultaneous use of GDD/SSI and VLYNQ. The switch is controlled by the VLYNQ\_EN bit in the OMAP5912 configuration control register (CONF\_5912\_CTRL).

**OMAP5912 Multimedia Processor Pinout Reference Guide** (literature number SPRU769) provides the pinout of the OMAP5912 multimedia processor. After power-up reset, the user can change the configuration of the default interfaces. If another interface is available on top of the default, it is possible to enable a new interface for each ball by setting the corresponding 3-bit field of the associated FUNC\_MUX\_CTRL register. It is also possible to configure on-chip pullup/pulldown. This document

also describes the various power domains so that the user can apply the different interfaces seamlessly with external components.

- **OMAP5912** Multimedia Processor Window Tracer (WT) Reference Guide (literature number SPRU770) describes the window tracer module used to capture the memory transactions from four interfaces: EMIFF, EMIFS, OCP-T1, and OCP-T2. This module is located in the OMAP3.2 traffic controller (TC).

- **OMAP5912 Multimedia Processor Real-Time Clock Reference Guide** (literature number SPRUxxx) describes the real-time clock of the OMAP5912 multimedia processor. The real-time clock (RTC) block is an embedded real-time clock module directly accessible from the TIPB bus interface.

### Trademarks

OMAP and the OMAP symbol are trademarks of Texas Instruments.

# **Contents**

| 1 | Overv | view    |                                                                            | 19 |

|---|-------|---------|----------------------------------------------------------------------------|----|

| 2 | USB   | Host Co | ntroller                                                                   | 19 |

|   | 2.1   | USB O   | pen Host Controller Interface Functionality                                | 22 |

|   |       | 2.1.1   | OHCI Controller Overview                                                   | 22 |

|   | 2.2   | OMAP    | 5912 USB Host Controller Differences From OHCI Specification for USB       | 22 |

|   |       | 2.2.1   | Power Switching Output Pins Not Supported                                  | 22 |

|   |       | 2.2.2   | Overcurrent Protection Input Pins Not Supported                            | 22 |

|   |       | 2.2.3   | HMC_MODE and Top-Level Pin Multiplexing and OHCI Registers                 | 23 |

|   |       | 2.2.4   | No Ownership Change Interrupt                                              | 23 |

|   | 2.3   | OMAP    | 5912 Implementation of OHCI Specification for USB                          | 23 |

|   |       | 2.3.1   | Isochronous Transmit Descriptor (TD) OFFSETX/PSWX Values                   | 23 |

|   |       | 2.3.2   | OMAP5912 USB Host Controller Endpoint Descriptor (ED) List Head            |    |

|   |       |         | Pointers                                                                   |    |

|   |       | 2.3.3   | OHCI USB Suspend State                                                     |    |

|   | 2.4   |         | ost Controller Registers                                                   |    |

|   | 2.5   |         | ost Controller Reserved Registers and Reserved Bit Fields                  |    |

|   | 2.6   |         | ost Controller Registers, USB Reset, and USB Clocking                      |    |

|   | 2.7   |         | nterrupts                                                                  |    |

|   |       | 2.7.1   | OHCI Scheduling Overrun Interrupt                                          |    |

|   |       | 2.7.2   | OHCI HCDONEHEAD Writeback Interrupt                                        |    |

|   |       | 2.7.3   | OHCI Start Of Frame Interrupt                                              |    |

|   |       | 2.7.4   | OHCI Resume Detect Interrupt                                               |    |

|   |       | 2.7.5   | OHCI Unrecoverable Error Interrupt                                         |    |

|   |       | 2.7.6   | OHCI Frame Number Overflow                                                 |    |

|   |       | 2.7.7   | OHCI Root Hub Status Change                                                |    |

|   |       | 2.7.8   | OHCI Ownership Change Interrupt                                            |    |

|   | 2.8   |         | ost Controller Access to System Memory                                     |    |

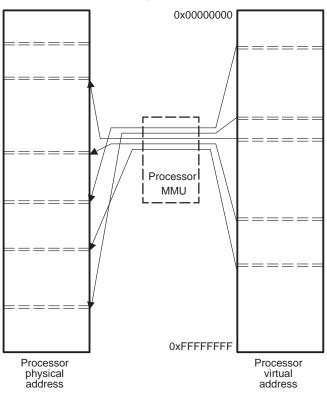

|   | 2.9   | •       | al Addressing                                                              |    |

|   | 2.10  |         | Coherency in OHCI Data Structures and Data Buffers                         |    |

|   | 2.11  |         | Bus Addressing and OHCI Data Structure Pointers                            | 64 |

|   |       | 2.11.1  | MPUVAtoPA()—MPU Virtual Address to Physical Address                        | ~~ |

|   |       | 0.44.0  | Conversion Function                                                        | 65 |

|   |       | 2.11.2  | PAtoMPUVA()—Physical Address to MPU Virtual Address<br>Conversion Function | 65 |

|   |       |         |                                                                            | 00 |

| Contents |

|----------|

|----------|

|   | <ol> <li>2.12</li> <li>2.13</li> <li>2.14</li> <li>2.15</li> <li>2.16</li> <li>2.17</li> <li>2.18</li> <li>2.19</li> </ol> | OMAPS<br>OCPI R<br>USB Ho<br>USB Ho<br>USB Ho | Pointers<br>5912 OCPI Bus and the USB Host Controller<br>Dest Controller Clock Control<br>Dest Controller Hardware Reset<br>Dest Controller OHCI Reset<br>Dest Controller Power Management<br>Clocking | . 65<br>. 66<br>. 66<br>. 66<br>. 67<br>. 67 |

|---|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3 |                                                                                                                            |                                               | Controller                                                                                                                                                                                             |                                              |

|   | 3.1                                                                                                                        |                                               | evice Controller Registers                                                                                                                                                                             |                                              |

|   |                                                                                                                            | 3.1.1                                         | EPn_TX[14:12].EPn_TX_SIZE: Transmit Endpoint n Size                                                                                                                                                    |                                              |

|   | 3.2                                                                                                                        |                                               | evice Transactions                                                                                                                                                                                     |                                              |

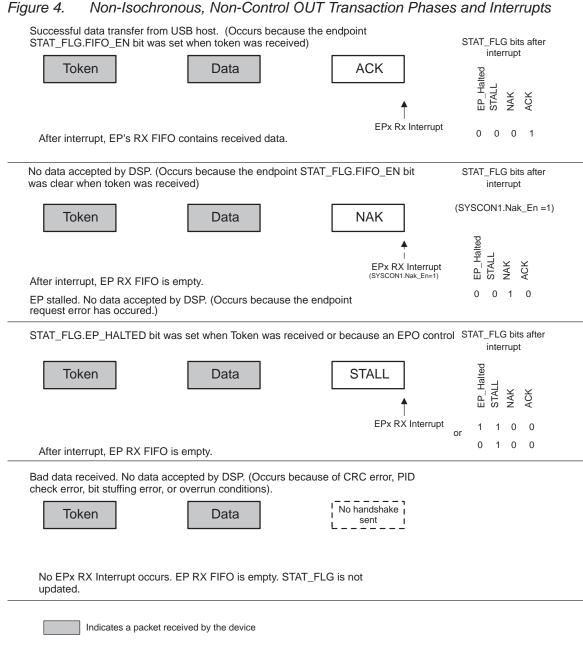

|   | 3.3                                                                                                                        |                                               | ochronous, Non-Setup OUT (USB HOST -> MPU) Transactions                                                                                                                                                |                                              |

|   |                                                                                                                            | 3.3.1                                         | Non-Isochronous, Non-Control OUT Endpoint Handshaking Conditions                                                                                                                                       |                                              |

|   |                                                                                                                            |                                               | Acknowledged Transactions (ACK)                                                                                                                                                                        |                                              |

|   |                                                                                                                            |                                               | Non-Acknowledged Transactions (NAK)                                                                                                                                                                    |                                              |

|   |                                                                                                                            | 3.3.2                                         | Non-Isochronous, Non-Control OUT Transaction Error Conditions                                                                                                                                          |                                              |

|   |                                                                                                                            |                                               | STALLed Transactions                                                                                                                                                                                   |                                              |

|   |                                                                                                                            |                                               | Packet Errors                                                                                                                                                                                          |                                              |

|   |                                                                                                                            |                                               | Sequence Bit Errors                                                                                                                                                                                    |                                              |

|   | 0.4                                                                                                                        | 3.3.3                                         | Non-Isochronous, Non-Control OUT Endpoint FIFO Error Conditions                                                                                                                                        |                                              |

|   | 3.4                                                                                                                        |                                               | ochronous IN (MPU->USB HOST) Transactions                                                                                                                                                              |                                              |

|   |                                                                                                                            | 3.4.1                                         | Non-Isochronous IN Endpoint Handshaking                                                                                                                                                                |                                              |

|   |                                                                                                                            |                                               | Acknowledged Transactions (ACK)                                                                                                                                                                        |                                              |

|   |                                                                                                                            | 040                                           | Non-Acknowledged Transactions (NAK)                                                                                                                                                                    |                                              |

|   |                                                                                                                            | 3.4.2                                         | Non-Isochronous IN Transaction Error Conditions                                                                                                                                                        |                                              |

|   |                                                                                                                            |                                               | Packet Errors                                                                                                                                                                                          |                                              |

|   |                                                                                                                            | 3.4.3                                         | Non-Isochronous IN Endpoint FIFO Error Conditions                                                                                                                                                      |                                              |

|   | 3.5                                                                                                                        |                                               | nous OUT (USB HOST-> MPU) Transactions                                                                                                                                                                 |                                              |

|   | 3.0                                                                                                                        | 3.5.1                                         | Isochronous OUT Endpoint Handshaking                                                                                                                                                                   |                                              |

|   |                                                                                                                            | 3.5.2                                         | Isochronous OUT Transaction Error Conditions                                                                                                                                                           |                                              |

|   |                                                                                                                            | 3.5.2                                         | Isochronous OUT Endpoint FIFO Error Conditions                                                                                                                                                         |                                              |

|   | 3.6                                                                                                                        |                                               | nous IN (MPU->USB HOST) Transactions                                                                                                                                                                   |                                              |

|   | 5.0                                                                                                                        | 3.6.1                                         | Isochronous IN Endpoint Handshaking                                                                                                                                                                    |                                              |

|   |                                                                                                                            | 3.6.2                                         | Isochronous IN Transaction Error Conditions                                                                                                                                                            |                                              |

|   |                                                                                                                            | 3.6.3                                         | Isochronous IN Endpoint FIFO Error Conditions                                                                                                                                                          |                                              |

|   | 3.7                                                                                                                        |                                               | Transfers on Endpoint 0                                                                                                                                                                                |                                              |

|   | 0.7                                                                                                                        | 3.7.1                                         | Autodecoded Control Write Transfers                                                                                                                                                                    |                                              |

|   |                                                                                                                            | 0.7.1                                         | Autodecoded Control Write Transfer Handshaking                                                                                                                                                         |                                              |

|   |                                                                                                                            |                                               | Autodecoded Control Write Transfer Error Conditions                                                                                                                                                    |                                              |

|   |                                                                                                                            |                                               |                                                                                                                                                                                                        | 120                                          |

|      | 3.7.2 | Autodecoded Control Read Transfers                      |     |

|------|-------|---------------------------------------------------------|-----|

|      |       | Autodecoded Control Read Transfer Handshaking           | 128 |

|      |       | Autodecoded Control Read Transfer Error Conditions      | 128 |

|      | 3.7.3 | Non-Autodecoded Control Write Transfers                 | 129 |

|      |       | Specific MPU Required Actions                           |     |

|      |       | Non-Autodecoded Control Write Transfer Handshaking      |     |

|      |       | Non-Autodecoded Control Write Transfer Error Conditions |     |

|      | 3.7.4 | Non-Autodecoded Control Read Transfers                  |     |

|      |       | Non-Autodecoded Control Read Transfer Handshaking       |     |

|      |       | Non-Autodecoded Control Read Transfer Error Conditions  |     |

|      | 3.7.5 | Autodecoded Versus Non-Autodecoded Control Requests     |     |

|      | 3.7.6 | Note on Control Transfers Data Stage Length             |     |

| 3.8  |       | evice Initialization                                    |     |

| 3.9  |       | ng for Transfers                                        |     |

| 3.10 |       | evice Interrupt Service Routine (ISR) Flowcharts        |     |

| 3.11 | •     | ant Note on USB Device Interrupts                       |     |

| 3.12 |       | g General USB Device Interrupt                          |     |

| 3.13 |       | nterrupt Handler                                        |     |

| 3.14 |       | nt 0 RX Interrupt Handler                               |     |

| 3.15 |       | nt 0 TX Interrupt Handler                               |     |

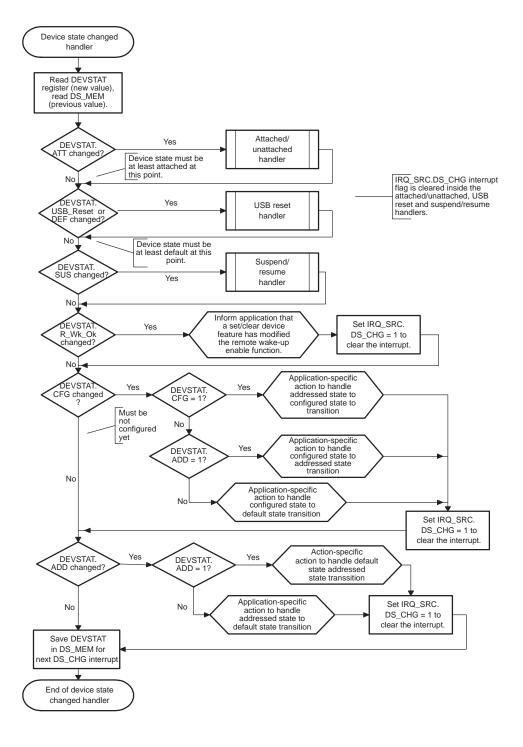

| 3.16 |       | States Changed Handler                                  |     |

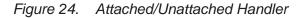

| 3.17 |       | States Attached/Unattached Handler                      |     |

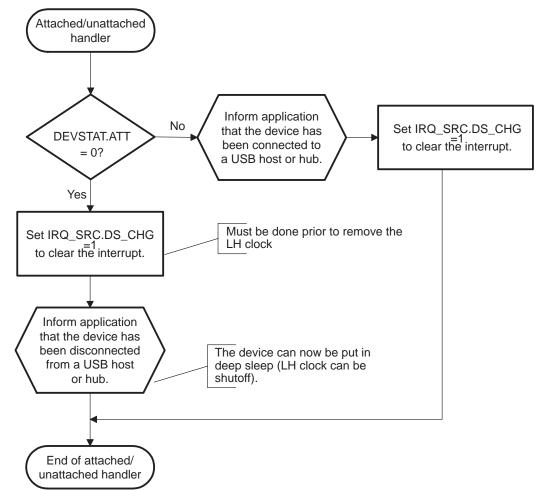

| 3.18 |       | State Configuration Changed Handler                     |     |

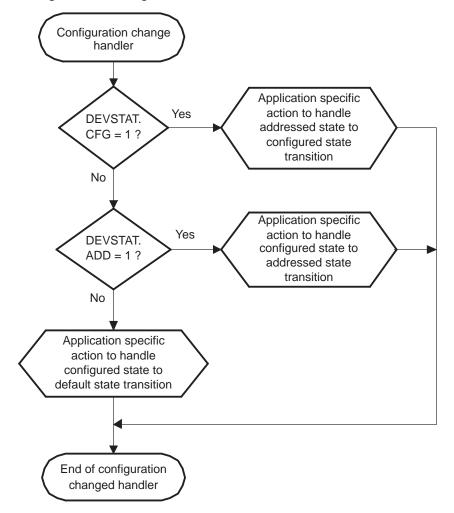

| 3.19 |       | State Address Changed Handler                           |     |

| 3.20 |       | evice Reset Interrupt Handler                           |     |

| 3.21 |       | nd/Resume Interrupt Handler                             |     |

| 3.22 |       | Non-ISO Endpoint-Specific Interrupt                     |     |

| 3.23 |       | O, Non-Control OUT Endpoint Receive Interrupt Handler   |     |

| 3.24 |       | O, Non-Control IN Endpoint Transmit Interrupt Handler   |     |

| 3.25 |       | terrupt Handler                                         |     |

| 3.26 |       | ary of USB Device Controller Interrupts                 |     |

|      |       | USB Device Controller Clock Control                     |     |

|      |       | USB Device Controller Hardware Reset                    |     |

| 3.27 | DMA O | peration                                                |     |

|      |       | Receive DMA Channels Overview                           |     |

|      |       | Non-Isochronous OUT (USB HOST -> MPU) DMA Transactions  |     |

|      |       | End of Transfer Interrupt (IRQ_SRC.RXn_EOT)             |     |

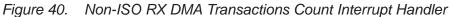

|      |       | Transaction Count Interrupt (IRQ_SRC.RXn_CNT)           |     |

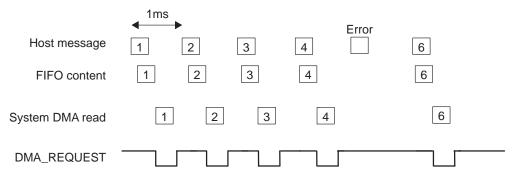

|      |       | Isochronous OUT (USB HOST -> MPU) DMA Transactions      |     |

|      |       | Transmit DMA Channels Overview                          |     |

|      |       | Non-Isochronous IN (MPU -> USB HOST) DMA Transactions   | 186 |

|      |       | Isochronous IN (USB HOST -> MPU) DMA Transactions       |     |

|      |       | Important Note on DMA Requests                          |     |

|      |       | Note on DMA Channels Deconfiguration                    |     |

| 3.28 | Power | Management                                              | 192 |

|      |       |                                                         |     |

*OMAP5912* 11

| 4 | USB | OTG Controller                                                         |

|---|-----|------------------------------------------------------------------------|

|   | 4.1 | OTG Controller Features                                                |

|   | 4.2 | OTG Controller Registers 195                                           |

|   |     | 4.2.1 OTG Clock and Reset Requirements 223                             |

|   |     | 4.2.2 OTG Controller Power Management 224                              |

|   |     | 4.2.3 OTG Controller Initialization 225                                |

|   |     | 4.2.4 OTG Controller Interrupt Handler and Related Software            |

|   |     | 4.2.5 Typical SRP and HNP Events                                       |

|   |     | 4.2.6 System-Level OTG Considerations                                  |

|   | 4.3 | Pin Multiplexing                                                       |

|   | 4.4 | Selecting and Configuring USB Connectivity                             |

|   |     | 4.4.1 Select Desired USB Functionality 244                             |

|   |     | 4.4.2 Select How USB Functionality Is Multiplexed to OMAP5912 Pins 245 |

|   |     | Select USB and/or USB OTG Transceiver Type                             |

|   |     | Determine Proper Top-level Multiplexing Settings                       |

|   |     | Determine OTG Module Control Register Settings                         |

|   | 4.5 | Transceiver Signaling Types                                            |

|   |     | USB Transceiver Unidirectional Signaling                               |

|   |     | USB Transceiver 3-Wire Bidirectional Signaling                         |

|   |     | USB Transceiver 4-Wire Bidirectional Signaling                         |

|   | 4.6 | USB OTG External Connectivity 264                                      |

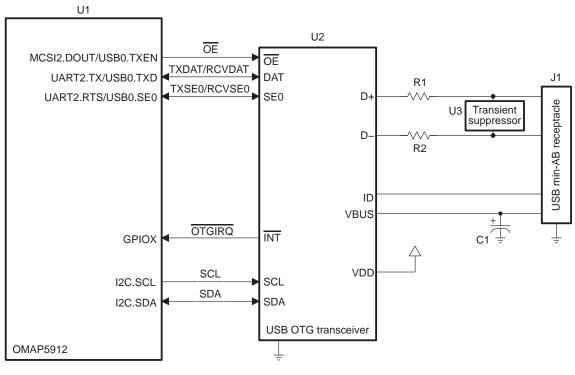

|   |     | Pin Group 0 OTG 265                                                    |

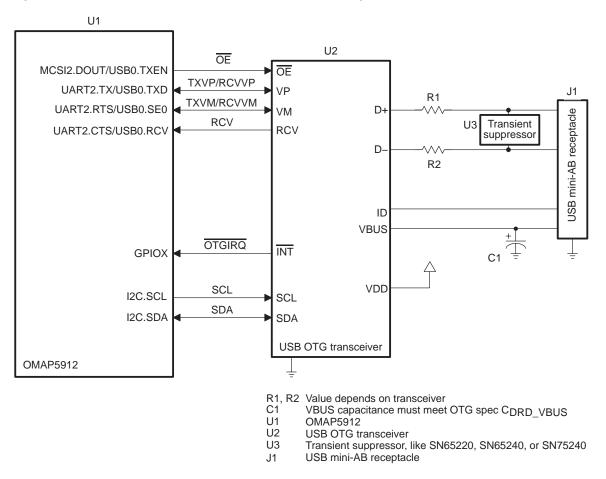

|   |     | OTG on Pin Group 1 Using 3-Wire OTG Transceiver                        |

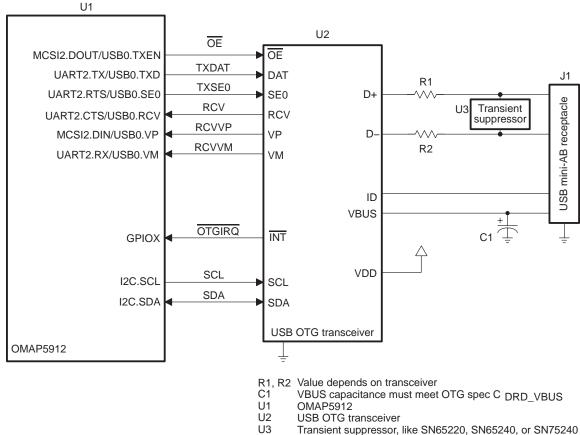

|   |     | OTG on Pin Group 1 Using 4-Wire OTG Transceiver                        |

|   |     | OTG on Pin Group 1 OTG Using 6-Wire OTG Transceiver                    |

|   |     | OTG on Alternate Pin Group 2 Using 3-Wire OTG Transceiver              |

|   |     | OTG on Alternate Pin Group 2 Using 4-Wire OTG Transceiver              |

|   |     | OTG on Alternate Pin Group 2 Using 6-Wire OTG Transceiver              |

|   | 4.7 | Host Controller Connectivity With USB Transceivers                     |

|   |     | USB Host Connections Using the OMAP5912 Integrated                     |

|   |     | USB Transceiver                                                        |

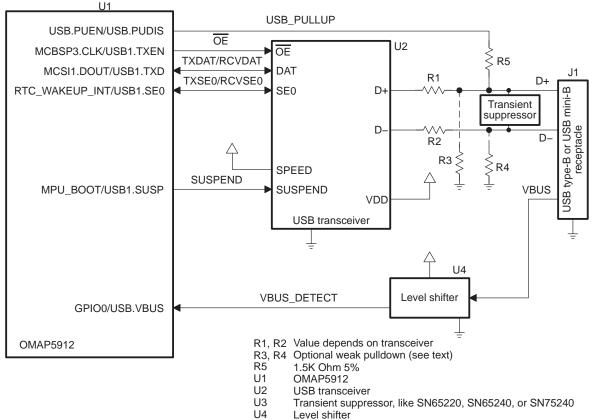

|   |     | Pin Group 1 USB Host Using 3-Wire USB Transceiver                      |

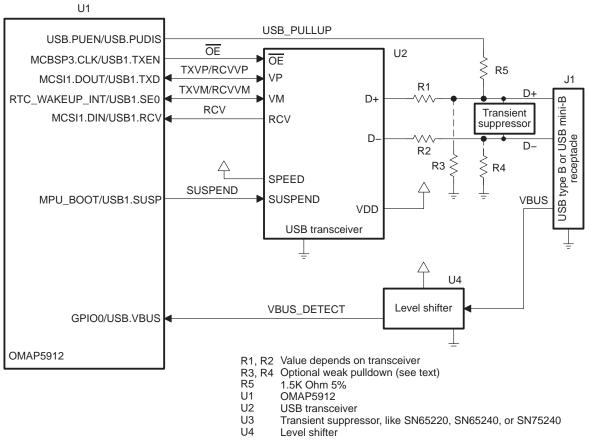

|   |     | Pin Group 1 USB Host Using 4-Wire USB Transceiver                      |

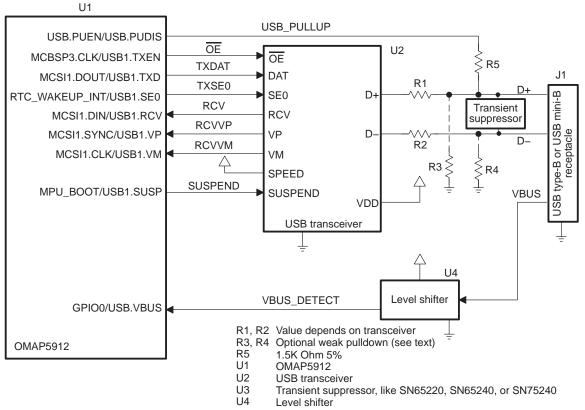

|   |     | Pin Group 1 USB Host Using 6-Wire USB Transceiver                      |

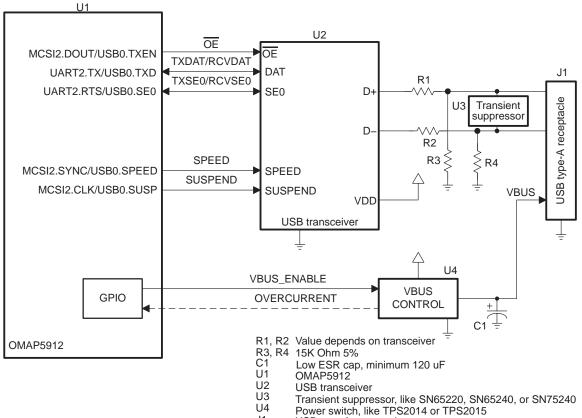

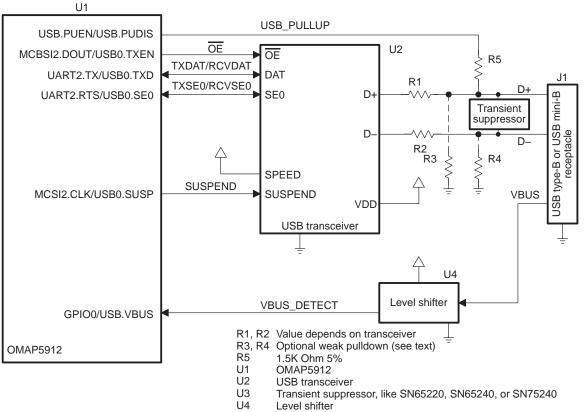

|   |     | Pin Group 2 USB Host Using 3-Wire USB Transceiver                      |

|   |     | Pin Group 2 USB Host Using 4-Wire USB Transceiver                      |

|   |     | Pin Group 2 USB Host Using 6-Wire USB Transceiver                      |

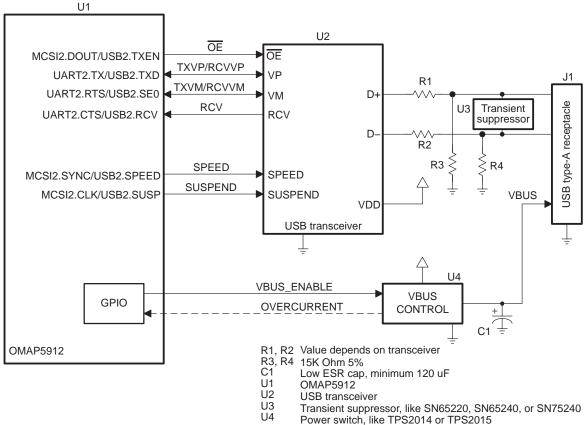

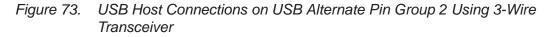

|   |     | USB Host on USB Alternate Pin Group 2, 3-Wire USB Transceiver          |

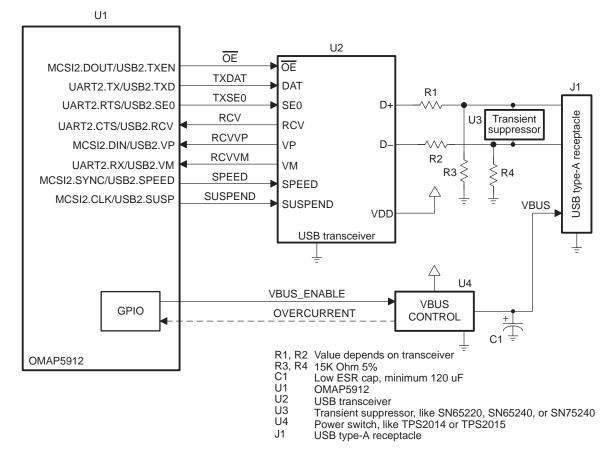

|   |     | USB Host on USB Alternate Pin Group 2, 4-Wire USB Transceiver          |

|   |     | USB Host on USB Alternate Pin Group 2, 6-Wire USB Transceiver          |

| 4.8  | USB Function Controller Connectivity With USB Transceivers                 |

|------|----------------------------------------------------------------------------|

|      | Pin Group 0 USB Device                                                     |

|      | Pin Group 1 USB Device Using 3-Wire USB Transceiver                        |

|      | Pin Group 1 USB Device Using 4-Wire USB Transceiver                        |

|      | Pin Group 1 USB Device Using 6-Wire USB Transceiver                        |

|      | USB Device on USB Alternate Pin Group 2, 3-Wire USB Transceiver 296        |

|      | USB Device on USB Alternate Pin Group 2, 4-Wire USB Transceiver 298        |

|      | USB Device on USB Alternate Pin Group 2, 6-Wire USB Transceiver 300        |

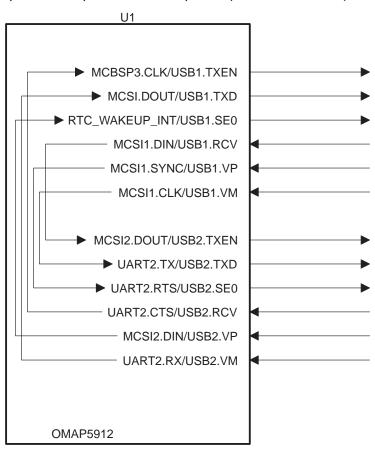

| 4.9  | Onboard Transceiverless Connection Using OMAP5912 Transceiverless Link 302 |

|      | USB Host With Transceiverless Link Logic (TXD/TXSE0)                       |

|      | USB Device With Transceiverless Link Logic (TXD/TXSE0)                     |

|      | USB Host With Transceiverless Link Logic (TXVP/TXVM)                       |

| 4.10 | Other Pin Connectivity Controlled by USB Signal Multiplexing               |

|      | Pin Group 1 to Pin Group 2 Internal Loopback                               |

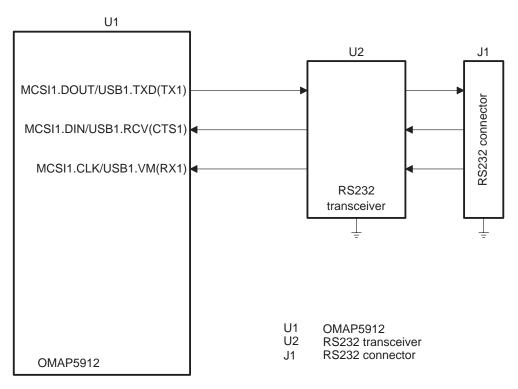

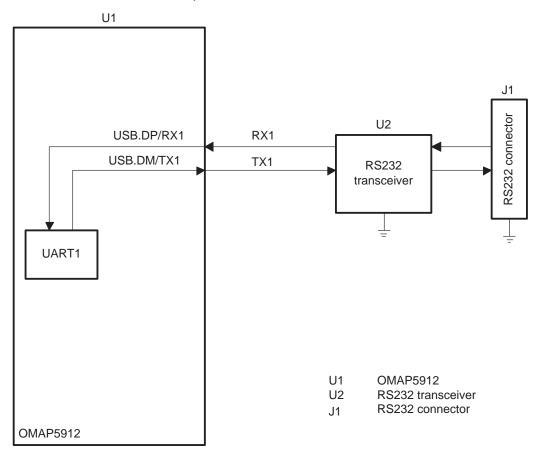

|      | UART 1 on USB Pin Group 2 Pins 310                                         |

|      | I2C on Pin Group 0 311                                                     |

|      | UART1 on Pin Group 0                                                       |

| 4.11 | Conflicts Between USB Signal Multiplexing and Top-Level Multiplexing       |

| 4.12 | OMAP5912 USB Hardware Considerations 313                                   |

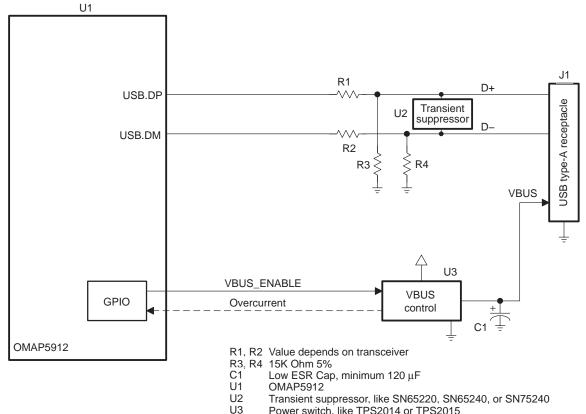

|      | 4.12.1 VBUS Power Switching for USB Type A Host Receptacles                |

|      | 4.12.2 Transient Suppression for USB Connectors 313                        |

|      | 4.12.3 VBUS Monitoring for USB Function Controller                         |

|      | 4.12.4 USB D+ Pullup Enable for USB Function Controller                    |

|      | 4.12.5 MPU_BOOT Signal Sharing 314                                         |

|      | 4.12.6 USB D+, D- Pulldown for USB Function Controller                     |

# Figures

| 1  | USB Host Controller                                                    | 21  |

|----|------------------------------------------------------------------------|-----|

| 2  | Relationships Between Virtual Address Physical Address                 |     |

| 3  | Little Endian and Big Endian Formats                                   |     |

| 4  | Non-Isochronous, Non-Control OUT Transaction Phases and Interrupts     |     |

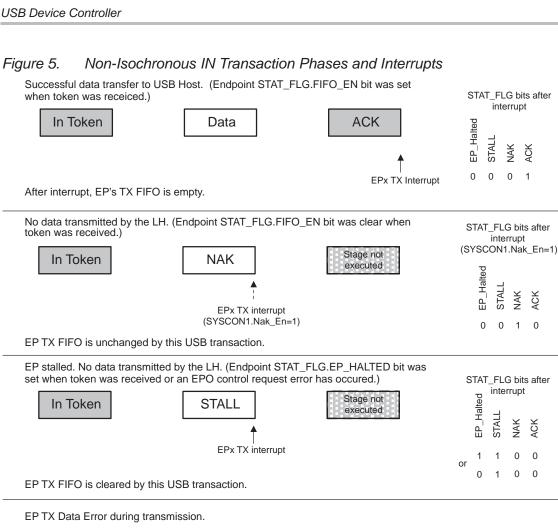

| 5  | Non-Isochronous IN Transaction Phases and Interrupts                   |     |

| 6  | Isochronous OUT Transaction Phases and Interrupts                      |     |

| 7  | Isochronous IN Transaction Phases and Interrupts                       |     |

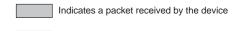

| 8  | Stages and Transaction Phases of Autodecoded Control Transfers         |     |

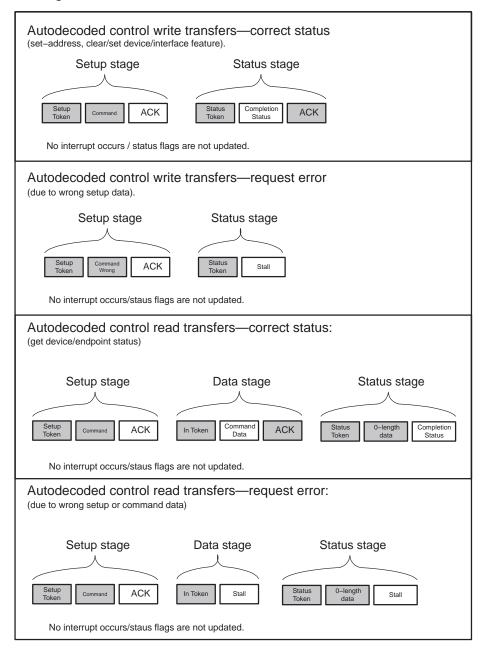

| 9  | Stages and Transaction Phases of Non-Autodecoded Control Transfers     |     |

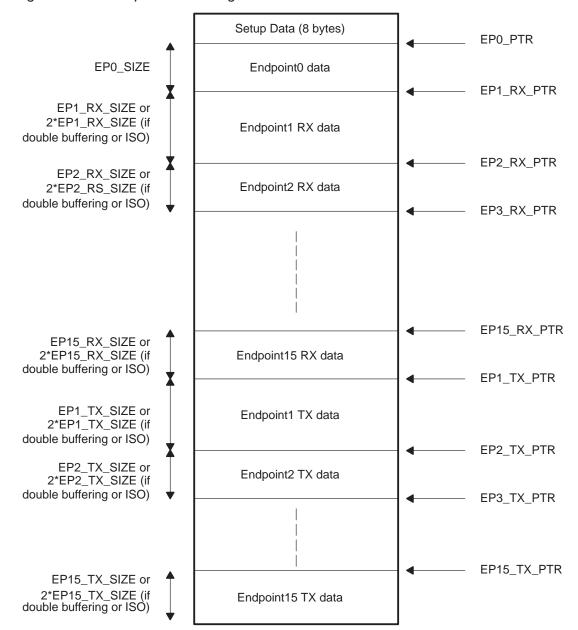

| 10 | Example of RAM Organization                                            |     |

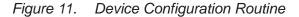

| 11 | Device Configuration Routine                                           |     |

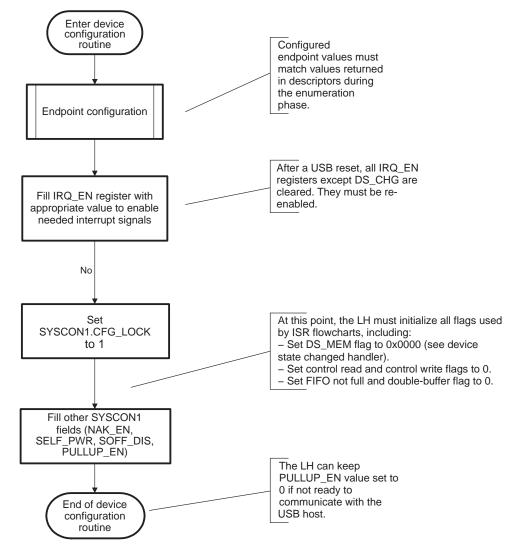

| 12 | Endpoint Configuration Routine                                         | 141 |

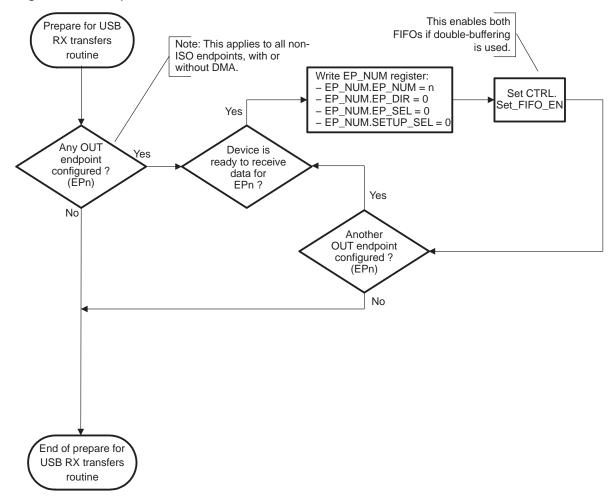

| 13 | Prepare for USB RX Transfers Routine                                   | 143 |

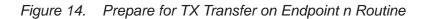

| 14 | Prepare for TX Transfer on Endpoint n Routine                          | 144 |

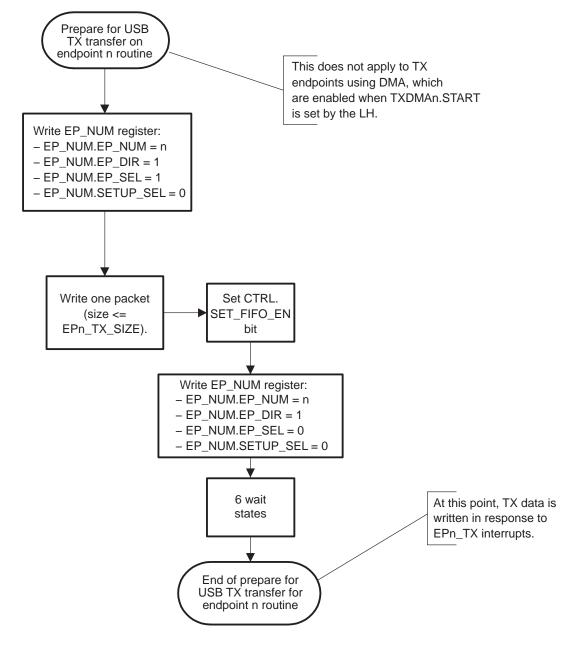

| 15 | General USB Interrupt ISR Source Parsing Flowchart                     | 147 |

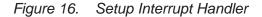

| 16 | Setup Interrupt Handler                                                | 149 |

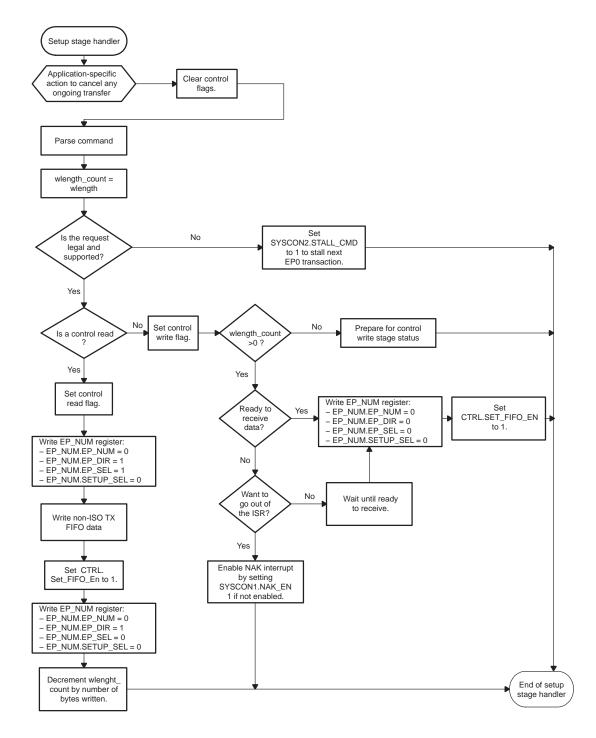

| 17 | Parse Command Routine (Setup Stage Control Transfer Request)           | 150 |

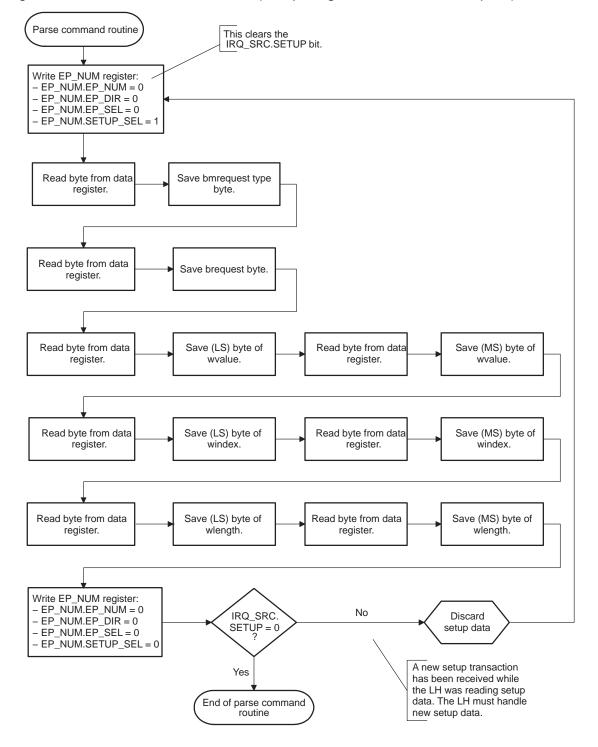

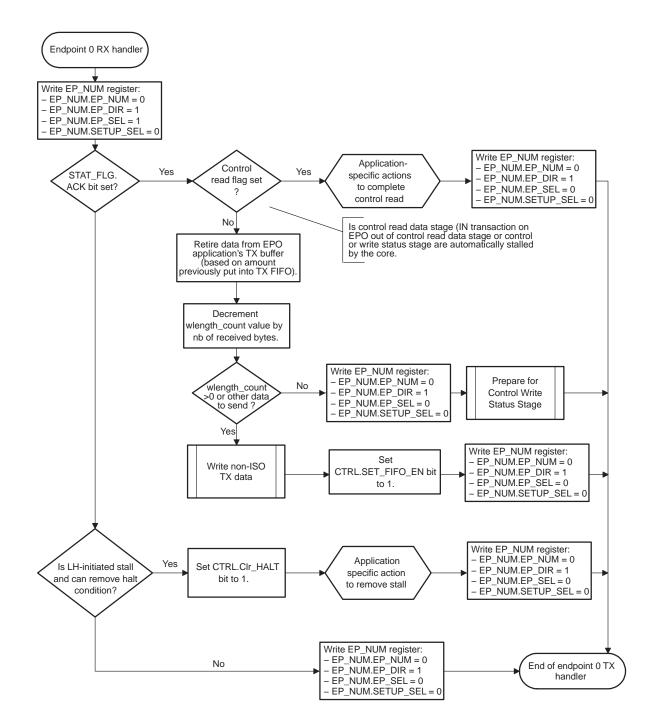

| 18 | Endpoint 0 RX Interrupt Handler                                        | 152 |

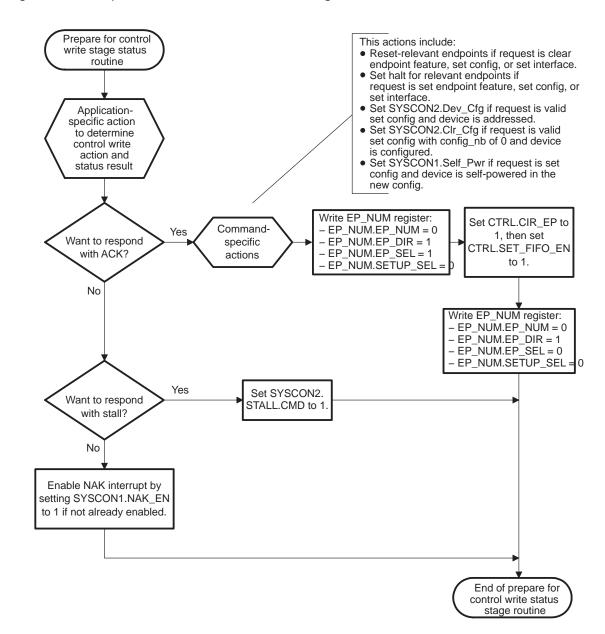

| 19 | Prepare for Control Write Status Stage Routine                         | 153 |

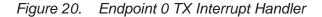

| 20 | Endpoint 0 TX Interrupt Handler                                        |     |

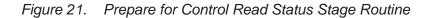

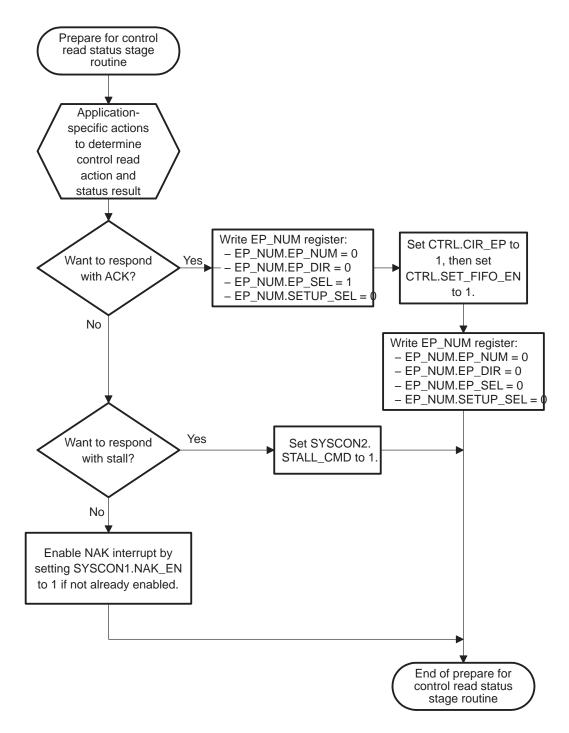

| 21 | Prepare for Control Read Status Stage Routine                          | 156 |

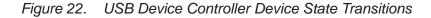

| 22 | USB Device Controller Device State Transitions                         |     |

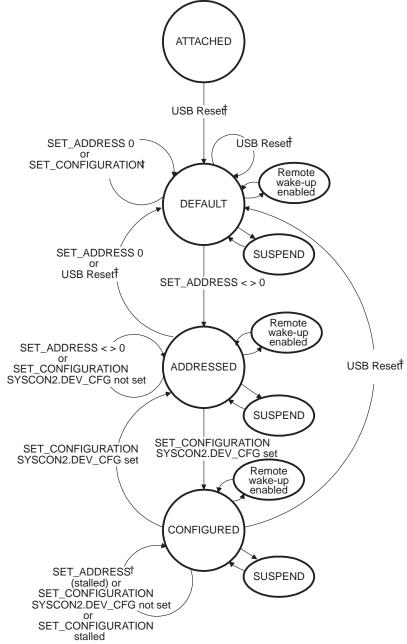

| 23 | Typical Operation for USB Device State Changed Interrupt Handler       |     |

| 24 | Attached/Unattached Handler                                            |     |

| 25 | Configuration Changed Handler                                          |     |

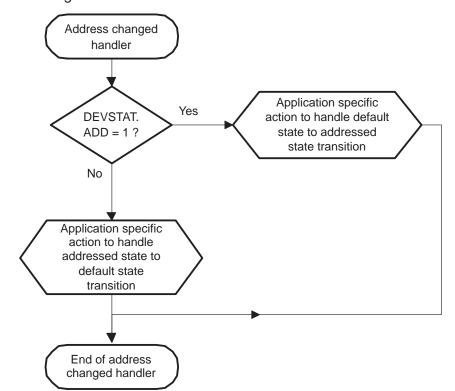

| 26 | Address Changed Handler                                                |     |

| 27 | USB Device Reset Handler Flowchart                                     |     |

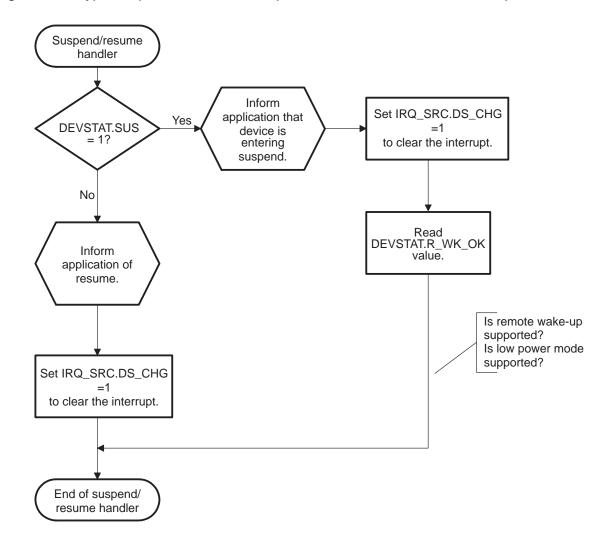

| 28 | Typical Operation for USB Suspend/Resume General USB Interrupt Handler |     |

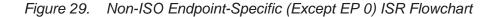

| 29 | Non-ISO Endpoint-Specific (Except EP 0) ISR Flowchart                  |     |

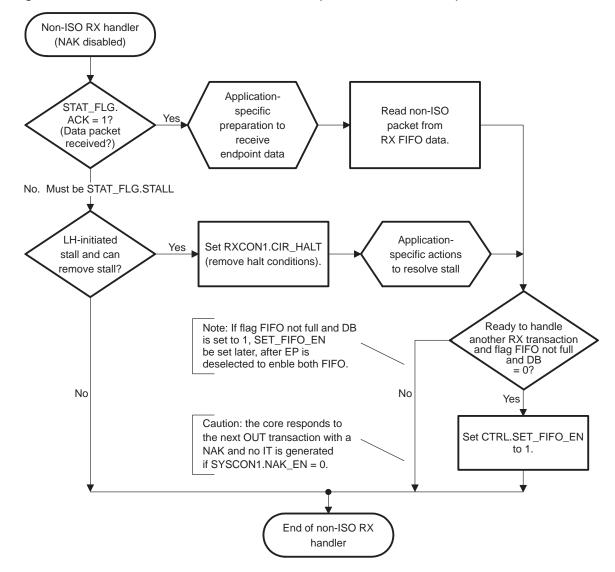

| 30 | Non-Isochronous Non-Control Endpoint Receive Interrupt Handler         |     |

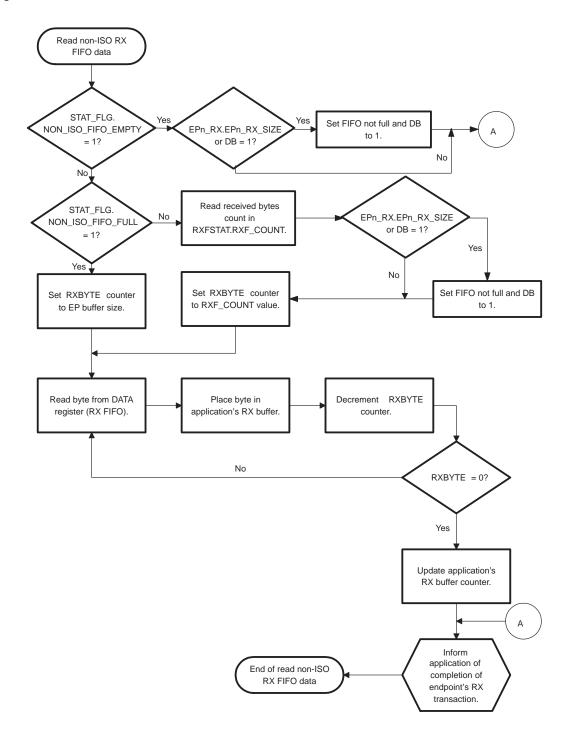

| 31 | Read Non-Isochronous RX FIFO Data Flowchart                            |     |

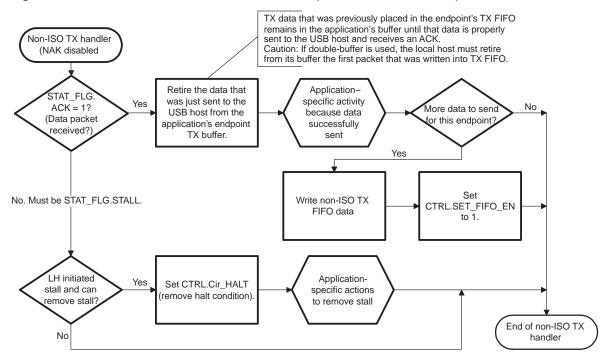

| 32 | Non-Isochronous Non-Control Endpoint Transmit Interrupt Handler        |     |

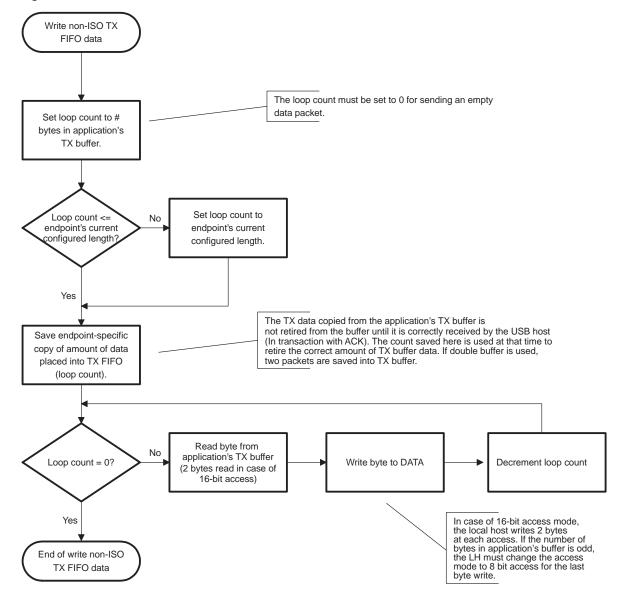

| 33 | Write Non-Isochronous TX FIFO Data Flowchart                           |     |

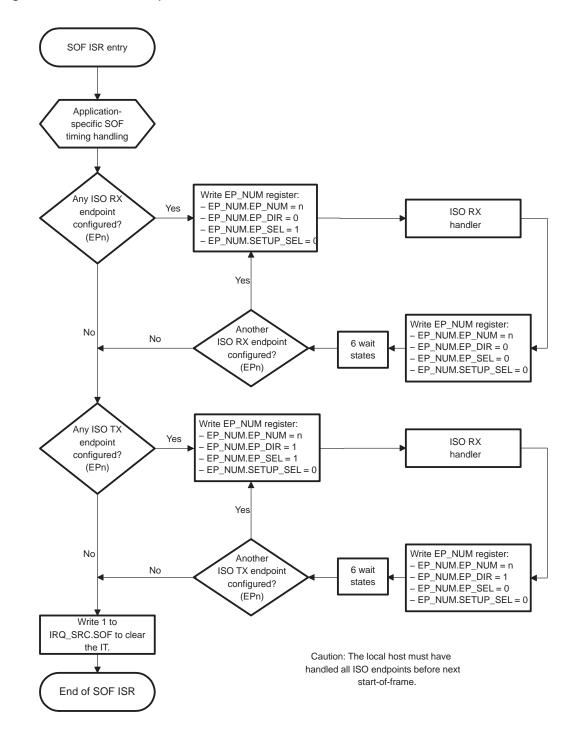

| 34 | SOF Interrupt Handler Flowchart                                        |     |

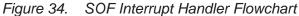

| 35 | Read Isochronous RX FIFO Data Flowchart                                |     |

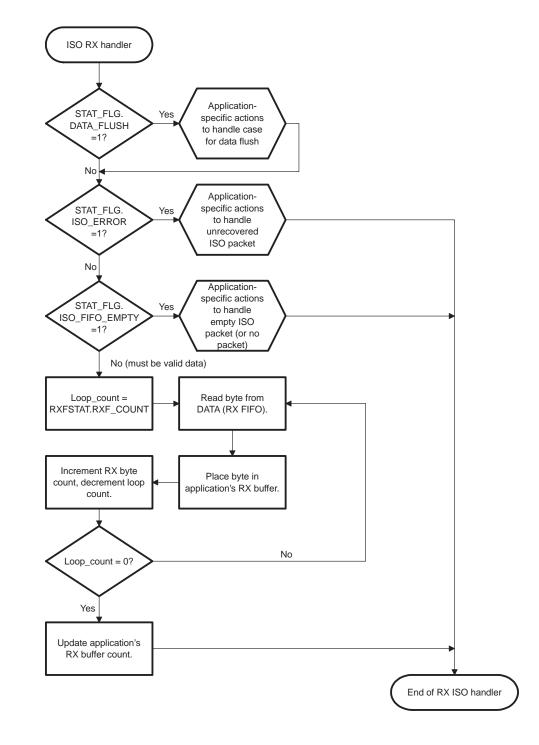

| 36 | Write Isochronous TX FIFO Data Flowchart                               | 176 |

14 *OMAP5912*

SPRU761A

\_

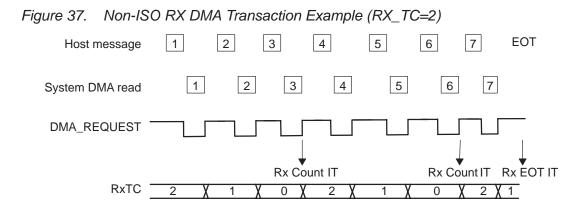

| 37 | Non-ISO RX DMA Transaction Example (RX_TC=2)                                            | 180 |

|----|-----------------------------------------------------------------------------------------|-----|

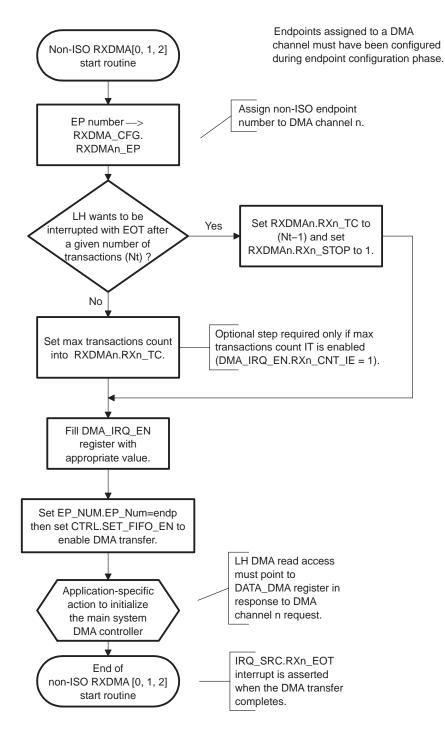

| 38 | Non-ISO RX DMA Start Routine                                                            | 181 |

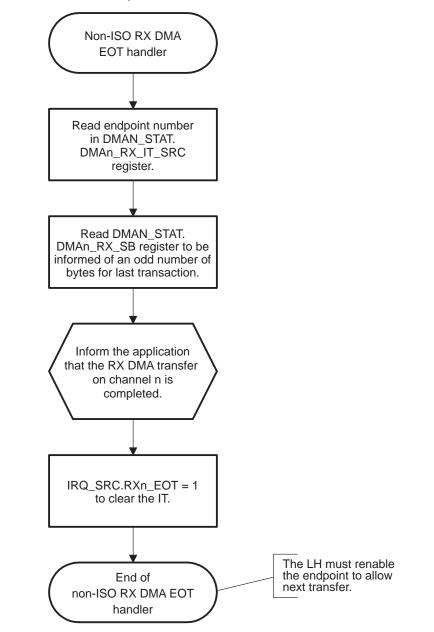

| 39 | Non-ISO RX DMA EOT Interrupt Handler                                                    | 182 |

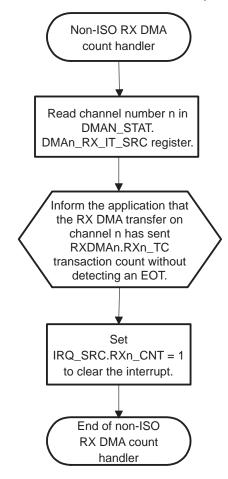

| 40 | Non-ISO RX DMA Transactions Count Interrupt Handler                                     | 183 |

| 41 | ISO RX DMA Transaction                                                                  | 184 |

| 42 | ISO RX DMA Start Routine                                                                | 185 |

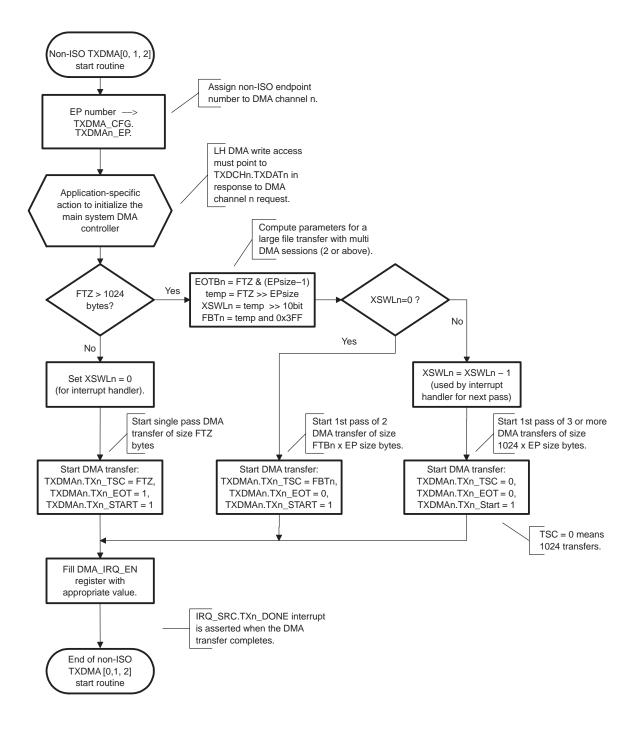

| 43 | Non-ISO TX DMA Start Routine                                                            | 187 |

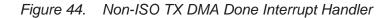

| 44 | Non-ISO TX DMA Done Interrupt Handler                                                   | 188 |

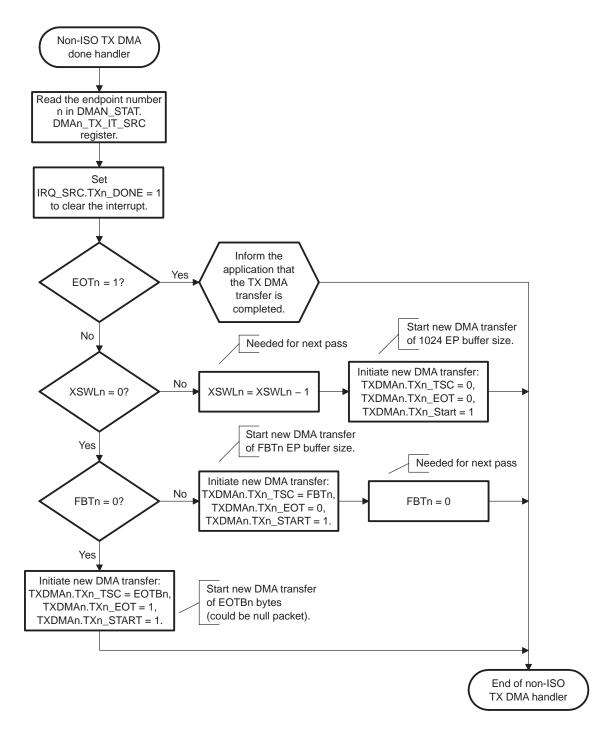

| 45 | ISO TX DMA Start Routine                                                                | 190 |

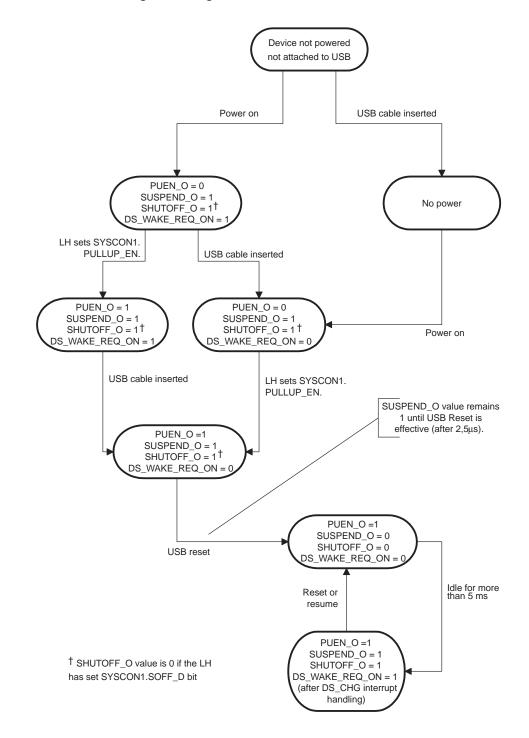

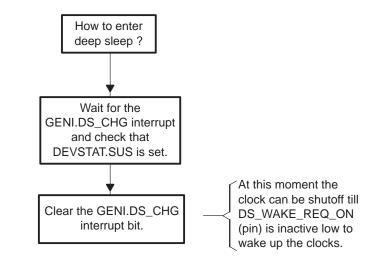

| 46 | Power Management Signal Values                                                          | 193 |

| 47 | Power Management Flowchart                                                              | 194 |

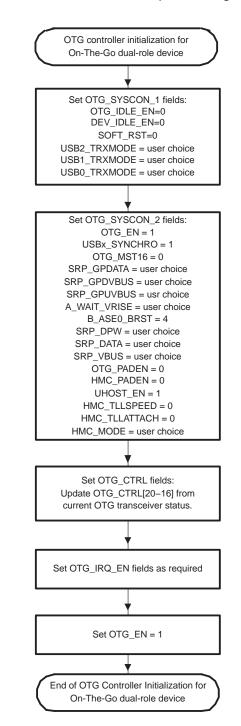

| 48 | OTG Controller Initialization When Implementing an OTG Dual-Role Device                 | 226 |

| 49 | OTG Controller Initialization When Not Implementing an OTG Dual-Role Device             | 228 |

| 50 | OTG Interrupt Handler                                                                   | 230 |

| 51 | OTG Driver Switch Handler                                                               | 232 |

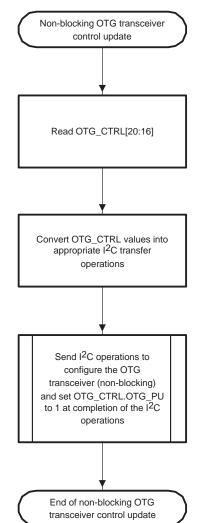

| 52 | OTG Transceiver I2C Control Handler                                                     | 234 |

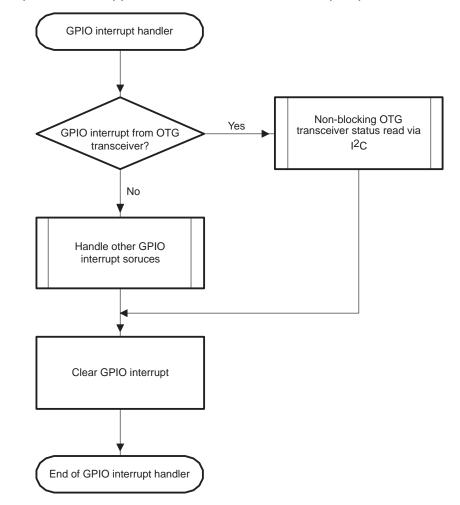

| 53 | GPIO Interrupt Handler Support for OTG Transceiver Interrupt Input                      | 235 |

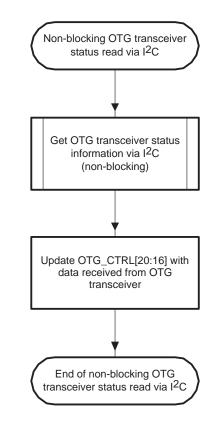

| 54 | OTG Transceiver Status Read                                                             | 236 |

| 55 | OMAP5912 OTG Controller Response To SRP When Acting as a Default-A Dual-Role OTG Device | 237 |

| 56 | OMAP5912 OTG Controller SRP Generation When Acting as a Default-A Dual-Role OTG Device  | 238 |

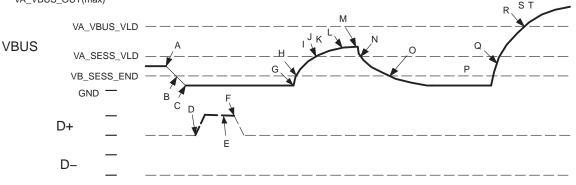

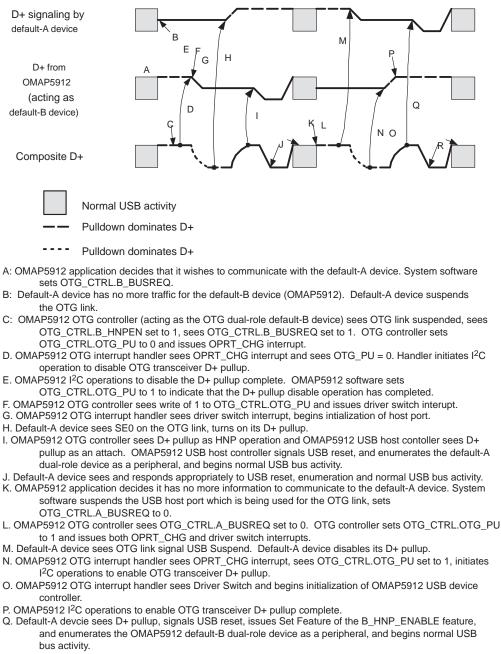

| 57 | OMAP5912 OTG Controller HNP Events When Acting as a Default-A Dual-Role OTG Device      |     |

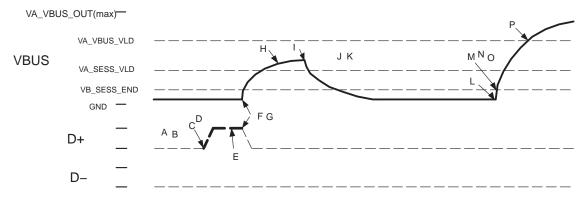

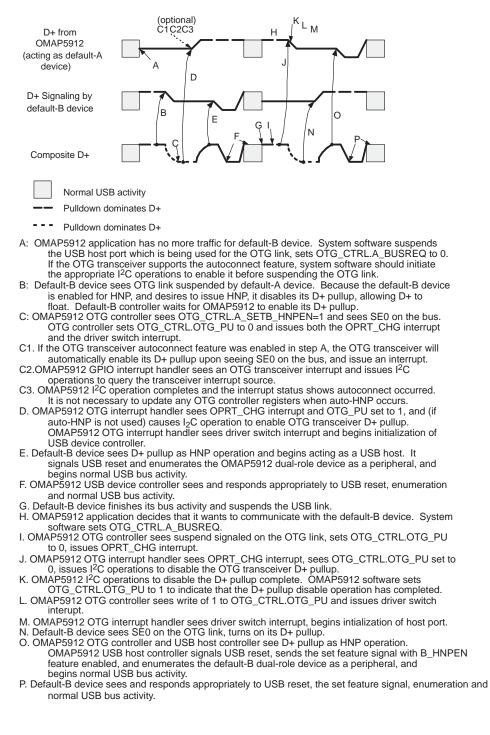

| 58 | OMAP5912 OTG Controller HNP Events When Acting as a Default-B<br>Dual-Role OTG Device   |     |

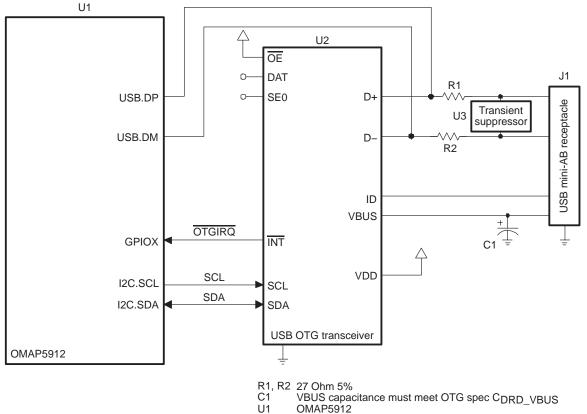

| 59 | OTG on USB Pin Group 0                                                                  |     |

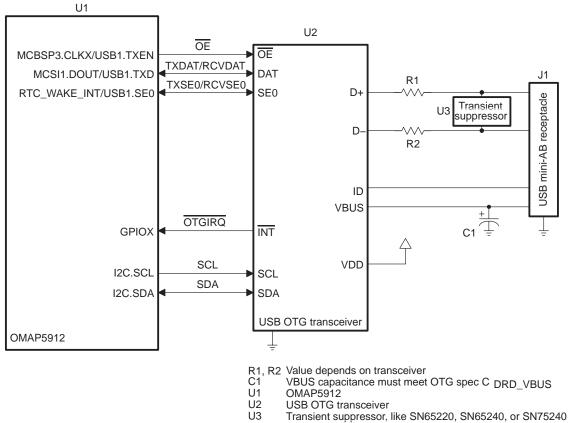

| 60 | OTG on USB Pin Group 1 Using 3-Wire OTG Transceiver                                     |     |

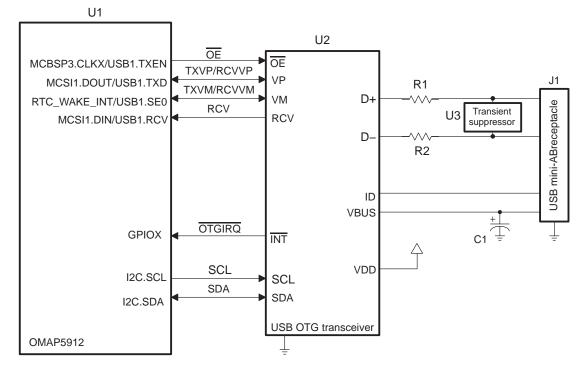

| 61 | OTG on USB Pin Group 1 Using 4-Wire OTG Transceiver                                     |     |

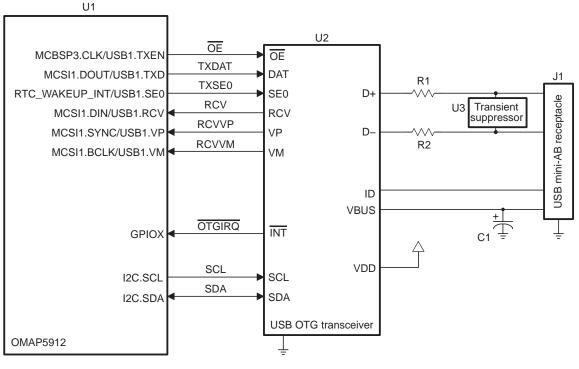

| 62 | OTG on USB Pin Group 1 Using 6-Wire OTG Transceiver                                     |     |

| 63 | OTG on USB Alternate Pin Group 2 Using 3-Wire OTG Transceiver                           |     |

| 64 | OTG on USB Alternate Pin Group 2 Using 4-Wire OTG Transceiver                           |     |

| 65 | OTG on USB Alternate Pin Group 2 Using 6-Wire OTG Transceiver                           |     |

| 66 | USB Host Connections Using the OMAP5912 Integrated USB Transceiver                      |     |

| 67 | USB Host Connections On USB Pin Group 1 Using 3-Wire Transceiver                        |     |

| 68 | USB Host Connections on USB Pin Group 1 Using 4-Wire Transceiver                        |     |

| 69 | USB Host Connections on USB Pin Group 1 Using 6-Wire OTG Transceiver                    |     |

| 70 | USB Host Connections on USB Pin Group 2 Using 3-Wire Transceiver                        |     |

| 71 | USB Host Connections on USB Pin Group 2 Using 4-Wire Transceiver                        |     |

| 72 | USB Host Connections on USB Pin Group 2 Using 6-Wire Transceiver                        |     |

| 73 | USB Host Connections on USB Alternate Pin Group 2 Using 3-Wire Transceiver              |     |

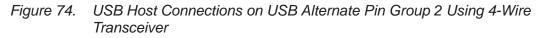

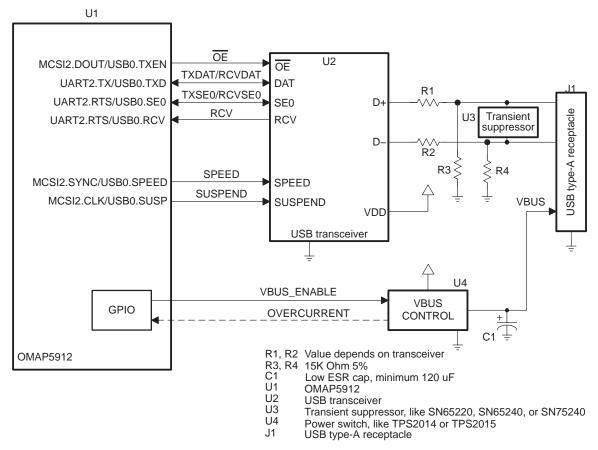

| 74 | USB Host Connections on USB Alternate Pin Group 2 Using 4-Wire Transceiver              |     |

| 75 | USB Host Connections on USB Alternate Pin Group 2 Using 6-Wire Transceiver              |     |

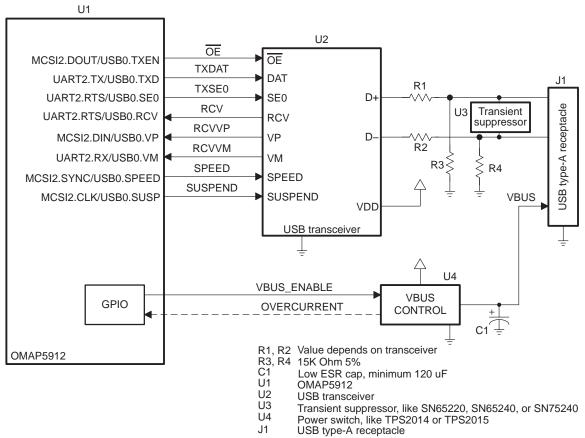

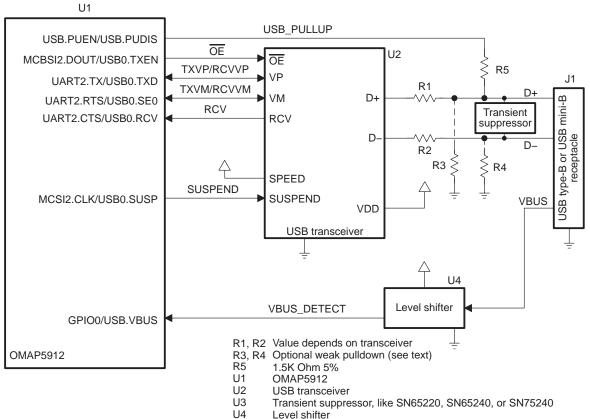

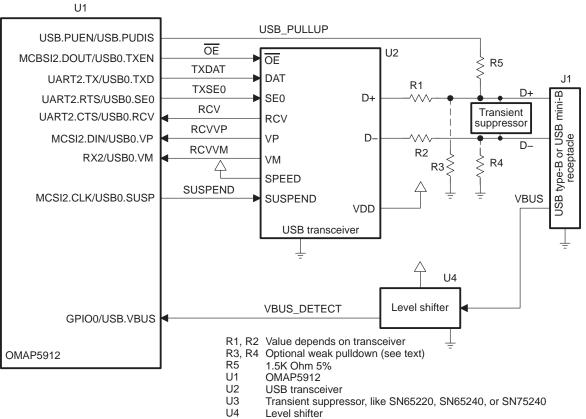

| 76 | USB Device Connections Using OMAP5912 Integrated USB Transceiver                        |     |

| 77 | USB Device Connections on USB Pin Group 1 Using 3-Wire Transceiver                      |     |

#### Figures

| 78 | USB Device Connections on USB Pin Group 1 Using 4-Wire Transceiver                                | 292 |

|----|---------------------------------------------------------------------------------------------------|-----|

| 79 | USB Device Connections on USB Pin Group 1 Using 6-Wire Transceiver                                | 294 |

| 80 | USB Device Connections on USB Alternate Pin Group 2 Using 3-Wire Transceiver                      | 296 |

| 81 | USB Device Connections on USB Alternate Pin Group 2 Using 4-Wire<br>OTG Transceiver               | 298 |

| 82 | USB Device Connections on USB Alternate Pin Group 2 Using 6-Wire Transceiver                      | 300 |

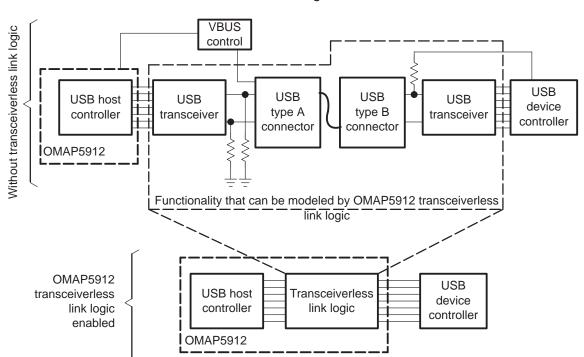

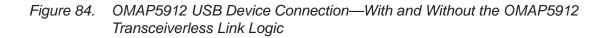

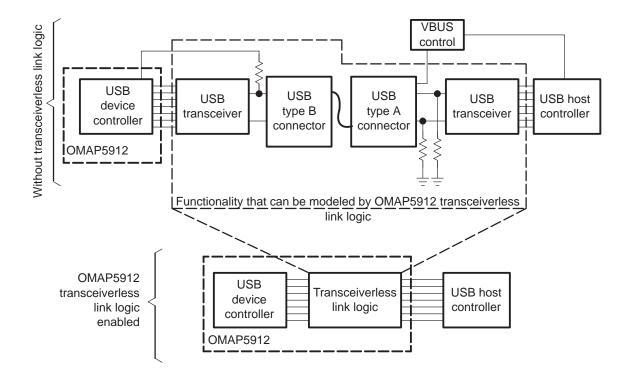

| 83 | OMAP5912 USB Host Controller Connection– With and Without the OMAP5912 Transceiverless Link Logic | 303 |

| 84 | OMAP5912 USB Device Connection– With and Without the OMAP5912<br>Transceiverless Link Logic       | 304 |

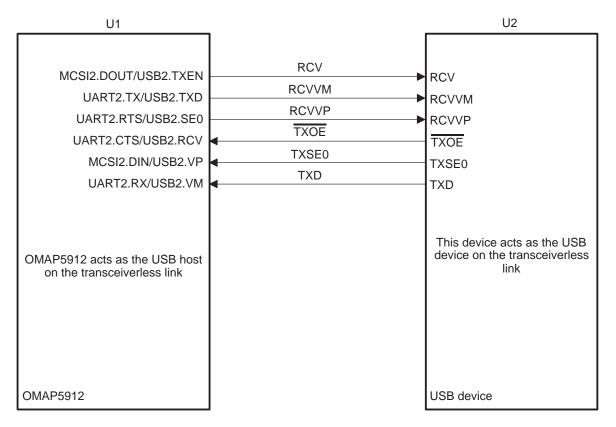

| 85 | OMAP5912 as USB Host on Transceiverless Link Using TXD/TXSE0 Signaling                            | 306 |

| 86 | OMAP5912 as USB Device Controller on Transceiverless Link Using TXD/TXSE0 Signaling               | 307 |

| 87 | OMAP5912 as USB Host Controller on Transceiverless Link Using TXVP/TXVM Signaling                 | 308 |

| 88 | OMAP5912 Pin Group 1 to Group 2 Internal Loopback (HMC_MODE = 7)                                  | 309 |

| 89 | External Connectivity When USB Pin Group 1 Configured for UART1 Signaling                         | 310 |

| 90 | I2C on USB Pin Group 0                                                                            |     |

| 91 | UART1 on USB Pin Group 0                                                                          | 312 |

# **Tables**

|    |                                                         | ~ - |

|----|---------------------------------------------------------|-----|

| 1  | USB Host Controller Registers                           |     |

| 2  | OHCI Revision Number Register (HCREVISION)              |     |

| 3  | HC Operating Mode Register (HCCONTROL)                  |     |

| 4  | HC Command and Status Register (HCCOMMANDSTATUS)        |     |

| 5  | HC Interrupt and Status Register (HCINTERRUPTSTATUS)    |     |

| 6  | HC Interrupt Enable Register (HCINTERRUPTENABLE)        |     |

| 7  | HC Interrupt Disable Register (HCINTERRUPTDISABLE)      |     |

| 8  | HC HCAA Address Register (HCHCCA)                       |     |

| 9  | HC Current Periodic Register (HCPERIODCURRENTED)        |     |

| 10 | HC Head Control Register (HCCONTROLHEADED)              |     |

| 11 | HC Current Control Register (HCCONTROLCURRENTED)        |     |

| 12 | HC Head Bulk Register (HCBULKHEADED)                    |     |

| 13 | HC Current Bulk Register (HCBULKCURRENTED)              |     |

| 14 | HC Head Done Register (HCDONEHEAD)                      |     |

| 15 | HC Frame Interval Register (HCFMINTERVAL)               |     |

| 16 | HC Frame Remaining Register (HCFMREMAINING)             |     |

| 17 | HC Frame Number Register (HCFMNUMBER)                   |     |

| 18 | HC Periodic Start Register (HCPERIODICSTART)            |     |

| 19 | HC Low-Speed Threshold Register (HCLSTHRESHOLD)         |     |

| 20 | HC Root Hub A Register (HCRHDESCRIPTORA)                |     |

| 21 | HC Root Hub B Register (HCRHDESCRIPTORB)                |     |

| 22 | HC Root Hub Status Register (HCRHSTATUS)                | 45  |

| 23 | HC Port 1 Status and Control Register (HCRHPORTSTATUS1) | 47  |

| 24 | HC Port 2 Status and Control Register (HCRHPORTSTATUS2) | 51  |

| 25 | HC Port 3 Status and Control Register (HCRHPORTSTATUS3) | 55  |

| 26 | Host UE Address Register (HOSTUEADDR)                   | 59  |

| 27 | Host UE Status Register (HOSTUESTATUS)                  | 59  |

| 28 | Host Time-out Control Register (HOSTTIMEOUTCTRL)        | 60  |

| 29 | Host Revision Register (HOSTREVISION)                   | 60  |

| 30 | USB Host Controller Clock Control                       | 61  |

| 31 | USB Device Controller Registers                         | 68  |

| 32 | Revision Register (REV)                                 | 70  |

| 33 | Endpoint Selection Register (EP_NUM)                    | 71  |

| 34 | Data Register (DATA)                                    | 72  |

| 35 | Control Register (CTRL)                                 | 73  |

| 36 | Status Register (STAT_FLG)                              | 75  |

| 37 | Receive FIFO Status Register (RXFSTAT)                                                              | . 79 |

|----|-----------------------------------------------------------------------------------------------------|------|

| 38 | System Configuration Register 1 (SYSCON1)                                                           | . 79 |

| 39 | System Configuration Register 2 (SYSCON2)                                                           | . 82 |

| 40 | Device Status Register (DEVSTAT)                                                                    | . 83 |

| 41 | Start of Frame Register (SOF)                                                                       | . 87 |

| 42 | Interrupt Enable Register (IRQ_EN)                                                                  | . 88 |

| 43 | DMA Interrupt Enable Register (DMA_IRQ_EN)                                                          | . 88 |

| 44 | Interrupt Source Register (IRQ_SRC)                                                                 | . 89 |

| 45 | Non-ISO Endpoint Interrupt Status Register (EPN_STAT)                                               | . 93 |

| 46 | Non-ISO DMA Interrupt Status Register (DMAN_STAT)                                                   |      |

| 47 | DMA Receive Channels Configuration Register (RXDMA_CFG)                                             | . 95 |

| 48 | DMA Transmit Channels Configuration Register (TXDMA_CFG)                                            | . 97 |

| 49 | DMA FIFO Data Register (DATA_DMA)                                                                   | . 99 |

| 50 | Transmit DMA Control Register n (TXDMAn)                                                            | 100  |

| 51 | Receive DMA Control Register n (RXDMAn)                                                             |      |

| 52 | Endpoint 0 Configuration Register (EP0)                                                             |      |

| 53 | Receive Endpoint n Configuration Register (EPn_RX)                                                  |      |

| 54 | Transmit Endpoint n Configuration Register (EPn_TX)                                                 |      |

| 55 | Autodecoded Versus Non-Autodecoded Control Requests                                                 |      |

| 56 | USB Device Controller Interrupt Type by Endpoint Type                                               |      |

| 57 | OTG Controller Registers                                                                            |      |

| 58 | OTG Revision Number Register (OTG_REV)                                                              |      |

| 59 | OTG System Configuration Register 1 (OTG_SYSCON_1)                                                  |      |

| 60 | Pin Group 2 Transceiver Type Selection                                                              |      |

| 61 | Pin Group 1 Transceiver Type Selection                                                              |      |

| 62 | Pin Group 0 Transceiver Type Selection                                                              |      |

| 63 | Alternate Pin Group 2 Transceiver Type Selection                                                    |      |

| 64 | OTG System Configuration Register 2 (OTG_SYSCON_2)                                                  |      |

| 65 | OTG_PADEN Source Status                                                                             |      |

| 66 | HMC_PADEN: USB Signal Multiplexing Control Source                                                   |      |

| 67 | OTG Control Register (OTG_CTRL)                                                                     |      |

| 68 | OTG Interrupt Enable Register (OTG_IRQ_EN)                                                          |      |

| 69 | OTG Interrupt StatusRegister (OTG_IRQ_SRC)                                                          |      |

| 70 | OTG Output pins control register (OTG_OUTCTRL)                                                      |      |

| 71 | OTG test register (OTG_TEST)                                                                        |      |

| 72 | OTG Vendor Code Register (OTG_VC)                                                                   | 223  |

| 73 | USB Signal Multiplexing Modes                                                                       |      |

| 74 | Top-Level Pin Multiplexing Configuration for OMAP5912 USB-Related Pins                              |      |

| 75 | UHOST_EN, HMC_MODE, TLL_ATTACH, TLL_SPEED Source Selection                                          |      |

| 76 | Signaling Between USB Controller and Unidirectional USB Transceiver<br>Using DAT/SE0 Signaling      |      |

| 77 | Signaling Between USB Controller and 3-Wire Bidirectional USB Transceiver                           |      |

|    | Using TXDAT/TXSE0 Signaling                                                                         | 262  |

| 78 | Signaling Between USB Controller and 4-Wire Unidirectional USB<br>Transceiver Using VP/VM Signaling | 263  |

|    |                                                                                                     |      |

This document describes the universal serial bus (USB) host on the OMAP5912 multimedia processor.

#### 1 Overview

The OMAP5912 processor provides several varieties of USB functionality, including:

- USB host: OMAP5912 provides a three-port USB Specification Revision 1.1-compliant host controller, which is based on the OHCI Specification for USB Release 1.0a.

- USB device: OMAP5912 provides a full-speed USB device.

- USB On-The-Go (OTG): OMAP5912 acts as an OTG dual-role device; the USB device functionality and one port of the USB host controller act in concert to provide an OTG port.

Flexible multiplexing of signals from the OMAP5912 USB host controller, the OMAP5912 USB function controller, and other OMAP5912 peripherals allow a wide variety of system-level USB capabilities. Many of the OMAP5912 pins can be used for USB-related signals or for signals from other OMAP5912 peripherals. The OMAP5912 top-level pin multiplexing controls each pin individually to select one of several possible internal pin signal interconnections. When these shared pins are programmed for use as USB signals, the OMAP5912 USB signal multiplexing selects how the signals associated with the three OMAP5912 USB host ports and the OMAP5912 USB function controller can be brought out to OMAP5912 pins.

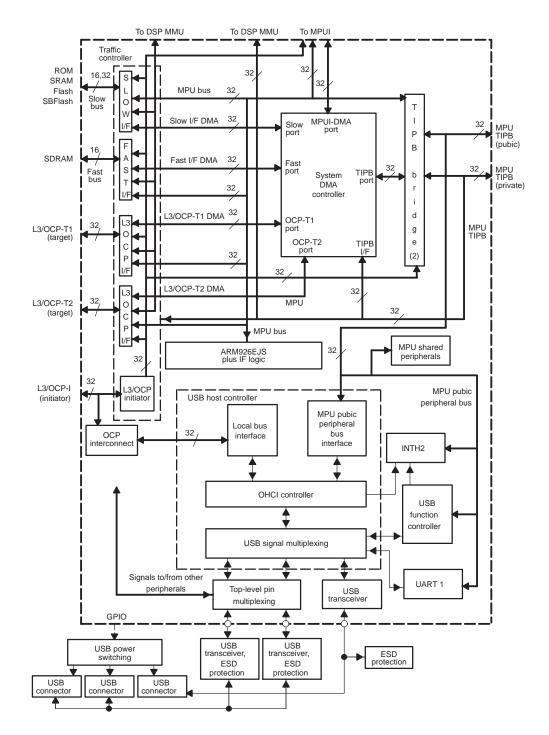

## 2 USB Host Controller

The OMAP5912 USB host controller (HC) is a three-port controller that communicates with USB devices at the USB low-speed (1.5M bit-per-second maximum) and full-speed (12M bit-per-second maximum) data rates. It is compatible with the *Universal Serial Bus Specification Revision 2.0* and the *Open HCI—Open Host Controller Interface Specification for USB*, Release 1.0a, available through the Compaq Computer Corporation web site, and hereafter called the *OHCI Specification for USB*. It is assumed that users of

the OMAP5912 USB host controller are already familiar with the USB Specification and OHCI Specification for USB.

The OMAP5912 OTG controller can use one of the USB host controller ports as part of a USB OTG-capable connection. When used for an OTG connection, the host controller port acts as the upstream device when OMAP5912 controls the OTG link, and the USB function controller acts as the downstream device when OMAP5912 acts as an OTG downstream device. The OMAP5912 OTG controller is described in Section 15.4, *USB OTG Controller*.

The OMAP5912 USB host controller implements the register set and makes use of the memory data structures defined in the OHCI Specification for USB. These registers and data structures are the mechanism by which a USB host controller driver software package can control the OMAP5912 USB host controller. The OHCI Specification for USB also defines how the USB host controller implementation must interact with those registers and data structures in system memory. The OMAP5912 MPU accesses these registers via the OMAP5912 MPU public peripheral bus.

To reduce processor software and interrupt overhead, the USB host controller generates USB traffic based on data structures and data buffers stored in system memory. The OMAP5912 USB host controller accesses these data structures without direct intervention by the processor using the OMAP5912 open-core protocol (OCPI) bus. These data structures and data buffers can be located in internal or external system RAM.

The USB host controller provides an interrupt to the MPU level 2 interrupt handler to signal certain hardware events to the host controller driver software.

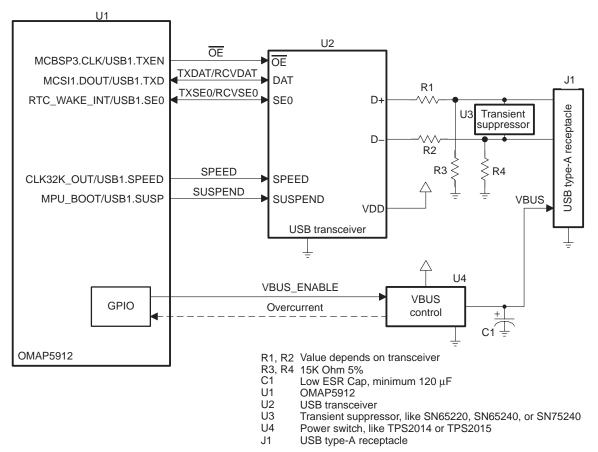

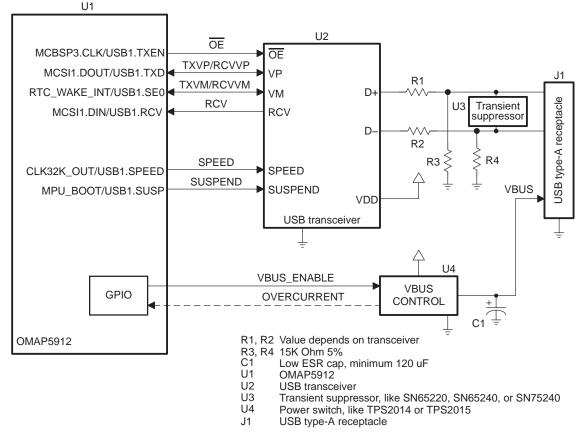

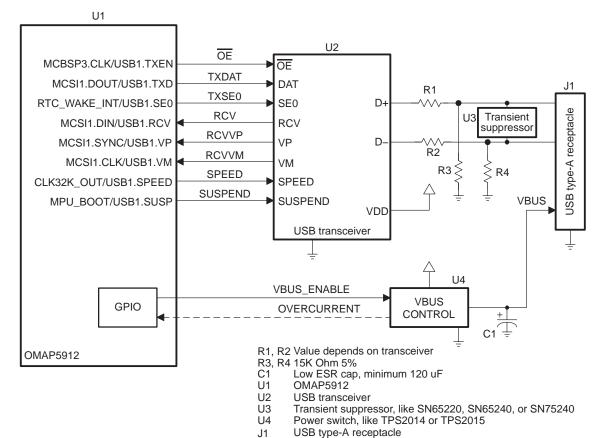

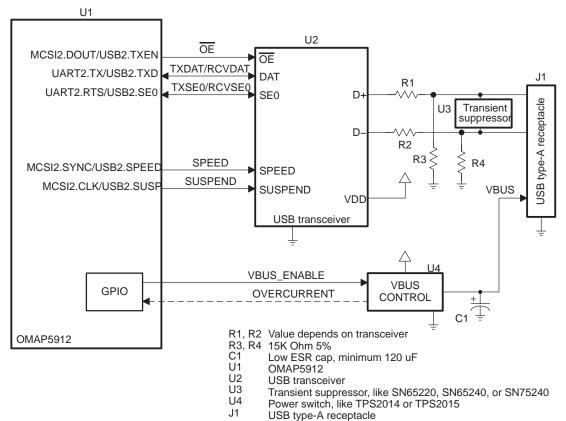

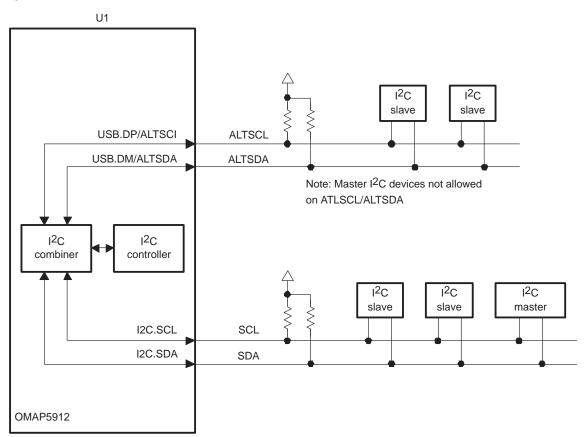

Figure 1 shows the OMAP5912 USB host controller.

## Figure 1. USB Host Controller

21

# 2.1 USB Open Host Controller Interface Functionality

## 2.1.1 OHCI Controller Overview

The Open HCI—Open Host Controller Interface Specification for USB, Release 1.0a, defines a set of registers and data structures stored in system memory that define how a USB host controller interfaces to system software. This specification, in conjunction with the Universal Serial Bus Specification Version 2.0, defines most of the USB functionality that the OMAP5912 USB host controller provides.

The OHCI Specification for USB focuses on two main aspects of the hardware implementation of a USB host controller: its register set and the memory data structures that define the activity to appear on the USB bus. Also discussed are issues such as interrupt generation, USB host controller state, USB frame management, and the methods that the hardware must use to process the lists of data structures in system memory.

This document does not duplicate the information presented in the OHCI Specification for USB or the USB Specification. OMAP5912 USB host controller users can refer to the USB Specification and the OHCI Specification for USB for detailed discussions of USB requirements and OHCI controller operation.

# 2.2 OMAP5912 USB Host Controller Differences From OHCI Specification for USB

The OMAP5912 USB host controller implementation does not implement every aspect of the functionality defined in the OHCI Specification for USB. The differences focus on power switching, overcurrent reporting, and the OHCI ownership change interrupt. Other restrictions are imposed by the effects of OMAP5912 pin multiplexing options.

# 2.2.1 Power Switching Output Pins Not Supported

The OMAP5912 device does not provide pins that can be controlled directly by the USB host controller OHCI port power control features. The OHCI RHPORTSTATUS register port power control bits can be programmed by the USB host controller driver software, but this does not have any direct effect on any VBUS switching implemented on the board.

Users can use software control of GPIO pins or other implementation-specific control mechanisms to control VBUS switching.

#### 2.2.2 Overcurrent Protection Input Pins Not Supported

The OMAP5912 device does not provide any pins that allow the USB host controller OHCI RHPORTSTATUS overcurrent protection status bits to be directly controlled by external hardware.

Users can use software monitoring of GPIO pins or other implementation-specific control mechanisms to report port overcurrent information to the USB host controller driver.

# 2.2.3 HMC\_MODE and Top-Level Pin Multiplexing and OHCI Registers

The USB signal multiplexing modes selected by HMC\_MODE provide selections where 0, 1, 2, or 3 USB host controller ports can be brought to OMAP5912 pins. The OHCI RHDESCRIPTORA register always reports three available USB host ports, regardless of the HMC\_MODE setting (see Table 20) or top-level pin multiplexing settings. When the HMC\_MODE setting disables a USB host controller port, the USB host controller sees that port as unattached.

When OMAP5912 top-level pin multiplexing configures a pin for functionality other than the USB, the USB host controller is disconnected from that pin and that pin does not affect the USB host controller.

# 2.2.4 No Ownership Change Interrupt

The OMAP5912 USB host controller does not implement the OHCI ownership change interrupt.

# 2.3 OMAP5912 Implementation of OHCI Specification for USB

# 2.3.1 Isochronous Transmit Descriptor (TD) OFFSETX/PSWX Values

The OMAP5912 USB host controller implements the OHCI Specification for USB optional feature of checking isochronous OFFSETX/PSWX values. If either OFFSETX or OFFSET(X+1) does not have a condition code of Not Accessed, or if the OFFSET(X+1) value is not greater than or equal to OFFSETX, then an unrecoverable error is reported. Unrecoverable errors issued for these reasons do not cause an update of the HOSTUEADDR, HOSTUESTATUS, or HOSTTIMEOUTCTRL registers.

## 2.3.2 OMAP5912 USB Host Controller Endpoint Descriptor (ED) List Head Pointers

The OHCI *Specification for USB* provides a specific sequence of operations for the host controller driver to perform when setting up the host controller. Failure to follow that sequence can result in malfunction. As a specific example, the HCCONTROLHEADED and HCBULKHEADED pointer registers and the 32 HCCAINTERRUPTTABLE pointers must all point to valid physical addresses of valid endpoint descriptors.

SPRU761A

The OMAP5912 USB host controller does not check HCCONTROLHEADED registers, HCBULKHEADED registers, or the values in the 32 HCCAINTERRUPTTABLE pointers before using them to access EDs. If any of these pointers are NULL when the corresponding list enable bit is set, the OMAP5912 USB host controller attempts to access using the physical address of 0, which causes an unrecoverable error to be signaled. HOSTUEADDR, HOSTUESTATUS, and HOSTTIMEOUTCTRL registers are updated in this case.

#### 2.3.3 OHCI USB Suspend State

The OMAP5912 USB host controller ignores upstream traffic from downstream devices for about 3 ms after the host controller state (HCCONTROL.HCFS) changes from USB resume state to USB operational state. If any TDs cause generation of downstream packets during that time, the downstream packets are sent, but any response provided by the downstream device is ignored. Any such TDs are aborted with completion codes marked as *Device Not Responding*. TDs on any of the lists (periodic, control, bulk, and isochronous) can cause such an occurrence.

The USB specification requires that system software must provide a 10-ms resume recovery time (T<sub>RSMRCY</sub>) after a bus segment transitions from resume signaling to normal operational mode. During that time, only start of frame packets are to be sent on the bus segment. It is recommended that system software disable all list enable bits (HCCONTROL.PLE, HCCONTROL.IE, HCCONTROL.CLE, and HCCONTROL.BLE) and then wait for at least 1 ms before setting the host controller into USB suspend state (via HCCONTROL.HCFS). When restoring from suspend, system software must set the host controller into USB resume state, and wait for the host controller to transition into USB operational state. System software must then wait 10 ms before enabling the host controller list enable bits.

When the host controller has been placed into the USB suspend state under software control, but is brought out by a remote wake-up, system software must monitor the HCRHPORTSTATUS[x].PSS and HCRHPORTSTATUS[x].PSSC bits. The HCRHPORTSTATUS[x].PSS bit changes to 0 only after completion of resume signaling on the bus segment completes and completion of the 3-ms period where packets from downstream devices are ignored.

When using port-specific suspend, it is not necessary to disable the host controller lists so long as there are no active EDs and TDs directed toward devices that are downstream of the suspended port. For port-specific suspend operations, the host controller does not issue a root hub status change interrupt with the HCRHPORTSTATUS[n].PSSC bit = 1 and

HCRHPORTSTATUS[n].PSS = 0 until after the approximately 3-ms delay after resume signaling completes.

When using port-specific suspend, system software must ensure that there are no active EDs for devices that are downstream of the suspended port before setting the port into suspend mode. While the port is in suspend or being resumed, system software must not enable any EDs for any devices downstream of the suspended port. Once the root hub status change interrupt

occurs as a result of the suspended port PSS bit changing to 0, EDs can be enabled for devices downstream of the port that is now operational.

## 2.4 USB Host Controller Registers

Most of the OMAP5912 host controller (HC) registers are the OHCI operational registers, which are defined by the OHCI Specification for USB. Four additional registers not specified by the OHCI Specification for USB provide additional information about the USB host controller state. USB host controller registers can be accessed in user and supervisor modes.

The OMAP5912 USB host controller registers are listed in Table 1. Table 2 through Table 29 describe specific register bits.

| Name               | Description                           | R/W | Size <sup>†</sup> | Address    |

|--------------------|---------------------------------------|-----|-------------------|------------|

| HCREVISION         | OHCI revision number                  | R   | 32                | FFFB:A000h |

| HCCONTROL          | HC operating mode                     | R/W | 32                | FFFB:A004h |

| HCCOMMANDSTATUS    | HC command and status                 | R/W | 32                | FFFB:A008h |

| HCINTERRUPTSTATUS  | HC interrupt status                   | R/W | 32                | FFFB:A00Ch |

| HCINTERRUPTENABLE  | HC interrupt enable                   | R/W | 32                | FFFB:A010h |

| HCINTERRUPTDISABLE | HC interrupt disable                  | R/W | 32                | FFFB:A014h |

| HCHCCA             | Physical address of HCCA <sup>‡</sup> | R/W | 32                | FFFB:A018h |

Table 1. USB Host Controller Registers

+ Access to these registers must be by 32-bit reads or 32-bit writes. Use of other access sizes may result in undefined operation.

‡ Restrictions apply to the physical addresses used in these registers. See Section 2.9, Physical Addressing.

§ This register provides control and status for the OMAP5912 pins normally associated with USB port 0 (the integrated USB transceiver) for some HMC\_MODE values.

This register provides control and status for the OMAP5912 pins normally associated with USB port 1 for some HMC\_MODE values.

<sup>#</sup> This register provides control and status for the OMAP5912 pins normally associated with USB port 2 for some HMC\_MODE values.

25

| Name                   | Description                                                                   | R/W           | Size <sup>†</sup> | Address    |  |

|------------------------|-------------------------------------------------------------------------------|---------------|-------------------|------------|--|

| HCPERIODCURRENTED      | Physical address of current periodic endpoint descriptor <sup>‡</sup>         | R/W           | 32                | FFFB:A01Ch |  |

| HCCONTROLHEADED        | Physical address of head of control endpoint descriptor list <sup>‡</sup>     | R/W           | 32                | FFFB:A020h |  |

| HCCONTROLCURRENTE<br>D | Physical address of current control endpoint descriptor <sup>‡</sup>          | R/W           | 32                | FFFB:A024h |  |

| HCBULKHEADED           | Physical address of head of bulk endpoint descriptor list <sup>‡</sup>        | R/W           | 32                | FFFB:A028h |  |

| HCBULKCURRENTED        | Physical of current bulk endpoint descriptor <sup>‡</sup>                     | R/W 32 FFFB:/ |                   |            |  |

| HCDONEHEAD             | Physical address of head of list of retired transfer descriptors <sup>‡</sup> | R             | 32 FFFB:A03       |            |  |

| HCFMINTERVAL           | HC frame interval                                                             | R/W           | 32                | FFFB:A034h |  |

| HCFMREMAINING          | HC frame remaining                                                            | R             | 32                | FFFB:A038h |  |

| HCFMNUMBER             | HC frame number                                                               | R             | 32                | FFFB:A03Ch |  |

| HCPERIODICSTART        | HC periodic start                                                             | R/W           | 32                | FFFB:A040h |  |

| HCLSTHRESHOLD          | HC low speed threshold                                                        | R/W           | 32                | FFFB:A044h |  |

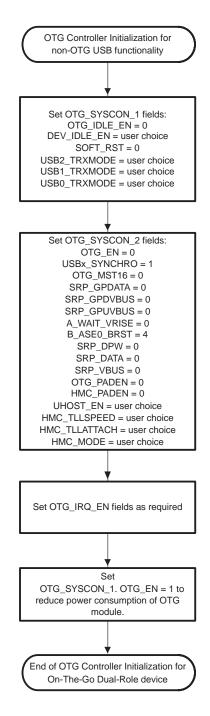

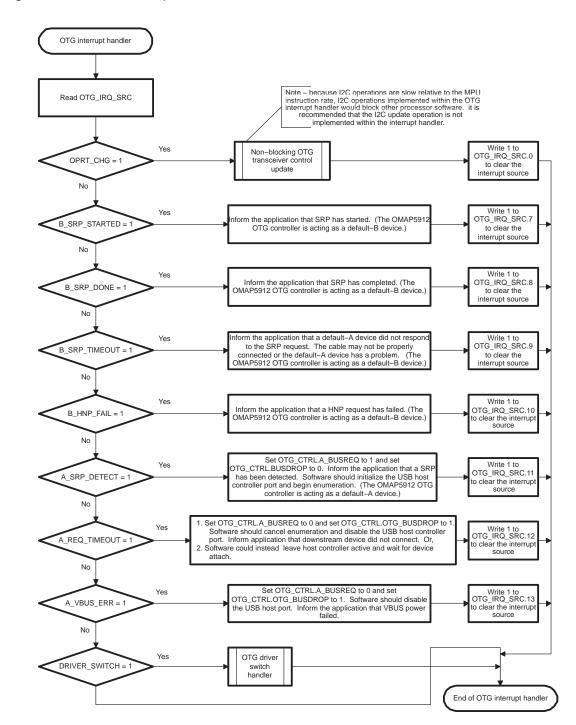

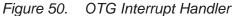

| HCRHDESCRIPTORA        | HC root hub A                                                                 | R, R/W        | 32                | FFFB:A048h |  |