## TMS320C621x/C671x DSP Two-Level Internal Memory Reference Guide

Literature Number: SPRU609B June 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                                       |                                                                            | Applications                                                                             |                                                                                                                                                                         |

|------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amplifiers                                     | amplifier.ti.com                                                           | Audio                                                                                    | www.ti.com/audio                                                                                                                                                        |

| Data Converters                                | dataconverter.ti.com                                                       | Automotive                                                                               | www.ti.com/automotive                                                                                                                                                   |

| DSP                                            | dsp.ti.com                                                                 | Broadband                                                                                | www.ti.com/broadband                                                                                                                                                    |

| Interface                                      | interface.ti.com                                                           | Digital Control                                                                          | www.ti.com/digitalcontrol                                                                                                                                               |

| Logic                                          | logic.ti.com                                                               | Military                                                                                 | www.ti.com/military                                                                                                                                                     |

| Power Mgmt                                     | power.ti.com                                                               | Optical Networking                                                                       | www.ti.com/opticalnetwork                                                                                                                                               |

| Microcontrollers                               | microcontroller.ti.com                                                     | Security                                                                                 | www.ti.com/security                                                                                                                                                     |

|                                                |                                                                            | Telephony                                                                                | www.ti.com/telephony                                                                                                                                                    |

|                                                |                                                                            | Video & Imaging                                                                          | www.ti.com/video                                                                                                                                                        |

|                                                |                                                                            | Wireless                                                                                 | www.ti.com/wireless                                                                                                                                                     |

| Data Converters DSP Interface Logic Power Mgmt | dataconverter.ti.com dsp.ti.com interface.ti.com logic.ti.com power.ti.com | Broadband Digital Control Military Optical Networking Security Telephony Video & Imaging | www.ti.com/broadband<br>www.ti.com/digitalcontrol<br>www.ti.com/military<br>www.ti.com/opticalnetwor<br>www.ti.com/security<br>www.ti.com/telephony<br>www.ti.com/video |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

## **Preface**

## **Read This First**

#### About This Manual

The TMS320C621x and TMS320C671x digital signal processors (DSPs) of the TMS320C6000™ DSP family have a two-level memory architecture for program and data. The first-level program cache is designated L1P, and the first-level data cache is designated L1D. Both the program and data memory share the second-level memory, designated L2. L2 is configurable, allowing for various amounts of cache and SRAM. This document discusses the C621x/C671x two-level internal memory.

#### **Notational Conventions**

This document uses the following conventions.

- ☐ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register. Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

### Related Documentation From Texas Instruments

The following documents describe the C6000<sup>™</sup> devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

**TMS320C6000 CPU and Instruction Set Reference Guide** (literature number SPRU189) describes the TMS320C6000™ CPU architecture, instruction set, pipeline, and interrupts for these digital signal processors.

TMS320C6000 DSP Peripherals Overview Reference Guide (literature number SPRU190) describes the peripherals available on the TMS320C6000™ DSPs.

- **TMS320C6000 Technical Brief** (literature number SPRU197) gives an introduction to the TMS320C62x<sup>™</sup> and TMS320C67x<sup>™</sup> DSPs, development tools, and third-party support.

- TMS320C6000 DSP Cache User's Guide (literature number SPRU656) explains the fundamentals of memory caches and describes how to efficiently utilize the two-level cache-based memory architecture in the digital signal processors (DSPs) of the TMS320C6000™ DSP family. It shows how to maintain coherence with external memory, how to use DMA to reduce memory latencies, and how to optimize your code to improve cache efficiency.

- **TMS320C6000 Programmer's Guide** (literature number SPRU198) describes ways to optimize C and assembly code for the TMS320C6000™ DSPs and includes application program examples.

- **TMS320C6000 Code Composer Studio Tutorial** (literature number SPRU301) introduces the Code Composer Studio™ integrated development environment and software tools.

- Code Composer Studio Application Programming Interface Reference Guide (literature number SPRU321) describes the Code Composer Studio™ application programming interface (API), which allows you to program custom plug-ins for Code Composer.

- TMS320C6x Peripheral Support Library Programmer's Reference (literature number SPRU273) describes the contents of the TMS320C6000™ peripheral support library of functions and macros. It lists functions and macros both by header file and alphabetically, provides a complete description of each, and gives code examples to show how they are used.

- **TMS320C6000 Chip Support Library API Reference Guide** (literature number SPRU401) describes a set of application programming interfaces (APIs) used to configure and control the on-chip peripherals.

#### **Trademarks**

Code Composer Studio, C6000, C62x, C64x, C67x, TMS320C6000, TMS320C62x, TMS320C64x, TMS320C67x, and VelociTl are trademarks of Texas Instruments.

## **Contents**

| 1 | Memo                                                     | ory Hier                                                                    | archy Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 9                                                      |

|---|----------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2 | Cache                                                    | e Terms                                                                     | and Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                       |

| 3 | <b>Level</b> 3.1 3.2                                     | L1D Pa                                                                      | Cache (L1D)  arameters erformance  L1D Memory Banking  L1D Miss Penalty  L1D Write Buffer                                                                                                                                                                                                                                                                                                                                                                                                                 | 19<br>20<br>20<br>20                                     |

| 4 | <b>Level</b> 4.1 4.2                                     | L1P Pa                                                                      | ram Cache (L1P) arameters ss Penalty                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22                                                       |

| 5 | <b>Level</b> 5.1 5.2 5.3 5.4                             | L2 Cac<br>L2 Ope<br>L2 Ban                                                  | che and L2 SRAM ceration clk Structure rfaces  L1D/L1P-to-L2 Request Servicing  EDMA-to-L2 Request Servicing  L2 Request Servicing Using EDMA  EDMA Access to Cache Controls  HPI and PCI Access to Memory Subsystem                                                                                                                                                                                                                                                                                      | 23<br>24<br>26<br>27<br>27<br>28<br>28<br>29             |

| 6 | Regis 6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10 6.11 6.12 | Cache L2 Writ L2 Writ L2 Writ L1P Inv L1P Inv L1D Wi L1D Wi L2 Writ L2 Writ | Configuration Register (CCFG)  teback Base Address Register (L2WBAR)  teback Word Count Register (L2WWC)  teback-Invalidate Base Address Register (L2WIWC)  validate Base Address Register (L1PIBAR)  validate Word Count Register (L1PIBAR)  validate Word Count Register (L1PIWC)  riteback-Invalidate Base Address Register (L1DWIBAR)  riteback-Invalidate Word Count Register (L1DWIWC)  teback All Register (L2WB)  teback-Invalidate All Register (L2WBINV)  mory Attribute Registers (MAR0-MAR15) | 30<br>34<br>34<br>35<br>35<br>36<br>37<br>37<br>38<br>39 |

| 7  | Mem    | ory Syst | em Control                                   | . 41 |

|----|--------|----------|----------------------------------------------|------|

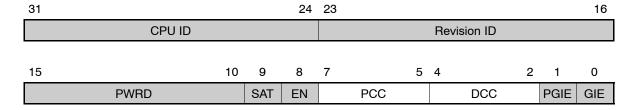

|    | 7.1    |          | Mode Selection                               |      |

|    |        | 7.1.1    | L1D Mode Selection Using DCC Field in CSR    | . 41 |

|    |        |          | L1P Mode Selection Using PCC Field in CSR    |      |

|    |        | 7.1.3    | L2 Mode Selection Using L2MODE Field in CCFG | . 42 |

|    | 7.2    | Cachea   | ability Controls                             | . 45 |

|    | 7.3    | Progra   | m-Initiated Cache Operations                 | . 46 |

|    |        | 7.3.1    | Global Cache Operations                      | . 48 |

|    |        | 7.3.2    | Block Cache Operations                       | . 49 |

|    |        | 7.3.3    | Effect of L2 Commands on L1 Caches           | . 51 |

| 8  | Mem    | ory Syst | em Policies                                  | . 53 |

|    | 8.1    | Memor    | y System Coherence                           | . 53 |

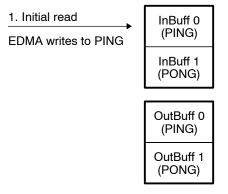

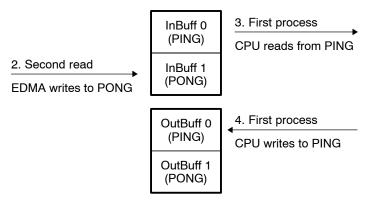

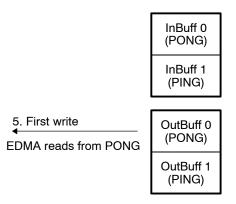

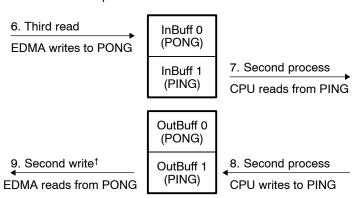

|    | 8.2    | EDMA     | Coherence in L2 SRAM Example                 | . 55 |

|    | 8.3    |          | y Access Ordering                            |      |

|    |        | 8.3.1    | Program Order of Memory Accesses             | . 60 |

|    |        | 8.3.2    | Strong and Relaxed Memory Ordering           | . 61 |

| Re | vision | History  |                                              | . 63 |

# **Figures**

| 1  | TMS320C621x/C671x DSP Block Diagram                       | 9  |

|----|-----------------------------------------------------------|----|

| 2  | TMS320C621x/C671x Two-Level Internal Memory Block Diagram | 12 |

| 3  | L1D Address Allocation                                    | 19 |

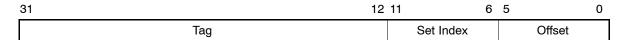

| 4  | L1P Address Allocation                                    | 22 |

| 5  | L2 Address Allocation (All L2 Cache Modes)                | 23 |

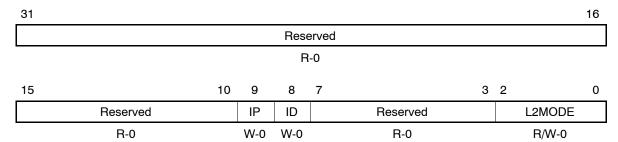

| 6  | Cache Configuration Register (CCFG)                       | 30 |

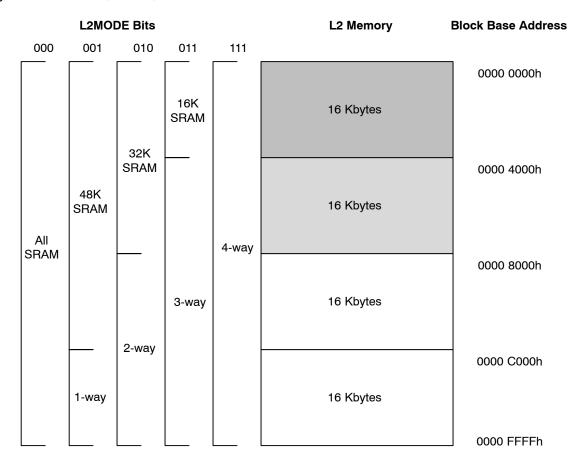

| 7  | C6211/C6711/C6712 L2 Cache Modes                          | 32 |

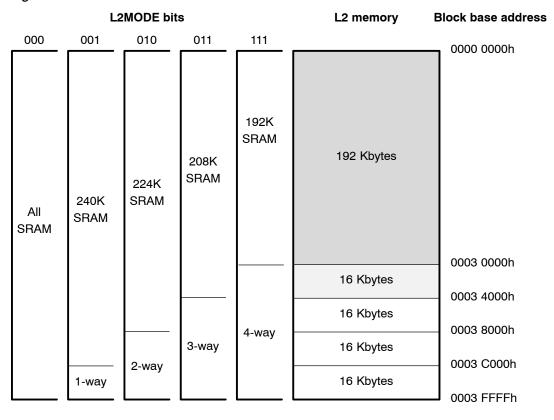

| 8  | C6713 L2 Cache Modes                                      | 33 |

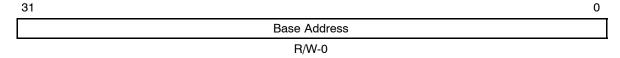

| 9  | L2 Writeback Base Address Register (L2WBAR)               | 34 |

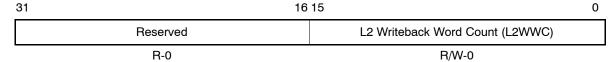

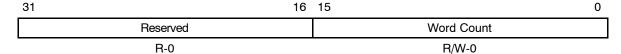

| 10 | L2 Writeback Word Count Register (L2WWC)                  | 34 |

| 11 | L2 Writeback-Invalidate Base Address Register (L2WIBAR)   |    |

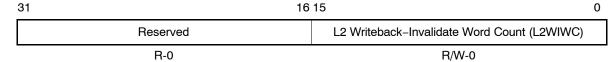

| 12 | L2 Writeback-Invalidate Word Count Register (L2WIWC)      | 35 |

| 13 | L1P Invalidate Base Address Register (L1PIBAR)            | 36 |

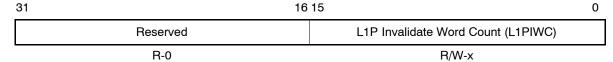

| 14 | L1P Invalidate Word Count Register (L1PIWC)               | 36 |

| 15 | L1D Writeback-Invalidate Base Address Register (L1DWIBAR) |    |

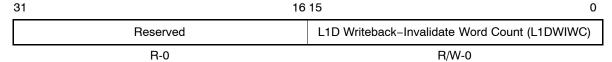

| 16 | L1D Writeback-Invalidate Word Count Register (L1DWIWC)    | 37 |

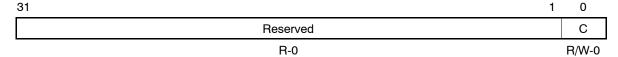

| 17 | L2 Writeback All Register (L2WB)                          | 38 |

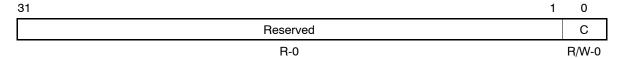

| 18 | L2 Writeback-Invalidate All Register (L2WBINV)            | 39 |

| 19 | L2 Memory Attribute Register (MAR)                        | 40 |

| 20 | CPU Control and Status Register (CSR)                     | 41 |

| 21 | Block Cache Operation Base Address Register (BAR)         | 49 |

| 22 | Block Cache Operation Word Count Register (WC)            | 49 |

| 23 | Streaming Data Pseudo-Code                                |    |

| 24 | Double Buffering Pseudo-Code                              |    |

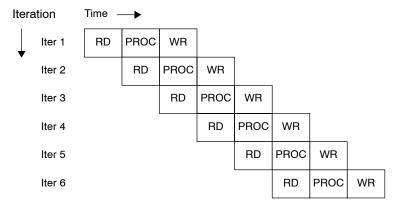

| 25 | Double-Buffering Time Sequence                            | 57 |

| 26 | Double Buffering as a Pipelined Process                   | 58 |

## **Tables**

| 1  | TMS320C621x/C671x/C64x Internal Memory Comparison                               |

|----|---------------------------------------------------------------------------------|

| 2  | Terms and Definitions                                                           |

| 3  | Internal Memory Control Registers                                               |

| 4  | Cache Configuration Register (CCFG) Field Descriptions                          |

| 5  | L2 Writeback Base Address Register (L2WBAR) Field Descriptions                  |

| 6  | L2 Writeback Word Count Register (L2WWC) Field Descriptions 34                  |

| 7  | L2 Writeback-Invalidate Base Address Register (L2WIBAR) Field Descriptions 35   |

| 8  | L2 Writeback-Invalidate Word Count Register (L2WIWC) Field Descriptions         |

| 9  | L1P Invalidate Base Address Register (L1PIBAR) Field Descriptions               |

| 10 | L1P Invalidate Word Count Register (L1PIWC) Field Descriptions                  |

| 11 | L1D Writeback-Invalidate Base Address Register (L1DWIBAR) Field Descriptions 37 |

| 12 | L1D Writeback-Invalidate Word Count Register (L1DWIWC) Field Descriptions 37    |

| 13 | L2 Writeback All Register (L2WB) Field Descriptions                             |

| 14 | L2 Writeback-Invalidate All Register (L2WBINV) Field Descriptions               |

| 15 | Memory Attribute Register (MAR) Field Descriptions                              |

| 16 | L1D Mode Setting Using DCC Field                                                |

| 17 | L1P Mode Setting Using PCC Field                                                |

| 18 | L2 Mode Switch Procedure 44                                                     |

| 19 | Memory Attribute Registers                                                      |

| 20 | Summary of Program-Initiated Cache Operations                                   |

| 21 | Coherence Assurances in the Two-Level Memory System                             |

| 22 | Program Order for Memory Operations Issued From a Single Execute Packet 60      |

| 23 | Document Revision History                                                       |

## TMS320C621x/C671x Two-Level Internal Memory

The TMS320C621x, TMS320C671x, and TMS320C64x $^{\text{TM}}$  digital signal processors (DSPs) of the TMS320C6000 $^{\text{TM}}$  DSP family have a two-level memory architecture for program and data. The first-level program cache is designated L1P, and the first-level data cache is designated L1D. Both the program and data memory share the second-level memory, designated L2. L2 is configurable, allowing for various amounts of cache and SRAM. This document discusses the C621x/C671x two-level internal memory. For a discussion of the C64x $^{\text{TM}}$  DSP two-level internal memory, see TMS320C64x DSP Two-Level Internal Memory Reference Guide (SPRU610).

## 1 Memory Hierarchy Overview

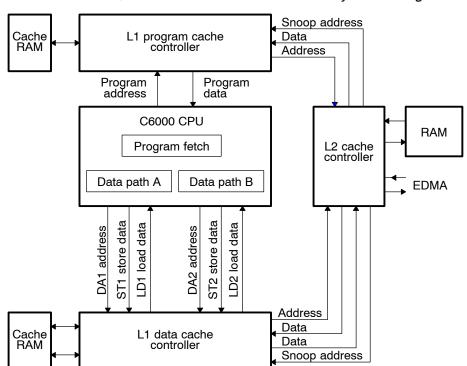

Figure 1 shows the block diagram of the C621x/C671x DSP. Table 1 summarizes the differences between the C621x/C671x and C64x internal memory. Figure 2, page 12, shows the bus connections between the CPU, internal memories, and the enhanced DMA (EDMA) of the C6000™ DSP.

L1P cache **EMIF** C6000 DSP core Instruction fetch Control Other registers Instruction dispatch peripherals Instruction decode Control Enhanced L2 logic DMA memory Data path A Data path B controller Test A register file B register file Interrupt In-circuit emulation selector L1 S1 M1 D1 D2 M2 S2 L2 Interrupt control Power down logic **Boot** L1D cache PLL configuration

Figure 1. TMS320C621x/C671x DSP Block Diagram

Table 1. TMS320C621x/C671x/C64x Internal Memory Comparison

|                                                                            | TMS320C621x/C671x DSP                 | TMS320C64x DSP                             |  |

|----------------------------------------------------------------------------|---------------------------------------|--------------------------------------------|--|

| Internal memory structure                                                  | Two                                   | Level                                      |  |

| L1P size                                                                   | 4 Kbytes                              | 16 Kbytes                                  |  |

| L1P organization                                                           | Direct                                | mapped                                     |  |

| L1P CPU access time                                                        | 1 (                                   | cycle                                      |  |

| L1P line size                                                              | 64 bytes                              | 32 bytes                                   |  |

| L1P read miss action                                                       | 1 line allo                           | cated in L1P                               |  |

| L1P read hit action                                                        | Data rea                              | d from L1P                                 |  |

| L1P write miss action                                                      | L1P writes                            | not supported                              |  |

| L1P write hit action                                                       | L1P writes                            | not supported                              |  |

| $L1P \rightarrow L2 \ request \ size$                                      | 2 fetches/L1P line                    | 1 fetch/L1P line                           |  |

| L1P protocol                                                               | Read Allocate                         | Read Allocate; Pipelined Misses            |  |

| L1P memory                                                                 | Single-cycle RAM                      |                                            |  |

| $\text{L1P} \rightarrow \text{L2 single request stall}$                    | 5 cycles for L2 hit                   | 8 cycles for L2 hit                        |  |

| $\text{L1P} \rightarrow \text{L2}$ minimum cycles between pipelined misses | Pipelined misses not supported        | 1 cycle                                    |  |

| L1D size                                                                   | 4 Kbytes                              | 16 Kbytes                                  |  |

| L1D organization                                                           | 2-way set associative                 |                                            |  |

| L1D CPU access time                                                        | 1 (                                   | cycle                                      |  |

| L1D line size                                                              | 32 bytes                              | 64 bytes                                   |  |

| L1D replacement strategy                                                   | 2-way Least                           | Recently Used                              |  |

| L1D banking                                                                | 64-bit-wide dual-ported RAM           | $8 \times 32$ bit banks                    |  |

| L1D read miss action                                                       | 1 line allocated in L1D               |                                            |  |

| L1D read hit action                                                        | Data read from L1D                    |                                            |  |

| L1D write miss action                                                      | No allocation in L1D, data sent to L2 |                                            |  |

| L1D write hit action                                                       | Data updated in L                     | 1D; line marked dirty                      |  |

| L1D protocol                                                               | Read Allocate                         | d Allocate Read allocate; Pipelined Misses |  |

| $L1D \rightarrow L2$ request size                                          | 2 fetche                              | s/L1D line                                 |  |

Table 1. TMS320C621x/C671x/C64x Internal Memory Comparison (Continued)

|                                                              | TMS320C621x/C671x DSP                                                                                          | TMS320C64x DSP                            |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| L1D → L2 single request stall                                | 4 cycles for L2 hit                                                                                            | 6 cycles/L2 SRAM hit                      |

|                                                              |                                                                                                                | 8 cycles/L2 cache hit                     |

| $L1D \rightarrow L2$ minimum cycles between pipelined misses | Pipelined misses not supported                                                                                 | 2 cycles                                  |

| L2 total size                                                | Varies by part number. Refer to the                                                                            | datasheet for the specific device.        |

| L2 SRAM size                                                 | Varies by part number. Refer to the                                                                            | datasheet for the specific device.        |

| L2 cache size                                                | 0/16/32/48/64 Kbytes                                                                                           | 0/32/64/128/256 Kbytes                    |

| L2 organization                                              | 1/2/3/4-way set associative                                                                                    | 4-way set associative cache               |

| L2 line size                                                 | 128 b                                                                                                          | ytes                                      |

| L2 replacement strategy                                      | 1/2/3/4-way Least Recently Used                                                                                | 4-way Least Recently Used                 |

| L2 banking                                                   | $4 \times 64$ bit banks                                                                                        | $8 \times 64$ bit banks                   |

| L2-L1P protocol                                              | Coherency invalidates                                                                                          |                                           |

| L2-L1D protocol                                              | Coherency snoop-invalidates                                                                                    | Coherency snoops and<br>snoop-invalidates |

| L2 protocol                                                  | Read and Write Allocate                                                                                        |                                           |

| L2 read miss action                                          | Data is read via EDMA into newly allocated line in L2; requested data is passed to the requesting L1           |                                           |

| L2 read hit action                                           | Data is read from L2                                                                                           |                                           |

| L2 write miss action                                         | Data is read via EDMA into newly allocated line in L2; write data is then written to the newly allocated line. |                                           |

| L2 write hit action                                          | Data is written into hit L2 location                                                                           |                                           |

| $L2 \rightarrow L1P$ read path width                         | 256                                                                                                            | bit                                       |

| $L2 \rightarrow L1D$ read path width                         | 128 bit                                                                                                        | 256 bit                                   |

| $L1D \rightarrow L2$ write path width                        | 32 bit                                                                                                         | 64 bit                                    |

| $L1D \rightarrow L2$ victim path width                       | 128 bit                                                                                                        | 256 bit                                   |

| $L2 \rightarrow EDMA$ read path width                        | 64 k                                                                                                           | oit                                       |

| $L2 \rightarrow EDMA$ write path width                       | 64 k                                                                                                           | oit                                       |

Figure 2. TMS320C621x/C671x Two-Level Internal Memory Block Diagram

12

## 2 Cache Terms and Definitions

Table 2 lists the terms used throughout this document that relate to the operation of the C621x/C671x two-level memory hierarchy.

Table 2. Terms and Definitions

| Term                | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Allocation          | The process of finding a location in the cache to store newly cached data. This process can include <i>evicting</i> data that is presently in the cache to make room for the new data.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Associativity       | The number of <i>line frames</i> in each <i>set</i> . This is specified as the number of <i>ways</i> in the cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Capacity miss       | A cache miss that occurs because the cache does not have sufficient room to hold the entire <i>working set</i> for a program. Compare with <i>compulsory miss</i> and <i>conflict miss</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Clean               | A cache <i>line</i> that is <i>valid</i> and that has not been written to by upper levels of memory or the CPU. The opposite state for a valid cache line is <i>dirty</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Coherence           | Informally, a memory system is coherent if any read of a data item returns the most recently written value of that data item. This includes accesses by the CPU and the EDMA. Cache coherence is covered in more detail in section 8.1.                                                                                                                                                                                                                                                                                                                                                                                         |

| Compulsory miss     | Sometimes referred to as a <i>first-reference miss</i> . A compulsory miss is a cache <i>miss</i> that must occur because the data has had no prior opportunity to be allocated in the cache. Typically, compulsory misses for particular pieces of data occur on the first access of that data. However, some cases can be considered compulsory even if they are not the first reference to the data. Such cases include repeated write misses on the same location in a cache that does not <i>write allocate</i> , and cache misses to noncacheable locations. Compare with <i>capacity miss</i> and <i>conflict miss</i> . |

| Conflict miss       | A cache <i>miss</i> that occurs due to the limited <i>associativity</i> of a cache, rather than due to capacity constraints. A <i>fully-associative cache</i> is able to allocate a newly cached <i>line</i> of data anywhere in the cache. Most caches have much more limited associativity (see <i>set-associative cache</i> ), and so are restricted in where they may place data. This results in additional cache misses that a more flexible cache would not experience.                                                                                                                                                  |

| Direct-mapped cache | A direct-mapped cache maps each address in the <i>lower-level memory</i> to a single location in the cache. Multiple locations may map to the same location in the cache. This is in contrast to a multi-way <i>set-associative cache</i> , which selects a place for the data from a <i>set</i> of locations in the cache. A direct-mapped cache can be considered a single-way set-associative cache.                                                                                                                                                                                                                         |

| Dirty               | In a <i>writeback cache</i> , writes that reach a given level in the memory hierarchy may update that level, but not the levels below it. Thus, when a cache <i>line</i> is <i>valid</i> and contains updates that have not been sent to the next lower level, that line is said to be dirty. The opposite state for a valid cache line is <i>clean</i> .                                                                                                                                                                                                                                                                       |

Table 2. Terms and Definitions (Continued)

| Term                    | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA                     | Direct Memory Access. Typically, a DMA operation copies a block of memory from one range of addresses to another, or transfers data between a peripheral and memory. On the C621x/C671x DSP, DMA transfers are performed by the enhanced DMA (EDMA) engine. These DMA transfers occur in parallel to program execution. From a cache <i>coherence</i> standpoint, EDMA accesses can be considered accesses by a parallel processor.                                                                                                                                                                                                                                                                                                                    |

| Eviction                | The process of removing a <i>line</i> from the cache to make room for newly cached data. Eviction can also occur under user control by requesting a <i>writeback-invalidate</i> for an address or range of addresses from the cache. The evicted line is referred to as the <i>victim</i> . When a victim line is <i>dirty</i> (that is, it contains updated data), the data must be written out to the next level memory to maintain <i>coherency</i> .                                                                                                                                                                                                                                                                                               |

| Execute packet          | A block of instructions that begin execution in parallel in a single cycle. An execute packet may contain between 1 and 8 instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fetch packet            | A block of 8 instructions that are fetched in a single cycle. One fetch packet may contain multiple <i>execute packets</i> , and thus may be consumed over multiple cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| First-reference miss    | A cache <i>miss</i> that occurs on the first reference to a piece of data. First-reference misses are a form of <i>compulsory miss</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fully-associative cache | A cache that allows any memory address to be stored at any location within the cache. Such caches are very flexible, but usually not practical to build in hardware. They contrast sharply with <i>direct-mapped caches</i> and <i>set-associative caches</i> , both of which have much more restrictive <i>allocation</i> policies. Conceptually, fully-associative caches are useful for distinguishing between <i>conflict misses</i> and <i>capacity misses</i> when analyzing the performance of a direct-mapped or set-associative cache. In terms of set-associative caches, a fully-associative cache is equivalent to a set-associative cache that has as many <i>ways</i> as it does <i>line frames</i> , and that has only one <i>set</i> . |

| Higher-level memory     | In a hierarchical memory system, higher-level memories are memories that are closer to the CPU. The highest level in the memory hierarchy is usually the Level 1 caches. The memories at this level exist directly next to the CPU. Higher-level memories typically act as caches for data from <i>lower-level memory</i> .                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Hit                     | A cache hit occurs when the data for a requested memory location is present in the cache. The opposite of a hit is a <i>miss</i> . A cache hit minimizes stalling, since the data can be fetched from the cache much faster than from the source memory. The determination of hit versus miss is made on each level of the memory hierarchy separately—a miss in one level may hit in a lower level.                                                                                                                                                                                                                                                                                                                                                   |

Table 2. Terms and Definitions (Continued)

| Term                                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Invalidate                           | The process of marking <i>valid</i> cache <i>lines</i> as invalid in a particular cache. Alone, this action discards the contents of the affected cache lines, and does not write back any updated data. When combined with a <i>writeback</i> , this effectively updates the next lower level of memory that holds the data, while completely removing the cached data from the given level of memory. Invalidates combined with writebacks are referred to as <i>writeback-invalidates</i> , and are commonly used for retaining <i>coherence</i> between caches. |

| Least Recently Used (LRU) allocation | For set-associative and <i>fully-associative caches</i> , least-recently used <i>allocation</i> refers to the method used to choose among <i>line frames</i> in a <i>set</i> when allocating space in the cache. When all of the line frames in the set that the address maps to contain <i>valid</i> data, the line frame in the set that was read or written the least recently (furthest back in time) is selected to hold the newly cached data. The selected line frame is then <i>evicted</i> to make room for the new data.                                  |

| Line                                 | A cache line is the smallest block of data that the cache operates on. The cache line is typically much larger than the size of data accesses from the CPU or the next higher level of memory. For instance, although the CPU may request single bytes from memory, on a read <i>miss</i> the cache reads an entire line's worth of data to satisfy the request.                                                                                                                                                                                                    |

| Line frame                           | A location in a cache that holds cached data (one <i>line</i> ), an associated <i>tag</i> address, and status information for the line. The status information can include whether the line is <i>valid</i> , <i>dirty</i> , and the current state of that line's <i>LRU</i> .                                                                                                                                                                                                                                                                                      |

| Line size                            | The size of a single cache <i>line</i> , in bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Load through                         | When a CPU request misses both the first-level and second-level caches, the data is fetched from the external memory and stored to both the first-level and second-level cache simultaneously. A cache that stores data and sends that data to the upper-level cache at the same time is a load-through cache. Using a load-through cache reduces the stall time compared to a cache that first stores the data in a lower level and then sends it to the higher-level cache as a second step.                                                                      |

| Long-distance access                 | Accesses made by the CPU to a noncacheable memory. Long-distance accesses are used when accessing external memory that is not marked as cacheable.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Lower-level memory                   | In a hierarchical memory system, lower-level memories are memories that are further from the CPU. In a C621x/C671x system, the lowest level in the hierarchy includes the system memory below L2 and any memory-mapped peripherals.                                                                                                                                                                                                                                                                                                                                 |

| LRU                                  | Least Recently Used. See <i>Least Recently Used allocation</i> for a description of the LRU replacement policy. When used alone, LRU usually refers to the status information that the cache maintains for identifying the least-recently used <i>line</i> in a <i>set</i> . For example, consider the phrase "accessing a cache line updates the LRU for that line."                                                                                                                                                                                               |

Table 2. Terms and Definitions (Continued)

| Term                  | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory ordering       | Defines what order the effects of memory operations are made visible in memory. (This is sometimes referred to as consistency.) Strong memory ordering at a given level in the memory hierarchy indicates it is not possible to observe the effects of memory accesses in that level of memory in an order different than program order. Relaxed memory ordering allows the memory hierarchy to make the effects of memory operations visible in a different order. Note that strong ordering does not require that the memory system execute memory operations in program order, only that it makes their effects visible to other requestors in an order consistent with program order. Section 8.3 covers the memory ordering assurances that the C621x/C671x memory hierarchy provides. |

| Miss                  | A cache miss occurs when the data for a requested memory location is not in the cache. A miss may stall the requestor while the <i>line frame</i> is allocated and data is fetched from the next lower level of memory. In some cases, such as a CPU write miss from L1D, it is not strictly necessary to stall the CPU. Cache misses are often divided into three categories: <i>compulsory misses</i> , <i>conflict misses</i> , and <i>capacity misses</i> .                                                                                                                                                                                                                                                                                                                             |

| Miss pipelining       | The process of servicing a single cache <i>miss</i> is pipelined over several cycles. By pipelining the miss, it is possible to overlap the processing of several misses, should many occur back-to-back. The net result is that much of the overhead for the subsequent misses is hidden, and the incremental stall penalty for the additional misses is much smaller than that for a single miss taken in isolation.                                                                                                                                                                                                                                                                                                                                                                      |

| Read allocate         | A read-allocate cache only allocates space in the cache on a read <i>miss</i> . A write miss does not cause an <i>allocation</i> to occur unless the cache is also a <i>write-allocate</i> cache. For caches that do not write allocate, the write data would be passed on to the next lower-level cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Set                   | A collection of <i>line frames</i> in a cache that a single address can potentially reside. A <i>direct-mapped cache</i> contains one line frame per set, and an N-way <i>set-associative cache</i> contains N line frames per set. A <i>fully-associative cache</i> has only one set that contains all of the line frames in the cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Set-associative cache | A set-associative cache contains multiple <i>line frames</i> that each <i>lower-level memory</i> location can be held in. When allocating room for a new <i>line</i> of data, the selection is made based on the <i>allocation</i> policy for the cache. The C621x/C671x devices employ a <i>Least Recently Used allocation</i> policy for its set-associative caches.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Snoop                 | A method by which a <i>lower-level memory</i> queries a <i>higher-level memory</i> to determine if the higher-level memory contains data for a given address. The primary purpose of snoops is to retain <i>coherency</i> , by allowing a lower-level memory to request updates from a higher-level memory. A snoop operation may trigger a <i>writeback</i> , or more commonly, a <i>writeback-invalidate</i> . Snoops that trigger writeback-invalidates are sometimes called snoop-invalidates.                                                                                                                                                                                                                                                                                          |

Table 2. Terms and Definitions (Continued)

| Term             | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tag              | A storage element containing the most-significant bits of the address stored in a particular <i>line</i> . Tag addresses are stored in special tag memories that are not directly visible to the CPU. The cache queries the tag memories on each access to determine if the access is a <i>hit</i> or a <i>miss</i> .                                                                                                                                                                                                                                                                                                                                               |

| Thrash           | An algorithm is said to thrash the cache when its access pattern causes the performance of the cache to suffer dramatically. Thrashing can occur for multiple reasons. One possible situation is that the algorithm is accessing too much data or program code in a short time frame with little or no reuse. That is, its <i>working set</i> is too large, and thus the algorithm is causing a significant number of <i>capacity misses</i> . Another situation is that the algorithm is repeatedly accessing a small group of different addresses that all map to the same set in the cache, thus causing an artificially high number of <i>conflict misses</i> . |

| Touch            | A memory operation on a given address is said to touch that address. Touch can also refer to reading array elements or other ranges of memory addresses for the sole purpose of allocating them in a particular level of the cache. A CPU-centric loop used for touching a range of memory in order to allocate it into the cache is often referred to as a touch loop. Touching an array is a form of software-controlled prefetch for data.                                                                                                                                                                                                                       |

| Valid            | When a cache <i>line</i> holds data that has been fetched from the next level memory, that <i>line frame</i> is valid. The invalid state occurs when the line frame holds no data, either because nothing has been cached yet, or because previously cached data has been <i>invalidated</i> for whatever reason ( <i>coherence</i> protocol, program request, etc.). The valid state makes no implications as to whether the data has been modified since it was fetched from the <i>lower-level memory</i> ; rather, this is indicated by the <i>dirty</i> or <i>clean</i> state of the line.                                                                     |

| Victim           | When space is allocated in a <i>set</i> for a new <i>line</i> , and all of the <i>line frames</i> in the set that the address maps to contain <i>valid</i> data, the cache controller must select one of the valid lines to <i>evict</i> in order to make room for the new data. Typically, the <i>least-recently used</i> (LRU) line is selected. The line that is <i>evicted</i> is known as the victim line. If the victim line is <i>dirty</i> , its contents are written to the next lower level of memory using a <i>victim writeback</i> .                                                                                                                   |

| Victim Buffer    | A special buffer that holds <i>victims</i> until they are <i>written back</i> . Victim <i>lines</i> are moved to the victim buffer to make room in the cache for incoming data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Victim Writeback | When a <i>dirty line</i> is <i>evicted</i> (that is, a line with updated data is evicted), the updated data is written to the lower levels of memory. This process is referred to as a victim writeback.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Way              | In a <i>set-associative cache</i> , each <i>set</i> in the cache contains multiple <i>line frames</i> . The number of line frames in each set is referred to as the number of ways in the cache. The collection of corresponding line frames across all sets in the cache is called a way in the cache. For instance, a 4-way set-associative cache has 4 ways, and each set in the cache has 4 line frames associated with it, one associated with each of the 4 ways. As a result, any given cacheable address in the memory map has 4 possible locations it can map to in a 4-way set-associative cache.                                                         |

Table 2. Terms and Definitions (Continued)

| Term                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Working set          | The working set for a program or algorithm is the total set of data and program code that is referenced within a particular period of time. It is often useful to consider the working set on an algorithm-by-algorithm basis when analyzing upper levels of memory, and on a whole-program basis when analyzing lower levels of memory.                                                                                                                                                                                                                                                                                                                                 |

| Write allocate       | A write-allocate cache allocates space in the cache when a write <i>miss</i> occurs. Space is allocated according to the cache's <i>allocation</i> policy ( <i>LRU</i> , for example), and the data for the <i>line</i> is read into the cache from the next lower level of memory. Once the data is present in the cache, the write is processed. For a <i>writeback cache</i> , only the current level of memory is updated—the write data is not immediately passed to the next level of memory.                                                                                                                                                                      |

| Writeback            | The process of writing updated data from a <i>valid</i> but <i>dirty</i> cache <i>line</i> to a <i>lower-level memory</i> . After the writeback occurs, the cache line is considered <i>clean</i> . Unless paired with an <i>invalidate</i> (as in <i>writeback-invalidate</i> ), the line remains valid after a writeback.                                                                                                                                                                                                                                                                                                                                              |

| Writeback cache      | A writeback cache will only modify its own data on a write <i>hit</i> . It will not immediately send the update to the next lower-level of memory. The data will be written back at some future point, such as when the cache <i>line</i> is <i>evicted</i> , or when the lower-level memory <i>snoops</i> the address from the <i>higher-level memory</i> . It is also possible to directly initiate a <i>writeback</i> for a range of addresses using cache control registers. A write hit to a writeback cache causes the corresponding line to be marked as <i>dirty</i> —that is, the line contains updates that have yet to be sent to the lower levels of memory. |

| Writeback-invalidate | A writeback operation followed by an invalidation. See writeback and invalidate. On the C621x/C671x devices, a writeback-invalidate on a group of cache lines only writes out data for dirty cache lines, but invalidates the contents of all of the affected cache lines.                                                                                                                                                                                                                                                                                                                                                                                               |

| Write merging        | Write merging combines multiple independent writes into a single, larger write. This improves the performance of the memory system by reducing the number of individual memory accesses it needs to process. For instance, on the C64x device, the L1D write buffer can merge multiple writes under some circumstances if they are to the same double-word address. In this example, the result is a larger effective write-buffer capacity and a lower bandwidth impact on L2.                                                                                                                                                                                          |

| Write-through cache  | A write-through cache passes all writes to the <i>lower-level memory</i> . It never contains updated data that it has not passed on to the lower-level memory. As a result, cache <i>lines</i> can never be <i>dirty</i> in a write-through cache. The C621x/C671x devices do not utilize write-through caches.                                                                                                                                                                                                                                                                                                                                                          |

## 3 Level 1 Data Cache (L1D)

The level 1 data cache (L1D) services data accesses from the CPU. The following sections describe the parameters and operation of the L1D. The operation of L1D is controlled by various registers, as described in section 7, *Memory System Controls*.

#### 3.1 L1D Parameters

The L1D is a 4K-byte cache. It is a two-way set associative cache with a 32-byte line size and 64 sets. It also features a 32-bit by 4-entry write buffer between L1D and the L2 memory.

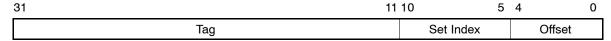

Physical addresses map onto the cache in a straightforward manner. The physical address divides into three fields as shown in Figure 3. Bits 4–0 of the address specify an offset within the line. Bits 10–5 of the address select one of the 64 sets within the cache. Bits 31–11 of the address serve as the tag for the line.

Figure 3. L1D Address Allocation

Because L1D is a two-way cache, each set contains two cache lines, one for each way. On each access, the L1D compares the tag portion of the address for the access to the tag information for both lines in the appropriate set. If the tag matches one of the lines and that line is marked valid, the access is a hit. If these conditions are not met, the access is a miss. Miss penalties are discussed in section 3.2.

The L1D is a read-allocate-only cache. This means that new lines are allocated in L1D for read misses, but not for write misses. For this reason, a 4-entry write buffer exists between the L1D and L2 caches that captures data from write misses. The write buffer is described in section 3.2.3.

The L1D implements a least-recently used (LRU) line allocation policy. This means that on an L1D read miss, the L1D evicts the least-recently read or written line within a set in order to make room for the incoming data. Note that invalid lines are always considered least-recently used.

If the selected line is dirty, that is, its contents are updated, then the victim line's data is prepared for writeback to L2 as a victim writeback. The actual victim writeback occurs after the new data is fetched, and then only if the newly fetched data is considered cacheable. If the newly fetched data is noncacheable, the victim writeback is cancelled and the victim line remains in the L1D cache.

### 3.2 L1D Performance

### 3.2.1 L1D Memory Banking

The C621x/C671x DSP does not employ a banked memory structure in L1D. The L1D is implemented with a single bank of dual-ported, 64-bit memory. This allows two simultaneous accesses on each cycle with no stalls under most circumstances. This is in contrast to the C620x/C670x and C64x devices, which use a least-significant bit (LSB) based memory banking structure that only allows one access to each bank on each cycle.

#### Note:

The L1D may stall with a bank conflict if a write occurs in parallel with another read or write within the same 64-bit double-word location.

## 3.2.2 L1D Miss Penalty

The L1D can service up to two data accesses from the CPU every cycle. Accesses that hit L1D complete without stalls.