# TMS320C6000 Host Port to MPC860 Interface

Zoran Nikolic

Digital Signal Processing Solutions

### ABSTRACT

This application report describes an interface between the Motorola MPC860 microprocessor and the host port interface (HPI) of a Texas Instruments TMS320C6000<sup>™</sup> (C6000<sup>™</sup>) digital signal processor (DSP) device. This document includes a schematic showing connections between the two devices, PAL equations, and verification that timing requirements are met for each device (tables and timing diagrams).

#### Contents

| 1   | <b>MPC860</b> | Interface                       | . 2 |

|-----|---------------|---------------------------------|-----|

|     |               | figuration                      |     |

|     |               | C860 to HPI Timing Verification |     |

| 2   | Reference     | ces                             | 13  |

| Арр | endix A       | TMS320C6x Timing Requirements   | 14  |

| Арр | endix B       | MPC860 Timing Requirements      | 17  |

| Арр | endix C       | PAL Equations                   | 18  |

### List of Figures

| Figure 1. | MPC860 to TMS320C62x/C67x/C64x (HPI16) HPI Interface Block Diagram                                           | 2  |

|-----------|--------------------------------------------------------------------------------------------------------------|----|

| Figure 2. | MPC860 to TMS320C64x (HPI32) HPI Interface Block Diagram                                                     | 3  |

| Figure 3. | MPC860 Reads Internal Memory of TMS320C62x/C67x/C64x (HPI16 Mode)<br>Using HPI (Read Without Auto-Increment) | 7  |

| Figure 4. | MPC860 Write to TMS320C62x/C67x/C64x (HPI16 Mode) HPI                                                        | 8  |

| Figure 5. | MPC860 Reads Internal Memory of TMS320C64x (HPI32 Mode) Using HPI<br>(Read Without Auto-Increment)           | 9  |

| Figure 6. | MPC860 Write to TMS320C64x (HPI32 Mode) HPI                                                                  | 10 |

## **List of Tables**

| Table 1. | MPC860 to HPI Pin Connections                                      | 3 |

|----------|--------------------------------------------------------------------|---|

| Table 2. | Base Register (BR) Relevant Bits                                   | 4 |

| Table 3. | Option Register (OR) Relevant Bits                                 | 5 |

| Table 4. | Timing Requirements for the C6201/C6701 HPI 1                      | 1 |

| Table 5. | Timing Requirements for MPC860 Interfaced to the C6201/C6701 HPI 1 | 1 |

Trademarks are the property of their respective owners.

TMS320C6000 and C6000 are trademarks of Texas Instruments.

| Table 6. Timing Requirements for the C6211/C6711 HPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 7. Timing Requirements for MPC860 Interfaced to the C6211/C6711 HPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12 |

| Table 8. Timing Requirements for the C64x HPI         C64x HPI </td <td>12</td> | 12 |

| Table 9. Timing Requirements for MPC860 Interfaced to the C64x HPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12 |

| Table A–1. TMS320C6201/C6701 Host Port Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14 |

| Table A–2.         TMS320C6211/C6711         Host Port Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15 |

| Table A–3.         TMS320C64x         Host Port Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16 |

| Table B–1.         Motorola MPC860 Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17 |

# 1 MPC860 Interface

The Motorola MPC860 PowerQUICC (quad integrated communication controller) is a single-chip integrated microprocessor. The PowerQUICC family incorporates the MC68360's communications-oriented peripheral set and integrates additional enhancements. The PowerQUICC family integrates a 32-bit embedded PowerPC core central processing unit (CPU), memory controller, RISC-based communication processor module (CPM), and system functions on a single chip.

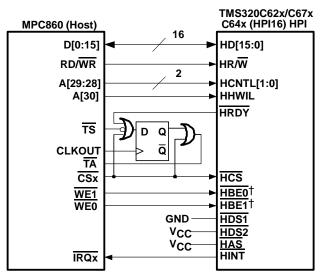

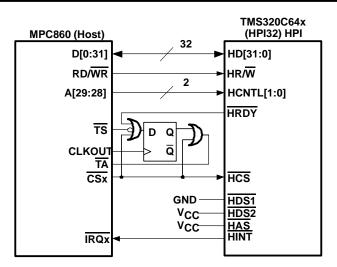

Figure 1 and Figure 2 show diagrams of the host (MPC860) interface to the HPI in TMS320C62x<sup>™</sup>, TMS320C67x<sup>™</sup>, and TMS320C64x<sup>™</sup> devices, while Table 1 shows the pin connections.

†TMS320C6201/C6701 Only

Figure 1. MPC860 to TMS320C62x/C67x/C64x (HPI16) HPI Interface Block Diagram

TMS320C62x, TMS320C67x, and TSM320C64x are trademarks of Texas Instruments.

# Figure 2. MPC860 to TMS320C64x (HPI32) HPI Interface Block Diagram

| HPI Pin                            | MPC860 Pin                        | Comments                                                                                                                                                                                                                                                        |

|------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCNTL[1:0]                         | A[28:29]                          | Address bits of MPC860 are used as control signals. A31 is the LSB of the MPC860 address bus.                                                                                                                                                                   |

| HHWIL                              | A[30]                             | Halfword identification input                                                                                                                                                                                                                                   |

| HR/W                               | RD/WR                             | Indicates a read or write access                                                                                                                                                                                                                                |

| 16-bit:HD[15:0]<br>32-bit:HD[31:0] | 16-bit:D[0:15]<br>32-bit:HD[0:31] | MPC860 uses D[0:15] for a 16-bit port interface and D[0:31] for a 32-bit port interface. D0 is the MSB of the MPC860 data bus; HD31 is the MSB of HPI.                                                                                                          |

| HDS1                               | GND                               | HDS1 and HDS2 are internally exclusively-NORed. HDS1 and HDS2 are tied logic low and high, respectively, to enable data strobe at all time.                                                                                                                     |

| HDS2                               | V <sub>CC</sub>                   | See above.                                                                                                                                                                                                                                                      |

| HAS                                | V <sub>CC</sub>                   | Because host device MPC860 has separate address and data bus, $\overline{\text{HAS}}$ does not need to be used. HAS is tied inactive high.                                                                                                                      |

| HCS                                | CSx                               | Any one of $\overline{\text{CS1}}$ to $\overline{\text{CS5}}$ of MPC860 can be connected to $\overline{\text{HCS}}$ as the chip-select signal. This also serves as the data-strobe signal in this case (because no separate MPC860 data strobe signal is used). |

| HBE0                               | WE1                               | Byte enable (TMS320C6201/C6701 only)                                                                                                                                                                                                                            |

| HBE1                               | WE0                               | Byte enable (TMS320C6201/C6701 only)                                                                                                                                                                                                                            |

| HRDY                               | TA                                | SETA bit in the MPC860 option register is set to 1 to indicate that $\overline{TA}$ is generated externally by HPI. HRDY is synchronized using the bus clock and connected to $\overline{TA}$ .                                                                 |

| HINT                               | IRQx                              | See the MPC860 User's Manual for the desired interrupt level (IRQ0 to IRQ7).                                                                                                                                                                                    |

### Table 1. MPC860 to HPI Pin Connections

For 32-bit accesses, the MPC860 data bus D[0:31] is connected to the HPI data bus HD[31:0] in reverse order, that is, D0 is connected to HD31, D1 is connected to HD30, D2 is connected to HD29, etc. This is because the most significant bit (MSB) of the MPC860 data bus is D0 and the MSB of the HPI data bus is HD32. For 16-bit accesses, the MPC860 data bus D[0:15] is connected to the HPI data bus HD[15:0] in reverse order. D0 is connected to HD15, D1 is connected to HD14, etc.

The transfer-acknowledge (TA) signal of the MPC860 chip is a synchronous signal; therefore, the HRDY signal of the HPI must be synchronized for the interface to function properly.

# 1.1 Configuration

The MPC860's memory controller is responsible for the control of up to eight memory banks and provides a set of eight programmable chip-select signals. A chip-select of the MPC860 is tied to the HCS input of the HPI. This simplifies the interfacing to the HPI.

Status bits for each one of the memory banks are in the memory controller status register (MSTAT). There is only one MSTAT for the entire memory controller. Each memory bank has a base register (BR) and an option register (OR). The MSTAT reports write-protect violations and parity errors for every bank. The BRx and the ORx registers are specific to memory bank x. The BR contains a valid (V) bit that indicates that the register information for that chip-select is valid.

Each one of the OR registers defines the attributes for the general-purpose chip-select machine when accessing the corresponding bank.

The general-purpose chip-select machine (GPCM) allows a glue-less and flexible interface between the MPC860 and HPI. If the MS bits in the BRx of the selected bank (Bank x) select the GPCM machine, the attributes for the memory cycle initiated are taken from the ORx register. These attributes include the CSNT, ACS(0:1), SCY(0:3), TRLX, EHTR, and SETA fields.

The configuration of the BR and OR is shown in Table 2 and Table 3.

| Bit Field | Description                                                                                                                                                                                                                                                                                                                                                             | Value                                          |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| BA[0:16]  | Base address<br>The base-address field, the upper 17 bits of each base-address register, and the<br>address-type code field are compared to the address on the address bus to<br>determine if a memory bank controlled by the memory controller is being accessed<br>by an internal bus master. These bits are used in conjunction with the AM[0:16] bits<br>in the OR. |                                                |

| PS[0:1]   | Port Size<br>This field specifies the port size of this memory region.                                                                                                                                                                                                                                                                                                  | 10 = 16-bit port size<br>00 = 32-bit port size |

| WP        | Write protect<br>This bit can restrict write accesses within the address range of a base register.                                                                                                                                                                                                                                                                      | 0 = Both read and write accesses are allowed.  |

| MS[0:1]   | Machine select<br>This field specifies the machine selected for the memory operations handling.                                                                                                                                                                                                                                                                         | 00 = GPCM                                      |

| V         | Valid bit<br>This bit indicat <u>es</u> that the contents of the base register and the option register pair<br>are valid. The CS signal does not assert until the V-bit is set.                                                                                                                                                                                         | 1 = This bank is valid.                        |

## Table 2. Base Register (BR) Relevant Bits

| Bit Field | Description                                                                                                                                                                                                                  | Value                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| AM[0:16]  | Address mask<br>The address mask provides masking on any corresponding bits in the associated<br>base register. By masking the address bits independently, external devices of<br>different size address ranges can be used. |                                                                                  |

| ATM[0:2]  | Address type mask<br>This field can be used to mask certain address type bits, allowing more than one<br>address space type to be assigned to a chip-select.                                                                 |                                                                                  |

| CSNT      | Chip-select negation time<br>This attribute is used to determine when CS/WE are negated during an external<br>memory write access handled by the GPCM.                                                                       | $0 = \overline{CS}/\overline{WE} \text{ are negated}$ normally.                  |

| ACS[0:1]  | Address to c <u>hip</u> -select setup<br>It allows the CS assertion to be delayed relative to the address change.                                                                                                            | $11 = \overline{CS}$ is output half a clock later than the address lines.        |

| BI        | Burst inhibit<br>This attribute determines whether or not this memory bank supports burst accesses.                                                                                                                          | 1 = This bank does not<br>support burst accesses.                                |

| SCY[0:3]  | Cycle length in clocks                                                                                                                                                                                                       | Because an external $\overline{TA}$ response is selected, SCY bits are not used. |

| SETA      | External transfer acknowledge                                                                                                                                                                                                | $1 = \overline{TA}$ is generated by external logic.                              |

| TRLX      | Timing relaxed<br>This bit, when asserted, modifies the timing of the signals that control the memory<br>devices when the GPCM is selected to handle the memory access initiated to this<br>memory region.                   | 0 = Normal timing is generated by GPCM.                                          |

| EHTR      | Extended hold time on read access.<br>This bit, when asserted, inserts an idle clock cycle after a read access from the<br>current bank and any MPC860.                                                                      | 0 = Normal timing is generated by the memory controller.                         |

# Table 3. Option Register (OR) Relevant Bits

# 1.2 MPC860 to HPI Timing Verification

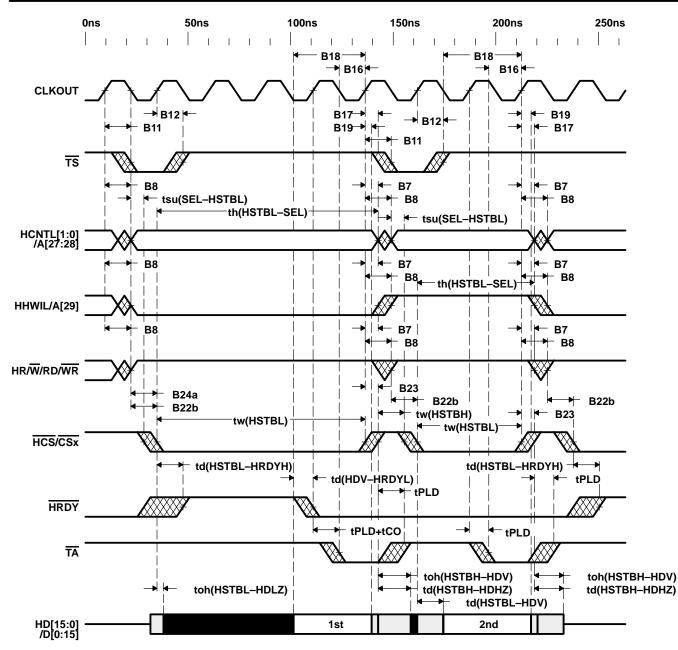

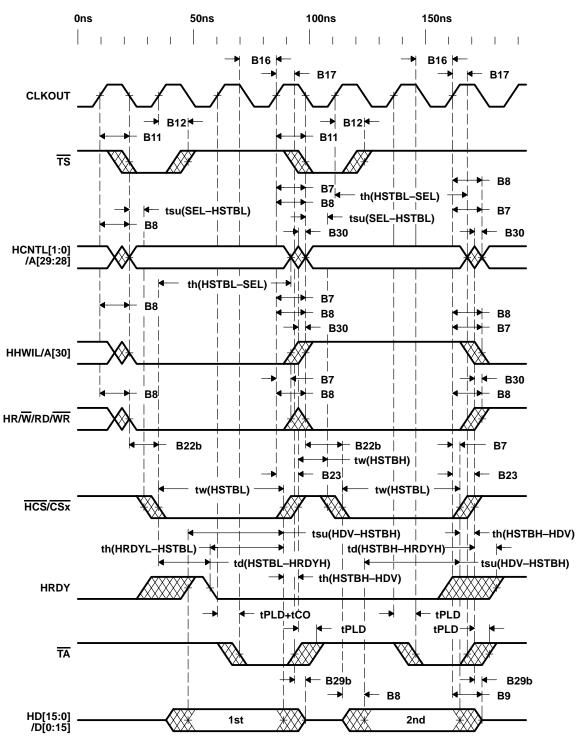

To verify proper operation, two functions have been examined:

- 1. an MPC860 write to HPI.

- 2. an MPC860 read from HPI.

In each instance, timing requirements were compared for each of the devices. The results are shown in the following tables and timing diagrams.

In the following figures and tables, tPLD and tCO represent the propagation time from input to combinatorial output and the propagation time from the clock to output, respectively, for the PALLV22V10.

Note that on a first halfword write, when  $\overline{CS}$  becomes valid,  $\overline{HRDY}$  indicates that the HPI is busy completing the internal portion of a previous HPI request.

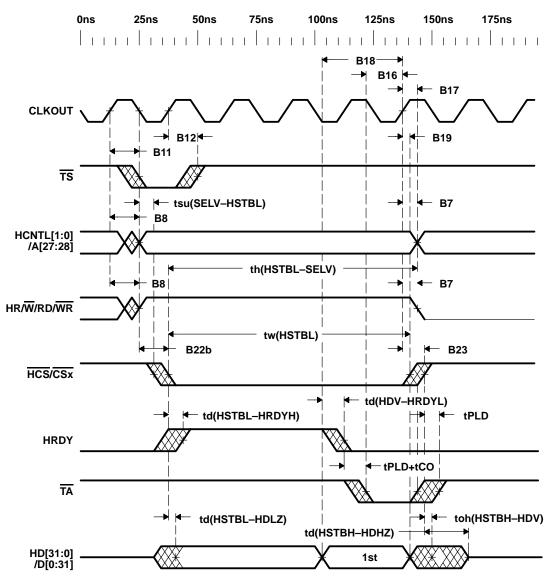

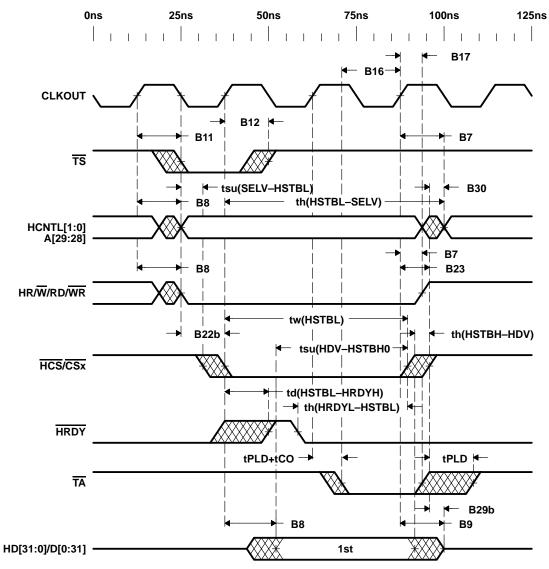

The parameters in Figure 3 through Figure 6 and Table 4 through Table 9 are named in the same way as those in the data sheets listed in the Reference section of this report. Actual timing parameter values are listed in Appendix A and Appendix B.

The tables and timing diagrams show that the timing parameters for both devices are met in the interface of the MPC860 and the HPI. This interface is based on an MPC860/40-MHz device and all TMS320C6x<sup>™</sup> HPI devices.

TMS320C6x is a trademark of Texas Instruments.

Figure 3. MPC860 Reads Internal Memory of TMS320C62x/C67x/C64x (HPI16 Mode) Using HPI (Read Without Auto-Increment)

TEXAS INSTRUMENTS

Figure 4. MPC860 Write to TMS320C62x/C67x/C64x (HPI16 Mode) HPI

Figure 5. MPC860 Reads Internal Memory of TMS320C64x (HPI32 Mode) Using HPI (Read Without Auto-Increment)

Figure 6. MPC860 Write to TMS320C64x (HPI32 Mode) HPI

| HPI Symbol                  | MPC860 Symbol                   |                                                     | Min<br>HPI (ns)      | Min<br>MPC860<br>(ns) |

|-----------------------------|---------------------------------|-----------------------------------------------------|----------------------|-----------------------|

| t <sub>su</sub> (SEL-HSTBL) | B24a                            | Setup time, Select signals valid before HSTROBE low | 4                    | 10                    |

| <sup>t</sup> h(HSTBL-SEL)   | 2.5*P <sub>M</sub> –B22b + B7   | Hold time, select signals valid after HSTROBE low   | 2                    | 55.75                 |

| <sup>t</sup> w(HSTBL)       | 2.5*P <sub>M</sub> – B22b +B23  | Pulse Duration, HSTROBE low                         | 2*P <sub>H</sub> =10 | 51.5                  |

| <sup>t</sup> w(HSTBH)       | 0.5*P <sub>M</sub> – B23 + B22b | Pulse Duration, HSTROBE high                        | 2*P <sub>H</sub> =10 | 10.75                 |

| t <sub>su(HDV-HSTBH)</sub>  | 2*P <sub>M</sub> – B8 + B23     | Setup time, host data valid before HSTROBE high     | 3                    | 39                    |

| <sup>t</sup> h(HSTBH-HDV)   | B29b                            | Hold time, host data valid after HSTROBE high       | 2                    | 4.25                  |

| <sup>t</sup> h(HRDYL-HSTBL) | 0.5*P <sub>M</sub> + B23        | Hold time, HSTROBE low after HRDY low               | 1                    | 14.5                  |

# Table 4. Timing Requirements for the C6201/C6701 HPI

NOTE:  $P_H$  = Period of TMS320C6201/C6701 clock = 5 ns at 200 MHz.  $P_M$  = Period of MPC860 clock = 25 ns at 40 MHz.

# Table 5. Timing Requirements for MPC860 Interfaced to the C6201/C6701 HPI

| HPI Symbol                                         | MPC860<br>Symbol |                                               | Min<br>HPI (ns) | Min<br>MPC860<br>(ns) |

|----------------------------------------------------|------------------|-----------------------------------------------|-----------------|-----------------------|

| B23 + t <sub>h(HSTBH-HDV)</sub>                    | B19              | Input data hold time from CLKOUT rising edge  | 4               | 1                     |

| $2.5^{*}P_{M} - B22b - t_{d(HSTBL-HDV)}$           | B18              | Data in valid to clock high (read setup time) | 37.5            | 6                     |

| P <sub>M</sub> - t <sub>PLD</sub> -t <sub>CO</sub> | B16              | TA valid to CLKOUT (setup time)               | 15              | 9.75                  |

| B23+t <sub>PLD</sub>                               | B17              | CLKOUT to TA valid (hold time)                | 7               | 1                     |

NOTE: P<sub>H</sub> = Period of TMS320C6201/C6701 clock = 5 ns at 200 MHz.

P<sub>M</sub> = Period of MPC860 clock = 25 ns at 40 MHz.

## Table 6. Timing Requirements for the C6211/C6711 HPI

| HPI Symbol                  | MPC860 Symbol                  | Parameter                                           | Min<br>HPI (ns)     | Min<br>MPC860<br>(ns) |

|-----------------------------|--------------------------------|-----------------------------------------------------|---------------------|-----------------------|

| t <sub>su(SEL-HSTBL)</sub>  | B24a                           | Setup time, select signals valid before HSTROBE low | 5                   | 10                    |

| <sup>t</sup> h(HSTBL-SEL)   | 2.5P <sub>M</sub> –B22b + B7   | Hold time, select signals valid after HSTROBE low   | 4                   | 55.75                 |

| <sup>t</sup> w(HSTBL)       | 2.5P <sub>M</sub> – B22b + B23 | Pulse Duration, HSTROBE low                         | 4P <sub>H</sub> =24 | 51.5                  |

| t <sub>w(HSTBH)</sub>       | 0.5P <sub>M</sub> – B23 + B22b | Pulse Duration, HSTROBE high                        | 4P <sub>H</sub> =24 | 10.75†                |

| t <sub>su(HDV-HSTBH)</sub>  | 2P <sub>M</sub> – B8 + B23     | Setup time, host data valid before HSTROBE high     | 5                   | 39                    |

| <sup>t</sup> h(HSTBH-HDV)   | B29b                           | Hold time, host data valid after HSTROBE high       | 3                   | 4.25                  |

| <sup>t</sup> h(HRDYL-HSTBL) | 0.5P <sub>M</sub> + B23        | Hold time, HSTROBE low after HRDY low               | 2                   | 14.5                  |

<sup>+</sup> To ensure that t<sub>w(HSTBH)</sub> is not violated for the C6211/C6711, the MPC860 should insert at least 13.25 ns of time between consecutive accesses to the HPI

NOTE:  $P_H$  = Period of TMS320C6211/C6711 clock = 6 ns at 167 MHz.

$P_{M}$  = Period of MPC860 clock = 25 ns at 40 MHz.

# Table 7. Timing Requirements for MPC860 Interfaced to the C6211/C6711 HPI

| HPI Symbol                                            | MPC860<br>Symbol |                                               | Min<br>HPI (ns) | Min<br>MPC860<br>(ns) |

|-------------------------------------------------------|------------------|-----------------------------------------------|-----------------|-----------------------|

| B23 + t <sub>h(HSTBH-HDV)</sub>                       | B19              | Input data hold time from CLKOUT rising edge  | 5               | 1                     |

| 2.5*P <sub>M</sub> – B22b – t <sub>d(HSTBL-HDV)</sub> | B18              | Data in valid to clock high (read setup time) | 38.5            | 6                     |

| P <sub>M</sub> – t <sub>PLD</sub> -t <sub>CO</sub>    | B16              | TA valid to CLKOUT (setup time)               | 15              | 9.75                  |

| B23+t <sub>PLD</sub>                                  | B17              | CLKOUT to TA valid (hold time)                | 7               | 1                     |

NOTE:  $P_H$  = Period of TMS320C6211/C6711 clock = 6 ns at 167 MHz.

$P_{M}$  = Period of MPC860 clock = 25 ns at 40 MHz.

### Table 8. Timing Requirements for the C64x HPI

| HPI Symbol                  | MPC860 Symbol                                | Parameter                                           | Min<br>HPI (ns)      | Min<br>MPC860<br>(ns) |

|-----------------------------|----------------------------------------------|-----------------------------------------------------|----------------------|-----------------------|

| t <sub>su(SEL-HSTBL)</sub>  | B24a                                         | Setup time, select signals valid before HSTROBE low | 5                    | 10                    |

| <sup>t</sup> h(HSTBL-SEL)   | 2.5 <sup>†</sup> P <sub>M</sub> –B22b + B7   | Hold time, select signals valid after HSTROBE low   | 2                    | 55.75                 |

| t <sub>w(HSTBL)</sub>       | 2.5 <sup>†</sup> P <sub>M</sub> – B22b +B23  | Pulse Duration, HSTROBE low                         | 4†P <sub>H</sub> =10 | 51.5                  |

| t <sub>w(HSTBH)</sub>       | 0.5 <sup>†</sup> P <sub>M</sub> – B23 + B22b | Pulse Duration, HSTROBE high                        | 4†P <sub>H</sub> =10 | 10.75                 |

| t <sub>su(HDV-HSTBH)</sub>  | 2*P <sub>M</sub> – B8 + B23                  | Setup time, host data valid before HSTROBE high     | 5                    | 39                    |

| <sup>t</sup> h(HSTBH-HDV)   | B29b                                         | Hold time, host data valid after HSTROBE high       | 2                    | 4.25                  |

| <sup>t</sup> h(HRDYL-HSTBL) | 0.5 <sup>†</sup> P <sub>M</sub> + B23        | Hold time, HSTROBE low after HRDY low               | 2                    | 14.5                  |

NOTE:  $P_H$  = Period of TMS320C64x DSP clock = 2.5 ns at 400 MHz.

$P_{M}$  = Period of MPC860 clock = 25 ns at 40 MHz.

NOTE: The timing specifications above are preliminary and the actual numbers may vary with a TMS part. Please refer to the latest data sheet for numbers.

## Table 9. Timing Requirements for MPC860 Interfaced to the C64x HPI

| HPI Symbol                                         | MPC860<br>Symbol |                                               | Min<br>HPI (ns) | Min<br>MPC860<br>(ns) |

|----------------------------------------------------|------------------|-----------------------------------------------|-----------------|-----------------------|

| B23 + t <sub>h(HSTBH-HDV)</sub>                    | B19              | Input data hold time from CLKOUT rising edge  | 5               | 1                     |

| $2.5^{*}P_{M} - B22b - t_{d(HSTBL-HDV)}$           | B18              | Data in valid to clock high (read setup time) | 41.5            | 6                     |

| P <sub>M</sub> - t <sub>PLD</sub> -t <sub>CO</sub> | B16              | TA valid to CLKOUT (setup time)               | 15              | 9.75                  |

| B23+t <sub>PLD</sub>                               | B17              | CLKOUT to TA valid (hold time)                | 7               | 1                     |

NOTE:  $P_H$  = Period of TMS320C64x DSP clock = 2.5 ns at 400 MHz.

$P_{M}$  = Period of MPC860 clock = 25 ns at 40 MHz.

NOTE: The timing specifications above are preliminary and the actual numbers may vary with a TMS part. Please refer to the latest data sheet for numbers.

# 2 References

- 1. TMS320C6000 Peripherals Reference Guide (SPRU190).

- 2. TMS320C6201 Digital Signal Processor (SPRS051).

- 3. TMS320C6701 Floating-Point Digital Signal Processor (SPRS067).

- 4. TMS320C6211, TMS320C6211B Fixed-Point Digital Signal Processors (SPRS073).

- 5. TMS320C6416 Fixed-Point Digital Signal Processor (SPRS164).

- 6. MPC860 Data Sheet, Motorola, Inc.

- 7. MPC860 User's Guide, Motorola, Inc.

# Appendix A TMS320C6x Timing Requirements

# Table A–1. TMS320C6201/C6701 Host Port Timing Specifications

| Symbol                       | Characteristic                                                                                                                                                                   | Min<br>(ns) | Max<br>(ns) |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| t <sub>su</sub> (SEL-HSTBL)  | Setup time, select signals <sup>§</sup> valid before HSTROBE <sup>†</sup> low                                                                                                    | 4           |             |

| <sup>t</sup> h(HSTBL-SEL)    | Hold time, select signals ${}^{\mbox{\scriptsize S}}$ valid after HSTROBE <sup>†</sup> low                                                                                       | 2           |             |

| t <sub>w(HSTBL)</sub>        | Pulse duration, HSTROBE <sup>†</sup> low                                                                                                                                         | 2P‡         |             |

| t <sub>w(HSTBH)</sub>        | Pulse duration, HSTROBE <sup>†</sup> high between consecutive accesses                                                                                                           | 2P‡         |             |

| t <sub>su(HDV-HSTBH)</sub>   | Setup time, host data valid before HSTROBE <sup>†</sup> high                                                                                                                     | 3           |             |

| <sup>t</sup> h(HSTBH-HDV)    | Hold time, host data valid after HSTROBE <sup>†</sup> high                                                                                                                       | 2           |             |

| <sup>t</sup> h(HRDYL-HSTBL)  | Hold time, HSTROBE <sup>†</sup> low after HRDY low. HSTROBE <sup>†</sup> should not be inactivated until HRDY is active (low); otherwise, HPI writes will not complete properly. | 1           |             |

| <sup>t</sup> d(HCS-HRDY)     | Delay time, HCS to HRDY¶                                                                                                                                                         | 1           | 9           |

| <sup>t</sup> d(HSTBL-HRDYH)  | Delay time, HSTROBE <sup>†</sup> low to HRDY high <sup>#</sup>                                                                                                                   | 3           | 12          |

| t <sub>oh</sub> (HSTBL-HDLZ) | Output hold time, HD low impedance after HSTROBE <sup>†</sup> low for an HPI read                                                                                                | 4           |             |

| <sup>t</sup> d(HDV-HRDYL)    | Delay time, HD valid to HRDY low                                                                                                                                                 | P‡-3        | P‡ + 3      |

| t <sub>oh</sub> (HSTBH-HDV)  | Output hold time, HD valid after HSTROBE <sup>†</sup> high                                                                                                                       | 2           | 12          |

| t <sub>d(HSTBH-HDHZ)</sub>   | Delay time, HSTROBE <sup>†</sup> high to HD high impedance                                                                                                                       | 3           | 12          |

| <sup>t</sup> d(HSTBL-HDV)    | Delay time, HSTROBE <sup>†</sup> low to HD valid                                                                                                                                 | 3           | 12          |

| <sup>t</sup> d(HSTBH-HRDYH)  | Delay time, HSTROBE <sup>†</sup> high to HRDY high <sup>  </sup>                                                                                                                 | 3           | 12          |

<sup>†</sup>HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

$\ddagger$  P = 1/CPU clock frequency in ns. For example, when running parts at 200 MHz, use P = 5 ns.

§ Select signals include: HCNTRL[1:0], HR/W, and HHWIL.

I HCS enables HRDY, and HRDY is always low when HCS is high. The case where HRDY goes high when HCS falls indicates that HPI is busy completing a previous HPID write or READ with autoincrement.

<sup>#</sup> This parameter is used during an HPID read. At the beginning of the first half-word transfer on the falling edge of HSTROBE, the HPI sends the request to the DMA auxiliary channel, and HRDY remains high until the DMA auxiliary channel loads the requested data into HPID.

This parameter is used after the second half-word of an HPID write or autoincrement read. HRDY remains low if the access is not an HPID write or autoincrement read. Reading or writing to HPIC or HPIA does not affect the HRDY signal.

| Symbol                       | Characteristic                                                                                                                                                                   | Min<br>(ns) | Max<br>(ns) |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| t <sub>su</sub> (SELV-HSTBL) | Setup time, select signals <sup>§</sup> valid before HSTROBE <sup>†</sup> low                                                                                                    | 5           |             |

| <sup>t</sup> h(HSTBL-SELV)   | Hold time, select signals <sup>§</sup> valid after HSTROBE <sup>†</sup> low                                                                                                      | 4           |             |

| t <sub>w(HSTBL)</sub>        | Pulse duration, HSTROBE <sup>†</sup> low                                                                                                                                         | 4P‡         |             |

| t <sub>w(HSTBH)</sub>        | Pulse duration, HSTROBE <sup>†</sup> high between consecutive accesses                                                                                                           | 4P‡         |             |

| t <sub>su(HDV-HSTBH)</sub>   | Setup time, host data valid before HSTROBE <sup>†</sup> high                                                                                                                     | 5           |             |

| <sup>t</sup> h(HSTBH-HDV)    | Hold time, host data valid after HSTROBE <sup>†</sup> high                                                                                                                       | 3           |             |

| <sup>t</sup> h(HRDYL-HSTBL)  | Hold time, HSTROBE <sup>†</sup> low after HRDY low. HSTROBE <sup>†</sup> should not be inactivated until HRDY is active (low); otherwise, HPI writes will not complete properly. | 2           |             |

| <sup>t</sup> d(HCS-HRDY)     | Delay time, HCS to HRDY¶                                                                                                                                                         | 1           | 15          |

| <sup>t</sup> d(HSTBL-HRDYH)  | Delay time, HSTROBE <sup>†</sup> low to HRDY high <sup>#</sup>                                                                                                                   | 3           | 15          |

| t <sub>oh</sub> (HSTBL-HDLZ) | Output hold time, HD low impedance after HSTROBE <sup>†</sup> low for an HPI read                                                                                                | 2           |             |

| <sup>t</sup> d(HDV-HRDYL)    | Delay time, HD valid to HRDY low                                                                                                                                                 | 2P‡-4       | 2P‡         |

| t <sub>oh(HSTBH-HDV)</sub>   | Output hold time, HD valid after HSTROBE <sup>†</sup> high                                                                                                                       | 3           | 15          |

| <sup>t</sup> d(HSTBH-HDHZ)   | Delay time, HSTROBE <sup>†</sup> high to HD high impedance                                                                                                                       | 3           | 15          |

| <sup>t</sup> d(HSTBL-HDV)    | Delay time, HSTROBE <sup>†</sup> low to HD valid                                                                                                                                 | 3           | 15          |

| <sup>t</sup> d(HSTBH-HRDYH)  | Delay time, HSTROBE <sup>†</sup> high to HRDY high <sup>∥</sup>                                                                                                                  | 3           | 15          |

# Table A–2. TMS320C6211/C6711 Host Port Timing Specifications

<sup>†</sup>HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

$\ddagger P = 1/CPU$  clock frequency in ns. For example, when running parts at 167 MHz, use P = 6 ns.

§ Select signals include: HCNTRL[1:0], HR/W, and HHWIL.

THCS enables HRDY, and HRDY is always low when HCS is high. The case where HRDY goes high when HCS falls indicates that HPI is busy completing a previous HPID write or READ with autoincrement.

<sup>#</sup> This parameter is used during an HPID read. At the beginning of the first half-word transfer on the falling edge of HSTROBE, the HPI sends the request to the DMA auxiliary channel, and HRDY remains high until the DMA auxiliary channel loads the requested data into HPID.

This parameter is used after the second half-word of an HPID write or autoincrement read. HRDY remains low if the access is not an HPID write or autoincrement read. Reading or writing to HPIC or HPIA does not affect the HRDY signal.

| Symbol                       | Characteristic                                                                                                                                                                   | Min<br>(ns) | Max<br>(ns) |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| t <sub>su</sub> (SELV-HSTBL) | Setup time, select signals <sup>§</sup> valid before HSTROBE <sup>†</sup> low                                                                                                    | 5           |             |

| <sup>t</sup> h(HSTBL-SELV)   | Hold time, select signals <sup>§</sup> valid after HSTROBE <sup>†</sup> low                                                                                                      | 2           |             |

| <sup>t</sup> w(HSTBL)        | Pulse duration, HSTROBE <sup>†</sup> low                                                                                                                                         | 4P‡         |             |

| <sup>t</sup> w(HSTBH)        | Pulse duration, HSTROBE <sup>†</sup> high between consecutive accesses                                                                                                           | 4P‡         |             |

| t <sub>su(HDV-HSTBH)</sub>   | Setup time, host data valid before HSTROBE <sup>†</sup> high                                                                                                                     | 5           |             |

| <sup>t</sup> h(HSTBH-HDV)    | Hold time, host data valid after HSTROBE <sup>†</sup> high                                                                                                                       | 2           |             |

| <sup>t</sup> h(HRDYL-HSTBL)  | Hold time, HSTROBE <sup>†</sup> low after HRDY low. HSTROBE <sup>†</sup> should not be inactivated until HRDY is active (low); otherwise, HPI writes will not complete properly. | 2           |             |

| <sup>t</sup> d(HCS-HRDY)     | Delay time, HCS to HRDY¶                                                                                                                                                         | 1           | 7           |

| <sup>t</sup> d(HSTBL-HRDYH)  | Delay time, HSTROBE <sup>†</sup> low to HRDY high <sup>#</sup>                                                                                                                   | 3           | 12          |

| <sup>t</sup> oh(HSTBL-HDLZ)  | Output hold time, HD low impedance after HSTROBE <sup>†</sup> low for an HPI read                                                                                                | 2           |             |

| <sup>t</sup> d(HDV-HRDYL)    | Delay time, HD valid to HRDY low                                                                                                                                                 | 2P‡-6       |             |

| <sup>t</sup> oh(HSTBH-HDV)   | Output hold time, HD valid after HSTROBE <sup>†</sup> high                                                                                                                       | 3           |             |

| <sup>t</sup> d(HSTBH-HDHZ)   | Delay time, HSTROBE <sup>†</sup> high to HD high impedance                                                                                                                       |             | 12          |

| <sup>t</sup> d(HSTBL-HDV)    | Delay time, HSTROBE <sup>†</sup> low to HD valid                                                                                                                                 |             | 12          |

| <sup>t</sup> d(HSTBH-HRDYH)  | Delay time, HSTROBE <sup>†</sup> high to HRDY high <sup>  </sup>                                                                                                                 | 3           | 12          |

### Table A–3. TMS320C64x Host Port Timing Specifications

<sup>†</sup>HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

$\ddagger$  P = 1/CPU clock frequency in ns. For example, when running parts at 600 MHz, use P = 1.67 ns.

§ Select signals include: HCNTRL[1:0], HR/W, and HHWIL.

¶ HCS enables HRDY, and HRDY is always low when HCS is high. The case where HRDY goes high when HCS falls indicates that HPI is busy completing a previous HPID write or READ with autoincrement.

<sup>#</sup> This parameter is used during an HPID read. At the beginning of the first half-word transfer on the falling edge of HSTROBE, the HPI sends the request to the DMA auxiliary channel, and HRDY remains high until the DMA auxiliary channel loads the requested data into HPID.

This parameter is used after the second half-word of an HPID write or autoincrement read. HRDY remains low if the access is not an HPID write or autoincrement read. Reading or writing to HPIC or HPIA does not affect the HRDY signal.

The timing requirements in the tables above are provided for quick reference only. For detailed description, notes, and restrictions, please see the data sheets listed in the Reference section of this report.

# Appendix B MPC860 Timing Requirements

| Symbol | Characteristic                                                                                | Min<br>(ns) | Max<br>(ns) |

|--------|-----------------------------------------------------------------------------------------------|-------------|-------------|

| B7     | CLKOUT to A[0:31], RD/WR,D invalid                                                            | 6.25        |             |

| B8     | CLKOUT to A(0:31), RD/WR,D(0:31),DP(0:3) valid                                                | 6.25        | 13          |

| B9     | CLKOUT to A(0:31),RD/WR,D(0:31) High-Z                                                        | 6.25        | 13          |

| B11    | CLKOUT to TS,BB assertion                                                                     | 6.25        | 12.25       |

| B12    | CLKOUT to TS,BB negation                                                                      | 6.25        | 13          |

| B18    | Data, DP valid to CLKOUT rising edge (setup time)                                             | 6           |             |

| B19    | CLKOUT rising edge to data, DP valid (hold time)                                              | 1           |             |

| B22    | CLKOUT rising edge to $\overline{CS}$ asserted (GPCM ACS = 00,TRLX = 0)                       | 6.25        | 13          |

| B22b   | CLKOUT rising edge to $\overline{CS}$ asserted (GPCM ACS = 11,TRLX = 0)                       | 6.25        | 13          |

| B23    | CLKOUT rising edge to CS negated – GPCM read access                                           | 2           | 8           |

| B24a   | A(0:31) to $\overline{CS}$ asserted (GPCM ACS = 11, TRLX = 0)                                 | 10.5        |             |

| B25    | CLKOUT rising edge to OE,WE(0:3) asserted                                                     |             | 9           |

| B26    | CLKOUT rising edge to OE negated                                                              | 2           | 9           |

| B28    | CLKOUT rising edge to $\overline{WE(0:3)}$ negated – $\overline{GPCM}$ write access, CSNT = 0 |             | 9           |

| B29B   | CS negated to data Hi-Z (write access) CSNT=0                                                 | 4.25        |             |

| B29    | WE(0:3) negated to D Hi-Z – GPCM write access, CSNT=0                                         | 4.25        |             |

| B30    | CS,WE(0:3) negated to A(0:31) invalid – GPCM write access                                     | 4.25        |             |

| B11A   | CLKOUT to TA, BI assertion                                                                    | 2.5         | 9.25        |

| B12A   | CLKOUT to TA, BI negation                                                                     | 2.5         | 11          |

| B13A   | CLKOUT to TA BI Hi-Z                                                                          | 2.5         | 15          |

| B7     | CLOCKOUT to D[31:0] invalid                                                                   | 6.25        |             |

| B16    | TA valid to CLKOUT (setup time)                                                               | 9.75        |             |

| B17    | CLKOUT to $\overline{TA}$ (hold time)                                                         | 1           |             |

# Table B–1. Motorola MPC860 Timing Parameters

The timing requirements in Table 13 are provided for quick reference only. For detailed description, notes, and restrictions, please visit Motorola's web site at http://www.motorola.com.

# Appendix C PAL Equations

# TEXAS INSTRUMENTS

### SPRA546A

| Synario 3.10 - Device Utili:<br>hpi2860.bls<br>P22V10C Chip Diagram: | zatio    | on C  | har | t        |    |        | Fr | i Apr 09 17:42:38 1999 |

|----------------------------------------------------------------------|----------|-------|-----|----------|----|--------|----|------------------------|

|                                                                      |          | <br>P | 22V | <br>7100 |    |        |    |                        |

|                                                                      | Н        | -     | C   |          | •  |        |    |                        |

|                                                                      | R        | С     | L   |          |    |        |    |                        |

|                                                                      | D        | S     | K   |          |    | Ν      |    |                        |

|                                                                      |          | x     |     |          |    | _      |    |                        |

|                                                                      | n        | n     | Ν   |          |    | 6      |    |                        |

|                                                                      | //       | 3     | 2   | 1        | 28 | <br>27 | 26 | -                      |

|                                                                      |          |       |     |          |    |        |    |                        |

| TSn                                                                  | 5<br>    |       |     |          |    |        | 25 |                        |

|                                                                      | 6        |       |     |          |    |        | 24 | 1                      |

|                                                                      | <br>  7  |       |     |          |    |        | 23 |                        |

|                                                                      | 8        |       |     |          |    |        | 22 |                        |

|                                                                      | <br>  9  |       |     |          |    |        | 21 |                        |

|                                                                      | <br>  10 |       |     |          |    |        | 20 |                        |

|                                                                      | <br>  11 |       |     |          |    |        | 19 |                        |

|                                                                      | <br>  12 | 13    | 14  | 15       | 16 | 17     | 18 |                        |

|                                                                      |          |       |     |          |    | !      |    | -                      |

|                                                                      |          |       |     |          |    | T<br>A |    |                        |

|                                                                      |          |       |     |          |    | n      |    |                        |

| SIGNA                                                                | TURE:    | N/    | A   |          |    |        |    |                        |

# TEXAS INSTRUMENTS

SPRA546A

| Synario 3.10 - Device Utilization Chart Fri Apr 09 17:42:38 1999<br>hpi2860.bls<br>P22V10C Resource Allocations:                 |              |             |             |           |          |        | 8 1999 |

|----------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------|-----------|----------|--------|--------|

| Device                                                                                                                           | .gn          |             |             |           |          |        |        |

| Resources   Available   Require                                                                                                  |              |             | ement       | Uni       | used     |        |        |

|                                                                                                                                  | =========    | ======      | ======      | ====      |          | ===    |        |

| Input Pins:                                                                                                                      |              | <br>        |             |           |          |        |        |

| Input:                                                                                                                           | <br>  12<br> | <br>  4<br> | <br>        | 8 ( 66 %) |          |        |        |

| Output Pins:                                                                                                                     |              | <br> <br>   |             |           |          |        |        |

| In/Out:                                                                                                                          | 10           | 2           | 2           |           | 8 ( 80 9 | 8)     |        |

| Output:                                                                                                                          | -            | –           | ·           |           | _        |        |        |

| Buried Nodes:                                                                                                                    | <br> <br>    | <br> <br>   | <br> <br>   |           |          |        |        |

| Input Reg:                                                                                                                       | _            | '<br>  -    | -           |           | _        |        |        |

| Pin Reg:                                                                                                                         | 10           | 1           | .           |           | 9 ( 90 9 | 8)     |        |

| Buried Reg:                                                                                                                      |              | -           | -           |           | -        |        |        |

| Page 5<br>Synario 3.10 - Device Utilization Chart Fri Apr 09 17:42:38 1999<br>hpi2860.bls<br>P22V10C Product Terms Distribution: |              |             |             |           |          |        |        |

| Signal                                                                                                                           |              |             | Pin         | n   Terms |          | Terms  | Terms  |

| Name                                                                                                                             |              |             | Assign      | led       | Used     | Max    | Unused |

|                                                                                                                                  |              | ======      | ======      | ===       | ======   | ====== | ====== |

| TAn                                                                                                                              |              | 17          |             | 1         | 8        | 7      |        |

| N_6.D                                                                                                                            | 27           |             | 3           | 8         | 5        |        |        |

| ==== List of Input<br>Signal Name                                                                                                | cs/Feedbacks | ====        | Din         |           |          |        |        |

|                                                                                                                                  | Pin<br>      |             | Pin Tyı<br> |           |          |        |        |

| CLKIN                                                                                                                            | 2            |             | CLK/IN      |           |          |        |        |

| CSxn                                                                                                                             |              |             | 3           |           | INPUT    |        |        |

| HRDYn                                                                                                                            |              |             | 4           |           | INPUT    |        |        |

| TSn                                                                                                                              | 5            |             | INPUT       |           |          |        |        |

#### SPRA546A

### Synario 3.10 - Device Utilization Chart

Fri Apr 09 17:42:39 1999

hpi2860.bls

#### P22V10C Unused Resources:

\_\_\_\_\_

| Pin<br>Number | Pin<br>Type | Product<br>Terms | Flip-flop<br>Type |

|---------------|-------------|------------------|-------------------|

| ======        | =======     | ===========      | =========         |

| 6             | INPUT       | -                | -                 |

| 7             | INPUT       | -                | –                 |

| 9             | INPUT       | -                | -                 |

| 10            | INPUT       | -                | -                 |

| 11            | INPUT       | -                | -                 |

| 12            | INPUT       | -                | -                 |

| 13            | INPUT       | -                | -                 |

| 16            | INPUT       | -                | -                 |

| 18            | BIDIR       | NORMAL 10        | D                 |

| 19            | BIDIR       | NORMAL 12        | D                 |

| 20            | BIDIR       | NORMAL 14        | D                 |

| 21            | BIDIR       | NORMAL 16        | D                 |

| 23            | BIDIR       | NORMAL 16        | D                 |

| 24            | BIDIR       | NORMAL 14        | D                 |

| 25            | BIDIR       | NORMAL 12        | D                 |

| 26            | BIDIR       | NORMAL 10        | D                 |

Synario 3.10 - Device Utilization Chart Fri Apr 09 17:42:39 1999 hpi2860.bls P22V10C Fuse Map: \_\_\_\_\_ 0 10 20 30 40 44: ----- ----88: ----X----- ----- -----132: -----X- -----176: -----X----- -----5368: ----- ---- ----- -----5412: --X--X---- ----- -----0 10 5808: XXXXXXXXX XXXXXXX-

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated