## TMS320C6000 Host Port to MC68360 Interface

Zoran Nikolic

Digital Signal Processing Solutions

#### **ABSTRACT**

This application report describes an interface between the Motorola MC68360 quad integrated communication controller (QUICC) and the host port interface (HPI) of a TMS320C6000™ (C6000™) digital signal processor (DSP) device. This includes a schematic showing connections between the two devices and verification that timing requirements are met for each device (tables and timing diagrams).

**NOTE:** This application report has not been verified in a board design.

**Contents**

| 1 MC6836     | 60 Processor Interface                                                                                     | 2  |

|--------------|------------------------------------------------------------------------------------------------------------|----|

| 1.1 Co       | nfiguration                                                                                                | 4  |

| 2 MC6836     | 60 to HPI Timing Verification                                                                              | 6  |

| 3 Referen    | ices                                                                                                       | 12 |

|              | TMS320C6x Timing Requirements                                                                              |    |

|              | MC68360 Timing Requirements                                                                                |    |

|              | List of Figures                                                                                            |    |

| Figure 1     | MC68360 to TMS320C62x/C67x/C64x (HPI16) HPI Interface Block Diagram                                        | 2  |

| Figure 2     | MC68360 to TMS320C64x (HPI32) HPI Interface Block Diagram                                                  |    |

| Figure 3     | MC68360 Reads Internal Memory of TMS320C62x/C67x/C64x (HPI16 Mode) Using HPI (Read Without Auto-Increment) |    |

| Figure 4     | MC68360 Write to TMS320C62x/C67x/C64x (HPI16 Mode) HPI                                                     |    |

| Figure 5     | MC68360 Reads Internal Memory of TMS320C64x (HPI32 Mode) Using HPI (Read Without Auto-Increment)           | 9  |

| Figure 6     | MC68360 Write to TMS320C64x (HPI32 Mode) HPI                                                               |    |

|              | List of Tables                                                                                             |    |

| Table 1. MC  | 68360 to HPI Pin Connections                                                                               | 3  |

|              | e Register 0 (BR0) Relevant Bits (MC68360)                                                                 |    |

| Table 3. Opt | ion Register (OR) Relevant Bits (MC68360)                                                                  | 6  |

| Table 4. Tim | ing Requirements for the C6201/C6701 HPI                                                                   | 11 |

|              |                                                                                                            |    |

Trademarks are the property of their respective owners.

TMS320C6000 and C6000 are trademarks of Texas Instruments.

| Table 5. Timing Requirements for MC68360 Interfaced to the C6201/C6701 HPI | . 11 |

|----------------------------------------------------------------------------|------|

| Table 6. Timing Requirements for the C6211/C6711 HPI                       | . 11 |

| Table 7. Timing Requirements for MC68360 Interfaced to the C6211/C6711 HPI | . 12 |

| Table 8. Timing Requirements for the C64x HPI                              | . 12 |

| Table 9. Timing Requirements for MC68360 Interfaced to the C64x HPI        | . 12 |

| Table A-1. TMS320C6201/C6701 Host Port Timing Specifications               | . 13 |

| Table A–2. TMS320C6211/C6711 Host Port Timing Specifications               | . 14 |

| Table A-3. TMS320C64x Host Port Timing Specifications                      | . 15 |

| Table B–1. Motorola MC68360 Timing Parameters NIL                          | . 16 |

### 1 MC68360 Processor Interface

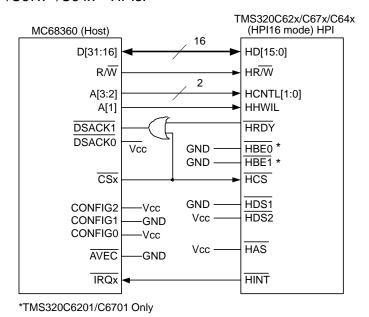

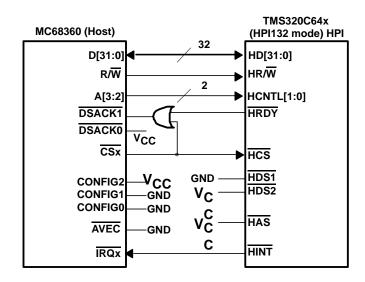

The MC68360 QUICC is 32-bit controller that is an extension of other members of the Motorola M68300 family. The MC68360 QUICC is a one-chip integrated microprocessor and peripheral combination that can be used in controller applications (particularly in communications activities). Figure 1 and Figure 2 show diagrams of the host (MC68360) interface to TMS320C62x<sup>™</sup>/C67x<sup>™</sup>/C64x<sup>™</sup> HPIs.

Figure 1. MC68360 to TMS320C62x/C67x/C64x (HPI16) HPI Interface Block Diagram

TMS320C62x, TMS320C67x, TMS320C64x, C62x, C67x and C64x are trademarks of Texas Instruments.

Figure 2. MC68360 to TMS320C64x (HPI32) HPI Interface Block Diagram

Table 1. MC68360 to HPI Pin Connections

| HPI Pin              | MC68360 Pin         | (                                                                                                                                                                                                                                                                                 | Comments                                                          |

|----------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| HCNTL[1:0]           | A[3:2]              | Address bits of MC68360 are used as control signals.                                                                                                                                                                                                                              |                                                                   |

| HHWIL                | A[1]                | A[1] identifies the first or second halfwo                                                                                                                                                                                                                                        | ord of transfer. Unused for HPI32 mode transfers.                 |

| HR/W                 | R/W                 | Indicates a read or write access                                                                                                                                                                                                                                                  |                                                                   |

| HD[15:0]<br>HD[31:0] | D[31:16]<br>D[31:0] | MC68360 uses D[31:16] for 16-bit por                                                                                                                                                                                                                                              | t interface and D[31:0] for 32-bit port interface.                |

| HDS1                 | GND                 | HDS1 and HDS2 are internally exclusi and high, respectively, to enable data                                                                                                                                                                                                       | ively-NORed. HDS1 and HDS2 are tied logic low strobe at all time. |

| HDS2                 | $V_{CC}$            | See above.                                                                                                                                                                                                                                                                        |                                                                   |

| HAS                  | $V_{CC}$            | Because host device MC68360 has separate address and data bus, HAS does not need to be used. HAS is tied inactive high.                                                                                                                                                           |                                                                   |

| HCS                  | CSx                 | Any one of the chip-selects of MC68360 can be connected to HCS as the chip-select signal. This also serves as the data-strobe signal in this case (because DS of MC68360 is not used as data strobe).                                                                             |                                                                   |

| HBE0                 | GND                 | MC68360 does not have byte write enable signals that have the same timing as other control signals. Therefore, HBE1 and HBE0 of HPI are tied low to enable host access to both lower and upper bytes of the half-word during a write. TMS320C6211 does not have HBE[1:0] signals. |                                                                   |

| HBE1                 | GND                 | See above.                                                                                                                                                                                                                                                                        |                                                                   |

| -                    | CONFIG[2:0]         | Because CONFIG[2:1] is set to 10, the CPU is enabled and the MBAR register is at 0x003FF00.                                                                                                                                                                                       |                                                                   |

|                      |                     | 16-bit interface<br>CONFIG[2:0]='101'                                                                                                                                                                                                                                             | 32-bit interface<br>CONFIG[2:0]='100'                             |

Table 1. MC68360 to HPI Pin Connections (Continued)

| HPI Pin | MC68360 Pin | Comments                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -       | AVEC='0'    | The Auto Vector input function is selected in normal operation.                                                                                                                                                                                                                                                                                                                                                               |

| HRDY    | DSACK1      | The SPS bits in the MC68360 option registers need to be set to indicate that $\overline{\text{DSACK1}}$ is generated externally by HPI. (See the $MC68360~User$ 's $Manual$ for details)                                                                                                                                                                                                                                      |

| HINT    | ĪRQx        | User can select interrupt level (IRQ1 to IRQ7). Priority level 7 interrupt is a special case. Level 7 interrupts are non-maskable interrupts (NMI). IRQ7 is a level-sensitive input and must remain low until the second instruction processing module (CPU32+) returns an interrupt acknowledge cycle for interrupt 7. (See the MC68360 Quad Integrated Communications Controller User's Manual for a detailed description.) |

DS (data strobe) of the MC68360 is not used in this interface because the MC68360 asserts DS only after it latches a DSACK low. However, the HPI of the C6000 does not assert HRDY (DSACK1) until after DS is asserted. Because of this timing conflict, HDS1 and HDS2 of the TMS320C6000 HPI are tied logic low and high, respectively, to enable data strobe at all times.

The HPI must keep  $\overline{DSACKx}$  asserted until it detects the negation of  $\overline{AS}$  or  $\overline{DS}$  (whichever it detects first). The C6000 must negate  $\overline{DSACKx}$  within approximately one clock period after sampling negation of  $\overline{AS}$  or  $\overline{DS}$ .  $\overline{DSACKx}$  signals that remain asserted beyond this limit may be prematurely detected for the next bus cycle. This is avoided by using an OR combination of the  $\overline{HRDY}$  and  $\overline{CSx}$  signals.

HBE1 and HBE2 of the HPI are tied low to enable host access to both lower and upper bytes of the halfword during a write in the TMS320C6201/6701. Although the MC68360 has byte write enable signals WE1 and WE0, they are not used in this interface because of timing issues. The HPI expects control signals, including HBE1 and HBE0, to be ready before data strobe (which is HCS in this case) is asserted. However, MC68360 asserts chip-select and write-enable signals at the same time. Therefore, WE1 and WE0 cannot be used.

The auto-vector (AVEC) signal is used to terminate interrupt acknowledge cycles, indicating that the QUICC should internally generate a vector (auto-vector) number to locate an interrupt handler routine. AVEC is ignored during all other bus cycles.

## 1.1 Configuration

The QUICC is comprised of three modules:

- CPU32+ core

- System integration module (SIM60)

- Communication processor module (CPM)

The memory controller is a sub-block of the SIM60 that is responsible for up to eight general-purpose chip-select lines. The general-purpose chip-selects are available on lines CS0-CS7. CS0 also functions as the global (boot) chip-select for accessing the boot EPROM. The SIM60 supports a glue-less interface to HPI.

All internal memory and registers of the MC68360 occupy a single 8K-byte memory block that can be relocated along 8K-byte boundaries. The location is fixed by writing the desired base address of the 8K-byte memory block to the MBAR. The 8K-byte block is divided into two 4K-byte sections. The RAM occupies the first section; the internal registers occupy the second section. The LSB (least significant bit) of the MBAR register indicates when the contents of the MBAR are valid (if the bit is equal to one the content is valid).

The MC68360's general-purpose chip-selects are controlled by the global memory register (GMR) and the memory controller status register (MSTAT). There is one GMR and MSTAT in the memory controller. The MSTAT reports write-protect violations and parity errors for all banks. The 32-bit read-write GMR contains selections that are common to the entire memory controller. The GMR is used to control global parameters for memory banks. The DPS bit field of the GMR register must be set to DPS[1:0] = 11 to enable external DSACKx response. The PBEE bit of the GMR register should be set to zero to disable parity bus error detection.

The 32-bit read-write GMR contains selections that are common to the entire memory controller. The GMR is used to control global parameters for memory banks.

The MSTAT reports write-protect violations and parity errors for all banks.

The configuration of the BR and OR registers is shown in Table 2 and Table 3.

Table 2. Base Register 0 (BR0) Relevant Bits (MC68360)

| Bit Field | Description                                                                                                                                                                                                            | Value                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| CSNTQ     | CS negate timing This bit is used to determine when CS is negated during an internal QUICC or external QUICC/MC68030-type bus-master write cycle.                                                                      | Set to 0 (CS negated normally).          |

| TRLXQ     | Timing relax This bit delays the beginning of the internal QUICC or external QUICC/MC68030-type bus-master cycle to relax the timing constraints on the user.                                                          | Set to 0 (do not relax timing).          |

| V         | Valid bit                                                                                                                                                                                                              | 1 = content of BR0 and OR0 pair is valid |

| PAREN     | Parity checking enable                                                                                                                                                                                                 | 0 = parity checking disabled             |

| BA31-BA11 | Base address The base address field, the upper 21 bits of each BR, and the function field are compared to the address on address bus to determine if a DRAM/SRAM region is being accessed by an internal QUICC master. |                                          |

The option register is 32-bit read-write register that may be accessed at any time.

Table 3. Option Register (OR) Relevant Bits (MC68360)

| Bit Field   | Description                                                                                                                                                                     | Value                                                                                                                          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| DSSEL       | Dynamic RAM select This bit determines if the bank is SRAM or DRAM.                                                                                                             | For HPI, set to 0.                                                                                                             |

| SPS1-SPS0   | SRAM port size Because external DSACKx is used, SPS[1:0] = 11                                                                                                                   | SPS0 = 1<br>SPS1 = 1                                                                                                           |

| AM27-AM11   | Address mask Mask any of the corresponding bits in the associated BR. By masking the address bits independently, external devices of different address range sizes can be used. | All base address and function code bits will be used in the bank hit comparison (all bits of the AM bit field are set to one). |

| TCYC3-TCYC0 | Cycle length in clocks                                                                                                                                                          | Because external DSACKx is selected with SPS, TCYC should not be set to zero.                                                  |

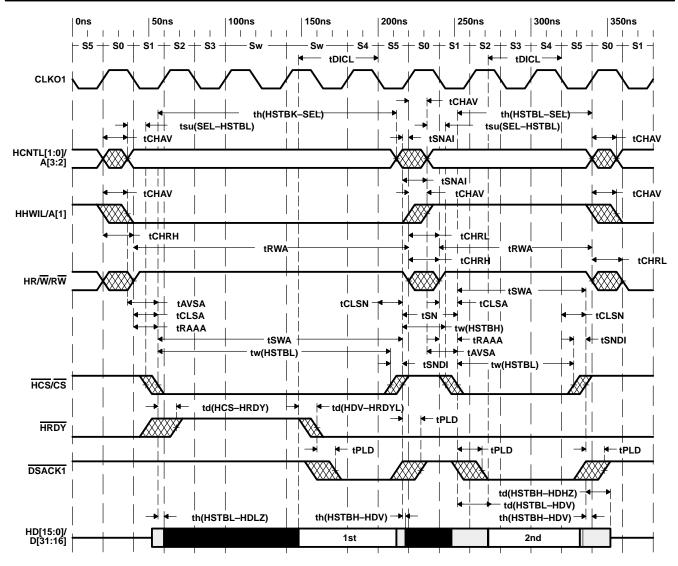

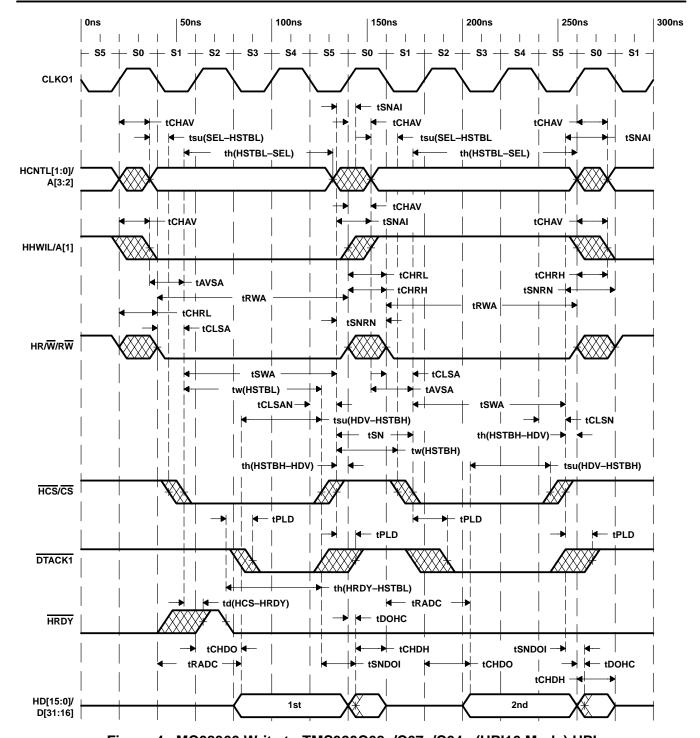

## 2 MC68360 to HPI Timing Verification

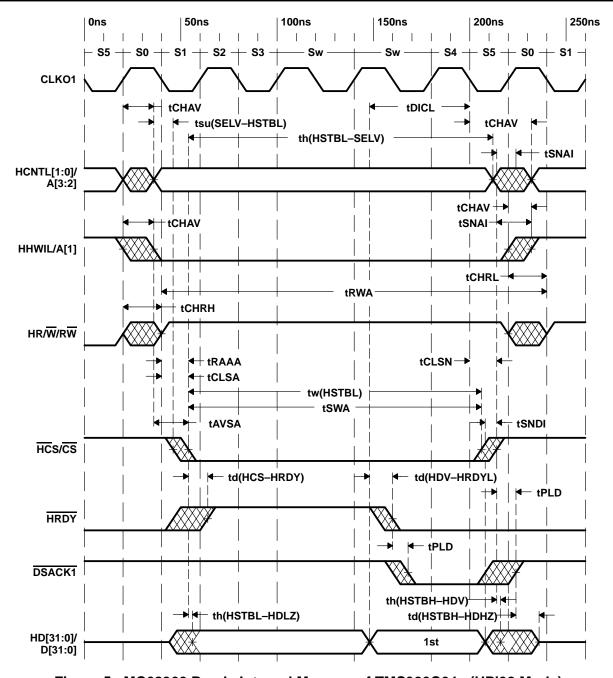

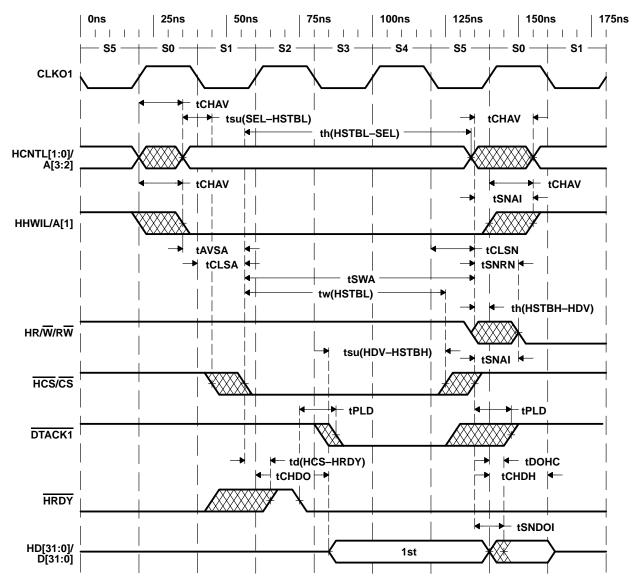

To verify proper operation, two functions have been examined: 1) an MC68360 write to HPI and 2) an MC68360 read from HPI. In each instance, timing requirements were compared for each of the devices. The results are shown in Figure 3 through Figure 6 and the timing requirements tables immediately following these figures. In all figures and tables, timing parameters are named in the same way as those in the data sheets for the TMS320C6000 and MC68360 devices. Actual timing parameter values are listed in Appendix A and Appendix B.

Figure 3 through Figure 6 and the timing requirement tables show that the timing parameters for both devices are met in all interfaces between the MC68360 and HPI. These interfaces are based on a MC68360/25-MHz device and TMS320C6x<sup>™</sup> devices operating at any frequency range.

Figure 3. MC68360 Reads Internal Memory of TMS320C62x/C67x/C64x (HPI16 Mode) Using HPI (Read Without Auto-Increment)

Figure 4. MC68360 Write to TMS320C62x/C67x/C64x (HPI16 Mode) HPI

Figure 5. MC68360 Reads Internal Memory of TMS320C64x (HPI32 Mode) Using HPI (Read Without Auto-Increment)

Figure 6. MC68360 Write to TMS320C64x (HPI32 Mode) HPI

Table 4. Timing Requirements for the C6201/C6701 HPI

| HPI Symbol                 | MC68360<br>Symbol                                             |                                                     | Min<br>HPI (ns)       | Min<br>MC68360 (ns) |

|----------------------------|---------------------------------------------------------------|-----------------------------------------------------|-----------------------|---------------------|

| t <sub>su(SEL-HSTBL)</sub> | t <sub>AVSA</sub>                                             | Setup time, select signals valid before HSTROBE low | 4                     | 10                  |

| <sup>t</sup> h(HSTBL-SEL)  | t <sub>SNAI</sub> + t <sub>SWA</sub>                          | Hold time, select signals valid after HSTROBE low   | 2                     | 85                  |

| t <sub>w(HSTBL)</sub>      | t <sub>SWA</sub>                                              | Pulse duration, HSTROBE low                         | 2*P <sub>H</sub> = 10 | 75                  |

| t <sub>w(HSTBH)</sub>      | t <sub>SN</sub>                                               | Pulse duration, HSTROBE high                        | 2*P <sub>H</sub> = 10 | 35                  |

| t <sub>su(HDV-HSTBH)</sub> | 1.5*P <sub>M</sub> – t <sub>CHDO</sub><br>+ t <sub>CLSN</sub> | Setup time, host data valid before HSTROBE high     | 3                     | 41                  |

| <sup>t</sup> h(HSTBH-HDV)  | t <sub>SNDOI</sub>                                            | Hold time, host data valid after HSTROBE high       | 2                     | 10                  |

| th(HRDYL-HSTBL)            | 0.5* P <sub>M</sub> + t <sub>CLSN</sub>                       | Hold time, HSTROBE low after HRDY low               | 1                     | 24                  |

NOTE: PH = Period of TMS3206201/6701DSP clock = 5 ns @ 200 MHz. PM = Period of MC68360 clock = 40 ns @ 25 MHz.

Table 5. Timing Requirements for MC68360 Interfaced to the C6201/C6701 HPI

| HPI<br>Symbol                                                        | MC68360<br>Symbol |                                              | Min HPI<br>(ns) | Min<br>MC68360 (ns) |

|----------------------------------------------------------------------|-------------------|----------------------------------------------|-----------------|---------------------|

| t <sub>oh(HSTBH-HDV)</sub>                                           | t <sub>SNDI</sub> | Hold time, input data from CS negated        | 2               | 0                   |

| 2* P <sub>M</sub> - t <sub>CLSA</sub><br>- t <sub>d(HSTBL-HDV)</sub> | tDICL             | Read set-up time, data-in valid to clock low | 52              | 1                   |

NOTE:  $P_M$  = Period of MC68360 clock = 40ns @ 25 MHz.

Table 6. Timing Requirements for the C6211/C6711 HPI

| HPI Symbol                  | MC68360<br>Symbol                                             |                                                     | Min<br>HPI (ns) | Min<br>MC68360 (ns) |

|-----------------------------|---------------------------------------------------------------|-----------------------------------------------------|-----------------|---------------------|

| t <sub>su(SELV-HSTBL)</sub> | t <sub>AVSA</sub>                                             | Setup time, Select signals valid before HSTROBE low | 5               | 10                  |

| t <sub>h(HSTBL-SELV)</sub>  | t <sub>SNAI</sub> + t <sub>SWA</sub>                          | Hold time, select signals valid after HSTROBE low   | 4               | 85                  |

| t <sub>w(HSTBL)</sub>       | t <sub>SWA</sub>                                              | Pulse Duration, HSTROBE low                         | $4*P_{H} = 24$  | 75                  |

| t <sub>w(HSTBH)</sub>       | t <sub>SN</sub>                                               | Pulse Duration, HSTROBE high                        | $4*P_{H} = 24$  | 35                  |

| t <sub>su(HDV-HSTBH)</sub>  | 1.5*P <sub>M</sub> – t <sub>CHDO</sub><br>+ t <sub>CLSN</sub> | Setup time, host data valid before HSTROBE high     | 5               | 41                  |

| t <sub>h(HSTBH-HDV)</sub>   | t <sub>SNDOI</sub>                                            | Hold time, host data valid after HSTROBE high       | 3               | 10                  |

| th(HRDYL-HSTBL)             | 0.5* P <sub>M</sub> + t <sub>CLSN</sub>                       | Hold time, HSTROBE low after HRDY low               | 2               | 24                  |

NOTE: PH = Period of TMS3206211/6711 DSP clock = 6 ns @ 167 MHz. PM = Period of MC68360 clock = 40 ns @ 25 MHz.

Table 7. Timing Requirements for MC68360 Interfaced to the C6211/C6711 HPI

| HPI<br>Symbol                                                         | MC68360 Symbol    |                                              | Min HPI<br>(ns) | Min<br>MC68360 (ns) |

|-----------------------------------------------------------------------|-------------------|----------------------------------------------|-----------------|---------------------|

| toh(HSTBH-HDV)                                                        | t <sub>SNDI</sub> | Hold time, input data from CS negated        | 2               | 0                   |

| 2* P <sub>M</sub> - t <sub>CLSA</sub><br>- t <sub>d</sub> (HSTBL-HDV) | t <sub>DICL</sub> | Read set-up time, data-in valid to clock low | 52              | 1                   |

NOTE: P<sub>M</sub> = Period of MC68360 clock = 40 ns @ 25 MHz.

Table 8. Timing Requirements for the C64x HPI

| HPI Symbol                 | MC68360 Symbol                                                |                                                     | Min<br>HPI (ns)       | Min<br>MC68360 (ns) |

|----------------------------|---------------------------------------------------------------|-----------------------------------------------------|-----------------------|---------------------|

| t <sub>su(SEL-HSTBL)</sub> | t <sub>AVSA</sub>                                             | Setup time, select signals valid before HSTROBE low | 4                     | 10                  |

| <sup>t</sup> h(HSTBL-SEL)  | t <sub>SNAI</sub> + t <sub>SWA</sub>                          | Hold time, select signals valid after HSTROBE low   | 2                     | 85                  |

| t <sub>w(HSTBL)</sub>      | t <sub>SWA</sub>                                              | Pulse duration, HSTROBE low                         | 4*P <sub>H</sub> = 10 | 75                  |

| t <sub>w(HSTBH)</sub>      | t <sub>SN</sub>                                               | Pulse duration, HSTROBE high                        | 4*P <sub>H</sub> = 10 | 35                  |

| t <sub>su(HDV-HSTBH)</sub> | 1.5*P <sub>M</sub> – t <sub>CHDO</sub><br>+ t <sub>CLSN</sub> | Setup time, host data valid before HSTROBE high     | 5                     | 41                  |

| <sup>t</sup> h(HSTBH-HDV)  | <sup>t</sup> SNDOI                                            | Hold time, host data valid after HSTROBE high       | 2                     | 10                  |

| th(HRDYL-HSTBL)            | 0.5* P <sub>M</sub> + t <sub>CLSN</sub>                       | Hold time, HSTROBE low after HRDY low               | 2                     | 24                  |

NOTE: PH = Period of TMS320C64x DSP clock = 2.5 ns @ 400 MHz.

P<sub>M</sub> = Period of MC68360 clock = 40 ns @ 25 MHz.

NOTE: The timing specifications above are preliminary and the actual numbers may vary with a TMS part. Please refer to the latest datasheet for numbers.

Table 9. Timing Requirements for MC68360 Interfaced to the C64x HPI

| HPI<br>Symbol                                                         | MC68360<br>Symbol |                                              | Min HPI<br>(ns) | Min<br>MC68360 (ns) |

|-----------------------------------------------------------------------|-------------------|----------------------------------------------|-----------------|---------------------|

| toh(HSTBH-HDV)                                                        | t <sub>SNDI</sub> | Hold time, input data from CS negated        | 2               | 0                   |

| 2* P <sub>M</sub> - t <sub>CLSA</sub><br>- t <sub>d</sub> (HSTBL-HDV) | <sup>t</sup> DICL | Read set-up time, data-in valid to clock low | 52              | 1                   |

NOTE: P<sub>M</sub> = Period of MC68360 clock = 40 ns @ 25 MHz.

NOTE: The timing specifications above are preliminary and the actual numbers may vary with a TMS part. Please refer to the latest datasheet for numbers.

### 3 References

- 1. TMS320C6200 Peripherals Reference Guide (SPRU190).

- 2. TMS320C6201 Digital Signal Processor (SPRS051).

- 3. TMS320C6701 Floating-Point Digital Signal Processor (SPRS067).

- 4. TMS320C6211, TMS320C6211B Fixed-Point Digital Signal Processors (SPRS073).

- 5. TMS320C6416 Fixed-Point Digital Signal Processor (SPRS164).

- 6. MC68360 Quad Integrated Communications Controller User's Manual, Motorola, Inc.

## Appendix A TMS320C6x Timing Requirements

#### Table A-1. TMS320C6201/C6701 Host Port Timing Specifications

| Symbol                      | Characteristic                                                                                                                                           | Min<br>(ns) | Max<br>(ns) |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| t <sub>su(SEL-HSTBL)</sub>  | Setup time, select signals§ valid before HSTROBE low †                                                                                                   | 4           |             |

| <sup>t</sup> h(HSTBL-SEL)   | Hold time, select signals§ valid after HSTROBE low †                                                                                                     | 2           |             |

| t <sub>w(HSTBL)</sub>       | Pulse duration, HSTROBE low †                                                                                                                            | 2P‡         |             |

| t <sub>w(HSTBH)</sub>       | Pulse duration, HSTROBE high between consecutive accesses †                                                                                              | 2P‡         |             |

| t <sub>su(HDV-HSTBH)</sub>  | Setup time, host data valid before HSTROBE high †                                                                                                        | 3           |             |

| <sup>t</sup> h(HSTBH-HDV)   | Hold time, host data valid after HSTROBE high †                                                                                                          | 2           |             |

| th(HRDYL-HSTBL)             | Hold time, HSTROBE† low after HRDY low. HSTROBE should not be inactivated until HRDY is active (low); otherwise, HPI writes will not complete properly.† | 1           |             |

| <sup>t</sup> d(HCS-HRDY)    | Delay time, HCS to HRDY ¶                                                                                                                                | 1           | 9           |

| <sup>t</sup> d(HSTBL-HRDYH) | Delay time, HSTROBE† low to HRDY high #                                                                                                                  | 3           | 12          |

| <sup>t</sup> oh(HSTBL-HDLZ) | Output hold time, HD low impedance after HSTROBE† low for an HPI read                                                                                    | 4           |             |

| <sup>t</sup> d(HDV-HRDYL)   | Delay time, HD valid to HRDY low                                                                                                                         | P‡-3        | P‡+3        |

| <sup>t</sup> oh(HSTBH-HDV)  | Output hold time, HD valid after HSTROBE† high                                                                                                           | 2           | 12          |

| <sup>t</sup> d(HSTBH-HDHZ)  | Delay time, HSTROBE† high to HD high impedance                                                                                                           | 3           | 12          |

| <sup>t</sup> d(HSTBL-HDV)   | Delay time, HSTROBE† low to HD valid                                                                                                                     | 3           | 12          |

| t <sub>d(HSTBH-HRDYH)</sub> | Delay time, HSTROBE <sup>†</sup> high to HRDY high ∥                                                                                                     | 3           | 12          |

<sup>†</sup>HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

$<sup>^{\</sup>ddagger}P = 1/CPU$  clock frequency in ns. For example, when running parts at 200 MHz, use P = 5 ns.

<sup>§</sup> Select signals include: HCNTRL[1:0], HR/W, and HHWIL.

<sup>¶</sup> HCS enables HRDY, and HRDY is always low when HCS is high. The case where HRDY goes high when HCS falls indicates that HPI is busy completing a previous HPID write or READ with autoincrement.

<sup>#</sup> This parameter is used during an HPID read. At the beginning of the first half-word transfer on the falling edge of HSTROBE, the HPI sends the request to the DMA auxiliary channel, and HRDY remains high until the DMA auxiliary channel loads the requested data into HPID.

This parameter is used after the second half-word of an HPID write or autoincrement read. HRDY remains low if the access is not an HPID write or autoincrement read. Reading or writing to HPIC or HPIA does not affect the HRDY signal.

Table A-2. TMS320C6211/C6711 Host Port Timing Specifications

| Symbol                       | Characteristic                                                                                                                                                                   | Min<br>(ns) | Max<br>(ns) |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| t <sub>su(SELV-HSTBL)</sub>  | Setup time, select signals§ valid before HSTROBE low †                                                                                                                           | 5           |             |

| <sup>t</sup> h(HSTBL-SELV)   | Hold time, select signals§ valid after HSTROBE low †                                                                                                                             | 4           |             |

| t <sub>w(HSTBL)</sub>        | Pulse duration, HSTROBE low †                                                                                                                                                    | 4P‡         |             |

| t <sub>w(HSTBH)</sub>        | Pulse duration, HSTROBE high between consecutive accesses †                                                                                                                      | 4P‡         |             |

| t <sub>su(HDV-HSTBH)</sub>   | Setup time, host data valid before HSTROBE high †                                                                                                                                | 5           |             |

| <sup>t</sup> h(HSTBH-HDV)    | Hold time, host data valid after HSTROBE high †                                                                                                                                  | 3           |             |

| <sup>t</sup> h(HRDYL-HSTBL)  | Hold time, HSTROBE <sup>†</sup> low after HRDY low. HSTROBE <sup>†</sup> should not be inactivated until HRDY is active (low); otherwise, HPI writes will not complete properly. | 2           |             |

| <sup>t</sup> d(HCS-HRDY)     | Delay time, HCS to HRDY ¶                                                                                                                                                        | 1           | 15          |

| <sup>t</sup> d(HSTBL-HRDYH)  | Delay time, HSTROBE† low to HRDY high #                                                                                                                                          | 3           | 15          |

| toh(HSTBL-HDLZ)              | Output hold time, HD low impedance after HSTROBE† low for an HPI read                                                                                                            | 2           |             |

| <sup>t</sup> d(HDV-HRDYL)    | Delay time, HD valid to HRDY low                                                                                                                                                 | 2P‡-4       | 2P‡         |

| toh(HSTBH-HDV)               | Output hold time, HD valid after HSTROBE high †                                                                                                                                  | 3           | 15          |

| <sup>t</sup> d(HSTBH-HDHZ)   | Delay time, HSTROBE high to HD high impedance †                                                                                                                                  | 3           | 15          |

| <sup>t</sup> d(HSTBL-HDV)    | Delay time, HSTROBE low to HD valid †                                                                                                                                            | 3           | 15          |

| t <sub>d</sub> (HSTBH-HRDYH) | Delay time, HSTROBE <sup>†</sup> high to HRDY high <sup>∥</sup>                                                                                                                  | 3           | 15          |

<sup>†</sup>HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

$<sup>\</sup>ddagger$  P = 1/CPU clock frequency in ns. For example, when running parts at 200 MHz, use P = 5 ns.

<sup>§</sup> Select signals include: HCNTRL[1:0], HR/W, and HHWIL.

<sup>¶</sup>HCS enables HRDY, and HRDY is always low when HCS is high. The case where HRDY goes high when HCS falls indicates that HPI is busy completing a previous HPID write or READ with autoincrement.

<sup>#</sup> This parameter is used during an HPID read. At the beginning of the first half-word transfer on the falling edge of HSTROBE, the HPI sends the request to the DMA auxiliary channel, and HRDY remains high until the DMA auxiliary channel loads the requested data into HPID.

This parameter is used after the second half-word of an HPID write or autoincrement read. HRDY remains low if the access is not an HPID write or autoincrement read. Reading or writing to HPIC or HPIA does not affect the HRDY signal.

Table A-3. TMS320C64x Host Port Timing Specifications

| Symbol                       | Characteristic                                                                                                                                                                   | Min<br>(ns) | Max<br>(ns) |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| t <sub>su(SELV-HSTBL)</sub>  | Setup time, select signals§ valid before HSTROBE† low                                                                                                                            | 5           |             |

| <sup>t</sup> h(HSTBL-SELV)   | Hold time, select signals§ valid after HSTROBE† low                                                                                                                              | 2           |             |

| t <sub>w(HSTBL)</sub>        | Pulse duration, HSTROBE† low                                                                                                                                                     | 4P‡         |             |

| t <sub>w(HSTBH)</sub>        | Pulse duration, HSTROBE† high between consecutive accesses                                                                                                                       | 4P‡         |             |

| t <sub>su(HDV-HSTBH)</sub>   | Setup time, host data valid before HSTROBE <sup>†</sup> high                                                                                                                     | 5           |             |

| <sup>t</sup> h(HSTBH-HDV)    | Hold time, host data valid after HSTROBE <sup>†</sup> high                                                                                                                       | 2           |             |

| <sup>t</sup> h(HRDYL-HSTBL)  | Hold time, HSTROBE <sup>†</sup> low after HRDY low. HSTROBE <sup>†</sup> should not be inactivated until HRDY is active (low); otherwise, HPI writes will not complete properly. | 2           |             |

| <sup>t</sup> d(HCS-HRDY)     | Delay time, HCS to HRDY¶                                                                                                                                                         | 1           | 7           |

| <sup>t</sup> d(HSTBL-HRDYH)  | Delay time, HSTROBE low to HRDY high #                                                                                                                                           | 3           | 12          |

| <sup>t</sup> oh(HSTBL-HDLZ)  | Output hold time, HD low impedance after HSTROBE† low for an HPI read                                                                                                            | 2           |             |

| <sup>t</sup> d(HDV-HRDYL)    | Delay time, HD valid to HRDY low                                                                                                                                                 | 2P‡-6       |             |

| toh(HSTBH-HDV)               | Output hold time, HD valid after HSTROBE <sup>†</sup> high                                                                                                                       | 3           |             |

| <sup>t</sup> d(HSTBH-HDHZ)   | Delay time, HSTROBE <sup>†</sup> high to HD high impedance                                                                                                                       |             | 12          |

| <sup>t</sup> d(HSTBL-HDV)    | Delay time, HSTROBE <sup>†</sup> low to HD valid                                                                                                                                 |             | 12          |

| t <sub>d</sub> (HSTBH-HRDYH) | Delay time, HSTROBE <sup>†</sup> high to HRDY high ∥                                                                                                                             | 3           | 12          |

<sup>†</sup>HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

The timing requirements in the tables above are provided for quick reference only. For detailed description, notes, and restrictions, please see the data sheets listed in the section.

$<sup>\</sup>ddagger$  P = 1/CPU clock frequency in ns. For example, when running parts at 200 MHz, use P = 5 ns.

<sup>§</sup> Select signals include: HCNTRL[1:0], HR/W, and HHWIL.

<sup>¶</sup> HCS enables HRDY, and HRDY is always low when HCS is high. The case where HRDY goes high when HCS falls indicates that HPI is busy completing a previous HPID write or READ with autoincrement.

<sup>#</sup>This parameter is used during an HPID read. At the beginning of the first half-word transfer on the falling edge of HSTROBE, the HPI sends the request to the DMA auxiliary channel, and HRDY remains high until the DMA auxiliary channel loads the requested data into HPID.

This parameter is used after the second half-word of an HPID write or autoincrement read. HRDY remains low if the access is not an HPID write or autoincrement read. Reading or writing to HPIC or HPIA does not affect the HRDY signal.

NOTE: The timing specifications above are preliminary and the actual numbers may vary with a TMS part. Please refer to the latest data sheet for numbers.

# **Appendix B MC68360 Timing Requirements**

Table B-1. Motorola MC68360 Timing Parameters

| Symbol             | Characteristic                                                     | Min<br>(ns) | Max<br>(ns) |

|--------------------|--------------------------------------------------------------------|-------------|-------------|

| t <sub>CHAV</sub>  | CLKO1 high to address, FC valid [6]                                | 0           | 15          |

| t <sub>CHAZn</sub> | CLKO1 high to address, FC Invalid [8]                              | 0           |             |

| t <sub>CLSA</sub>  | CLKO1 low to CS asserted [9]                                       | 4           | 16          |

| t <sub>STSA</sub>  | AS to DS or CS asserted [9A]                                       | -6          | 6           |

| tSTCA              | AS to CS asserted [9C]                                             | 14          | 26          |

| t <sub>AVSA</sub>  | Address valid to AS, CS, OE asserted [11]                          | 10          |             |

| t <sub>CLSN</sub>  | CLKO1 low to CS negated [12]                                       | 4           | 16          |

| t <sub>SNAI</sub>  | AS,DS, CS,OE,WE negated to address, FC invalid (address hold) [13] | 10          |             |

| t <sub>SWA</sub>   | AS, CS, OE and DS (read) width asserted [14]                       | 75          |             |

| t <sub>SN</sub>    | AS,DS, <del>CS</del> ,OE width negated [15]                        | 35          |             |

| t <sub>CHSZ</sub>  | CLKO1 high to AS,DS,R/W high impedance [16]                        |             | 40          |

| t <sub>SNRN</sub>  | AS,DS,CS,WE negated to R/W high [17]                               | 10          |             |

| t <sub>CHRH</sub>  | CLKO1 high to R/W high [18]                                        | 0           | 20          |

| t <sub>CHRL</sub>  | CLKO1 high to R/W low [20]                                         | 0           | 20          |

| t <sub>RAAA</sub>  | R/W high to AS, CS, OE asserted [21]                               | 10          |             |

| t <sub>RASA</sub>  | R/W low to DS asserted (write) [22]                                | 47          |             |

| t <sub>CHDO</sub>  | CLKO1 high to data-out valid [23]                                  |             | 23          |

| <sup>t</sup> SNDOI | DS, CS, WE negated to data-out invalid (data out hold) [25]        | 10          |             |

| $t_{DVSA}$         | Data out valid to DS asserted (write) [26]                         | 10          |             |

| t <sub>DICL</sub>  | Data In to CLKO1 low (data setup) [27]                             | 1           |             |

| t <sub>SNDN</sub>  | AS,DS, negated to DSACK negated [28]                               | 0           | 50          |

| t <sub>SNDI</sub>  | DS, CS, OE negated to data in invalid (data in hold) [29]          | 0           |             |

| t <sub>SHDI</sub>  | DS, CS, OE negated to data in high Z [29A]                         |             | 40          |

| $t_{DADV}$         | DSACK asserted to DSACK valid (skew) [31A]                         |             | 10          |

| t <sub>RWA</sub>   | $R/\overline{W}$ width asserted (write or read) [46]               | 100         |             |

| t <sub>AIST</sub>  | Async input setup time [47A]                                       | 5           |             |

| t <sub>AIHT</sub>  | Async input hold time [47B]                                        | 10          |             |

| <sup>t</sup> DOHC  | Data out from CLKO1 high [53]                                      | 0           |             |

### Table B-1. Motorola MC68360 Timing Parameters (Continued)

| Symbol            | Characteristic                                 | Min<br>(ns) | Max<br>(ns) |

|-------------------|------------------------------------------------|-------------|-------------|

| tCHDH             | CLKO1 high to data-out high Z [54]             |             | 20          |

| t <sub>RADC</sub> | R/W asserted to data bus impedance change [55] | 25          |             |

The timing requirements in are provided for quick reference only. For detailed description, notes, and restrictions, please see the *MC68360 Quad Integrated Communications Controller User's Manual.*

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265