# Stellaris® LM3S Sandstorm-, Fury-, and DustDevil-Class Microcontrollers Errata

# Silicon Errata

Literature Number: SPMZ860 June 2014

# **Contents**

| 1     | Introduction                                         | 3   |

|-------|------------------------------------------------------|-----|

| 2     | Device Date Code                                     | . 3 |

| 3     | Advisory to Silicon Revision Correlation             | 4   |

| 4     | Known Design Exceptions to Functional Specifications | . 7 |

| Revis | sion History                                         | 41  |

# Stellaris® LM3S Sandstorm-, Fury-, and DustDevil-Class Microcontrollers Errata

#### 1 Introduction

This document describes known exceptions to the functional specifications for the Stellaris Sandstorm-class Rev C2, the Stellaris Fury-class Rev A2 and the Stellaris DustDevil-class Rev A0 microcontrollers. See also the ARM® Cortex™-M3 errata, <u>SPMZ091</u> (for Sandstorm-class) or <u>SPMZ092</u> (for Fury- or DustDevil-class).

Note that each Stellaris microcontroller may not have all peripherals so not all errata may apply to your device.

For product details on the microcontrollers, see:

- Sandstorm-Class MCUs

- Fury-Class MCUs

- DustDevil-Class MCUs

#### 2 Device Date Code

To determine the date code of your part, look at the third line in the part markings, at the fourth and fifth characters following the dash (outlined in red below). The first number after the dash indicates the last decimal digit of the year. The next character indicates the month, in hexadecimal. So, in the below example, the 9B indicates a date code of November 2009.

# 3 Advisory to Silicon Revision Correlation

Table 1. Advisory to Silicon Revision Matrix

| Advisory                                                                                                             |                                                                                                             | Silicon Revision(s) Affected |                |                     |  |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------|----------------|---------------------|--|

| Advisory<br>Number                                                                                                   | Advisory Title                                                                                              | Sandstorm<br>Rev C2          | Fury<br>Rev A2 | DustDevil<br>Rev A0 |  |

|                                                                                                                      | ADC                                                                                                         |                              |                |                     |  |

| LM3ADC#01                                                                                                            | Use of "Always" triggering for ADC Sample Sequencer 3 does not work                                         | Χ                            | X              | Χ                   |  |

| LM3ADC#02                                                                                                            | Incorrect behavior with timer ADC triggering when another timer is used in 32-bit mode                      | X                            | Х              | Х                   |  |

| LM3ADC#03                                                                                                            | ADC hardware averaging produces erroneous results in differential mode                                      | Х                            | Х              | Х                   |  |

| LM3ADC#04                                                                                                            | Retriggering a sample sequencer before it has completed the current sequence results in continuous sampling | Х                            | Х              | Х                   |  |

| LM3ADC#05                                                                                                            | Using the PWM unit to trigger the ADC results in only one sample taken                                      |                              |                | Χ                   |  |

| LM3ADC#06                                                                                                            | TIMER3 cannot trigger ADC                                                                                   |                              |                | Χ                   |  |

| LM3ADC#07                                                                                                            | For devices with 4 or 6 ADC channels, inputs have the incorrect channel assignments                         |                              |                | Х                   |  |

| LM3ADC#18                                                                                                            | Data may not be present in the FIFO at the time of the sequence interrupt or trigger                        | Х                            | х              | Х                   |  |

| LM3ADC#19                                                                                                            | The first two ADC samples may be incorrect                                                                  | Х                            | Х              | Х                   |  |

|                                                                                                                      | Boot Loader                                                                                                 |                              | 1              |                     |  |

| LM3BOOT#01                                                                                                           | ROM-resident boot loader does not operate                                                                   |                              |                | Х                   |  |

|                                                                                                                      | CAN                                                                                                         |                              |                |                     |  |

| LM3CAN#01                                                                                                            | CAN register accesses require software delays                                                               |                              | Х              |                     |  |

|                                                                                                                      | DMA                                                                                                         |                              |                |                     |  |

| LM3DMA#01                                                                                                            | No interrupt generated with software-triggered DMA transfer using channel 30                                |                              |                | Х                   |  |

| LM3DMA#02                                                                                                            | The µDMA controller fails to generate capture mode DMA requests from Timer A in the Timer modules           |                              |                | Х                   |  |

|                                                                                                                      | Electrical Characteristics                                                                                  |                              |                |                     |  |

| LM3ELEC#01                                                                                                           | Certain pins do not fully comply with the JEDEC ESD standard                                                |                              |                | Χ                   |  |

|                                                                                                                      | GPIO                                                                                                        |                              |                |                     |  |

| LM3GPIO#01                                                                                                           | GPIO input pin latches in the Low state if pad type is open drain                                           | Χ                            | Х              |                     |  |

| LM3GPIO#02                                                                                                           | GPIO pins may glitch during power supply ramp up                                                            | Χ                            | Х              |                     |  |

| LM3GPIO#03                                                                                                           | GPIO commit register control not working as expected                                                        |                              |                | Х                   |  |

| LM3GPIO#04                                                                                                           | PB0 and PB1 have permanent internal pull-down resistance                                                    |                              |                | Х                   |  |

|                                                                                                                      | General-Purpose Timers                                                                                      |                              | 1              |                     |  |

| LM3GPTM#01                                                                                                           | General-purpose timer Edge Count mode count error when timer is disabled                                    | Х                            | Х              |                     |  |

| LM3GPTM#02                                                                                                           | General-purpose timer 16-bit Edge Count or Edge Time mode does not load reload value                        | Х                            | Х              | Х                   |  |

| LM3GPTM#03                                                                                                           | The General-Purpose Timer Match register does not function correctly in 32-bit mode                         | Х                            | Х              | Х                   |  |

| LM3GPTM#04                                                                                                           | A sourious DMA request is generated when the timer rolls over in Input.                                     |                              |                | Х                   |  |

| LM3GPTM#14 Writes to some General-Purpose Timer registers cause the counter to increment and decrement in some cases |                                                                                                             | Х                            | х              | Х                   |  |

|                                                                                                                      | Hibernation Module                                                                                          |                              |                |                     |  |

| LM3HIB#01                                                                                                            | Hibernation module does not operate correctly                                                               |                              | Х              |                     |  |

| LM3HIB#02                                                                                                            | Hihernation module may have higher current draw than specified in data                                      |                              |                |                     |  |

| LM3HIB#03                                                                                                            | Hibernation module HIB pin is not an open-drain output                                                      |                              |                | Х                   |  |

| LM3HIB#04                                                                                                            | Hibernation module registers are cleared by POR if not in Hibernate mode                                    |                              |                | Х                   |  |

**Table 1. Advisory to Silicon Revision Matrix (continued)**

| Advisory                                                                                                      |                                                                                                                                                         | Silicon Revision(s) Affected |                |                     |  |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|---------------------|--|

| Number                                                                                                        | Advisory Title                                                                                                                                          | Sandstorm<br>Rev C2          | Fury<br>Rev A2 | DustDevil<br>Rev A0 |  |

| LM3HIB#05 Hibernation Raw Interrupt Status (HIBRIS) register may not properly indicate Hibernation wake cause |                                                                                                                                                         |                              |                | Х                   |  |

| LM3HIB#06                                                                                                     | In Hibernate mode, the microcontroller may be parasitically powered by external USB signals                                                             |                              |                | Х                   |  |

| LM3HIB#07                                                                                                     | Writes to certain Hibernation module registers sometimes fail                                                                                           |                              |                | Χ                   |  |

| LM3HIB#08                                                                                                     | Writes to Hibernation module registers may change the value of the RTC                                                                                  |                              |                | Х                   |  |

|                                                                                                               | I2C                                                                                                                                                     |                              | •              |                     |  |

| LM3I2C#01                                                                                                     | I <sup>2</sup> C Slave Masked Interrupt Status (I2CSMIS) register bits are incorrect                                                                    |                              |                | Х                   |  |

|                                                                                                               | JTAG and Serial Wire Debug                                                                                                                              |                              |                |                     |  |

| LM3JTAG#01                                                                                                    | JTAG INTEST instruction does not work                                                                                                                   | Χ                            | Х              | Χ                   |  |

| LM3JTAG#02                                                                                                    | JTAG pins do not have internal pull-ups enabled at power-on reset                                                                                       |                              | Х              |                     |  |

| LM3JTAG#03                                                                                                    | Subsequent attempts to mass erase the Flash memory following a locked device recovery will fail                                                         |                              |                | Х                   |  |

| LM3JTAG#04                                                                                                    | Boundary scan is not functional                                                                                                                         |                              |                | Χ                   |  |

|                                                                                                               | Memory                                                                                                                                                  |                              |                |                     |  |

| LM3MEM#01                                                                                                     | MERASE bit of the FMC register does not erase the entire Flash array                                                                                    |                              | Х              |                     |  |

| LM3MEM#02                                                                                                     | FMPPE and FMPRE registers cannot be committed to non-volatile storage                                                                                   |                              |                | Х                   |  |

| LM3MEM#03                                                                                                     | ROM_SSIConfigSetExpClk function is incorrect                                                                                                            |                              |                | Х                   |  |

|                                                                                                               | PWM                                                                                                                                                     |                              |                |                     |  |

| LM3PWM#01                                                                                                     | PWM pulses cannot be smaller than dead-band time                                                                                                        | Χ                            | Х              |                     |  |

| LM3PWM#02                                                                                                     | PWM interrupt clear misses in some instances                                                                                                            | Χ                            | Х              |                     |  |

| LM3PWM#03                                                                                                     | PWM generation is incorrect with extreme duty cycles                                                                                                    | Х                            | Х              | Χ                   |  |

| LM3PWM#04                                                                                                     | PWMINTEN register bit does not function correctly                                                                                                       | Χ                            | Х              |                     |  |

| LM3PWM#05                                                                                                     | Sync of PWM does not trigger "zero" action                                                                                                              | Χ                            | Х              | Х                   |  |

| LM3PWM#06                                                                                                     | PWM "zero" action occurs when the PWM module is disabled                                                                                                | Χ                            | Х              | Х                   |  |

| LM3PWM#07                                                                                                     | PWM sync status is not properly cleared                                                                                                                 |                              |                | Х                   |  |

| LM3PWM#08                                                                                                     | PWM fault latch does not operate correctly                                                                                                              |                              |                | Х                   |  |

| LM3PWM#09                                                                                                     | Under certain circumstances, the PWM load interrupt is triggered as soon as the PWM is enabled                                                          | ×                            | х              | Х                   |  |

| LM3PWM#10                                                                                                     | Setting the PWMSYNC bits may not synchronize the PWM counters if PWMDIV is used                                                                         | Х                            | х              | Х                   |  |

|                                                                                                               | QEI                                                                                                                                                     |                              |                |                     |  |

| LM3QEI#01                                                                                                     | QEI index resets position when index is disabled                                                                                                        | Х                            | Х              | Х                   |  |

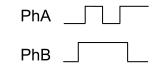

| LM3QEI#02                                                                                                     | QEI hardware position can be wrong under certain conditions                                                                                             | Х                            | Х              | Х                   |  |

| LM3QEI#03                                                                                                     | When using the index pulse to reset the counter, a specific initial conditions in the QEI module causes the direction for the first count to be misread | Х                            | х              | Х                   |  |

|                                                                                                               | SSI                                                                                                                                                     |                              |                |                     |  |

| LM3SSI#02                                                                                                     | SSI Receive FIFO Time-out interrupt may assert sooner than expected in slave                                                                            | Х                            | х              | Х                   |  |

|                                                                                                               | System Control                                                                                                                                          |                              | •              |                     |  |

| LM3SYSCTL#01                                                                                                  | MOSC verification circuit does not detect all failures of the main oscillator                                                                           | Χ                            |                |                     |  |

| LM3SYSCTL#02                                                                                                  | Excessive input pin current when level exceeds V <sub>DD</sub>                                                                                          | Х                            |                |                     |  |

| LM3SYSCTL#03                                                                                                  | LDO Current Limit interrupt does not function properly                                                                                                  | Χ                            |                |                     |  |

| LM3SYSCTL#04                                                                                                  | LDO Power Unregulated interrupt unpredictable after LDO voltage adjustments                                                                             | Х                            |                |                     |  |

| LM3SYSCTL#05                                                                                                  | PLL Lock Raw Interrupt Status triggers when PLL is powered down                                                                                         | Х                            |                |                     |  |

| LM3SYSCTL#06                                                                                                  | I/O buffer 5-V tolerance issue                                                                                                                          | Х                            | Х              | Х                   |  |

# Table 1. Advisory to Silicon Revision Matrix (continued)

| Advisory           |                                                                                                                    | Silicon Revision(s) Affected |                |                     |

|--------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|---------------------|

| Advisory<br>Number | Advisory Title                                                                                                     | Sandstorm<br>Rev C2          | Fury<br>Rev A2 | DustDevil<br>Rev A0 |

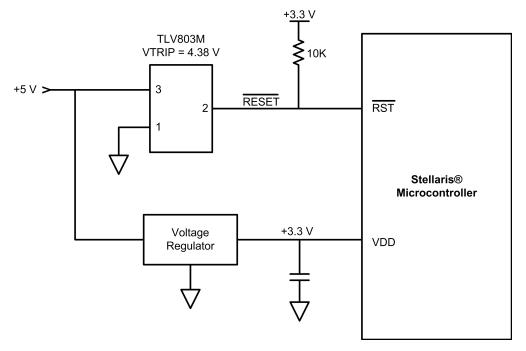

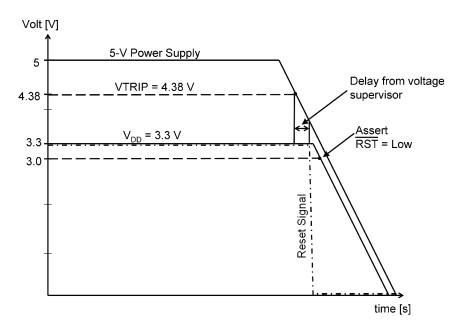

| LM3SYSCTL#07       | Standard R-C network cannot be used on RST to extend POR timing                                                    | Х                            | Х              |                     |

| LM3SYSCTL#08       | Clock source incorrect when waking up from Deep Sleep mode in some configurations                                  |                              | Х              |                     |

| LM3SYSCTL#09       | PLL may not function properly at default LDO setting                                                               |                              | Х              |                     |

| LM3SYSCTL#10       | PLL runs fast when using a 3.6864-MHz crystal                                                                      |                              | Х              |                     |

| LM3SYSCTL#11       | External reset does not reset the XTAL to PLL Translation (PLLCFG) register                                        |                              | Х              | Х                   |

| LM3SYSCTL#12       | Debugger cannot halt processor when in Sleep Mode                                                                  |                              |                | Х                   |

| LM3SYSCTL#13       | MOSC valid detect circuit should not be enabled                                                                    |                              |                | Х                   |

| LM3SYSCTL#24       | DSDIVORIDE value of 0x1 does not divide Deep Sleep clock by 2                                                      |                              | Х              | Х                   |

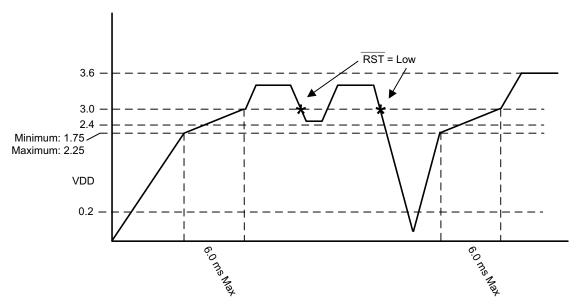

| LM3SYSCTL#25       | Special considerations for power transitions are required to ensure correct device operation                       | Х                            | Х              | Х                   |

|                    | UART                                                                                                               |                              |                |                     |

| LM3UART#01         | The RTRIS bit in the UARTRIS register is only set when the interrupt is enabled                                    | ×                            | Х              | Х                   |

| LM3UART#03         | When UART SIR mode is enabled, µDMA burst transfer does not occur                                                  |                              |                | Х                   |

|                    | USB                                                                                                                |                              |                |                     |

| LM3USB#01          | Device Capabilities 6 (DC6) register incorrectly specifies USB OTG functionality                                   |                              |                | Х                   |

| LM3USB#02          | Violating USB VBUS in-rush current specifications may cause USB controller to hang                                 |                              |                | Х                   |

| LM3USB#03          | PB0 and PB1 pins may not be used for GPIO or peripheral functions if USB Host or Device mode functionality is used |                              |                | Х                   |

| LM3USB#04          | Transfer may stall when size of µDMA transfer does not match USB FIFO                                              |                              |                | Х                   |

| LM3USB#05          | USB Host controller may not be used to communicate with a low-speed Device when connected through a hub            |                              |                | Х                   |

| LM3USB#06          | The USB PLL may fail to lock after reset                                                                           |                              |                | Х                   |

| LM3USB#07          | USB OTG signaling does not function correctly                                                                      |                              |                | Х                   |

| LM3USB#15          | USB controller sends EOP at end of device Remote Wake-Up                                                           |                              |                | Х                   |

| LM3USB#16          | Device sends SE0 in response to a USB bus reset                                                                    |                              |                | Х                   |

| LM3USB#17          | USB Resume occasionally does not wake device from Deep Sleep                                                       |                              |                | Х                   |

# 4 Known Design Exceptions to Functional Specifications Table 2. Advisory List

| Title                                                                                                                   | Page |

|-------------------------------------------------------------------------------------------------------------------------|------|

| LM3ADC#01 — Use of "Always" triggering for ADC Sample Sequencer 3 does not work                                         | . 9  |

| LM3ADC#02 — Incorrect behavior with timer ADC triggering when another timer is used in 32-bit mode                      | . 9  |

| LM3ADC#03 — ADC hardware averaging produces erroneous results in differential mode                                      | . 9  |

| LM3ADC#04 — Retriggering a sample sequencer before it has completed the current sequence results in continuous          |      |

| sampling                                                                                                                |      |

| LM3ADC#05 — Using the PWM unit to trigger the ADC results in only one sample taken                                      |      |

| LM3ADC#06 — TIMER3 cannot trigger ADC                                                                                   |      |

| LM3ADC#07 — For devices with 4 or 6 ADC channels, inputs have the incorrect channel assignments                         |      |

| LM3ADC#18 — Data may not be present in the FIFO at the time of the sequence interrupt or trigger                        |      |

| LM3ADC#19 — The first two ADC samples may be incorrect                                                                  |      |

| LM3BOOT#01 — ROM-resident boot loader does not operate                                                                  |      |

| LM3CAN#01 — CAN register accesses require software delays                                                               |      |

| LM3DMA#01 — No interrupt generated with software-triggered DMA transfer using channel 30                                | 13   |

| <b>LM3DMA#02</b> — The μDMA controller fails to generate capture mode DMA requests from Timer A in the Timer modules    | 13   |

| LM3ELEC#01 — Certain pins do not fully comply with the JEDEC ESD standard                                               | 14   |

| LM3GPIO#01 — GPIO input pin latches in the Low state if pad type is open drain                                          | 14   |

| LM3GPIO#02 — GPIO pins may glitch during power supply ramp up                                                           | 15   |

| LM3GPIO#03 — GPIO commit register control not working as expected                                                       | 15   |

| LM3GPIO#04 — PB0 and PB1 have permanent internal pull-down resistance                                                   | 16   |

| <b>LM3GPTM#01</b> — General-purpose timer Edge Count mode count error when timer is disabled                            | 17   |

| LM3GPTM#02 — General-purpose timer 16-bit Edge Count or Edge Time mode does not load reload value                       | 18   |

| <b>LM3GPTM#03</b> — The General-Purpose Timer Match register does not function correctly in 32-bit mode                 | 18   |

| <b>LM3GPTM#04</b> — A spurious DMA request is generated when the timer rolls over in Input-Edge Time mode               | 18   |

| LM3GPTM#14 — Writes to some General-Purpose Timer registers cause the counter to increment and decrement in some cases  | 18   |

| LM3HIB#01 — Hibernation module does not operate correctly                                                               |      |

| LM3HIB#02 — Hibernation module may have higher current draw than specified in data sheet under certain                  |      |

| conditions                                                                                                              |      |

| LM3HIB#03 — Hibernation module HIB pin is not an open-drain output                                                      |      |

| LM3HIB#04 — Hibernation module registers are cleared by POR if not in Hibernate mode                                    |      |

| <b>LM3HIB#05</b> — Hibernation Raw Interrupt Status (HIBRIS) register may not properly indicate Hibernation wake cause. |      |

| <b>LM3HIB#06</b> — In Hibernate mode, the microcontroller may be parasitically powered by external USB signals          | 20   |

| LM3HIB#07 — Writes to certain Hibernation module registers sometimes fail                                               |      |

| LM3HIB#08 — Writes to Hibernation module registers may change the value of the RTC                                      |      |

| LM3I2C#01 — I <sup>2</sup> C Slave Masked Interrupt Status (I2CSMIS) register bits are incorrect                        |      |

| LM3JTAG#01 — JTAG INTEST instruction does not work                                                                      |      |

| LM3JTAG#02 — JTAG pins do not have internal pull-ups enabled at power-on reset                                          |      |

| LM3JTAG#03 — Subsequent attempts to mass erase the Flash memory following a locked device recovery will fail            |      |

| LM3JTAG#04 — Boundary scan is not functional                                                                            |      |

| LM3MEM#01 — MERASE bit of the FMC register does not erase the entire Flash array                                        |      |

| LM3MEM#02 — FMPPE and FMPRE registers cannot be committed to non-volatile storage                                       |      |

| LM3MEM#03 — ROM_SSIConfigSetExpClk function is incorrect                                                                |      |

| LM3PWM#01 — PWM pulses cannot be smaller than dead-band time                                                            |      |

| LM3PWM#02 — PWM interrupt clear misses in some instances                                                                |      |

| LM3PWM#03 — PWM generation is incorrect with extreme duty cycles                                                        |      |

| LM3PWM#04 — PWMINTEN register bit does not function correctly                                                           |      |

| LM3PWM#05 — Sync of PWM does not trigger "zero" action                                                                  | 25   |

# **Table 2. Advisory List (continued)**

| LM3PWM#06 — PWM "zero" action occurs when the PWM module is disabled                                                                                                        | 26 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| LM3PWM#07 — PWM sync status is not properly cleared                                                                                                                         |    |

| LM3PWM#08 — PWM fault latch does not operate correctly                                                                                                                      | 26 |

| $\textbf{LM3PWM\#09} \hspace{0.1cm} \textbf{-} \textbf{Under certain circumstances, the PWM load interrupt is triggered as soon as the PWM is enabled \hspace{0.1cm} \dots$ | 27 |

| <b>LM3PWM#10</b> —Setting the PWMSYNC bits may not synchronize the PWM counters if PWMDIV is used                                                                           | 27 |

| LM3QEI#01 — QEI index resets position when index is disabled                                                                                                                |    |

| <b>LM3QEI#02</b> — QEI hardware position can be wrong under certain conditions                                                                                              | 27 |

| <b>LM3QEI#03</b> — When using the index pulse to reset the counter, a specific initial conditions in the QEI module causes the direction for the first count to be misread  | 28 |

| LM3SSI#02 —SSI Receive FIFO Time-out interrupt may assert sooner than expected in slave                                                                                     | 28 |

| <b>LM3SYSCTL#01</b> — MOSC verification circuit does not detect all failures of the main oscillator                                                                         | 28 |

| LM3SYSCTL#02 — Excessive input pin current when level exceeds V <sub>DD</sub>                                                                                               | 29 |

| LM3SYSCTL#03 — LDO Current Limit interrupt does not function properly                                                                                                       | 29 |

| <b>LM3SYSCTL#04</b> — LDO Power Unregulated interrupt unpredictable after LDO voltage adjustments                                                                           | 29 |

| LM3SYSCTL#05 — PLL Lock Raw Interrupt Status triggers when PLL is powered down                                                                                              | 30 |

| LM3SYSCTL#06 — I/O buffer 5-V tolerance issue                                                                                                                               | 30 |

| LM3SYSCTL#07 — Standard R-C network cannot be used on RST to extend POR timing                                                                                              | 30 |

| $\textbf{LM3SYSCTL\#08} \ - \ \text{Clock source incorrect when waking up from Deep Sleep mode in some configurations}$                                                     | 30 |

| LM3SYSCTL#09 — PLL may not function properly at default LDO setting                                                                                                         | 31 |

| LM3SYSCTL#10 — PLL runs fast when using a 3.6864-MHz crystal                                                                                                                | 31 |

| <b>LM3SYSCTL#11</b> — External reset does not reset the XTAL to PLL Translation (PLLCFG) register                                                                           | 31 |

| LM3SYSCTL#12 — Debugger cannot halt processor when in Sleep Mode                                                                                                            |    |

| LM3SYSCTL#13 — MOSC valid detect circuit should not be enabled                                                                                                              | 32 |

| LM3SYSCTL#24 —DSDIVORIDE value of 0x1 does not divide Deep Sleep clock by 2                                                                                                 | 32 |

| $\textbf{LM3SYSCTL\#25} \ - \ \text{Special considerations for power transitions are required to ensure correct device operation}$                                          | 32 |

| <b>LM3UART#01</b> — The RTRIS bit in the UARTRIS register is only set when the interrupt is enabled                                                                         | 37 |

| <b>LM3UART#03</b> — When UART SIR mode is enabled, μDMA burst transfer does not occur                                                                                       | 37 |

| <b>LM3USB#01</b> — Device Capabilities 6 (DC6) register incorrectly specifies USB OTG functionality                                                                         | 37 |

| $\textbf{LM3USB\#02} \ - \ \text{Violating USB VBUS in-rush current specifications may cause USB controller to hang} \$                                                     | 37 |

| LM3USB#03 — PB0 and PB1 pins may not be used for GPIO or peripheral functions if USB Host or Device mode                                                                    |    |

| functionality is used                                                                                                                                                       |    |

| LM3USB#04 — Transfer may stall when size of µDMA transfer does not match USB FIFO                                                                                           | 38 |

| <b>LM3USB#05</b> — USB Host controller may not be used to communicate with a low-speed Device when connected through a hub.                                                 | 39 |

| LM3USB#06 — The USB PLL may fail to lock after reset                                                                                                                        |    |

| LM3USB#07 — USB OTG signaling does not function correctly                                                                                                                   |    |

| LM3USB#15 — USB controller sends EOP at end of device Remote Wake-Up                                                                                                        |    |

| LM3USB#16 — Device sends SE0 in response to a USB bus reset                                                                                                                 |    |

| LM3USB#17 — USB Resume occasionally does not wake device from Deep Sleep                                                                                                    | 40 |

LM3ADC#01 Use of "Always" triggering for ADC Sample Sequencer 3 does not work

Device(s) Affected: Stellaris Sandstorm-class Rev C2, Fury-class Rev A2, and DustDevil-class Rev A0

**Description:** When using ADC Sample Sequencer 3 (SS3) and configuring the trigger source to

"Always" to enable continuous sampling by programming the SS3 Trigger Select field (EM3) in the **ADC Event Multiplexer Select (ADCEMUX)** register to 0xF, the first sample will be captured, but no further samples will be updated to the sequencer FIFO. Interrupts are continuously generated after the first sample and the FIFO status remains

empty.

**Workaround(s):** Software must disable and re-enable the sample sequencer to capture another sample.

LM3ADC#02 Incorrect behavior with timer ADC triggering when another timer is used in 32-bit

mode

Device(s) Affected: Stellaris Sandstorm-class Rev C2, Fury-class Rev A2, and DustDevil-class Rev A0

**Description:** When a timer is configured to trigger the ADC and another timer is configured to be a

32-bit periodic or one-shot timer, the ADC is triggered continuously instead of the

specified interval.

Workaround(s): Do not use a 32-bit periodic or one-shot timer when triggering ADC. If the timer is in 16-

bit mode, the ADC trigger works as expected.

LM3ADC#03 ADC hardware averaging produces erroneous results in differential mode

Device(s) Affected: Stellaris Sandstorm-class Rev C2, Fury-class Rev A2, and DustDevil-class Rev A0

**Description:** The implementation of the ADC averaging circuit does not work correctly when the ADC

is sampling in differential mode and the difference between the voltages is approximately

0.0 V.

Workaround(s): Do not use hardware averaging in differential mode. Instead, use the FIFO to store

results and average them in software.

LM3ADC#04 Retriggering a sample sequencer before it has completed the current sequence

results in continuous sampling

Device(s) Affected: Stellaris Sandstorm-class Rev C2, Fury-class Rev A2, and DustDevil-class Rev A0

**Description:** Re-triggering a sample sequencer before it has completed its programmed conversion

sequence causes the sample sequencer to continuously sample. If interrupts have been enabled, interrupts are generated at the appropriate place in the sample sequence. This

problem only occurs when the new trigger is the same type as the current trigger.

Workaround(s): Ensure that a sample sequence has completed before triggering a new sequence using

the same type of trigger.

LM3ADC#05 Using the PWM unit to trigger the ADC results in only one sample taken

Device(s) Affected: Stellaris DustDevil-class Rev A0

**Description:** If the ADC is configured to trigger from a PWM generator source, the ADC unit is

triggered on the first matched event in the **PWMn Interrupt and Trigger Enable** (**PWMnINTEN**) register; however, it will receive no further triggers at the subsequent

event matches.

Workaround(s): If the raw interrupt status is cleared before the next event match, the ADC correctly receives the next event signal. Therefore, the trigger condition must be cleared using the same interrupt condition in the **PWMn Interrupt Status and Clear (PWMnISC)** register.

| Trigger Condition | Interrupt Status and Clear |

|-------------------|----------------------------|

| TrCntZero         | IntCntZero                 |

| TrCntLoad         | IntCntLoad                 |

| TrCmpAU           | IntCmpAU                   |

| TrCmpAD           | IntCmpAD                   |

| TrCmpBU           | IntCmpBU                   |

| TrCmpBD           | IntCmpBD                   |

For example, consider the scenario where the ADC performs sequence 0 and generates a processor interrupt when triggered by PWM generator 2 CmpAD (compararator A value count down match). The DriverLib call to enable the PWM to trigger the ADC is:

```

PWMGenIntTrigEnable(PWM_BASE, PWM_GEN_2, PWM_TR_CNT_AD);

```

In the ADC sequence 0 interrupt handler, both the ADC interrupt status bit and the PWM generator 2 status bits must be cleared, as follows:

```

void

ADC0IntHandler(void)

{

//

// Clear the PWM trigger source

// This step is for an errata workaround

//

PWMGenIntClear(PWM_BASE, PWM_GEN_2, PWM_INT_CNT_AD);

//

// Clear the ADC interrupt status

//

ADCIntClear(ADC_BASE, 0);

...remaining ADC interrupt handler code...

```

## LM3ADC#06 TIMER3 cannot trigger ADC

Device(s) Affected: Stellaris DustDevil-class Rev A0

Description: The ADC Event Multiplexer Select (ADCEMUX) register can be used to select the

event (trigger) that initiates sampling for each sample sequencer. However, Timer 3

cannot be used to trigger analog-to-digital conversions.

**Workaround(s):** Use one of the other timers to trigger ADC.

LM3ADC#07 For devices with 4 or 6 ADC channels, inputs have the incorrect channel

assignments

Device(s) Affected: Stellaris DustDevil-class Rev A0

Description: For devices with 4 channels

Instead of channels 0, 1, 2, and 3 available on pins PE3, PE2, PE1, and PE0,

respectively, the available channels are 4, 5, 6 and 7 on pins PD3, PD2, PD1 and PD0,

respectively.

For devices with 6 channels

Instead of channels 0, 1, 2, 3, 4 and 5 available on pins PE3, PE2, PE1, PE0, PD3 and PD2, respectively, the available channels are 0, 1, 4, 5, 6, 7 on pins PE3, PE2, PD3,

PD2, PD1 and PD0, respectively.

Workaround(s): Software must utilize the alternate channels when programming the ADC (for example,

use ADC4 instead of ADC0). When configuring the GPIOAMSEL register, software must

enable analog inputs for the alternate pins (for example, PD3 instead of PE3).

**Fixed:** Fixed devices have 8 channels available so that board changes are not required and

have date codes of:

0x07 or later for LM3S1625, LM3S1626, LM3S1627, LM3S1776, LM3S2276, LM3S2616,

LM3S2671, LM3S2776, LM3S5632, LM3S5732

0x19 or later for LM3S3651, LM3S5652, LM3S5752, LM3S5662, LM3S5762

See Section 2, Device Date Code, for more information on date codes.

LM3ADC#18 Data may not be present in the FIFO at the time of the sequence interrupt or

trigger

Device(s) Affected: Stellaris Sandstorm-class Rev C2, Fury-class Rev A2 and DustDevil-class Rev A0

**Description:** The interrupt or trigger for a sample sequence may occur before data is placed in the

ADC sample sequence FIFO.

Workaround(s): Insert a delay after receiving the interrupt or trigger and before reading the data in the

FIFO. The minimum length of the delay is given by the following equation, where H is the number of samples to be averaged if hardware averaging is enabled (H=1 if hardware

averaging is not used), and S is the sample rate:

Delay = H/S

For example, if sampling at a rate of 1 MSPS and 4 samples are to be hardware averaged, delay at least 4 µs before reading the data in the FIFO. The StellarisWare API

SysCtlDelay() can be used to add a delay based on your system clock frequency.

LM3ADC#19 The first two ADC samples may be incorrect

Device(s) Affected: Stellaris Sandstorm-class Rev C2, Fury-class Rev A2 and DustDevil-class Rev A0

**Description** The first two ADC samples taken after the ADC clock is enabled in the **xCGC0** register

may be incorrect.

Workaround(s) Reset the ADC peripheral using the SRCR0 register after the ADC peripheral clock is

enabled and before initializing the ADC and enabling the sample sequencer.

LM3BOOT#01 ROM-resident boot loader does not operate

Stellaris DustDevil-class Rev A0 Device(s) Affected:

Description: The ROM-resident boot loader cannot be used to program the on-chip Flash. The boot

loader enters the hard-fault state as a result of trying to access a peripheral that does

not exist.

Use the Stellaris Flash-resident boot loader to update the on-chip Flash. Workaround(s):

LM3CAN#01 CAN register accesses require software delays

Stellaris Fury-class Rev A2 Device(s) Affected:

Description:

Because of a synchronization issue between the processor clock and the 8-MHz CAN clock, both read and write accesses to CAN registers require a software delay in order to ensure proper operation. If this delay is not observed between reads or writes, then register data corruption will occur, causing problems that are difficult to debug. Due to the nature of the synchronization issue, write accesses and read accesses have slightly different issues.

When performing CAN register write accesses, a delay is required between successive writes to any CAN register. The amount of delay required is related to the ratio of the processor clock to the CAN clock. For example, if the processor clock is 4 times greater than the CAN clock, then there must be a 4-processor-cycle gap between successive writes to the CAN controller. However, in the case that the processor clock is less than or equal to the CAN clock, then there are no write access limitations.

When performing CAN register read accesses, a delay is required between the reads of the CAN registers. The difference with read accesses is that all read accesses to CAN registers must perform a double read to receive the correct data. The first read initiates the read request to the CAN controller and the second read access retrieves the data. This sequence cannot be interrupted by another read to the same CAN controller or the data read by the second read access will have invalid data. This means that code that reads the CAN registers must protect this read/delay/read sequence from other asynchronous code, such as interrupt handlers, that access the same CAN controller. Like the case for writing CAN registers, the delay between successive reads to CAN registers is related to the ratio of the processor to the CAN clock. For example, if the processor clock is 4 times greater than the CAN clock, then there must be a 4-cycle gap between reads. However, unlike the write case, when the processor clock is less than or equal to the CAN clock, there still must be a 2-processor cycle delay between read accesses in order to retrieve the correct data.

Debugger accesses to the CAN registers will also show these issues, usually when debuggers perform read accesses to display the register data in a memory window, or in some cases, a register display window. The data displayed in the memory window will not show the correct data for the CAN registers. In most cases, the read accesses are slow and in sequence so they will show the CAN registers in the memory window offset by one word. However, this cannot be guaranteed as the debugger could possibly read the registers too guickly or not in address order and display invalid data.

#### Workaround(s):

In order to safely read or write the CAN registers, delays must be inserted for the correct number of cycles. Writes can delay before or after the CAN register write depending on the system needs, while reads must always perform a double-read to get data back from the CAN register. The Stellaris Peripheral Driver Library (DriverLib) provides the following two functions to perform the delays necessary for reading or writing the CAN registers: CANReadReg and CANWriteReg. The default behavior is tuned for a 50-MHz processor clock via the define (CAN\_RW\_DELAY) in the can.c file of DriverLib. If the processor clock is lower, this value can be changed and DriverLib can be rebuilt for more optimal performance. Care should be taken when adjusting this value as different compilers may generate the looping code differently. When this erratum is fixed, future releases of DriverLib will replace these functions with direct hardware accesses to the registers.

As an example, the amount of delay necessary if the processor clock is 25 MHz and the CAN clock is 8 MHz is 3.125 processor clocks or at least 4 processor clocks. When reading CAN registers, no other CAN accesses can occur. This requires protecting the non-interrupt code from interrupt handlers corrupting the read operations. This precaution is not required for writes, as the default interrupt latency is higher than the delay necessary at 50 MHz.

To write a CAN register, use the following simple sequence:

- 1. Write the CAN register.

- 2. Delay for (processor clock/CAN clock) processor cycles.

To read a CAN register, use the following simple sequence:

- 1. Acquire CAN mutex (mutual exclusion).

- 2. Read the CAN register and discard the data.

- 3. Delay for (processor clock/CAN clock) processor cycles.

- 4. Read the CAN register again to get the correct data.

- 5. Release CAN mutex

The mutex used to protect CAN access can be done more than one way. One method is to simply disable interrupts for the CAN controller that is being accessed during read accesses. Whatever method is used, it must be sure to protect against any asynchronous code that accesses the same CAN controller as the code that it interrupts.

#### LM3DMA#01

#### No interrupt generated with software-triggered DMA transfer using channel 30

Device(s) Affected:

Stellaris DustDevil-class Rev A0

**Description:**

When performing a software-triggered data transfer using µDMA channel 30, no interrupt is triggered when the transfer completes.

Workaround(s):

Use any of the other channels (except for channels 30 and 31) that are not already assigned to a peripheral. See the "DMA Channel Assignments" table in the Micro Direct Memory Access (µDMA) chapter in the data sheet.

This issue is fixed on parts with a date code of 06 (June 2010) or later. See Section 2, Device Date Code, for more information.

# LM3DMA#02

The  $\mu DMA$  controller fails to generate capture mode DMA requests from Timer A in the Timer modules

Device(s) Affected:

Stellaris DustDevil-class Rev A0

**Description:**

The µDMA controller fails to generate DMA requests from Timer A in the General-Purpose Timer modules when in the Event Count and Event Time modes.

Workaround(s):

Use Timer B.

#### LM3ELEC#01

# Certain pins do not fully comply with the JEDEC ESD standard

Device(s) Affected:

Stellaris DustDevil-class Rev A0

**Description:**

The pins listed below do not fully meet the industry ESD standard of 2.0 KV Human Body Model (HBM) under all conditions. All Stellaris devices are tested using JEDEC Standard JESD22-A114. These pins fail only in the pin-to-power condition using a positive voltage transient. The pins pass at 500 V. All other HBM conditions pass on these pins. All other device pins fully comply with this HBM JEDEC standard.

- PB0/USB0ID

- PB1/USB0VBUS

- USB0DM

- USB0DP

- USB0RBIAS

- PF0

- OSC0

- OSC1

Workaround(s):

Extra caution should be taken to ensure proper ESD handling of these devices. Use appropriate caution when implementing ESD protection circuits on signals routed to these pins.

# LM3GPIO#01

## GPIO input pin latches in the Low state if pad type is open drain

Device(s) Affected:

Stellaris Sandstorm-class Rev C2 and Fury-class Rev A2

Description:

GPIO pins function normally if configured as inputs and the open-drain configuration is disabled. If open drain is enabled while the pin is configured as an input using the GPIO Alternate Function Select (GPIOAFSEL), GPIO Open Drain Select (GPIOODR), and GPIO Direction (GPIODIR) registers, then the pin latches Low and excessive current (into pin) results if an attempt is made to drive the pin High. The open-drain device is not controllable.

A GPIO pin is not normally configured as open drain and as an input at the same time. A user may want to do this when driving a signal out of a GPIO open-drain pad while configuring the pad as an input to read data on the same pin being driven by an external device. Bit-banging a bidirectional, open-drain bus (for example, I<sup>2</sup>C) is an example.

Workaround(s):

If a user wants to read the state of a GPIO pin on a bidirectional bus that is configured as an open-drain output, the user must first disable the open-drain configuration and then change the direction of the pin to an input. This precaution ensures that the pin is never configured as an input and open drain at the same time.

A second workaround is to use two GPIO pins connected to the same bus signal. The first GPIO pin is configured as an open-drain output, and the second is configured as a standard input. This way the open-drain output can control the state of the signal and the input pin allows the user to read the state of the signal without causing the latch-up condition.

# LM3GPIO#02 GPIO pins may glitch during power supply ramp up

Device(s) Affected: Stellaris Sandstorm-class Rev C2 and Fury-class Rev A2

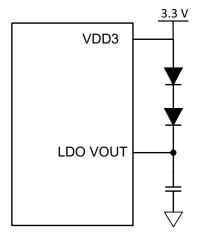

**Description:** Upon completing a POR (power-on reset) sequence, the GPIO pins default to a tri-stated

input condition. However, during the initial ramp up of the external  $V_{DD}$  supply from 0.0 V to 3.3 V, the GPIO pins are momentarily configured as output drivers during the time the internal LDO circuit is also ramping up. As a result, a signal glitch may occur on GPIO pins before both the external  $V_{DD}$  supply and internal LDO voltages reach their normal operating conditions. This situation can occur when the  $V_{DD}$  and LDO voltages ramp up at significantly different rates. The LDO voltage ramp-up time is affected by the load capacitance on the LDO pin, therefore, it is important to keep this load at a nominal 1  $\mu$ F value as recommended in the data sheet. Adding significant more capacitance loading beyond the specification causes the time delay between the two supply ramp-up times to

grow, which possibly increases the severity of the glitching behavior.

Workaround(s): Ensuring that the  $V_{DD}$  power supply ramp up is as fast as possible helps minimize the

potential for GPIO glitches. Follow guidelines for LDO pin capacitive loading documented in the electrical section of the data sheet. System designers must ensure that, during the  $V_{DD}$  supply ramp-up time, possible GPIO pin glitches can cause no adverse effects to

their systems.

LM3GPIO#03 GPIO commit register control not working as expected

**Device(s) Affected:** Stellaris DustDevil-class Rev A0

**Description:** The commit control registers provide a layer of protection against accidental

programming of critical hardware peripherals, especially the JTAG/SWD pin functionality. Writes to protected bits of the GPIO Alternate Function Select (GPIOAFSEL), GPIO Digital Enable (GPIODEN), and GPIO Pull-up Select (GPIOPUR) registers are not committed to storage unless the GPIO Lock (GPIOLOCK) register has been unlocked and the appropriate bits of the GPIO Interrupt Clear (GPIOCR) register have been set. Registers GPIODEN and GPIOPUR should be protected by this mechanism but are not.

registers of repert and of for one and be protected by this meditalism but are not

Extra caution should be taken by software when modifying the **GPIODEN** and **GPIOPUR** registers as they are not protected by the **GPIOCR** commit register mechanism. Writes to the register bits that affect the JTAG/SWD pins (PC3:PC0) should be done with great care as this interface may become permanently disabled if done incorrectly. The NMI pin

(PB7) is not protected either.

Workaround(s):

# LM3GPIO#04 PB0 and PB1 have permanent internal pull-down resistance

Device(s) Affected: Stellaris DustDevil-class Rev A0

**Description:** Regardless of their configuration, PB0 and PB1 have an internal pull-down resistance. The internal structure of these pins is shown in Figure 1.

Figure 1. Internal Structure of PB0 and PB1

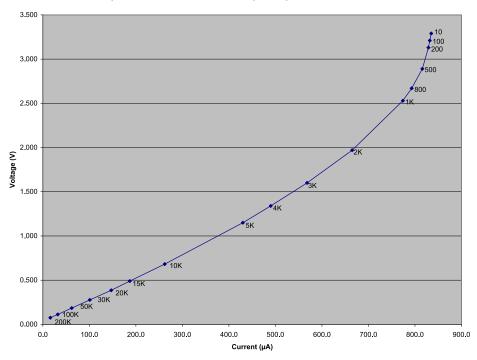

The characteristic of the pull-down for PB0 is shown in Figure 2. The data labels for each data point show the external pull-up resistance in Ohms.

Figure 2. Voltage versus Current for Various External Pull-up Resistors on PB0

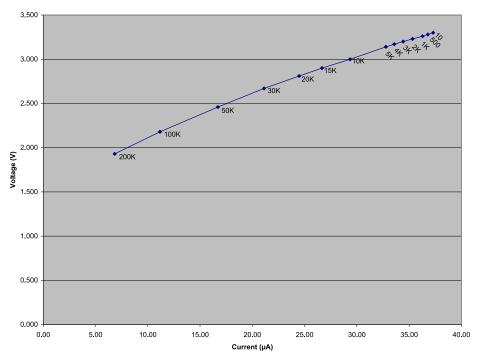

The characteristic of the pull-down for PB1 is shown in Figure 3. The data labels for each data point show the equivalent resistance in Ohms.

Figure 3. Voltage versus Current for Various External Pull-up Resistors on PB1

# Workaround(s):

When either of these pins is configured as an input, the external circuit must provide enough drive strength to over-drive the internal pull-down and achieve the necessary  $V_{IH}$  voltage level. If an external pull-up resistor is used, it must have a low value such as ~1 K $\Omega$  or less for PB0 and ~50 K $\Omega$  or less for PB1.

When either of these pins is configured as an output, the drive current needed to overdrive the internal pull-down resistance must be subtracted from the drive capabilities of the pin. In some applications, it may be necessary to select a higher drive strength (such as 4 mA instead of 2 mA) to achieve an acceptable output voltage on PB0.

## LM3GPTM#01

# General-purpose timer Edge Count mode count error when timer is disabled

Device(s) Affected: Stellaris Sandstorm-class Rev C2 and Fury-class Rev A2

**Description** When a general-purpose timer is configured for 16-Bit Input Edge Count Mode, the timer

(A or B) erroneously decrements by one when the Timer Enable (TnEN) bit in the **GPTM**

**Control (GPTMCTL)** register is cleared (the timer is disabled).

Workaround(s)

When the general-purpose timer is configured for Edge Count mode and software needs to "stop" the timer, the timer should be reloaded with the current count + 1 and restarted.

LM3GPTM#02 General-purpose timer 16-bit Edge Count or Edge Time mode does not load reload

value

Device(s) Affected: Stellaris Sandstorm-class Rev C2, Fury-class Rev A2 and DustDevil-class Rev A0

**Description** In Edge Count or Edge Time mode, the input events on the CCP pin decrement the

counter until the count matches what is in the GPTM Timern Match

**(GPTMTnMATCHR)** register. At that point, an interrupt is asserted and then the counter should be reloaded with the original value and counting begins again. However, the

reload value is not reloaded into the timer.

Workaround(s) Rewrite the GPTM Timern Interval Load (GPTMTnILR) register before restarting.

LM3GPTM#03 The General-Purpose Timer Match register does not function correctly in 32-bit

mode

**Device(s) Affected:** Stellaris Sandstorm-class Rev C2, Fury-class Rev A2 and DustDevil-class Rev A0

**Description:** The **GPTM Timer A Match (GPTMTAMATCHR)** register triggers a match interrupt and

a DMA request, if enabled, when the lower 16 bits match, regardless of the value of the

upper 16 bits.

Workaround(s): None.

LM3GPTM#04 A spurious DMA request is generated when the timer rolls over in Input-Edge Time

mode

Device(s) Affected: Stellaris DustDevil-class Rev A0

**Description:** When the timer is in Input-Edge Time mode and rolls over after the terminal count, a

spurious DMA request is generated.

Workaround(s): Either ignore the spurious interrupt, or disable DMA requests shortly before the terminal

count and enable them again shortly after the terminal count.

LM3GPTM#14 Writes to some General-Purpose Timer registers cause the counter to increment

and decrement in some cases

Device(s) Affected: Stellaris Sandstorm-class Rev C2, Fury-class Rev A2 and DustDevil-class Rev A0

**Description:** Writes to the following registers when the timer is enabled cause the counter to

increment in up count mode and decrement in down count mode when incrementing or

decrementing the counter inside the General-Purpose timers:

GPTM Timer n Match (GPTMTnMATCHR)

GPTM Timer n Prescale (GPTMTnPR)

Situations in which the counter is incremented or decremented include:

RTC Mode

Input edge count mode

Workaround(s): None.

LM3HIB#01 Hibernation module does not operate correctly

**Device(s) Affected:** Stellaris Fury-class Rev A2

**Description:** The Hibernation module on this microcontroller does not operate correctly.

Workaround(s): None.

LM3HIB#02 Hibernation module may have higher current draw than specified in data sheet

under certain conditions

Device(s) Affected: Stellaris DustDevil-class Rev A0

**Description:** If a battery voltage is applied to the VBAT power pin prior to power being applied to the

VDD power pins of the device, the current draw from the VBAT pin is greater than expected. The current may be as high as 1.6 mA instead of the data sheet specified 17 µA. The condition exists until power is applied to the VDD pin. Once the VDD pin has been powered, the VBAT current draw functions as expected. The VDD pin can then be powered up and down as required and the VBAT pin current specification is maintained.

Workaround(s): The VBAT pin higher-than-specified current draw condition can be avoided if the

microcontroller's VDD power pins are powered on prior to the time a battery voltage is

initially applied to the VBAT pin.

LM3HIB#03 Hibernation module HIB pin is not an open-drain output

Device(s) Affected: Stellaris DustDevil-class Rev A0

**Description:** Because the HIB pin is not an open-drain output, the pin is capable of sourcing current

to the power supply circuit that it controls. Under certain conditions, this configuration

may result in the Hibernation module drawing more current than expected.

If the voltage on the circuit connected to HIB drops below  $V_{BAT}$  before HIB is asserted, current may be sourced out of the HIB pin, increasing Hibernation module current to approximately 300  $\mu$ A instead of 16  $\mu$ A. This condition also occurs if the Hibernation

module attempts to wake but the power supply circuit remains below  $V_{BAT}$ .

Workaround(s): Add a diode between the HIB pin and the power supply to prevent current being sourced

by the Hibernation module. The cathode of the diode should be connected to the HIB signal. A diode with a low reverse current, such as the Panasonic MA2J728, is

recommended.

LM3HIB#04 Hibernation module registers are cleared by POR if not in Hibernate mode

Device(s) Affected: Stellaris DustDevil-class Rev A0

**Description:** The Hibernation module registers are reset by a POR event if the module is not in

Hibernate mode. This condition disables the module and stops the 32-kHz clock.

Workaround(s): To preserve Hibernation module settings, always enter Hibernate mode before removing

power. Note that the battery-backed memory is not cleared and is valid as long as V<sub>BAT</sub>

voltage remains within specification.

LM3HIB#05 Hibernation Raw Interrupt Status (HIBRIS) register may not properly indicate

Hibernation wake cause

Device(s) Affected: Stellaris DustDevil-class Rev A0

Description: The Hibernation Raw Interrupt Status (HIBRIS) register may not properly indicate the

event that caused the wake-up from hibernation. After the first wake-up event, the external wake (EXTW) status bit will get set incorrectly each time a wake-up event is

triggered, regardless of the wake-up source.

Workaround(s): If the EXTW bit is the only bit set, the cause is an external wake-up. If the EXTW bit and

another bit is set, the wake-up source is indicated by the other bit.

LM3HIB#06 In Hibernate mode, the microcontroller may be parasitically powered by external

USB signals

**Device(s) Affected:** Stellaris DustDevil-class Rev A0

**Description:** If a USB cable is still connected when the device is in Hibernation mode, the part may

be parasitically powered by external voltages on USB signals. These signals include the USB bidirectional differential data pins USB0DP and USB0DM, the USB OTG signals USB0VBUS and USB0ID, the USB VBUS supply if connected to PB1, and the pull-up on

PB0 if the part is used as a USB device.

Workaround(s): If Hibernate mode is required, it may be necessary to insert a switching circuit in the

USB signals to provide isolation during power down. The switching circuit should be

controlled by the HIB pin.

LM3HIB#07 Writes to certain Hibernation module registers sometimes fail

**Device(s) Affected:** Stellaris DustDevil-class Rev A0

**Description:** Due to a synchronization issue with the independent clock domain of the Hibernation

module, writes to certain registers may sometimes fail, even though the WRC bit in the **HIBCTL** register is set after the write occurs. Registers affected include **HIBRTCC**,

HIBRTCM0, HIBRTCM1, HIBRTCLD, HIBRTCT, and HIBDATA.

Workaround(s): After performing a write to any Hibernation module register or battery-backed memory,

read the contents back and verify that they are correct. If they are incorrect, perform the

write operation again.

#### LM3HIB#08

# Writes to Hibernation module registers may change the value of the RTC

Device(s) Affected:

Stellaris DustDevil-class Rev A0

**Description:**

If the Hibernation module's RTC counter is active, any write to certain Hibernation module registers that occurs while the RTC counter is changing from the current value to the next can cause corruption of the RTC counter stored in the HIBRTCC register. Registers affected are: HIBRTCC, HIBRTCM0, HIBRTCM1, HIBRTCLD, HIBRTCT, and HIBDATA.

Workaround(s):

The user application must guarantee that writes to the affected Hibernation module registers cannot occur on the RTC counter boundary. Any initial configuration of the affected Hibernation module registers must be done before enabling the RTC counter.

There are two ways to update affected Hibernation Module registers after initial configuration:

- Use the Hibernation RTC match interrupt to perform writes to the affected

Hibernation module registers. Assuming the interrupt is guaranteed to be serviced

within 1 second, this technique provides a mechanism for the application to know that

the RTC update event has occurred and that it is safe to write data to the affected

Hibernation module registers. This method is useful for applications that don't require

many writes to Hibernation module registers.

- 2. Set up a secondary time-keeping resource to indicate when it is safe to perform writes to the affected Hibernation module registers. For example, use a general-purpose timer in combination with the Hibernation RTC match interrupt. In this scenario, the RTC match interrupt is used to both update the match register value and enable the general-purpose timer in one-shot mode. The timer must be configured to have a maximum time-out period of less than 1 second. In this configuration, a global variable is used to indicate that it is safe to perform writes to the affected Hibernation module registers. When the one-shot timer times out, the timer interrupt updates the global variable to indicate that writes are no longer safe. This procedure is repeated on every RTC match interrupt.

LM3I2C#01 fC Slave Masked Interrupt Status (I2CSMIS) register bits are incorrect

Device(s) Affected: Stellaris DustDevil-class Rev A0

Description: The bits within the I<sup>2</sup>C Slave Masked Interrupt Status (I2CSMIS) register do not

operate properly. This register should not be used by software.