# TLV803EA29EVM 3-Pin Voltage Supervisor User Guide

This user's guide describes the TLV803EA29EVM evaluation module (EVM). This guide contains the EVM schematic, bill of materials (BOM), assembly drawing, and top and bottom board layouts.

#### Contents

| 1 | Introduction                             | 2 |

|---|------------------------------------------|---|

| 2 | Schematic, Bill of Materials, and Layout | 3 |

| 3 | EVM Connectors                           | 7 |

| 4 | EVM Setup and Operation                  | 8 |

#### List of Figures

| 1  | TLV803EA29EVM Board Top                                               | 2 |

|----|-----------------------------------------------------------------------|---|

| 2  | TLV803EA29EVM Board Bottom                                            | 2 |

| 3  | TLV803EA29EVM Schematic                                               | 3 |

| 4  | Component Placement—Top Assembly                                      | 5 |

| 5  | Component Placement—Bottom Assembly                                   | 5 |

| 6  | Layout—Top                                                            | 5 |

| 7  | Layout—Bottom                                                         | 5 |

| 8  | Top Layer                                                             | 5 |

| 9  | Bottom Layer                                                          | 5 |

| 10 | Top Solder Mask                                                       | 6 |

| 11 | TLV803EA29EVM Propagation Delay Time High-to-Low (t <sub>PDHL</sub> ) | 8 |

| 12 | TLV803EA29EVM Reset Delay Time (t_D)                                  | 8 |

| 13 | TLV803EA29EVM Return From Fault Glitch Immunity                       | 9 |

|    |                                                                       |   |

#### List of Tables

| 1 | EVM BOM                                       | 4 |

|---|-----------------------------------------------|---|

| 2 | Test Points                                   | 7 |

| 3 | List of Onboard Jumpers                       | 7 |

| 4 | Nominal Supply and Typical Threshold Voltages | 8 |

|   |                                               |   |

### Trademarks

All trademarks are the property of their respective owners.

### 1 Introduction

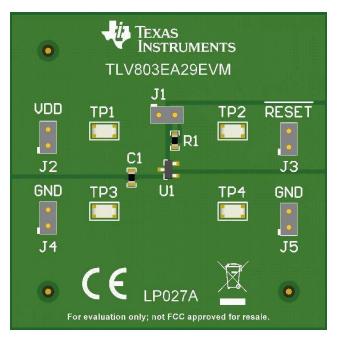

The TLV803EA29EVM is an evaluation module (EVM) for the TLV803E voltage supervisor also called a Reset IC. The TLV803EA29EVM can be used with any TLV803E, TLV809E, TLV803, and TLV809 devices variants, but please note that if using a push-pull device variant (TLV809E or TLV809), the shunt on J1 must be removed as push-pull devices do not use a pull-up resistor so R1 must be disconnected. The TLV803E has a supply voltage range of 1.7 V to 6 V, and offers connections for all device input and output pins. Test points are provided to give the user access to extra connections if needed for oscilloscope or multimeter measurements.

Figure 1. TLV803EA29EVM Board Top

# 1.1 Related Documentation

TLV803E / TLV809E Datasheet

# 1.2 TLV803E Applications

- Applications using DSPs, microcontrollers, or microprocessors

- Wireless communication systems

- Portable/battery-powered equipment

- Setup boxes and TVs

- Building automation

- Notebook/desktop computers, servers

# 2 Schematic, Bill of Materials, and Layout

This section provides a detailed description of the TLV803EA29EVM schematic, bill of materials (BOM), and layout.

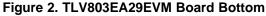

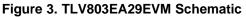

# 2.1 TLV803EA29EVM Schematic

Schematic, Bill of Materials, and Layout

# 2.2 TLV803EA29EVM Bill of Materials

| DESIGNATOR            | QTY | VALUE | DESCRIPTION                                                                            | PACKAGE<br>REFERENCE                      | PART NUMBER          | MANUFACTURER      |

|-----------------------|-----|-------|----------------------------------------------------------------------------------------|-------------------------------------------|----------------------|-------------------|

| !PCB                  | 1   |       | Printed Circuit Board                                                                  |                                           | LP027                | Any               |

| C1                    | 1   | 0.1uF | CAP, CERM, 0.1 uF, 10 V, +/- 10%,<br>X7R, 0603                                         | 0603                                      | C0603C104K8RACTU     | Kemet             |

| H1, H2, H3,<br>H4     | 4   |       | Bumpon, Hemisphere, 0.44 X 0.20,<br>Clear                                              | Transparent<br>Bumpon                     | SJ-5303 (CLEAR)      | 3M                |

| J1, J2, J3, J4,<br>J5 | 5   |       | Header, 100mil, 2x1, TH                                                                | Header, 2x1, 100mil,<br>TH                | 800-10-002-10-001000 | Mill-Max          |

| R1                    | 1   | 49.9k | RES, 49.9 k, 1%, 0.1 W, AEC-Q200<br>Grade 0, 0603                                      | 0603                                      | ERJ-3EKF4992V        | Panasonic         |

| SH-J1                 | 1   |       | Shunt, 100mil, Tin plated, Black                                                       | Shunt Connector<br>Black Open Top,<br>2x1 | SNT-100-BK-T-H       | Samtec            |

| TP1, TP2,<br>TP3, TP4 | 4   |       | Test Point, Miniature, SMT                                                             | Test Point,<br>Miniature, SMT             | 5019                 | Keystone          |

| U1                    | 1   |       | 3-Pin Voltage Supervisors with<br>Active-Low, Open-Drain Reset,<br>DBZ0003A (SOT-23-3) | DBZ0003A                                  | TLV803EA29DBZR       | Texas Instruments |

| FID1, FID2,<br>FID3   | 0   |       | Fiducial mark. There is nothing to buy or mount.                                       | N/A                                       | N/A                  | N/A               |

### Table 1. EVM BOM

#### 2.3 Layout and Component Placement

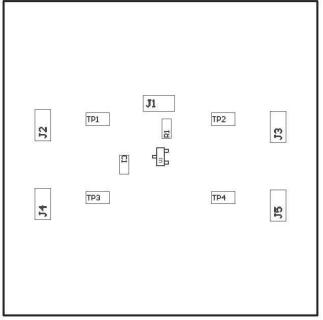

Figure 4 and Figure 5 show the top and bottom assemblies of the printed circuit board (PCB) to show the component placement on the EVM.

Figure 6 and Figure 7 show the top and bottom layouts, Figure 8 and Figure 9 show the top and bottom layers, and Figure 10 shows the top solder mask of the EVM.

Figure 4. Component Placement—Top Assembly

Figure 6. Layout—Top

Figure 5. Component Placement—Bottom Assembly

Figure 7. Layout—Bottom

#### Schematic, Bill of Materials, and Layout

Figure 8. Top Layer

Figure 9. Bottom Layer

Figure 10. Top Solder Mask

### 3 EVM Connectors

This section describes the connectors, jumpers, and test points on the EVM as well as how to connect, set up, and properly use the EVM. Each EVM has an input power supply connection, and output RESET pin, and a ground pin.

# 3.1 EVM Test Points

Table 2 lists the test points and functional descriptions. All pins of the device are broken out to test points on the EVM.

| TEST POINT<br>NUMBER | TEST POINT<br>SILKSCREEN<br>LABEL | FUNCTION                | DESCRIPTION                                                                                         |

|----------------------|-----------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|

| TP1                  | VDD                               | Connection to VDD pin   | Allows user to monitor the VDD pin. The VDD pin connects to the input power supply.                 |

| TP2                  | RESET                             | Connection to RESET pin | Allows user to monitor the RESET pin. This pin changes logic state depending on the voltage on VDD. |

| TP3                  | GND                               | Connection to GND pin   | Allows user to connect to the GND pin.                                                              |

| TP4                  | GND                               | Connection to GND pin   | Allows user to connect to the GND pin.                                                              |

## Table 2. Test Points

# 3.2 EVM Jumpers

Table 3 lists the jumpers on the TLV803EA29EVM. As ordered, the EVM will have 5 jumpers populated.

| JUMPER DEFAULT<br>CONNECTION |         | DESCRIPTION                                                                                                              |

|------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------|

| J1                           | Closed  | Connect a shunt jumper to jumper J1 to use R1 as the pull-up resistor on the $\ensuremath{\overline{RESET}}$ output pin. |

| J2                           | Shorted | Both pins on J2 are connected together. Connect one of the pins to the positive (VDD) terminal of the power supply.      |

| J3                           | Shorted | Both pins on J3 are connected together. Use either pin on jumper J3 to monitor the RESET output pin.                     |

| J4 Shorted                   |         | Both pins on J4 are connected together. Use either pin on jumper J4 as the ground connection.                            |

| J5                           | Shorted | Both pins on J5 are connected together. Use either pin on jumper J5 as the ground connection.                            |

#### 4 EVM Setup and Operation

This section describes the functionality and operation of the TLV803EA29EVM. The user must read the TLV803E / TLV809E Datasheet for electrical characteristics of the device.

### 4.1 Input Power (V<sub>DD</sub>)

The  $V_{DD}$  supply is connected through the J2 header on board. Both pins of jumper J2 are connected together so power can be applied to either pin. Supply voltage is dependent on what the user wants to monitor, but the range is 1.7 V to 6 V. Table 4 details the nominal supply and typical threshold voltage.

| DEVICE     | NOMINAL SUPPLY VOLTAGE<br>(V) | TYPICAL THRESHOLD<br>VOLTAGE (V) |

|------------|-------------------------------|----------------------------------|

| TLV803EA29 | 3.3                           | 2.9 (+/- 2% MAX)                 |

#### Table 4. Nominal Supply and Typical Threshold Voltages

#### 4.2 Monitoring Voltage on VDD

The TLV803E device monitors voltage via the VDD pin. The EVM provides jumper J2 and test point TP1 for connecting the power supply input to the VDD pin. If the voltage on this pin drops below  $V_{IT}$ , RESET is asserted low. The VDD pin is connected internally to a comparator through an internal resistor divider at the positive input and the negative input is connected to an internal reference. The internal resistor divider is set to provide the input voltage threshold to cause a reset,  $V_{IT}$ , that corresponds to the chosen device variant. Please see the Device Comparison Table in the *TLV803E / TLV809E Datasheet* for more information on the different device variants.

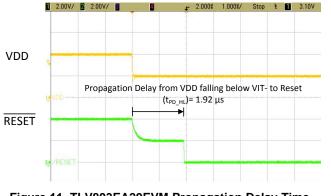

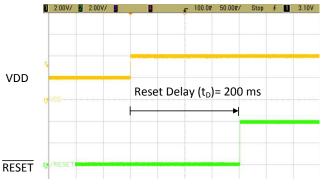

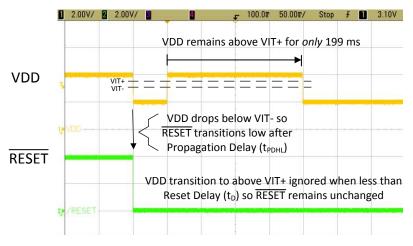

Upon startup, the TLV803E requires VDD to be above  $V_{POR}$  before the RESET output is in the correct logic state. Figure 11 shows the propagation time delay high-to-low ( $t_{PDHL}$ ) when a voltage fault occurs by VDD falling below  $V_{IT}$  to the time RESET transitions active low. Figure 12 shows the reset time delay when the fault condition is removed by VDD rising above  $V_{IT}$  to the time RESET transitions inactive high. The TLV803E has built-in glitch immunity so falling voltage transients on VDD are ignored if the falling pulse duration is less than the glitch immunity timing ( $t_{GI}$ ). The glitch immunity specification depends on the amplitude of the voltage transient and the operating conditions. Please see the Glitch Immunity specification in the Timing Requirements section of the TLV803E / TLV809E Datasheet for more detailed information.

Figure 11. TLV803EA29EVM Propagation Delay Time High-to-Low (t<sub>PDHL</sub>)

Figure 12. TLV803EA29EVM Reset Delay Time (t<sub>D</sub>)

# 4.3 Reset Output (RESET )

The TLV803EA29EVM comes populated with TLV803EA29 device variant which has open-drain, activelow output topology for the RESET pin. The other device variants provide different output topolgies and/or different voltage threshold options and can be used on this EVM. Note: if using a TLV809E device variant with push-pull output topology, the pull-up resistor must be disconnected by leaving jumper J1 open. The EVM provides a jumper J3 and a test point TP2 connected directly to the RESET pin for monitoring and/or interfacing to other devices. The reset signal will be asserted low when the voltage on the VDD pin falls below V<sub>IT</sub>. When the voltage on VDD rises higher than the hysteresis voltage above the threshold voltage (V<sub>HYS</sub> + V<sub>IT</sub>. or also labeled V<sub>IT+</sub>), the RESET pin is pulled high to the inactive state indicating no fault condition. As Figure 13 shows, when returning from a fault condition, that is when VDD rises above V<sub>IT+</sub>, VDD must be above V<sub>IT+</sub> for longer than the reset delay (t<sub>D</sub>) otherwise RESET will not transition back to logic high inactive state. This is to prevent a premature signaling of no fault condition if VDD briefly comes out of undervoltage condition before faulting again.

Figure 13. TLV803EA29EVM Return From Fault Glitch Immunity

Develote a Ultration -

| Revision History |          |                 |  |  |  |

|------------------|----------|-----------------|--|--|--|

| DATE             | REVISION | NOTES           |  |  |  |

| June 2019        | *        | Initial Release |  |  |  |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated