# LM833

AN-1002 ADC16071/ADC16471 Analog Layout and Interface Design Considerations

Literature Number: SNOA350

# ADC16071/ADC16471 Analog Layout and **Interface Design** Considerations

## INTRODUCTION

The ADC16071 and the ADC16471 are 16-bit oversampling delta-sigma ( $\Delta\Sigma$ ) analog to digital converters that are capable of delivering high performance signal conversions at data output rates up to 192 kSps (kilo samples per second). The ADC16071/ADC16471's ultimate performance is dependent on the analog interface, the digital interface, and the printed circuit board on which it is placed. While the board design and layout can sometimes be taken for granted in lower resolution ADC applications, it is critical in obtaining best performance from high-resolution ADCs. Extracting all of the performance that the ADC16071/ ADC16471 is capable of delivering requires special attention to such areas as board layout, ground planes, power supply bypassing, power supply routing, socketing, clock generation, signal routing, and analog signal conditioning.

### ANALOG INPUT RANGE

o

The ADC16071/ADC16471 produces a 16-bit, twos compliment output according to the following equation:

$$utput = \frac{32768 \bullet (V_{IN+} - V_{IN-})}{(V_{REF+} - V_{REF-})}$$

The signals applied to  $V_{IN+}$  and  $V_{IN-}$  must have potentials between the analog supply  $(V_{A\,+})$  and analog ground (AGND). For accurate conversions, the absolute difference between  $V_{\text{IN}\,+}$  and  $V_{\text{IN}\,-}$  should be less than the difference between V<sub>REF+</sub> and V<sub>REF-</sub>. Best harmonic performance will result when a balanced voltage is applied to  $V_{IN+}$  and National Semiconductor Application Note 1002 Mark Seiders September 1995

$V_{\text{IN}-}$  that has a common mode voltage at or below  $V_{\text{MID}},$ where  $V_{\mbox{MID}}$  is an output pin on the ADC16071/ADC16471 with a potential equal to one half of the analog supply (VA+/2). The ADC16471 has an internal 2.5V bandgap reference that sets  $V_{\mathsf{REF}+}$  =  $V_{\mathsf{MID}}$  + 1 .25V and  $V_{\mathsf{REF}-}$  = V<sub>MID</sub> - 1.25V. The ADC16071 requires an externally applied reference whose range ( $V_{REF+} - V_{REF-}$ ) can be varied from 1V to  $V_{A+}$ . See Reference Voltage Generation for the ADC16071 for examples of driving the ADC16071's reference inputs.

### ANTI-ALIASING FILTER CONSIDERATIONS

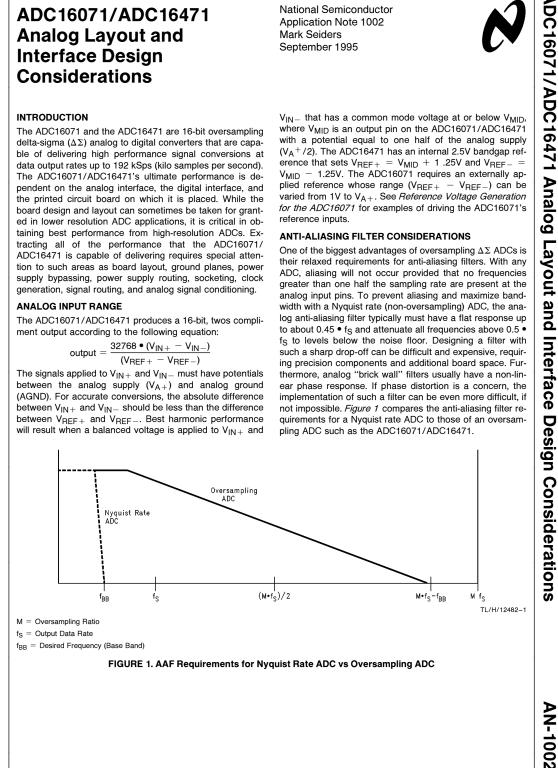

One of the biggest advantages of oversampling  $\Delta\Sigma$  ADCs is their relaxed requirements for anti-aliasing filters. With any ADC, aliasing will not occur provided that no frequencies greater than one half the sampling rate are present at the analog input pins. To prevent aliasing and maximize bandwidth with a Nyquist rate (non-oversampling) ADC, the analog anti-aliasing filter typically must have a flat response up to about 0.45 • f<sub>S</sub> and attenuate all frequencies above 0.5 • f<sub>S</sub> to levels below the noise floor. Designing a filter with such a sharp drop-off can be difficult and expensive, requiring precision components and additional board space. Furthermore, analog "brick wall" filters usually have a non-linear phase response. If phase distortion is a concern, the implementation of such a filter can be even more difficult, if not impossible. Figure 1 compares the anti-aliasing filter requirements for a Nyquist rate ADC to those of an oversampling ADC such as the ADC16071/ADC16471.

© 1995 National Semiconductor Corporation TL/H/12482 RRD-B30M115/Printed in U.S.A

The ADC164071/ADC16471's modulator samples the analog input at a rate equal to  $f_{CLK}/2$ , where  $f_{CLK}$  is the frequency of the clock applied to the ADC16071/ADC16471's CLK pin. The output data rate ( $f_{S}$ ) is equal to  $1_{64}^{\prime}$  (the oversampling ratio) of the modulator's sample rate, or  $f_{CLK}/128$ . The analog baseband ( $f_{BB}$ ) is equal to one half of the data output rate, or  $f_{CLK}/256$ .

By oversampling the analog input at 64 times the Nyquist rate ( $f_S$ ) for the desired analog baseband, the ADC16071/ADC16471 pushes out the point at which aliasing occurs. This dramatically relaxes the performance requirements for the anti-aliasing filter. The critical point of attenuation for an oversampling ADC's anti-aliasing filter is typically pushed out even further because of on-chip digital filtering. The ADC16071/ADC16471 contains a 246 tap internal, linear phase, finite impulse response (FIR) filter that cuts off all frequencies above the analog baseband ( $f_{BB}$ ).

Aliased frequencies are mirrored about half the sampling rate of the modulator,  $(M \bullet f_S)/2$ . Therefore, any frequencies between  $(M \bullet f_S)/2$  and  $M \bullet f_S$  are aliased into the range between  $(M \bullet f_S)/2$  and DC. Since all frequencies greater than the baseband (f\_BB) are filtered out by the onchip digital filters, the only potentially damaging frequencies

are those above  $M \bullet f_S - f_{BB}$ , which are aliased into the baseband. Thus the external anti-aliasing filter for the ADC16071/ADC16471 need only cut off frequencies above  $M \bullet f_S - f_{BB}$ . The ADC16071/ADC16471 has an oversampling ratio of 64 (M=64). This ratio allows the ADC16071/ADC16471's anti-aliasing filter's critical point of attenuation to be pushed out 127 times (63.5  $\bullet$  f\_S vs 0.5  $\bullet$  f\_S) higher than what it would need to be for a Nyquist rate converter with equivalent output bandwidth!

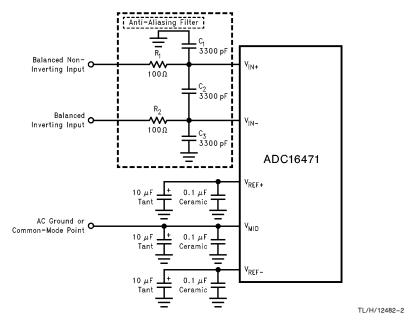

### PASSIVE RC ANTI-ALIASING FILTER NETWORK

A recommended, simple anti-aliasing input network is the first-order, passive, low-pass RC filter shown in *Figure 2*. This network has a flat frequency and linear phase response in the analog baseband, and eliminates analog frequency components above M •  $f_{\rm S}-f_{\rm BB}$  that may cause aliasing. In addition, C<sub>1</sub>, C<sub>2</sub>, and C<sub>3</sub> provide a charge reservoir for the ADC16071/ADC16471 modulator's input capacitors (see *Analog Interface Amplifier Considerations*). The filter's -3 dB cutoff frequency is:

$$f_C = \frac{1}{6\pi \; \text{RC}}$$

where R = R\_1 = R\_2 and C = C\_1 = C\_2 = C\_3

FIGURE 2. Simple, Passive, Low-Pass Input Network

To ensure that the filter's frequency response is flat in the baseband and that it provides sufficient attenuation to frequencies above  $M \bullet f_S - f_{BB}$ , the values of R and C should be chosen so that the filter's 3 dB cutoff is between  $f_{CLK}/$ 250 and  $f_{CLK}/100$ . With an  $f_{CLK}$  of 24.576 MHz (192 kHz data output rate), typical values for R and C are  $100\Omega$  and 3300 pF, respectively. These values result in a 3 dB cutoff equal to approximately 160 kHz, or  $f_{CLK}/150$  and an attenuation of about 40 dB at  $M \bullet f_S - f_{BB}$ .

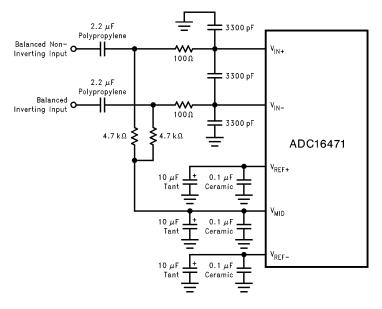

# LEVEL SHIFTING THE INPUT SIGNAL

For best conversion performance, the signal applied to the ADC16071/ADC16471's analog input pins,  $V_{IN}+$  and  $V_{IN}-$ , should be a balanced AC signal with a common mode voltage at or below one-half of the ADC's supply voltage ( $V_{MID}$ ). The simplest way to do this is to capacitively couple the applied input signal and connect the  $V_{MID}$  output to  $V_{IN}+$  and  $V_{IN}-$  through 4.7 k $\Omega$  resistors (*Figure 3*).

TL/H/12482-3

FIGURE 3. Capacitively Coupling and Level Shifting a Balanced Input Signal

# RELATION BETWEEN CAPACITOR DIELECTRIC AND SIGNAL DISTORTION.

For any capacitors connected to the ADC16071/ ADC16471's analog inputs, the dielectric plays an important role in determining the amount of distortion generated in the input signal. The dielectric must have low dielectric absorption. This requirement is fulfilled by using capacitors that have film dielectrics. Of these, polypropylene and polystyrene are the best. These are followed by polycarbonate and mylar. If ceramic capacitors are chosen, use only capacitors with NPO dielectrics.

### INPUT SIGNAL MAGNITUDE AND OVERLOAD

Following the switched capacitor input of the ADC16071/ ADC16471, the analog input and reference voltages are fed into a pseudo fourth order, MASH (Multistage noise Shaping) delta sigma modulator. The modulator is designed to act as a high-pass filter to the quantization noise introduced by its comparators. This high-pass noise shaping characteristic minimizes the amount of quantization noise present in the baseband at the output of the modulator. The higher frequency quantization noise that is present at the output of the modulator is filtered by the internal, brick wall FIR. See Appendix: *Noise Shaping in Delta Sigma Modulators* for further discussion.

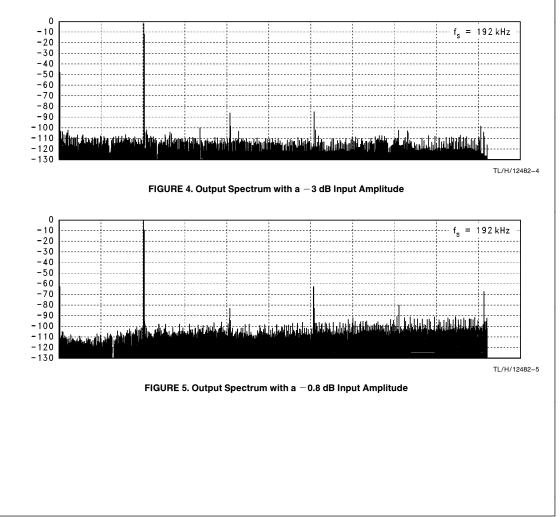

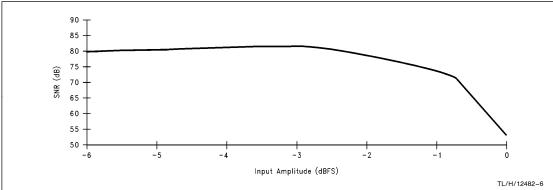

Due to overload in the modulator's comparators, as the analog input amplitude approaches full scale, the modulator's feedback coefficients begin to change. This tends to reduce the cutoff frequency of the modulator's noise shaping characteristic, allowing more quantization noise to pass in the analog baseband. Since anything passed in the analog baseband won't be filtered by the FIR, added quantization noise will be present in the output of the ADC16071/ ADC16471. When examining an output spectrum from the ADC16071/ADC16471, this additional quantization noise can be seen as a slight raising of the noise floor toward the upper end of the analog baseband and increased odd harmonic distortion. Figures 4 and 5 show output spectra from the same ADC16071 with input amplitudes of -3 dB and -0.8 dB below full scale (dBFS), respectively. The raised noise floor and additional odd harmonic distortion are visually noticeable with a -0.8 dB input.

At room temperature, the ADC16071/ADC16471 performs well (meets its published specifications) with input amplitudes up to  $-3 \, dB \, FS$ . As the input amplitude exceeds  $-3 \, dB \, FS$ , performance begins to degrade. At  $-2 \, dB \, FS$ , the SNR is about 2 dB worse than with  $a -3 \, dB \, FS$  input. With  $a -1.4 \, dB \, FS$  input, the SNR is about 6 dB worse. With  $a -0.66 \, dB \, FS$  input, the SNR drops by more than 10 dB from the  $-3 \, dB \, FS$  input case. *Figure 6* illustrates the typical degradation in the dynamic performance of the ADC16071/ADC16471 as the input amplitude approaches full scale. At higher temperatures, the nonlinearities may be a factor at slightly lower input amplitudes, but overload noise and distortion shouldn't be experienced over the entire  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range with input amplitude ampli-

### ANALOG INTERFACE AMPLIFIER CONSIDERATIONS

The input impedance of the ADC16071/ADC16471, due to the effective resistance of the switched capacitor input, varies as follows:

$$Z_{\rm IN} = \frac{10^{12}}{2.35 \bullet (f_{\rm CLK}/2)}$$

where  $f_{CLK}$  is the frequency of the clock applied to the ADC16071/ADC16471's CLK pin.

The current required during the act of switching, or connecting, the input sampling capacitors between the source circuitry and the ADC16071/ADC16471's modulator input can cause momentary instability in amplifiers with limited gainbandwidth. To overcome this problem, amplifiers used to drive the inputs of the ADC16071/ADC16471 must be able to recover quickly from the transient current requirements of the switched capacitor input. The capacitors used in the recommended anti-aliasing filter configuration (*Figure 2*) help by acting as charge reservoirs for these current spikes, but it is still recommended that amplifiers be used that have a minimum gain bandwidth of one half the frequency of the clock. For example, when the clock frequency is 24.576 MHz, the gain-bandwidth of any op-amps driving the inputs of the ADC16071/ADC16471 should be at least 13 MHz. The LM6218 and the LM833 are good choices for buffering or amplifying signals applied to the ADC16071/ADC16471. These amplifiers have sufficient bandwidth and slew rate and produce sufficiently low distortion and noise. Additionally, they are available in a dual package, saving board space and component count.

To help source amplifiers settle faster, a series resistance (50 $\Omega$  to 100 $\Omega$ ) may be placed between the amplifier's output and the ADC16071/ADC16471's inputs. This is already accomplished when the passive low-pass network as shown in *Figure 2* is connected between the amplifier's output and the ADC16071/ADC16471's inputs.

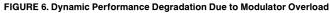

# SINGLE-ENDED BIPOLAR INPUT TO BALANCED UNIPOLAR OUTPUT BUFFER

The ADC16071/ADC16471 exhibits the best distortion performance when a balanced AC signal is applied to its analog inputs that has a common mode offset at or below V<sub>MID</sub>. The circuit in *Figure 7* can be used to convert a single-ended, bipolar signal centered about ground to a balanced signal centered about V<sub>MID</sub>.

### FIGURE 7. Unbalanced-to-Balanced Buffer

This circuit's level shifting is accomplished using the ADC16071/ADC16471's on-chip one-half supply voltage output, V<sub>MID</sub>. The V<sub>MID</sub> output voltage is divided in half and applied to the non-inverting input of the circuit's first inverting buffer. V<sub>MID</sub> is divided in half because the difference between the DC offset at the input to the circuit (OV) and the voltage at the non-inverting input of the first buffer (V<sub>MID</sub>/2) will see a gain of two. This results in an offset voltage equal to V<sub>MID</sub> at the output of the first inverting buffer. V<sub>MID</sub> is also applied to the non-inverting input of the circuit's second inverting buffer. The outputs are two 180° out-of-phase signals (V<sub>IN+</sub> and V<sub>IN-</sub>) that swing above and below the V<sub>MID</sub> voltage.

It is important to note that because of the difference in potential between the inverting input of the first buffer and the common mode output of the signal source, the signal source will have to sink an average of about 270  $\mu$ A and up to a peak of about 540  $\mu$ A. An alternate approach is to connect a coupling capacitor between the output of the signal source and the input to the circuit in *Figure 7*.

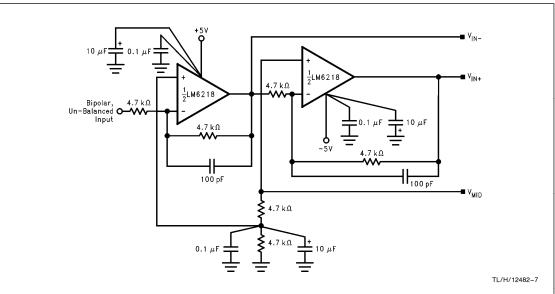

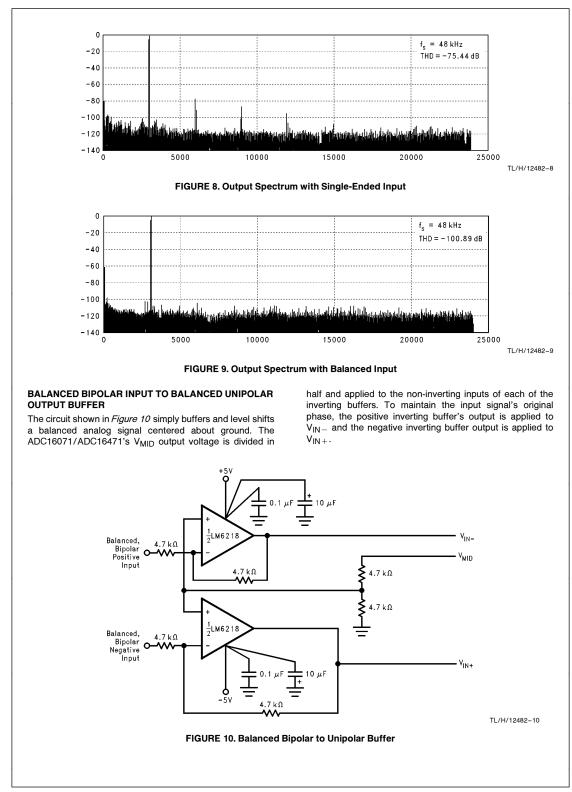

When the ADC16071/ADC16471 is driven by a balanced signal, the conversion process will cancel out common mode noise and reduce harmonic distortion. *Figure 8* shows an output spectrum from an ADC16071 with a single-ended input signal centered around V<sub>MID</sub>. *Figure 9* shows the output spectrum from the same ADC16071 with same signal source (without the V<sub>MID</sub> offset) after it has been converted to a balanced signal using the circuit in *Figure 7*. The distortion performance (THD) improves by more than 25 dB when the input is converted to a balanced signal.

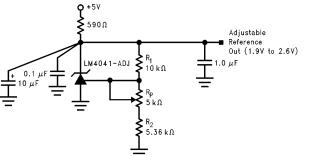

# REFERENCE VOLTAGE GENERATION FOR THE ADC16071

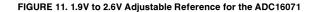

The ADC16071 requires an external reference voltage source. It must have low output noise and be stable. A suggested circuit that generates a stable reference voltage that can be adjusted between 1.9V and 2.6V is shown in *Figure 11*. It uses the LM4041-ADJ adjustable shunt bandgap reference. The potentiometer, R<sub>P</sub>, adjusts the output between 1.9V and 2.6V. If a fixed output is desired, replace the R<sub>1</sub>, R<sub>P</sub>, and R<sub>2</sub> resistor string with the fixed resistor string shown in *Figure 12*. Use the equation in *Figure 12* to determine the fixed resistor values.

### POWER SUPPLY VOLTAGES FOR IMPROVED PERFORMANCE

While adequate performance will be achieved by operating the ADC16071/ADC16471 with +5V connected to  $V_{A+}$ ,  $V_{M+}$  and  $V_{D+}$ , dynamic performance, as indicated by SINAD, can be further enhanced by changing  $V_{D+}$  to a voltage lower than  $V_{A+}$  and  $V_{M+}$ . By setting  $V_{D+}$  to 3.5V and  $V_{A+}$  and  $V_{M+}$  to 5.5V, improvements of up to 5 dB will be seen in both noise floor and harmonic performance. The improved performance can be attributed to the reduction of digital switching noise due to the lower digital supply voltage.

TL/H/12482-11

From the LM4041-ADJ datasheet:  $\frac{\text{R2}}{\text{R1}} = \frac{\text{V}_{\text{OUT}}}{1.24 - (1.3 \times 10^{-3}) \, \text{V}_{\text{OUT}}} -$

#### FIGURE 12. 2.0V Fixed Reference for the ADC16071

### PRINTED CIRCUIT BOARD CONSIDERATIONS

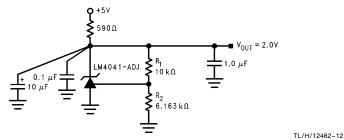

#### Ground Planes and Signal Trace Lavers

Analog and digital ground planes are essential in extracting the best performance from high-resolution delta-sigma converters. Ground planes reduce ground return impedances to low levels, ensuring that power supply bypass capacitors have the lowest AC-resistance path possible. The ADC16071/ADC16471's conversion performance is optimized using separate analog and digital ground planes. The ground planes should be connected together at a single point, the power supply ground connection.

Best performance is achieved by ensuring that the trace/ ground plane association integrity is maintained. All analog and digital traces are placed over, or within, their associated ground plane.

In a multilayer printed circuit board with separate ground and trace layers, the supply and signal trace layers should be "sandwiched" between the analog and digital ground plane layers (Figure 13). The outer ground plane layers act as shields, attenuating noise from external sources and from internal digital switching.

Analog signal, digital control signal, and power supply traces should be separated from each other. If the physical board layout prevents adequate separation of the digital, analog, and power supply traces, they should be placed on different circuit board layers and cross at right angles.

### INPUT NETWORK LAYOUT AND ROUTING

Careful consideration must be observed concerning the layout and placement of the input network connected to the two balanced inputs,  $V_{\text{IN}+}$  and  $V_{\text{IN}-}.$  The layout should be balanced and symmetrical with respect to the  $V_{IN+}$  and  $V_{\text{IN}-}$  pins. All associated traces should have equal trace length and width dimensions. This symmetry should be extended back to the outputs of circuitry that drives  $V_{IN+}$  and  $V_{IN}$

### CLOCK SIGNAL GENERATION AND ROUTING

The ADC16071/ADC16471 requires a low jitter clock signal

shoot of no more than 100 mVPP) and has rise and fall times in the range of 3 ns-10 ns (10%-90%). The Ecliptek (EC1100 series) and SaRonix (NCH060 and NCH080 series) are recommended crystal clock oscillators for driving the CLK input of the ADC16071/ADC16471. Both of these families use HCMOS logic circuitry for fast rise and fall times.

Overshoot and ringing on the clock-signal edge that a converter uses to internally clock its operation will result in increased noise and distortion. The effects of overshoot and ringing can be minimized by using a series damping resistor between the output of the clock-signal source and the ADC16071/ADC16471's CLK pin. The value of the resistor used is dependent on the board layout, and usually ranges from 25 $\Omega$  to 150 $\Omega$ . A typical starting value is 50 $\Omega$ .

### SOCKET CONSIDERATIONS FOR IMPROVED POWER SUPPLY BYPASSING

The ADC16071/ADC16471 is clocked at very high frequencies. This high frequency clocking produces high frequency current spikes and glitches on the power supply lines. If not attenuated, these power supply perturbations will degrade the ADC16071/ADC16471's conversion performance.

For all integrated circuits, the power supply inputs should always be viewed as signal inputs. The internal circuit will treat any AC signal appearing on the power supply voltage as another input signal.

The ADC16071/ADC16471's power supply rejection (PSR) is high at low frequencies and usually decreases as frequency increases. Thus, at the high frequencies used to clock the ADC16071/ADC16471, the PSR is low. Therefore, external power supply bypass capacitors are needed to provide the ADC16071/ADC16471's transient current requirements and to improve the PSR by attenuating the high frequency noise created by high speed digital switching.

As the distance between the ADC16071/ADC16471 and its bypass capacitors increases, so do the bypass capacitor lead inductances. Increased lead inductances result in decreased high frequency attenuation. At the frequencies used to clock the ADC16071/ADC16471 (f<sub>CLK</sub> = 24.576 MHz), even a typical lead-length (bond wires, package lead, and capacitors leads) of 10mm has an inductance of 20 nH or 3 $\Omega$  impedance. This impedance reduces the efficiency of the bypass capacitors. Spikes and glitches riding on the DC supply voltage are most efficiently attenuated when power supply bypass capacitors are placed as close as possible to the power supply pins.

Ideally the ADC16071/16471 should be soldered directly to the printed circuit board. This minimizes lead length between power supply and ground pins and power supply bypass components. Even a lead-length increase of 0.125" can degrade SINAD performance by 5 dB–15 dB.

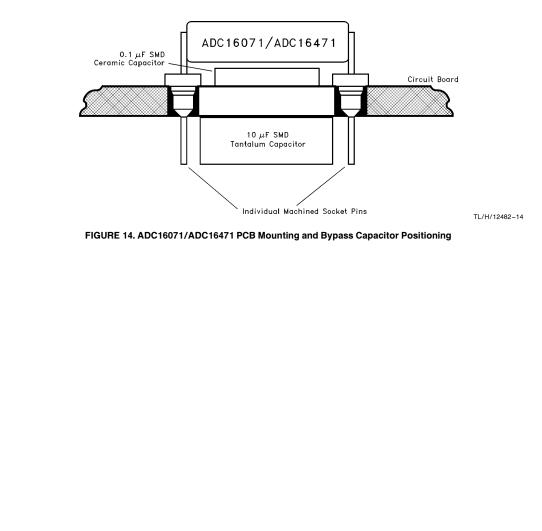

When using the ADC16071/ADC16471 in the molded Dualin-Line Package (DIP), mounting the ADC in a modified "socket", allows surface-mount capacitors to be placed directly under the package and between the pins using the shortest possible trace lengths (*Figure 14*). This "socket" is created by using individual machined socket-pins. These pins require a hole size of 58 mils. This hole size ensures that only the topmost portion of the pin remains above the circuit board. These "socket" pins will tightly grip the ADC16071/ADC16471 plastic package's pins, further reducing a possible source of performance degradation caused by loose fitting sockets.

Suggested power-supply bypassing consists of surfacemount 0.1  $\mu$ F monolithic ceramic and 10  $\mu$ F tantalum capacitors. When using the ADC16071/ADC16471 in the DIP package, the bypass capacitors' size is limited by the distance between the DIP package pins. When placed under an ADC16071/ADC16471 DIP package using a modified "socket" as in *Figure 14*, the 0.1  $\mu$ F SMD capacitor's physical size is limited to package number 0805. The 10  $\mu$ F SMD capacitor's physical size is limited to package number 1210.

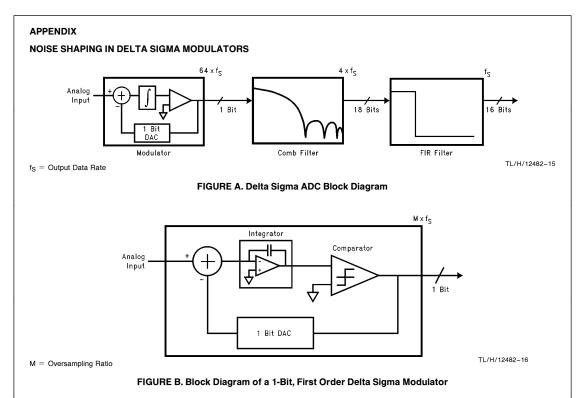

A delta-sigma converter consists of a  $\Delta\Sigma$  modulator that is essentially a high speed, low resolution ADC, and a DSP block that trades time for resolution (i.e.,  $64 \bullet f_S$  with 1-bit to  $f_S$  with 16 bits) and filters the output of the modulator. The DSP block typically consists of a comb filter, sometimes called a decimator, and an FIR filter that has a "brick wall" low-pass characteristic.

Figure B is a block diagram of a 1-bit, first order modulator. The difference ( $\Delta$ ) between the analog input and the comparator's previous output is integrated ( $\Sigma$ ) in such a manner that the *average* of the digital output is equal to the analog input.

The ones and zeros at the modulator's output represent the comparator's positive and negative full scale, respectively.

For example, a modulator output of: 1,0,1,1,1,0,0,0,1,0, represents an analog input halfway between positive and negative full scale (5 out of a possible 10 ones).

Because of the crude approximation made by the comparator of a  $\Delta\Sigma$  modulator (it is quantizing with only 1-bit of resolution), a large amount of quantization noise is introduced into the system. But because of the noise "shaping" characteristic that is inherent to the design of  $\Delta\Sigma$  modulators, much of the quantization noise introduced by the modulator's comparators is pushed beyond the frequency band of interest (f<sub>BB</sub>), where it may be filtered digitally.

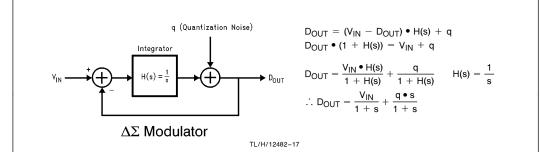

#### FIGURE C. Noise Shaping in Delta Sigma Modulator

If we make the approximation that the comparator of *Figure B* can be treated as the addition of quantization noise (q) that has a "white" spectral distribution (uniform energy at all frequencies) and uncorrelated to the analog input, then the substitution shown in the block diagram of *Figure C* may be made. From this block diagram, the output of the modulator may be equated to the difference between the quantized output,  $D_{OUT}$ , and the analog input,  $V_{IN}$ , times the transfer function of the integrator, H(s), plus the quantization noise, q. From the resulting transfer function noise, it can be shown that quantization noise is filtered through a high-pass filtered the the distribution of the modulation of the the distribution that quantization noise is filtered through a high-pass filtered the the distribution of the modulation of the the distribution of the the distribution of the the distribution the distribution the the distribution the distribution the distribution of the distribution of the distribution the distribution of the distribution of the distribution of the distribution the distribution the distribution on the distribution on the distribution of the distribution of the distribution on the distribution of the distribution of the distribution on the distribution of the distribution on the distribution of the distribution on the distribution of the distribution of the distribution of the distribution of the distribution on the distribution of the distribution distri

$$\left(\frac{\mathbf{q} \bullet \mathbf{s}}{\mathbf{s}+1}\right)$$

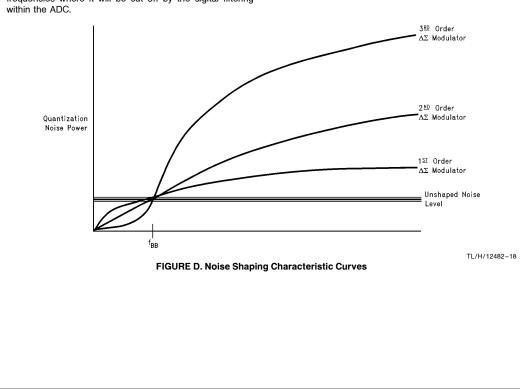

while the input signal passes unattenuated at low frequencies (f <  $f_{BB} << M \bullet f_S$ ). This high-pass function "shapes" the quantization noise out of the baseband,  $f_{BB}$  to higher frequencies where it will be cut off by the digital filtering within the ADC.

By increasing the order of a  $\Delta\Sigma$  modulator (adding more integrators to the modulator), the noise shaping effect is enhanced. *Figure D's* curves show how the flat quantization noise is "shaped" into first-, second-, and third-order modulator characteristics.

$\Delta\Sigma$  modulators further reduce the amount of quantization noise in the baseband by oversampling the input signal. The quantization noise is assumed to be spread out equally from DC up to the sample rate of the modulator. As the oversampling ratio is increased, so is the range over which the quantization noise is spread. The total noise does not decrease, but the density per frequency band does. With a first order modulator, the theoretical maximum signal-to-quantizationnoise ratio in the baseband can be shown to increase by 9 dB with each doubling of the oversampling ratio.

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| National Semiconductor<br>Corporation National Semiconductor<br>Europe   Trili West Bardin Road<br>Arlington, TX 76017<br>Tel: 1(800) 737-7018 Fax: (+49) 0-180-530 85 86<br>Email: cnjwg@tevm2.nsc.com   Fax: 1(800) 737-7018 Deutsch Tel: (+49) 0-180-532 78 32<br>Français Tel: (+49) 0-180-532 93 58<br>Italiano Tel: (+49) 0-180-532 93 58 | National Semiconductor<br>Hong Kong Ltd.<br>13th Floor, Straight Block,<br>Ocean Centre, 5 Canton Rd.<br>Tsimshatsui, Kowloon<br>Hong Kong<br>Tel: (852) 2737-1600<br>Fax: (852) 2737-1600 | National Semiconductor<br>Japan Ltd.<br>Tel: 81-043-299-2309<br>Fax: 81-043-299-2408 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

# **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

|  | Products               |                                 | Applications                  |                                   |

|--|------------------------|---------------------------------|-------------------------------|-----------------------------------|

|  | Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

|  | Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

|  | Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

|  | DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

|  | DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

|  | Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

|  | Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

|  | Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

|  | Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

|  | Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

|  | RFID                   | www.ti-rfid.com                 |                               |                                   |

|  | OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

|  | Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|  |                        | a O a Al a a m                  |                               |                                   |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated