# LMH0303,LMH0344,LMH0356

Literature Number: SNLA173

# 3G-SDI: 32 Loop Cascade Analysis

National Semiconductor Lab Report Nasser Mohammadi October 2008

## Abstract

A distribution amplifier (DA) is often used as a repeater in broadcast video applications to extend the reach of a link, most commonly 75 $\Omega$  coaxial cable. The data path in a DA consists of an SDI adaptive cable equalizer, SDI reclocker and SDI cable driver. In an operational system a video signal may be transmitted through multiple DAs or similar equipment, such as a video router, before reaching its final destination. The DA's primary function is to reconstruct signal integrity of the incoming attenuated signal back to its original state by opening the waveform eye (equalizer), cleaning high-frequency jitter (reclocker) and setting appropriate slew rate and signal amplitude (cable driver). Low frequency jitter, below the loop bandwidth of the reclocker's PLL, will be passed through. Adding several DAs in cascade will eventually result in accumulated low frequency jitter commonly referred to as jitter peaking. Some SDI reclockers and equalizers are more susceptible to jitter peaking than others. This report focuses on an experiment to determine the effects of cascading multiple DAs using National Semiconductor's LMH0344 SDI adaptive cable equalizer, LMH0356 SDI reclocker, and LMH0303 SDI cable driver.

In the experiment, eye patterns were collected, jitter tolerance graphs acquired using a PRBS10 and matrix pathological data patterns, and bit error rate testing (BERT) was conducted. This report examines in detail the experiments performed and results obtained.

### **Table of Contents**

| Test Setup                    | .2 |

|-------------------------------|----|

| Jitter Definitions            | .3 |

| SMPTE Jitter Requirements     | 4  |

| Waveform Eye Diagrams         | 5  |

| Jitter Tolerance Measurements | 8  |

| Bit Error Testing             | 10 |

| Conclusion                    | 11 |

#### **Test Setup**

Test Equipment List:

- Agilent N4903A J-BERT Bit Error Rate Tester

- Agilent DCA-J Scope

- HP 6023A DC Power Supply

#### Hardware List:

- Octal DA Evaluation Board (4)

- Pasternack  $50\Omega$  to  $75\Omega$  Adaptor PE7006

- Belden 1694A coaxial cable (100m lengths)

- Belden 1694A coaxial Cable (1m and 2m lengths)

#### Conditions:

- Room temperature

- 3.3V supply voltage

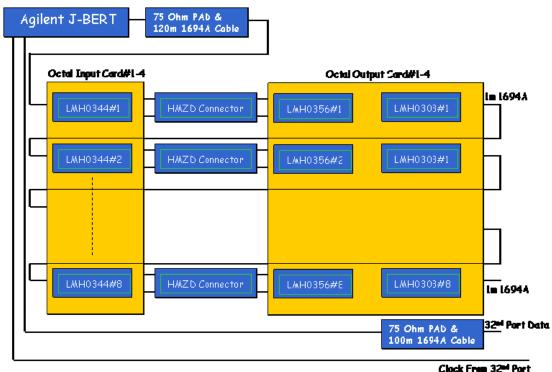

Figure 1 shows the experimental setup. After going through a  $50\Omega$  to  $75\Omega$  adaptor, the signal from the  $50\Omega$  data output of the Agilent J-BERT goes through 120m of Belden 1694A cable. In between each stage, 1m lengths of Belden 1694A cable connect consecutive DA ports. For the jitter tolerance test, the last stage data and the recovered clock are fed to the test data input of the Agilent J-BERT. A second  $50\Omega$  to  $75\Omega$  matching attenuator was used on the data output of the DA cascade. An automated test program developed at National Semiconductor was run to first align the clock and data and then record the jitter tolerance using a PRBS-10 data pattern.

CIUCK FINE J2-" I

FIGURE 1. Experimental Setup

#### **Jitter Definitions**

In digital communication, jitter is defined as time deviation from the ideal timing of the signal transition [1]. Any jitter that describes how much in time a clock edge varies can be given as a peak-to-peak number. Peak-to-peak jitter specifications are convenient when the jitter is deterministically characterizable. But as random jitter is probabilistic, it is difficult to say what the maximum jitter can possibly be [2]. In general jitter is divided into two categories: Random Jitter and Deterministic Jitter [2]:

Random jitter (RJ) is characterized by a Gaussian distribution and comes from physical sources such as thermal noise, shot noise, and wave scattering in fiber (i.e. mainly from Multimode Fiber). RJ is modeled as a Gaussian distribution and is used to predict peak-to-peak jitter as a function of bit error [2].

Deterministic jitter (DJ) is generally bounded and non-Gaussian. Duty Cycle Distortion (DCD), Periodic Jitter and Bounded Uncorrelated jitter all are components of Deterministic Jitter [3].

In Video applications, there is a potential for a long chain of regenerative repeaters. Signal regeneration is beneficial in extending the reach of the transmission media, preventing the accumulation of noise and distortion through the transmission media. However, the regenerative repeater itself contributes an accumulation of jitter which can become a critical problem if it is not properly controlled through the careful design of the timing recovery circuit. This accumulation of jitter will typically result in a limit on the number of repeaters of a given design which can be installed in the transmission path before the accumulated jitter becomes intolerable.

When considering the accumulation of jitter it is imperative to distinguish between the two basic types of jitter. In a long chain of repeaters deterministic jitter greatly dominates random jitter [2]. This is because the DJ component is the same in each repeater and therefore adds coherently. Effects of the jitter introduced by one repeater on the jitter introduced upstream will be slight as long as the total introduced jitter remains low and thus we can assume that the jitter in each repeater is additive [2].

Let's assume each repeater has an equivalent jitter transfer function. We should consider the following three cases [2]:

At frequencies where the jitter transfer function has gain, as the number of repeaters in cascade increases, the overall jitter gain could approach infinity. As such, the jitter peaking of the PLL will eventually limit the number of repeaters that can be placed in cascade.

For frequencies where the jitter transfer function has a magnitude much less than unity, meaning the input jitter is attenuated through the repeater, we can say there is not much jitter accumulation and the only significant jitter is that introduced in the last stage.

The third critical case is where the jitter transfer function is equal to unity (i.e. the input jitter is passed through). This will occur within the pass band of the jitter transfer function. As such N repeaters would result into N times the jitter amplitude and jitter increases in proportion to number of loops or cascade. In this case, the only way to limit the accumulated jitter is to reduce loop bandwidth.

#### **SMPTE Jitter Requirements**

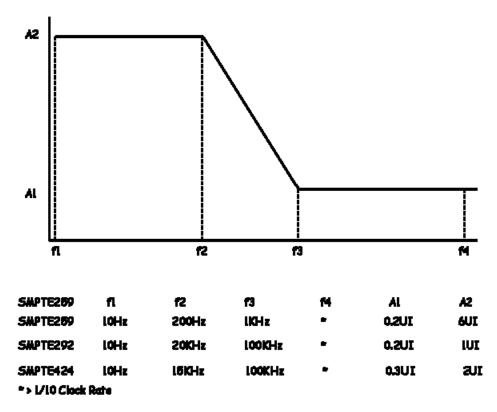

Random jitter is specified in the way it describes clock edge fluctuations. Accordingly, jitter is typically listed as an amount of one clock period, or an amount of one unit interval (UI). Should the edge of a clock jitter around over time 10 picoseconds (ps) within a 100ps clock period, then the jitter is 0.1 UI.

FIGURE 2 – Jitter Tolerance Specifications from SMPTE serial data transmission standards

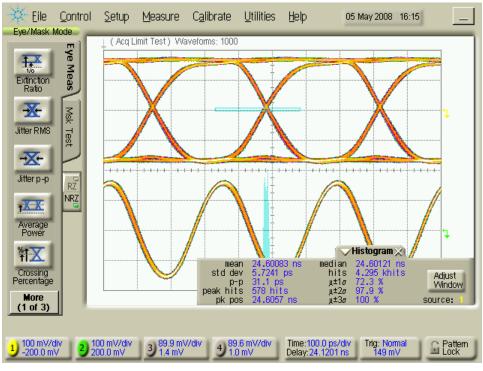

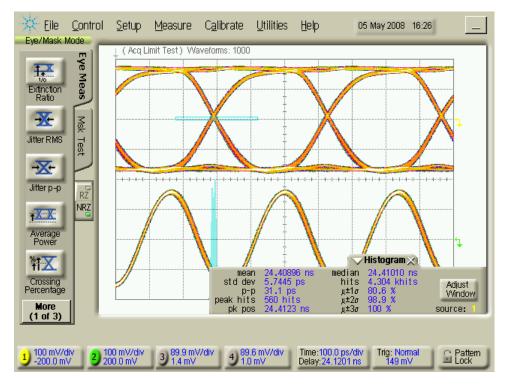

The eye diagrams from the first twelve cascaded loops are shown next. The output clock from the BERT was used as the trigger or clock source for the DCA-J scope. A PRBS10 data pattern was used.

| Figure Number | Number of DAs | Data Pattern |

|---------------|---------------|--------------|

| 3             | 1             | PRBS10       |

| 4             | 2             | PRBS10       |

| 5             | 3             | PRBS10       |

| 6             | 6             | PRBS10       |

| 7             | 12            | PRBS10       |

Table 1 – Eye Diagram Tests

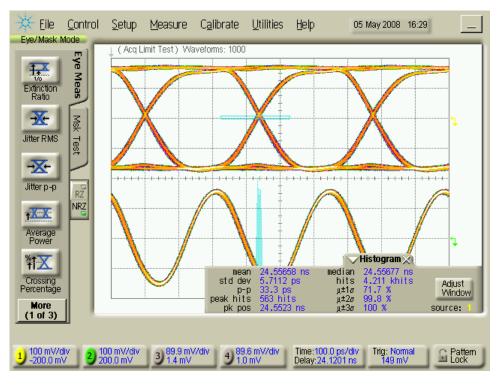

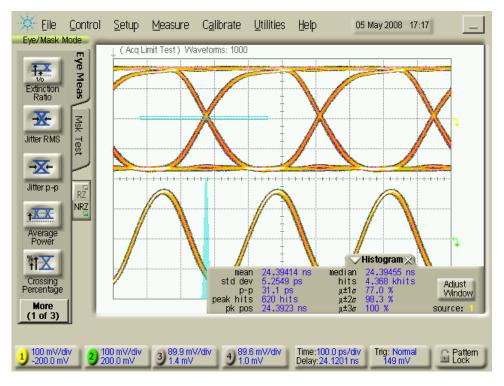

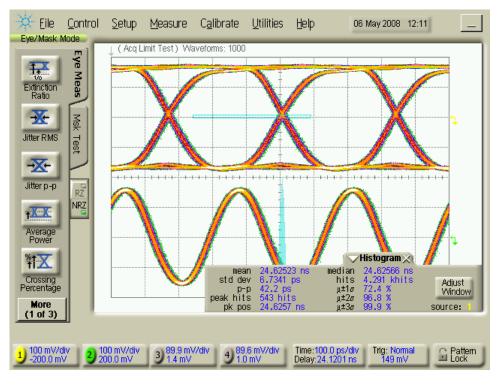

FIGURE 3. Eye Diagram after the first stage using a PRBS10 data pattern

FIGURE 4. Eye Diagram after the second stage using a PRBS10 data pattern

FIGURE 5. Eye Diagram after the third stage using a PRBS10 data pattern

FIGURE 6. Eye Diagram after the sixth stage using a PRBS10 data pattern

FIGURE 7. Eye Diagram after the twelfth stage using a PRBS10 data pattern

Based on these eye diagrams, the PRBS10 data pattern which, from a spectral standpoint, is very much like a color bar pattern, exhibits essentially the same jitter at every point in the cascade. Thus it is conceivable that using the PRBS10 or color bar pattern we could potentially have a much larger number of cascaded ports even than 32.

#### **Jitter Tolerance Measurements**

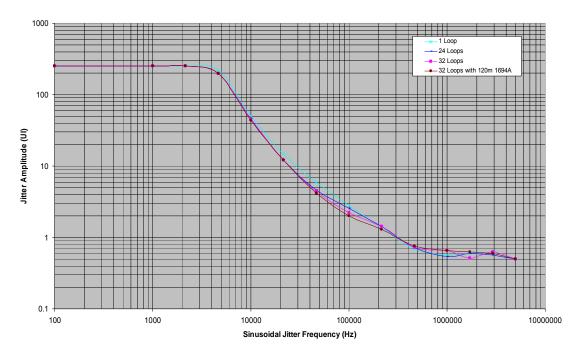

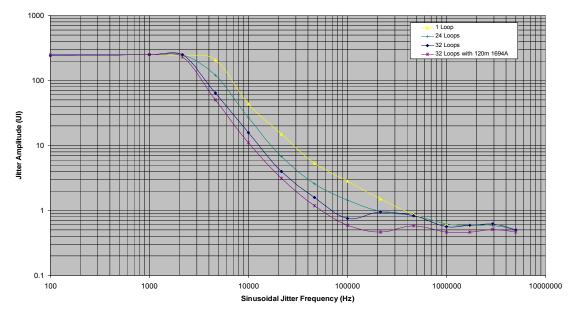

The number of loops used in the experiment was increased from 1 to 8, 16, to 24, and then to 32. For each cascade setup, the jitter tolerance was measured. Figures 8 and 9 show the jitter tolerance for a PRBS10 data pattern and the matrix pathological data pattern, respectively.

Figure 8. Jitter Transfer using PRBS10 data pattern

Figure 9. Jitter Transfer using Matrix Pathological data pattern

Inspection of jitter tolerance graphs shows that as the number of loops increase, the overall loop bandwidth is reduced. Even with a cascade of 32 DAs, a jitter tolerance at high jitter frequencies of 0.4 to 0.5UI is maintained. Further, the low frequency jitter tolerance is maintained at 250UI (the limit of the instrumentation). This suggests that a cascade of more than 32 loops may be achievable with reasonable performance.

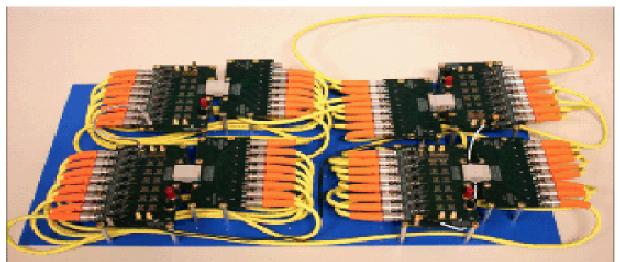

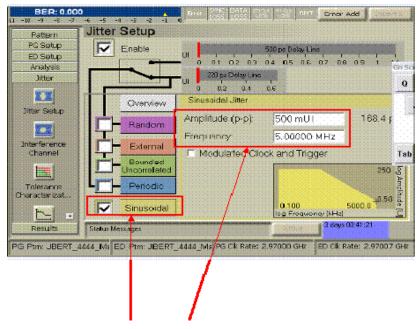

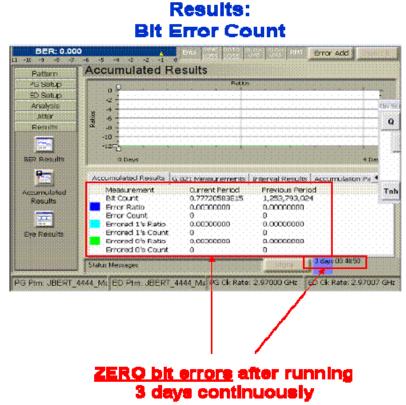

Using the 32-port cascade setup and an Agilent J-BERT, we ran data with 0.5 UI of injected sinusoidal jitter at 5 MHz through the cascade error-free for 3 consecutive days<sup>1</sup>. Note Figures 10, 11, and 12.

Figure 10. 32 Port Cascade Hardware Setup

<sup>&</sup>lt;sup>1</sup> BERT experiment was limited to three days due to equipment availability, no error was detected.

# **Jitter Setup**

#### Input: 0.5 UI of 5 MHz sinusoidal jitter

Figure 11. J-BERT Jitter Setup for 32 port reference clock cascade application

Figure 12. J-BERT Result for 32 port reference clock cascade application

### Conclusion

Using the setup described in this report, we were able to successfully pass stressful signals through 32 cascaded distribution amplifiers with zero bit errors demonstrating the robustness of National Semiconductor's SDI data path. We have conducted further experiments with a higher number of cascaded stages and have not yet found the fundamental limit of the system. Through the experiment, we demonstrate the low intrinsic output jitter of National's LMH0344 SDI cable equalizer and LMH0303 SDI cable driver. The LMH0356 reclocker shows very robust low-frequency jitter tolerance while at high-frequencies the low-pass jitter transfer function attenuates the input high-frequency jitter. Therefore, the system is able to pass matrix pathological and PRBS10 (similar to color bars) data patterns while exceeding SMPTE jitter tolerance/transfer requirements with significant margin. The Agilent J-BERT jitter measurements confirmed that the system can run error free with at least 32 DAs in cascade for extended periods of time.

A single 27 MHz crystal as a reference clock for all 32 reclockers in this experiment. Please refer to the Reference Clock Cascade Lab Report.

#### References

SMPTE Recommendation "Specification of Jitter in Bit-Serial Digital Systems" RP-184-2004 Revision of RP184-1996

Edward A. Lee & David G. Messerschmitt "Digital Communication" – Second Edition

National Semiconductor "LVDS Owner's Manual" - Fourth Edition, 2008

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated