## Electronic Design.

# **Comparing Power-Supply Architectures for a 12-bit ADC**

Powering any data converter, such as an analog-to-digital converter (ADC) or digital-to-analog converter (DAC), requires a clean, low-noise power supply. Traditionally, engineers used low-dropout (LDO) linear regulators because this topology introduces no switching noise onto the supply voltage. However, LDOs are the least-efficient power-supply type due to their linear operation.

#### Electronic Design Chris Glaser Thu, 2016-08-25 15:5

To overcome this, engineers added dc-dc step-down (buck) converters before the LDOs to increase the conversion efficiency. This architecture adds extra semiconductor devices and passive components, and increases the total power supply cost.

While noisier than LDOs, many modern dc-dc converters do have lowenough noise as to not decrease the data converter's performance. A dc-dc converter-only design, not using any LDOs, is shown to power a 12-bit ADC without losing any performance. The article compares its noise performance, efficiency, power loss, and cost against the other two power-supply architectures.

### **Powering the ADS5407**

Texas Instruments' ADS5407 is a 12-bit ADC used for applications such as test and measurement and data acquisition.<sup>1</sup> It requires a 3.3-V analog supply with 239 mA of current, as well as a 1.8-V supply with 418 mA of current for the analog, digital, and clock domains. Typical input voltage is 5 V in many industrial systems. These three voltages allow LDOs, step-down dc-dc converters, or both to be used to power this ADC.

### **The Linear-Regulator Approach**

Two LDOs are required to convert the 5-V input voltage to the 3.3- and 1.8-V voltages. The simplified efficiency of any LDO is VOUT/VIN. And the simplified power loss in any LDO is the voltage across the LDO multiplied by the current. Therefore, the 3.3-V LDO's efficiency is 66% with 406 mW of power loss, and the 1.8-V LDO's efficiency is 36% with 1.34 W of power loss. Overall, 47% efficiency with 1.746 W of total loss is achieved.

The LDOs provide acceptable noise performance for the ADC and serve as the baseline case for comparison. LDOs are usually the lowest-cost solution for a 12-bit data converter due to the low device cost, as well as low number and cost of passive components. Higher-resolution data converters typically require much-higher-performance LDOs, which are more expensive.

The low level of efficiency limits the run time for battery-powered equipment, while the total power loss poses thermal challenges in equipment with higher ambient temperatures or smaller sizes. However, the low cost enables low-end applications, which aren't concerned with efficiency or temperature rise, and applications that don't utilize the full capabilities of the ADC (and thus have lower power consumption).

#### The Linear-Regulator + Step-Down DC-DC Approach

Step-down dc-dc converters are added to increase efficiency, while LDOs are placed after them to filter out the switching noise created. Typically, 0.5 V of headroom above the output voltage is required at the LDO's input to provide sufficient noise rejection. Therefore, the voltage across each LDO is 0.5 V. Less headroom may be used, but then the noise performance may not be sufficient for the ADC. Assuming 85% efficiency for the 2.3-V dc-dc, 90% efficiency for the 3.8-V dc-dc, the combined efficiency is 72% and power loss is 599 mW.

Since LDOs are used after the dc-dc converters with sufficient voltage headroom, the noise performance is the same as the LDO case. This architecture is the most costly, because it requires the most power-supply devices and associated passive components. The added cost enables a decent overall efficiency for portable equipment with a manageable power loss.

#### The Step-Down DC-DC Approach

The most efficient solution is to use just dc-dc converters and no LDOs. Using the same 85% efficiency estimate for the 1.8-V rail and 90% efficiency for the 3.3-V rail, overall efficiency is 88%. This corresponds to a power loss of just 220 mW.

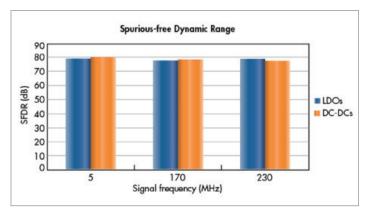

Modern, low-noise dc-dc converters can power data converters with no reduction in performance.<sup>2</sup> This requires specific testing, which adds a minimal amount of development time. **Figures 1** and **2** show the signal-to-noise ratio (SNR) and spurious-free dynamic range (SFDR) test results for the two LDO architectures, LDOs only and LDOs plus dc-dcs, and the dc-dc-only architecture. Three different input signal frequencies are tested in order to validate a wide range of ADS5407 operation.

The minimal difference in measured results shows that the tested dc-dc converters, the TPS62231 and TPS62237, don't reduce the ADC's performance. In these tests, the circuitry after the power supply, ferrite beads, and decoupling capacitors remained the same for each configuration. This portion of the test setup is a control variable in order to evaluate changing a single variable—the power-supply type.

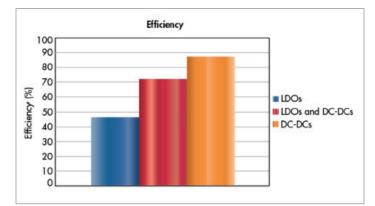

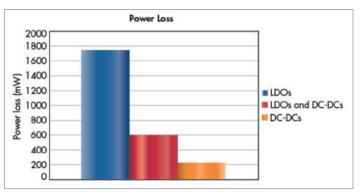

**Figures 3** and **4** compare the efficiency and power loss, respectively, of the three different architectures. Using only dc-dcs decreases the power loss by over 85%. This greatly reduces thermal challenges in the end equipment, which might otherwise require expensive heat sinks and so on.

Using just dc-dc converters is sometimes more expensive than using just LDOs, due to the generally higher device cost and additional passives that are required. This depends on the exact LDO and dc-dc required by the specific data converter.

However, the higher efficiency and corresponding lower power loss may save cost in other areas. For example, dc-dc converters generally don't require heat sinks and allow for a lower-power—and thus lower-cost—5-V input power supply to be used due to their reduced power consumption.

#### Conclusion

The table shows a comparison of the noise performance, efficiency, power loss, and cost for three power-supply architectures. When some basic testing is possible, the dc-dc-only architecture shows the best overall performance except in those designs that require absolute lowest cost.

| OVERALL COMPARISON OF DIFFERENT<br>POWER-SUPPLY ARCHITECTURES |                      |            |               |            |

|---------------------------------------------------------------|----------------------|------------|---------------|------------|

| Architecture                                                  | Noise<br>performance | Efficiency | Power<br>loss | Cost       |

| LDOs                                                          | Sufficient           | Poor       | High          | Low        |

| LDOs and<br>DC-DCs                                            | Sufficient           | Average    | Average       | High       |

| DC-DCs                                                        | Sufficient*          | Good       | Low           | Low-medium |

\*with basic testing

#### References

- 1. Product folders: ADS5407, TPS62231, TPS62237

- 2. TI Design: http://www.ti.com/tool/pmp9767

- 3. Source URL: http://electronicdesign.com/analog/

- comparing\_ power-supply-architectures-12-bit-adc

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated