# Application Note Designing a Simple and Low-Cost Flybuck Solution With the TPS62933F

Ruby Li, Harry Ma, Shuai Fan

#### ABSTRACT

In many applications, simple, low part-count, isolated power supplies working from an input voltage are needed. A popular solution to these requirements is an isolated buck power supply. This application report presents a simple and low-cost flybuck solution using the TPS62933F device. The basic operating principles of a flybuck converter are discussed, operating current and voltage waveforms are shown, and key design equations are derived. Lastly, a step-by-step design example is presented.

## **Table of Contents**

| 1 Introduction                                               | 2  |

|--------------------------------------------------------------|----|

| 2 Flybuck Converter Device Overview                          | 3  |

| 2.1 Operation Description                                    |    |

| 2.2 Equations for Maximum Output Current                     | 5  |

| 3 Design Flybuck With TPS62933F                              | 7  |

| 3.1 Primary Voltage and Turns Ratio                          | 7  |

| 3.1 Primary Voltage and Turns Ratio<br>3.2 Feedback Resistor | 8  |

| 3.3 Rectifier Diode                                          |    |

| 3.4 Primary Inductance                                       |    |

| 3.5 Primary Turns                                            |    |

| 3.6 Input and Output Capacitor                               | 9  |

| 3.7 Pre-Load                                                 | 10 |

| 3.8 Factors Affecting Voltage Regulation                     | 10 |

| 3.9 Avoiding Low-Side Sink Current Limit                     | 10 |

| 4 Experimental Results                                       |    |

| 5 Conclusion                                                 |    |

| 6 References                                                 | 13 |

### List of Figures

| Figure 2-1. Isolated Buck Converter With Two Outputs                                                                                               | 3 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 2-2. Simplified Isolated Buck Operating Waveforms                                                                                           |   |

| Figure 2-3. Current Waveforms Affected by Leakage Inductance                                                                                       |   |

| Figure 3-1. TPS62933F Two Output Isolated Buck Solution                                                                                            | 7 |

| Figure 4-1. Steady State Waveforms (V <sub>IN</sub> = 10 V, I <sub>OUT1</sub> = 1 A, I <sub>OUT2</sub> = 0.2 A, and I <sub>OUT3</sub> = 0.2 A)     | 1 |

| Figure 4-2. Steady State Waveforms (V <sub>IN</sub> = 10 V, I <sub>OUT1</sub> = 0 A, I <sub>OUT2</sub> = 0.2 A, and I <sub>OUT3</sub> = 0.2 A)     | 1 |

| Figure 4-3. Ripple Voltage Waveforms (V <sub>IN</sub> = 10 V, I <sub>OUT1</sub> = 1 A, I <sub>OUT2</sub> = 0.2 A, and I <sub>OUT3</sub> = 0.2 A)11 |   |

| Figure 4-4. Load Step Response 50 mA to 200 mA (V <sub>IN</sub> = 10 V, I <sub>OUT1</sub> = 0 A, and I <sub>OUT3</sub> = 0 A)                      |   |

|                                                                                                                                                    |   |

# List of Tables

Table 3-1. Design Parameters......7

#### Trademarks

All trademarks are the property of their respective owners.

# **1** Introduction

Isolated bias rails are common in many systems or subsystems, such as telecommunication equipment, medical equipment, and industrial factory automation. It is mandatory by safety standards to protect users from the hazardous voltage of a power supply, or the isolation is installed to break the ground loop interference for noise-sensitive applications.

In many cases, simple, low part count, isolated power supplies working from an input voltage are needed. This design solution is for when regulation may not be as important, but cost and board area are. A popular solution to these requirements is an isolated buck power supply, which is a synchronous buck converter, with the inductor replaced by a coupled inductor or flyback-type transformer. There is no need for an optocoupler or auxiliary winding because the secondary output closely tracks the primary voltage, resulting in smaller solution size and cost. The flybuck can support a simple, small, and cost effective power solution making it suitable as a flyback alternative.

This application report presents the basic operating principles of a flybuck converter, shows some typical operating current and voltage waveforms, and the key design equations are derived. The design example shows a step-by-step procedure for designing one nonisolated and two isolated outputs with the synchronous buck regulator TPS62933F.

The TPS62933F device is a 3.8-V to 30-V input voltage range, 3-A switching regulator, that has two integrated switching FETs and internal loop compensation. By integrating the MOSFETs and employing the SOT-5x3 package, the TPS63933F achieves high-power density and offers a small footprint on the PCB.

# 2 Flybuck Converter Device Overview

# 2.1 Operation Description

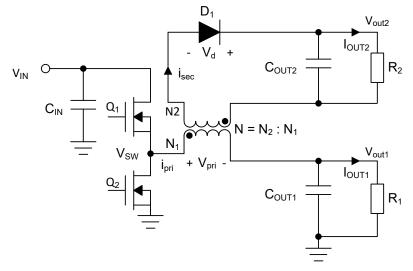

An isolated buck converter is a synchronous buck converter with the inductor replaced by a coupled inductor or flyback-type transformer. The primary output is still regulated as in a sync buck. The secondary output is generated by a diode rectifying the secondary winding. Figure 2-1 shows an isolated buck converter with two outputs.

Figure 2-1. Isolated Buck Converter With Two Outputs

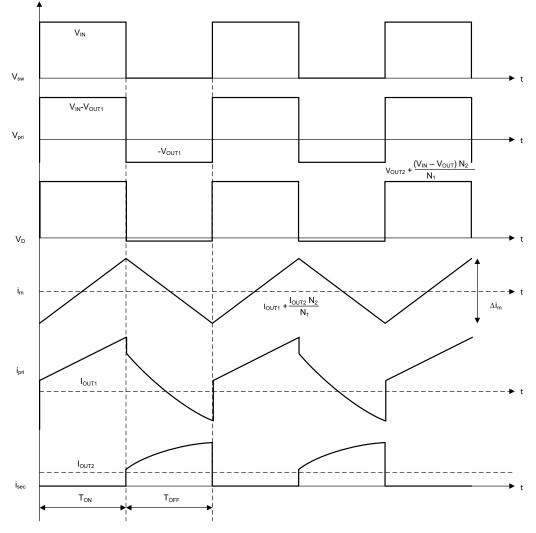

Figure 2-2 shows typical isolated buck operating waveforms, where  $V_{IN}$  is the input voltage of the converter,  $V_{OUT1}$  is the primary output voltage and  $V_{OUT2}$  is the secondary output voltage. During  $T_{ON}$ , the high-side MOSFET  $Q_1$  is on and the voltage stress of the low side FET  $Q_2$  is the input voltage,  $V_{IN}$ . The rectifier diode  $D_1$  is turned off, because the reflected voltage across the secondary winding is negative and its voltage stress is  $N \times (V_{IN}-V_{OUT1})+V_{OUT2}$ . The isolated output capacitor  $C_{OUT2}$  is discharged, supplying the load current, and the primary side behaves identical to a buck regulator. During  $T_{OFF}$ , the low-side MOSFET is on, and the reflected voltage on the secondary winding turns positive, forcing the diode forward conducting. The current in the primary winding splits into two parts: one part continues to supply the primary output (the magnetizing current,  $i_m$ , similar to a buck converter inductor current), the other part starts to flow to the secondary output. The secondary current waveform is determined by the load, leakage inductance, and output capacitance.

The primary output voltage is the same as a buck converter and is given by Equation 1:

$$V_{OUT1} = \frac{T_{on}}{T_{on} + T_{off}} V_{IN} = D \times V_{IN}$$

(1)

(2)

The secondary output voltage is given by Equation 2:

$$V_{OUT2} = V_{OUT1} \times \frac{N_2}{N_1} - V_F$$

where

- N<sub>1</sub> and N<sub>2</sub> are the turns of the primary winding and secondary winding

- V<sub>F</sub> is the forward voltage drop of the secondary rectifier diode

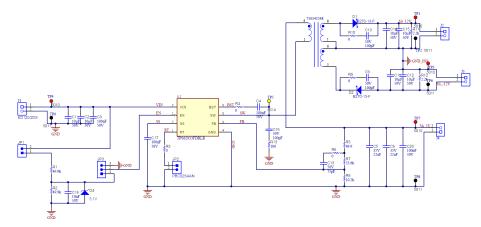

#### 2.2 Equations for Maximum Output Current

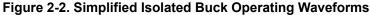

In practice, the transformer has more or less leakage inductance, which determines the ramp rate of the current in the secondary winding to charge the output capacitor. The simplified current waveforms in Figure 2-3 shows its relationship with leakage inductance. With lower leakage inductance, the current ramps up quickly to a high value, charging the output capacitor quickly. With the leakage inductance increasing, the current rises slowly, which can result in less energy being supplied to the output capacitance and less output voltage. The higher leakage inductance is the higher peak charging current obtained in secondary winding under the same output power rate. A high negative current is reflected in the primary winding at the same time. Leakage inductance along with duty cycle impacts not only the output voltage regulation, but also limits the output power resulting from the minimum low-side sink current limit. Therefore, the leakage inductance must be minimized and the maximum duty cycle must be chosen carefully to mitigate their impacts.

The winding and output currents have a relationship as shown in Equation 3 and Equation 4 on one cycle average basis.

$$I_{pri} = I_{OUT1} \tag{3}$$

$$I_{sec} = I_{OUT2} \tag{4}$$

The magnetizing current in the transformer that combines the two windings current is identical to a buck converter. Therefore, the magnetizing current ripple can be derived as in Equation 5.

$$\Delta i_m = \frac{(V_{IN} - V_{OUT1})}{L_{pri} \times f_{SW}} \frac{V_{OUT1}}{V_{IN}} = \frac{(V_{IN} - V_{OUT1})}{L_{pri}} \frac{D}{f_{SW}}$$

(5)

The positive primary winding and switching peak current during  $T_{ON}$  is given by Equation 6.

$$i_{SW_pospk} = i_{pri_pospk} = I_{OUT1} + \frac{N_2}{N_1} I_{OUT2} + \frac{\Delta i_m}{2}$$

(6)

Implementing the principle of charge balance to the secondary output capacitor, the secondary winding peak current can be approximately derived as Equation 7 for a higher leakage case.

Considering the worst case, the following equation is derived based on having higher leakage.

$$i_{sec\_pk} = \frac{2}{1-D} I_{OUT2} \tag{7}$$

Then the negative primary winding peak current can be derived as Equation 8.

$$i_{pri_negpk} = -\frac{N_2}{N_1} I_{sec_pk} + i_{pri_pospk} - \Delta i_m = -\frac{N_2}{N_1} I_{OUT2} \left(\frac{1+D}{1-D}\right) - \frac{\Delta i_m}{2} + I_{OUT1}$$

(8)

In fact, we must ensure that during  $T_{ON}$  the positive primary winding peak current does not exceed the minimum high-side source current limit,  $ILIM_{HS(min)}$ , and that during  $T_{OFF}$ , the negative primary winding peak current does not exceed the minimum low-side sink current limit,  $ILIM_{LSSOC(min)}$ . Therefore the positive and negative primary winding peak current should meet that of Equation 9.

$$\begin{cases} i_{pri_pospk} \leq I_{HS_LIMIT(min)} \\ |i_{pri_negpk}| \leq I_{LS_NOC(min)} \end{cases}$$

(9)

# 3 Design Flybuck With TPS62933F

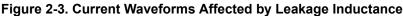

Figure 3-1 shows the design example with the typical flybuck circuit, using the synchronous buck regulator TPS62933F from TI.

Figure 3-1. TPS62933F Two Output Isolated Buck Solution

Table 3-1 lists the design specification.

| Design Parameter                                      | Example Value |

|-------------------------------------------------------|---------------|

| Input voltage range (V <sub>IN</sub> )                | 10 V to 24 V  |

| Primary output voltage (V <sub>OUT1</sub> )           | 5 V           |

| Positive isolated output voltage (V <sub>OUT2</sub> ) | 12 V          |

| Negative isolated output voltage (V <sub>OUT3</sub> ) | –12 V         |

| Primary load current (I <sub>OUT1</sub> )             | 1 A           |

| Positive isolated load current (I <sub>OUT2</sub> )   | 0.2 A         |

| Negative isolated load current (I <sub>OUT3</sub> )   | 0.2 A         |

| Switching frequency (f <sub>sw</sub> )                | 500 kHz       |

Table 3-1. Design Parameters

In this example, one primary output and two isolated outputs are obtained. We will begin with the buck converter component calculations and qualify the steps for the isolated configuration.

### 3.1 Primary Voltage and Turns Ratio

The primary-side, nonisolated output is set to 5 V for several considerations. First, the setting is below the minimum input voltage, 10 V, and the theoretical duty cycle varies from 20 to 50 percent at the full  $V_{IN}$  range, which is a balanced duty cycle during normal operation. Because the isolated outputs only have the off-time window to transfer energy, for a duty cycle that is too high, the secondary winding current will have a huge spike, which leads to poor regulation. Next, the turns ratio of the transformer is not too high to handle for the 5 V voltage level steps up to 12 V. Last, 5 V is one of the most common voltage levels in many applications. In this design, a transformer turns ratio ( $N_1$ : $N_2$ : $N_3$ ) of 1:2.5:2.5 is selected (see Equation 10 and Equation 11).

$$V_{OUT2} = V_{OUT1} \times \frac{N_2}{N_1} - V_F = 12V$$

(10)

$$|V_{OUT3}| = V_{OUT1} \times \frac{N_3}{N_1} - V_F = 12V$$

<sup>(11)</sup>

In this design, the  $V_F$  is targeted at 0.5 V.

# 3.2 Feedback Resistor

With the expected primary voltage set point at 5 V, and  $V_{FB}$  = 0.8 V (typical),  $V_{OUT1}$  is calculated to be as in Equation 12:

$$V_{out1} = V_{FB} \times \left(1 + \frac{R_7}{R_8}\right) \tag{12}$$

Start with 10 k $\Omega$  for the lower resistor divider, R8 = 10.2 k $\Omega$  (see Equation 13).

$$R_7 = \frac{V_{out1} - V_{FB}}{V_{FB}} R_8 \tag{13}$$

Next choose R7 = 53.6 k $\Omega$ . The 49.9- $\Omega$  resistor, R5, is provided as a convenient location to break the control loop for stability testing.

#### 3.3 Rectifier Diode

The rectifier diode  $D_1$  and  $D_2$ , must meet the blocking voltage and maximum current requirements (see Equation 14, Equation 15, Equation 16, and Equation 17).

$$V_{D1} = \left(V_{IN(max)} - V_{OUT1}\right) \times \frac{N_2}{N_1} + V_{OUT2} = 57.6V$$

(14)

$$V_{D2} = \left(V_{IN(max)} - V_{OUT1}\right) \times \frac{N_2}{N_1} + V_{OUT3} = 57.6V$$

(15)

$$i_{D1\_pk} = \frac{2}{1 - D_{max}} I_{OUT2} = 0.8A \tag{16}$$

$$i_{D2\_pk} = \frac{2}{1 - D_{max}} I_{OUT3} = 0.8A \tag{17}$$

Considering the voltage spike and keeping some margin, as well as the less forward voltage drop, a schottky diode of 70 V or higher reverse voltage rating is required. A 70-V, 2-A diode is selected for each rectifier diode in this design.

#### 3.4 Primary Inductance

8

For the TPS62933F, the minimum high-side current is 4.2A, and therefore the maximum magnetizing current ripple that can be tolerated is given by Equation 18:

$$\Delta i_m = 2 \times \left( I_{HS\_LIMIT(min)} - \left( I_{OUT1} + \frac{N_2}{N_1} I_{OUT2} + \frac{N_3}{N_1} I_{OUT3} \right) \right) = 4.48A$$

(18)

Using Equation 18 for the maximum magnetizing current ripple calculation, the minimum primary inductance is given by Equation 19.

$$L_{pri(min)} = \frac{\left(V_{IN(max)} - V_{OUT1}\right)}{\Delta i_m \times f_{SW}} \frac{V_{OUT1}}{V_{IN(max)}} = 1.77 \mu H$$

(19)

Too much high  $\Delta i_m$  may not be good for the efficiency and output voltage ripple. Assuming the 40% ripple of the rate output current of the device, then the optimized minimum primary inductance is given by Equation 20:

$$L_{pri} = \frac{\left(V_{IN}(max) - V_{OUT1}\right)}{0.4 \times 3 \times f_{SW}} \frac{V_{OUT1}}{V_{IN}(max)} = 6.6\mu H$$

(20)

We chose 6.8  $\mu$ H for the primary inductor, therefore  $\Delta i_{m(max)} = 1.16$  A. When all the outputs are with full loading, the positive and negative primary winding peak current is the highest and check the peak value not be over the high side FET over current limit (see Equation 21).

Designing a Simple and Low-Cost Flybuck Solution With the TPS62933F

$$i_{SW_pospk(max)} = I_{OUT1} + \frac{N_2}{N_1} I_{OUT2} + \frac{\Delta i_{m(max)}}{2} = 2.54A$$

(21)

The primary output side is not always loaded, and without the primary load, the negative current is more obvious. So consider the worst case,  $I_{OUT1} = 0$  A, and the secondary output side with full loading, check the negative primary winding peak current, as given by Equation 22.

$$i_{SW_negpk(max)} = -\left(\frac{N_2}{N_1}I_{OUT2} + \frac{N_3}{N_1}I_{OUT3}\right)\left(\frac{1+D}{1-D}\right) - \frac{\Delta i_m}{2} + I_{OUT1} = -1.2A$$

(22)

For the TPS62933F, the minimum high-side source current limit,  $ILIM_{HS(min)}$ , is 4.2 A and the minimum low-side sink current limit,  $ILIM_{LSSOC(min)}$ , is 1.2 A. Therefore the positive and negative primary winding peak current can meet the current requirements with the normal leakage of a transformer.

#### 3.5 Primary Turns

A coupled inductor or a flyback-type transformer is required for flybuck topology. Calculate the minimum primary turns for a flyback-type transformer using Equation 23.

$$N_1 = \frac{L_{pri} \times i_{SW\_pospk(max)}}{B_{max} \times A_e}$$

(23)

where

- B<sub>max</sub> is the maximum flux density.

- A<sub>e</sub> is the effective core area of the chosen transformer.

In this design, the 750345248 inductor from Würth is selected for the transformer. Würth offers many other flyback-type transformers and ready-made coupled inductors, in a variety of standard values, saturation currents, and sizes.

#### 3.6 Input and Output Capacitor

The TPS62933F device requires an input decoupling capacitor and, depending on the application, a bulk input capacitor. The typical recommended value for the decoupling capacitor is 10  $\mu$ F, and an additional 0.1- $\mu$ F capacitor from the VIN pin to ground is recommended to provide high frequency filtering.

The value of a ceramic capacitor varies significantly over temperature and the amount of DC bias applied to the capacitor. X5R and X7R ceramic dielectrics are recommended because they have a high capacitance-to-volume ratio and are fairly stable over temperature. The capacitor must also be selected with the DC bias taken into account. The effective capacitance value decreases as the DC bias increases. The capacitor voltage rating needs to be greater than the maximum input voltage. The input capacitor must be large enough to limit the input voltage ripple, see Equation 24.

$$C_{IN} \ge \frac{I_{OUT1} + \frac{N_2}{N_1} I_{OUT2} + \frac{N_3}{N_1} I_{OUT3}}{4 \times f_{SW} \times \Delta V_{IN}}$$

(24)

Choosing  $\Delta V_{IN}$ = 0.2 V gives a minimum of C<sub>IN</sub>= 4.9 µF. Considering derating, two standard value 10-µF, 50-V capacitors are selected for better input ripple performance. Another 0.1µF capacitor has been added as a bypass capacitor to clear high-frequency noise.

Energy is transferred from primary to secondary when the synchronous switch of the buck converter is on. The primary output capacitance is given by Equation 25.

$$C_{OUT1} \ge \frac{\left(\frac{N_2}{N_1}I_{OUT2} + \frac{N_3}{N_1}I_{OUT3}\right) \times D_{max}}{f_{SW} \times \Delta V_{OUT1}}$$

(25)

Choosing  $\Delta V_{OUT1}$ = 0.05 V gives a minimum of C<sub>OUT1</sub>= 19.2 µF. Considering derating, two standard value 22-µF, 35-V capacitors are selected.

The secondary output current is sourced by  $C_{OUT2}$  during  $T_{ON}$ . Ignoring the current transitions time in the secondary winding, the value of the secondary output capacitor can be calculated using Equation 26.

$$C_{OUT2} \ge \frac{I_{OUT2} D_{max}}{f_{SW} \times \Delta V_{OUT2}}$$

(26)

Choosing  $\Delta V_{OUT2}$ = 0.05 V gives a minimum of C<sub>OUT2</sub>= 4 µF. Considering derating, two standard value 10-µF, 50-V capacitors are selected, the same as the C<sub>OUT3</sub>.

### 3.7 Pre-Load

Pre-load is necessary to prevent V<sub>OUT2</sub> and V<sub>OUT3</sub> from going too high at light load. The required pre-load current is usually set around 5 mA as a starting point, but it should be adjusted based on the circuit test and application requirements. In this design, the pre-load resistor is selected as 2.2 k $\Omega$  for ±12-V outputs. Users can use a Zener diode instead of the pre-load resistor to increase the transfer efficiency.

### 3.8 Factors Affecting Voltage Regulation

A flybuck converter regulates the primary output voltage with a closed-loop controller. The isolated output is achieved by rectifying the secondary winding of the coupled inductor when the low side MOSFET is on. Therefore the isolated output regulation is passive, affected by the winding leakage inductance, winding resistances, diode drop, and low-side MOSFET, R<sub>DSON</sub>.

### 3.9 Avoiding Low-Side Sink Current Limit

In a flybuck application, the isolated output power rate may be limited by the low-side sink current limit. Therefore, users must select design parameters elaborately to promote the isolated power rate. The key factors affecting the negative primary winding peak current are  $D_{max}$ ,  $N_2/N_1$ ,  $N_3/N_1$ , and the output current. The following tips are for trying to keep the margin:

- Select a reasonable range of duty cycle. TI recommends a duty cycle ranging from 20% to 50% in most cases. Users can reduce D<sub>max</sub> by setting a lower primary voltage or increasing the minimum input voltage to increase the negative current margin.

- Minimize the leakage inductance. Leakage inductance is a crucial factor determining the ramp rate of the current in the secondary winding which charges the output capacitor. A nominal amount of leakage is within 1% of primary inductance.

- 3. Pick the correct turns ratio. A lower turns ratio (isolated side to non-isolated side) results in a lower reflected current in the primary winding.

- 4. Raise the non-isolated output power, which will reduce the negative winding peak current.

- 5. Reduce the isolated output power. This is the most direct way to lower the level of the negative current.

# **4 Experimental Results**

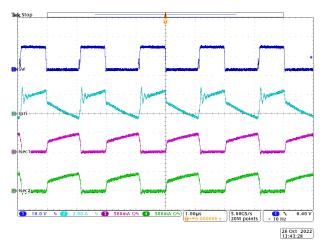

Steady State Waveforms ( $V_{IN}$  = 10 V,  $I_{OUT1}$  = 1 A,  $I_{OUT2}$  = 0.2 A, and  $I_{OUT3}$  = 0.2 A) through x show the experimental test results of Figure 3-1.

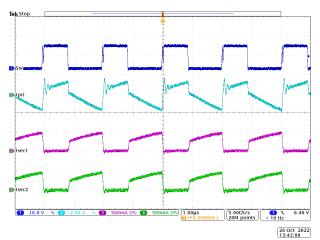

Figure 4-1. Steady State Waveforms ( $V_{IN}$  = 10 V, I<sub>OUT1</sub> = 1 A, I<sub>OUT2</sub> = 0.2 A, and I<sub>OUT3</sub> = 0.2 A)

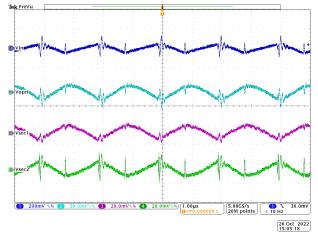

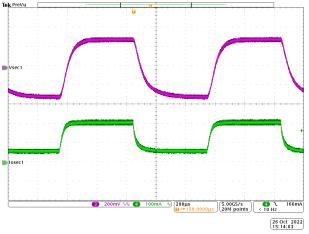

Figure 4-3. Ripple Voltage Waveforms (V<sub>IN</sub> = 10 V,  $I_{OUT1} = 1 \text{ A}$ ,  $I_{OUT2} = 0.2 \text{ A}$ , and  $I_{OUT3} = 0.2 \text{ A}$ )

Figure 4-2. Steady State Waveforms ( $V_{IN}$  = 10 V, I<sub>OUT1</sub> = 0 A, I<sub>OUT2</sub> = 0.2 A, and I<sub>OUT3</sub> = 0.2 A)

Figure 4-4. Load Step Response 50 mA to 200 mA ( $V_{IN}$  = 10 V,  $I_{OUT1}$  = 0 A, and  $I_{OUT3}$  = 0 A)

# **5** Conclusion

This application note presented the operating principles of a flybuck converter, showed typical operating current and voltage waveforms, and provided a detailed, step-by-step design example which explained how to select the external components. Data and waveforms tested based on the example design show that the flybuck can support a simple, small, and cost effective power solution, making it suitable as a flyback alternative, and the TPS62933F makes the advantage more obvious.

# 6 References

- Texas Instruments, TPS6293x 3.8-V to 30-V, 2-A, 3-A Synchronous Buck Converters in a SOT583 Package, data sheet

- Texas Instruments, Designing an Isolated Buck (Flybuck) Converter, application report

- Texas Instruments, Design a Flybuck Solution With Optocoupler to Improve Regulation Performance Create an Inverting Power Supply, application note

- Texas Instruments, Creating a Split-Rail Power Supply With a Wide Input Voltage Buck Regulator, application note

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated