# How to overcome negative voltage transients on low-side gate drivers' inputs

### Mamadou Diallo, High Power Drivers

Switch-Mode Power Supplies (SMPS) and Merchant DC-DC converter applications often require high current drive and hard switching to drive large loads. This hard switching of the power FETs in combination with layout constraints often lead to noise in the system. This noise appears as ground bounce and ringing at the driver's input/output terminals as the power ground and controller ground are connected. Most gate drivers are equipped to handle short negative pulses at the output stage through the internal FET's body diodes in the output stage. It is necessary to take precautions to prevent the overshoot and undershoot from damaging the driver's inputs.

## Causes of Negative Voltages at the Inputs of Gate Driver

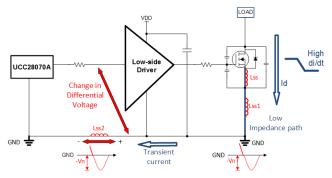

Low-side drivers are used between the controller and the power MOSFETs to help minimize switching losses in the PFC stage. Achieving this requires high drive current during hard switching of the power FET to guickly pass through the Miller plateau region. Figure 1 shows a simplified schematic of a low-side gate drive. During the switching transition of the MOSFET, there is a pulse of high di/dt generated by guick turn-on/off of the MOSFET. This fast changing slew rate coupled with the parasitic inductance from the high current loop generates a negative voltage spike that can be estimated using the equation:  $V_n =$ L<sub>ss</sub>\* di/dt. L<sub>ss</sub> represents the parasitic inductance of the internal bond wires of the power MOSFET and the PCB trace inductance in the return ground loop and can range anywhere from a few nanoHenries (nH) to more than 10 nH depending on layout and device package.

From this equation, it is obvious that this negative voltage is proportional to the parasitic inductance in the circuit (influenced by the PCB trace length and width) and the change in current of the power switch. In a typical low-side gate drive circuit, the controller and the power stage share the same DC ground reference, but some AC parasitics exist when the controller is some distance away from the driver. The high di/dt from the MOSFET's source flows through the low impedance ground path shown on Figure 1 and causes a negative  $V_n$  voltage on the power stage ground. This can corrupt the gate driver input signal by changing the differential voltage between input pins and the driver's ground reference pin, which leads to a

## Texas Instruments

false turn-on of the driver and potentially damage to the power FET. The transient currents from the high di/dt switching coupled with the trace inductance  $L_{ss2}$  on the controller ground path also create a voltage that can damage the controller.

Figure 1. Simplified Schematic of a Low-side Gate Drive Using UCC27511A

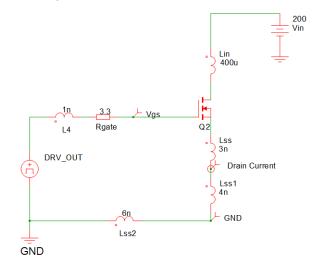

Figure 2 shows a simulation of a simplified power stage in a low-side gate drive where DRV\_OUT represents the driver's output and  $L_{ss}$  and  $L_{ss1}$  represent the previously described internal parasitic source inductance of the power FET and the parasitic inductance from the PCB trace length of the ground return loop.

How to overcome negative voltage transients on low-side gate drivers' inputs Mamadou Diallo, High Power Drivers

Copyright © 2019, Texas Instruments Incorporated

1

www.ti.com

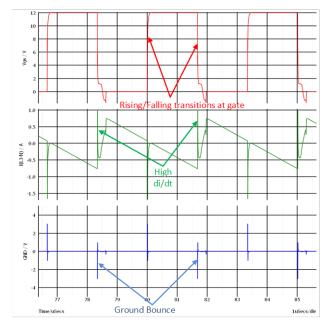

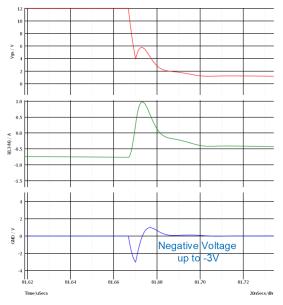

Figure 3 and Figure 4 show the simulation results when switching at 300 kHz with a gate voltage  $V_{GS}$  = 12 V. We can observe the ground shifting during the rising and falling transitions of the gate voltage  $V_{GS}$ . The high frequency switching causes rapid change in drain current di/dt which coupled with the parasitic inductances on the source of the MOSFET L<sub>ss</sub> and L<sub>ss1</sub>, cause the negative transients on the circuit's ground (blue waveform) to reach up to -3 V. This can damage the driver's input stage if an appropriate driver is not selected to handle such transients.

**Figure 3. Simulation Results**

Figure 4. Zoomed-in Simulation Results

#### **Design Guidelines**

The simplest method to prevent these negative transients on the driver's input stage is to slow down the switching transitions at the gate. Series gate resistors help limit the rise and fall times of the power FET while reducing the power dissipation across the gate driver IC. An optimized layout helps minimize the effects of the parasitic inductance  $L_{ss}$  contributing to the negative transients on the input stage. In general, it is recommended to place the driver very close to the power FETs to reduce PCB trace length throughout the power stage and to use bypass capacitors placed very close to the driver's V\_DD pin. A small input RC filter ranging between 0  $\Omega$  to 100  $\Omega$  and 10 pF to 100 pF helps to minimize differential input voltage changes at the driver, but only if the capacitor is placed very close to the driver's input pins. But in SMPS applications where fast switching and large input transients are unavoidable, it is essential to select a robust driver capable of tolerating negative transients at its inputs. UCC27511A is part of TI's portfolio of low-side drivers capable of handling negative voltage transients up to -5 V at its inputs. This device gives designers sufficient margins for driving large loads and improve the overall system efficiency and reliability.

In summary, this tech note discusses negative transients on gate drivers' inputs common in SMPS applications and their impact in the gate drive. It is important for designers to consider these transients when driving large loads and selecting a robust driver in order to improve reliability in the system.

### **Related Documentation**

Find more information on low-side gate drivers at ti.com/gatedrivers

UCC27511A Product Folder UCC27524A Product Folder UCC28070A Product Folder UCC27517A Product Folder

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated