# TVP5150AM1 Powerdown Mode

Digital Video and Imaging

#### 1 Lowest Power Consumption in TVP5150AM1 Powerdown Mode

Mobile applications such as cell phones and PDAs have low power consumption as a key requirement. The TVP5150AM1 offers very low power consumption in normal operation. When the TVP5150AM1 is not in use, the power consumption must also be very low. This application report outlines how to correctly implement the powerdown mode to ensure the lowest power consumption. All of the following pins must either (1) be enabled as outputs, or (2) be disabled and externally driven low or high, or externally pulled low or high through a resistor. The pin numbers are for the 32-terminal TQFP (PBS) package.

| Name             |  |  |

|------------------|--|--|

| YOUT[7:0]        |  |  |

| SCL              |  |  |

| SDA              |  |  |

| FID/GLCO         |  |  |

| VSYNC/PALI       |  |  |

| HSYNC            |  |  |

| AVID             |  |  |

| INTREQ/GPCL/VBLK |  |  |

|                  |  |  |

If these I/O pins on the TVP5150AM1 are left in a floating state (0.4 V < I/O voltage < 2.9 V) during powerdown mode, the I/O buffers leak current. If not enabled as outputs or driven externally, each pin should be either pulled up or down through a 10-k $\Omega$  (or similar) resistor. Pin YOUT7/I2CSEL is always pulled high or low for the I<sup>2</sup>C address select, so the YCrCb output must always be disabled (bit 3 of register 0x03 set to 0) in powerdown mode and pins YOUT[6:0] driven or pulled high/low. The clock pin should always be enabled.

To prevent current leakage in powerdown mode, one of the following three options must be followed:

- 1. Do not use powerdown function (pin 28); instead, power off the TVP5150AM1 when not in use. If the system is using a RAM patch code, the system must redownload the patch code to the TVP5150AM1 each time the TVP5150AM1 is powered back on.

- 2. Use hardware powerdown function (pin 28) with the I/O control and clock pins enabled. Enabling the outputs prevents them from floating, forcing them to 0 V or 3.3 V. The data outputs must be disabled and driven or pulled high/low. See Section 2.

- 3. Use hardware powerdown function (pin 28) with the I/O data and control pins disabled. If the I/O pins are disabled in powerdown mode, then it is required to use external pulldown/pullup resistors for these floating pins, or to drive them high or low with another device in the customer system. The clock pin is enabled. The SDA and SCL pins should already be pulled high for I<sup>2</sup>C. See Section 3.

- **NOTE:** Pin 23 is always enabled as an output in GLCO mode (default) and cannot be disabled. Because this pin is enabled as an output, it should not be pulled down or driven externally as recommended for the other I/O pins.

#### 2 Procedure 1: Using the Powerdown Mode with Control/Clock Outputs Enabled and Data Outputs Disabled

#### System Requirements for This Example

The following procedure ensures that the PCLK/SCLK, HSYNC, VSYNC/PALI, AVID, FID/GLCO, and INTREQ/GPCL/VBLK pins are enabled as outputs, and that the Y[7:0] pins are disabled, by setting register 0x0F to 0x0A and register 0x03 to 0x25. Enabling the control outputs prevents them from floating, forcing them to 0 V or 3.3 V. The clock is enabled and forced to a low state. These pins should not be pulled low/high through a resistor or driven low/high by another device in the system. The YOUT[6:0] pins should be pulled low/high through a resistor or driven low/high by another device in the system. YOUT7 should already be pulled high or low for the I<sup>2</sup>C address select.

If the requirements above are met, powerdown mode is correctly initiated by the following procedure.

#### **To Enter Powerdown Mode**

- Write the following values to the TVP5150AM1 internal registers. This I<sup>2</sup>C write has double the normal amount of wait time, which must be accounted for.

- 1. Write 0x51 to I2C\_0x21 // Unlock password for register write

- 2. Write 0x50 to I2C\_0x22 // Unlock password for register write

- 3. Write 0xFF to I2C\_0x23 // Unlock password for register write

- 4. Write 0x04 to I2C\_0x24 // Unlock password for register write

- 5. Write 0xC8 to I2C\_0x21 // Bypass PLL to set clock low

- 6. Write 0xC8 to I2C\_0x22 // Bypass PLL to set clock low

- 7. Write 0x17 to I2C\_0x23 // Bypass PLL to set clock low

- Write 0x06 to I2C\_0x24 // Bypass PLL to set clock low

- 9. Write 0x0A to I2C 0x0F // Enable GLCO and GPCL pins

- 10. Write 0x25 to I2C\_0x03 // Enable control pins and clock; disable data outputs

- 2. Wait at least 250µs. (See detailed timing requirements below.)

- 3. Assert powerdown pin by setting a low level to pin 28. The device powers down.

#### To Exit Powerdown Mode

- 1. De-assert the powerdown pin by setting a high level to pin 28. The device powers up.

- 2. Wait for the external crystal to be stable (~20 ms).

- 3. Assert the reset pin by setting a low level to pin 8.

- 4. Wait at least 2 ms.

8.

- 5. Negate the reset pin by setting a high level to pin 8.

- 6. Write 0x05 to I2C\_0x10 for activating patch code.

- 7. Write preferred settings to  $I^2C$ .

- **NOTE:** If the patch code is downloaded before entering powerdown mode, it remains in the internal program memory, while all settings to I<sup>2</sup>C registers are negated by reset operation. Therefore, downloading the patch code is not required after exiting the powerdown mode.

www.ti.com

#### 3 Procedure 2: Using the Powerdown Mode With Outputs Disabled

#### System Requirements for This Example

- The following procedure assumes that the YOUT[7:0], HSYNC, VSYNC/PALI, AVID, and INTREQ/GPCL/VBLK pins are disabled as outputs by setting register 0x03 to 0x01. It is required to use external pulldowns for these floating output control and YOUT[6:0] pins, or to drive them high or low with another device in the customer system.

- The clock, PCLK/SCLK, is enabled and forced to a low state, so it should not be pulled or driven high/low.

- The FID/GLCO pin (pin 23) is always enabled as an output in GLCO mode (default) and can not be disabled. Since this pin is enabled as an output, it should not be pulled down or driven externally as recommended for the other I/O pins.

If the requirements above are met, the powerdown mode is correctly initiated by the following procedure.

#### To Enter Powerdown Mode

1. Write the following values to the TVP5150AM1 internal registers.

This I<sup>2</sup>C write has double the normal amount of wait time, which needs to be accounted for.

- 1. Write 0x51 to I2C\_0x21 // Unlock password for register write

- 2. Write 0x50 to I2C\_0x22 // Unlock password for register write

- 3. Write 0xFF to I2C\_0x23 // Unlock password for register write

- 4. Write 0x04 to I2C\_0x24 // Unlock password for register write

- 5. Write 0xC8 to I2C\_0x21 // Bypass PLL to set clock low

- 6. Write 0xC8 to I2C\_0x22 // Bypass PLL to set clock low

- 7. Write 0x17 to I2C\_0x23 // Bypass PLL to set clock low

- 8. Write 0x06 to I2C\_0x24 // Bypass PLL to set clock low

- 9. Write 0x01 to I2C\_0x03 // Enable clock; disable data outputs and control pins

- 2. Wait at least 250µs. (See detailed timing requirements below.)

- 3. Assert powerdown pin by setting a low level to pin 28. The device powers down.

#### To Exit Powerdown Mode

- 1. De-assert the powerdown pin by setting a high level to pin 28. The device powers up.

- 2. Wait for the external crystal to be stable (~20 ms).

- 3. Assert the reset pin by setting a low level to pin 8.

- 4. Wait at least 2 ms.

- 5. Negate the reset pin by setting a high level to pin 8.

- 6. Write 0x05 to I2C\_0x10 for activating patch code.

- 7. Write preferred settings to  $I^2C$ .

- **NOTE:** If the patch code is downloaded before entering powerdown mode, it remains in the internal program memory, while all settings to I<sup>2</sup>C registers are negated by reset operation. Therefore, downloading the patch code is not required after exiting the powerdown mode.

Timing Requirements

www.ti.com

### 4 Timing Requirements

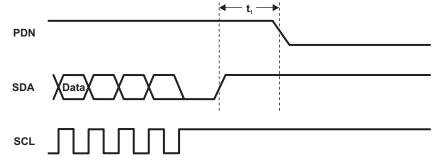

**Timing Requirement to Enter Powerdown Mode**

## Figure 1. Powerdown Timing

| Table 1. Powerdown Timing | Table | 1. | Powerdown | Timing |

|---------------------------|-------|----|-----------|--------|

|---------------------------|-------|----|-----------|--------|

| [ | PARAMETER                                           | MIN | TYP | MAX | UNIT |

|---|-----------------------------------------------------|-----|-----|-----|------|

|   | t <sub>1</sub> Delay before entering powerdown mode | 250 |     |     | μs   |

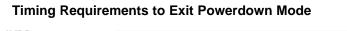

# Figure 2. Power-On Reset Timing

#### Table 2. Power-On Reset Timing

|                | PARAMETER                                                  | MIN | TYP | MAX | UNIT |

|----------------|------------------------------------------------------------|-----|-----|-----|------|

| t <sub>1</sub> | Delay time between power supplies active and reset         | 20  |     |     | ms   |

| t <sub>2</sub> | RESETB pulse duration                                      | 500 |     |     | ns   |

| t <sub>3</sub> | Delay time between end of reset to I <sup>2</sup> C active | 200 |     |     | μs   |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                     |                                   |

|-----------------------------|------------------------|----------------------------------|-----------------------------------|

| Audio                       | www.ti.com/audio       | Communications and Telecom       | www.ti.com/communications         |

| Amplifiers                  | amplifier.ti.com       | Computers and Peripherals        | www.ti.com/computers              |

| Data Converters             | dataconverter.ti.com   | Consumer Electronics             | www.ti.com/consumer-apps          |

| DLP® Products               | www.dlp.com            | Energy and Lighting              | www.ti.com/energy                 |

| DSP                         | dsp.ti.com             | Industrial                       | www.ti.com/industrial             |

| Clocks and Timers           | www.ti.com/clocks      | Medical                          | www.ti.com/medical                |

| Interface                   | interface.ti.com       | Security                         | www.ti.com/security               |

| Logic                       | logic.ti.com           | Space, Avionics and Defense      | www.ti.com/space-avionics-defense |

| Power Mgmt                  | power.ti.com           | Transportation and<br>Automotive | www.ti.com/automotive             |

| Microcontrollers            | microcontroller.ti.com | Video and Imaging                | www.ti.com/video                  |

| RFID                        | www.ti-rfid.com        | Wireless                         | www.ti.com/wireless-apps          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        |                                  |                                   |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated