# Code Porting From MSP430FR2000 to MSP430FR2311 MCUs

Ryan Meredith

MSP430 Applications

# ABSTRACT

This guide is intended to help developers who are interested in testing code written for the MSP430FR2000 MCU by loading it onto the MSP430FR2311 MCU. Running the code on the MSP430FR2311 LaunchPad<sup>™</sup> Development Kit may help to reduce test costs, because the LaunchPad development kit with built-in eZ-FET emulation is less expensive than purchasing the MSP-TS430PW20 Target Development Board and MSP-FET Flash Emulation Tool.

Key differences between the two MCUs are outlined in this guide. These differences may require a change in code when porting from the MSP430FR2000 MCU to the MSP430FR2311 MCU.

#### Contents

| 1 | GPIO N  | Aultiplexing                        | 2 |

|---|---------|-------------------------------------|---|

|   |         | eUSCI_A0 UART and SPI Communication |   |

|   | 1.2     | Timer0_B3                           | 3 |

|   | 1.3     | Comparator                          | 6 |

| 2 | Porting | from MSP430FR2311 to MSP430FR2000   | 7 |

# List of Figures

| 1 | UART and SPI Signals | 2 |

|---|----------------------|---|

| 2 | Timer0_B3 Signals    | 3 |

| 3 | Comparator Signals   | 6 |

# List of Tables

| 1 | Comparison of MSP430FR2311 and MSP430FR2000 Features   | 7 |

|---|--------------------------------------------------------|---|

| 2 | MSP430FR2311 Peripherals Not Available on MSP430FR2000 | 7 |

# **Trademarks**

LaunchPad, MSP430 are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

# 1 GPIO Multiplexing

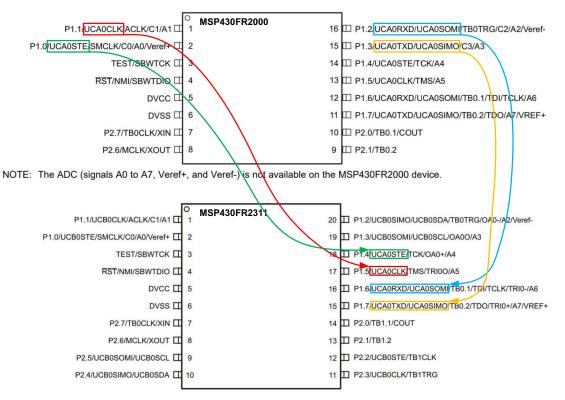

# 1.1 eUSCI\_A0 UART and SPI Communication

If the MSP430FR2000 code configures P1.0, P1.1, P1.2, or P1.3 for UART or SPI communication, the code must be changed to instead use P1.4, P1.5, P1.6, or P1.7, respectively (see Figure 1). This is achieved by removing SYSCFG3 code and changing the selection bits.

| Figure | 1. | UART | and | SPI | Signals |

|--------|----|------|-----|-----|---------|

|        |    |      |     |     |         |

| MSP430FR2000                                       |               | MSP430FR2311                         |

|----------------------------------------------------|---------------|--------------------------------------|

| All Serial Communication<br>SYSCFG3  = USCIARMP_1; | $\rightarrow$ | <pre>//SYSCFG3  = USCIARMP_1;</pre>  |

| UART<br>P1SELO  = BIT2   BIT3;                     | $\rightarrow$ | P1SEL0  = BIT6   BIT7;               |

| 3-Wire SPI<br>P1SEL0  = BIT1   BIT2   BIT3;        | $\rightarrow$ | P1SELO  = BIT5   BIT6   BIT7;        |

| 4-Wire SPI<br>P1SEL0  = BIT0   BIT1   BIT2   BIT3; | $\rightarrow$ | P1SELO  = BIT4   BIT5   BIT6   BIT7; |

See Chapter 21 and Chapter 22 of the MSP430FR4xx and MSP430FR2xx Family User's Guide for more details about the Enhanced Universal Serial Communication Interface (eUSCI) UART and SPI modes.

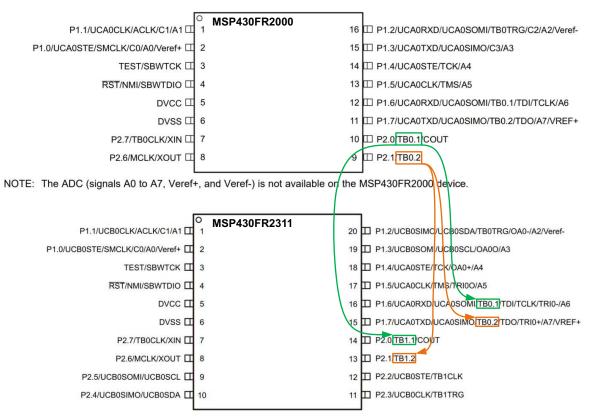

# 1.2 Timer0\_B3

If the MSP430FR2000 code sets Timer0\_B3 to use the capture input functionality on P2.0 or P2.1 (CCIS in TB0CCTL0 is set to 00b or 01b and TBRMP in SYSCFG3 is set to 1), the input pins must be changed to P1.6 or P1.7.

Additionally, if the MSP430FR2000 code sets Timer0\_B3 to output a PWM on P2.0 or P2.1 (P2.0 or P2.1 set to output and P2SEL set to 01b), the outputs must be changed to P1.6 or P1.7.

Alternatively, to keep P2.0 and P2.1 as GPIOs when using the MSP430FR2311, the code can be changed to use Timer1\_B3 instead of Timer0\_B3 (see Figure 2). This involves changing the register assignments from those for Timer0\_B3 to Timer1\_B3. In most cases, it is sufficient to perform a find and replace search of "TB0" to "TB1" and to update the interrupt service routine, if present.

Figure 2. Timer0\_B3 Signals

#### **GPIO** Multiplexing

TEXAS **NSTRUMENTS**

www.ti.com

The following comparison summarizes how to update the code to change from using P2.0 and P2.1 to P1.6 and P1.7.

#### MSP430FR2000

# MSP430FR2311

# P2.0 set to TB0.CCI1A

SYSCFG3 |= TBRMP 1; TBOCCTLO |= CCIS\_O; P2DIR &= ~BITO → TBOCCTLO |= CCIS\_O; P1DIR &= ~BIT6 P2SELO |= BITO;

PISEL1 |= BIT6;

P1.6 set to TB0.CCI1A

//SYSCFG3 |= TBRMP 1;

SYSCFG3 |= TBRMP\_1; TBOCCTLO |= CCIS\_1; → TBOCCTLO |= CCIS\_1; P2DIR &= ~BIT1 → P1DIR &= ~BIT7 P2DIR &= ~BIT1 P2SEL0 |= BIT1;

P2.1 set to TB0.CCI2A

#### P2.0 set to TB0.1

P2DIR |= BIT0; P2SELO |= BITO;

### P2.1 set to TB0.2

| P2DIR  | = BIT1; |

|--------|---------|

| P2SEL0 | = BIT1; |

P1.7 set to TB0.CCl2A

//SYSCFG3 |= TBRMP\_1; P1SEL1 |= BIT7;

#### P1.6 set to TB0.1

P1DIR |= BIT6; → PISEL1 |= BIT6;

## P1.7 set to TB0.2

P1DIR |= BIT7;  $\rightarrow$ P1SEL1 |= BIT7;

TEXAS

```

The following comparison summarizes how to update the code to change from using Timer0_B3 to Timer1_B3.

```

$\rightarrow$

#### MSP430FR2000

**NSTRUMENTS**

#### P2.0 set to TB0.CCI1A

SYSCFG3 |= TBRMP\_1; TBOCCTL0 |= CCIS\_0; P2DIR &= ~BIT0 P2SEL0 |= BIT0;

#### P2.1 set to TB0.CCI2A

SYSCFG3 |= TBRMP\_1; TB0CCTL0 |= CCIS\_1; P2DIR &= ~BIT1 P2SEL0 |= BIT1;

#### Outputting PWM on P2.0 and P2.1

P2DIR |= BIT0 | BIT1; P2SEL0 |= BIT0 | BIT1; // Setup Timer0\_B TB0CCR0 = 100-1; TB0CCR1 = OUTMOD\_7; TB0CCR1 = 75; TB0CCR2 = 0UTMOD\_7; TB0CCR2 = 25; TB0CTL = TBSSEL\_1 | MC\_1 | TBCLR;

#### **Timer Interrupt Service Routine**

#if defined(\_\_TI\_COMPILER\_VERSION\_\_) || defined(\_\_IAR\_SYSTEMS\_ICC\_\_) #pragma vector = TIMER0\_B1\_VECTOR \_\_interrupt void Timer0\_B1\_ISR(void) #elif defined(\_\_GNUC\_\_) void \_\_attribute\_\_ ((interrupt(TIMER0\_B1\_VECTOR))) Timer0\_B1\_ISR (void) #endif {

```

switch(__even_in_range(TB0IV,TB0IV_TBIFG))

{

case TB0IV_NONE: break;

case TB0IV_TBCCR1: break;

case TB0IV_TBCCR2: break;

case TB0IV_TBIFG: break;

default: break;

}

}

```

#### MSP430FR2311

```

P2.0 set to TB1.CCI1A

```

```

//SYSCFG3 |= TBRMP_1;

TB1CCTL0 |= CCIS_0;

P2DIR &= ~BIT0

P2SEL0 |= BIT0;

P2.1 set to TB1.CCI2A

//SYSCFG3 |= TBRMP_1;

TB1CCTL0 |= CCIS_1;

P2DIR &= ~BIT1

P2SEL0 |= BIT1;

P2DIR |= BIT0 | BIT1;

P2SEL0 |= BIT0 | BIT1;

// Setup Timer1_B

TB1CCR0 = 100-1;

TB1CCTL1 = OUTMOD_7;

```

→ TB1CCTL1 = OUTMOD\_7; TB1CCR1 = 75; TB1CCTL2 = OUTMOD\_7; TB1CCR2 = 25; TB1CTL = TBSSEL\_1 | MC\_1 | TBCLR;

```

#if defined(__TI_COMPILER_VERSION__) ||

defined(__IAR_SYSTEMS_ICC__)

#pragma vector = TIMER1_B1_VECTOR

__interrupt void Timer1_B1_ISR(void)

#elif defined(__GNUC__)

void __attribute__

((interrupt(TIMER1_B1_VECTOR)))

Timer1_B1_ISR (void)

#endif

{

```

switch(\_\_even\_in\_range(TB1IV,TB1IV\_TBIFG))

{

case TB1IV\_NONE: break;

case TB1IV\_TBCCR1: break;

case TB1IV\_TBCCR2: break;

case TB1IV\_TBIFG: break;

default: break;

}

See Chapter 12 and Chapter 13 of the MSP430FR4xx and MSP430FR2xx Family User's Guide for more details about Timer\_A and Timer\_B.

}

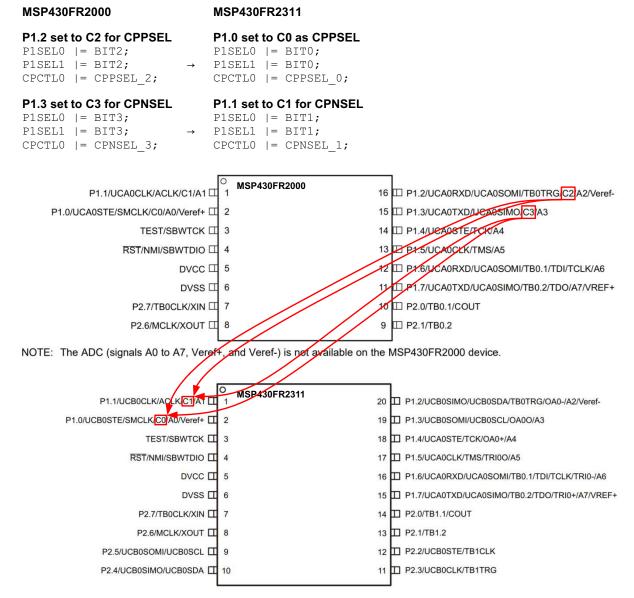

## 1.3 Comparator

If the MSP430FR2000 code selects P1.2 or P1.3 as an input to the comparator, these pins should be changed to P1.0 or P1.1 (see Figure 3).

**Figure 3. Comparator Signals**

See Section 6.11.12 eCOMP0 of the MSP430FR231x Mixed-Signal Microcontrollers data sheet and Chapter 17 of the MSP430FR4xx and MSP430FR2xx Family User's Guide for more details about using the comparator.

# 2 Porting from MSP430FR2311 to MSP430FR2000

The MSP430FR2311 MCU has features not available on the MSP430FR2000, so care should be taken if code is developed on the MSP430FR2311 for the MSP430FR2000. Table 1 summarizes differences between the two MCUs.

| Feature                  | MSP430FR2311               | MSP430FR2000 |

|--------------------------|----------------------------|--------------|

| Nonvolatile memory (KB)  | 4                          | 0.5          |

| RAM (KB)                 | 1                          | 0.5          |

| GPIO pins                | 16                         | 12           |

| I <sup>2</sup> C         | 1                          | 0            |

| SPI                      | 2                          | 1            |

| ADC                      | 10-bit ADC<br>(8 channels) | Slope        |

| Comparators              | 2                          | 4            |

| Timers (16-bit)          | 2                          | 1            |

| Active power (µA/MHz)    | 126                        | 120          |

| Approximate price (US\$) | 0.56   1ku                 | 0.29   1ku   |

# Table 1. Comparison of MSP430FR2311 and MSP430FR2000 Features

For more comparisons between these and other MCU architectures, visit MSP430<sup>™</sup> ultra-low-power MCUs.

Table 2 summarizes peripherals of the MSP430FR2311 that are not present on the MSP430FR2000.

| Function | Signal Name | Pin Name | PxDIR.x    | PxSELx | Description                                                                         |

|----------|-------------|----------|------------|--------|-------------------------------------------------------------------------------------|

|          | A0          | P1.0     | Х          | 11     | Analog input A0                                                                     |

|          | A1          | P1.1     | Х          | 11     | Analog input A1                                                                     |

|          | A2          | P1.2     | Х          | 11     | Analog input A2                                                                     |

|          | A3          | P1.3     | Х          | 11     | Analog input A3                                                                     |

| ADC      | A4          | P1.4     | Х          | 11     | Analog input A4                                                                     |

| ADC      | A5          | P1.5     | Х          | 11     | Analog input A5                                                                     |

|          | A6          | P1.6     | Х          | 11     | Analog input A6                                                                     |

|          | A7          | P1.7     | Х          | 11     | Analog input A7                                                                     |

|          | Veref+      | P1.0     | Х          | 11     | ADC positive reference                                                              |

|          | Veref-      | P1.2     | Х          | 11     | ADC negative reference                                                              |

|          | TRI0+       | P1.7     | Х          | 11     | TIA0 positive input                                                                 |

| TIA0     | TRI0-       | P1.6     | Х          | 11     | TIA0 negative input                                                                 |

|          | TRI0O       | P1.5     | Х          | 11     | TIA0 output                                                                         |

|          | OA0+        | P1.4     | Х          | 11     | SAC0, OA positive input                                                             |

| SAC0     | OA0-        | P1.2     | Х          | 11     | SAC0, OA negative input                                                             |

|          | OA0O        | P1.3     | Х          | 11     | SAC0, OA output                                                                     |

|          | P1.4        | P1.4     | I: 0; O: 1 | 00     |                                                                                     |

|          | P1.5        | P1.5     | I: 0; O: 1 | 00     | GPIO that can be configured for edge-<br>selectable interrupt and for LPM3.5, LPM4. |

|          | P1.6        | P1.6     | I: 0; O: 1 | 00     | and LPM4.5 wake-up input capability                                                 |

| GPIO     | P1.7        | P1.7     | I: 0; O: 1 | 00     |                                                                                     |

| GFIO     | P2.2        | P2.2     | I: 0; O: 1 | 00     | General-purpose I/O                                                                 |

|          | P2.3        | P2.3     | I: 0; O: 1 | 00     | General-purpose I/O                                                                 |

|          | P2.4        | P2.4     | I: 0; O: 1 | 00     | General-purpose I/O                                                                 |

|          | P2.5        | P2.5     | I: 0; O: 1 | 00     | General-purpose I/O                                                                 |

# Table 2. MSP430FR2311 Peripherals Not Available on MSP430FR2000

| Function         | Signal Name | Pin Name                  | PxDIR.x | PxSELx | Description                            |

|------------------|-------------|---------------------------|---------|--------|----------------------------------------|

| l <sup>2</sup> C | UCB0SCL     | P1.3, P2.5 <sup>(1)</sup> | Х       | 01     | eUSCI_B0 I2C clock                     |

| TC TC            | UCB0SDA     | P1.2, P2.4 <sup>(1)</sup> | Х       | 01     | eUSCI_B0 I2C data                      |

|                  | UCB0STE     | P1.0, P2.2 <sup>(1)</sup> | Х       | 01     | eUSCI_B0 slave transmit enable         |

| SPI              | UCB0CLK     | P1.1, P2.3 <sup>(1)</sup> | Х       | 01     | eUSCI_B0 clock input/output            |

| 581              | UCB0SIMO    | P1.2, P2.4 <sup>(1)</sup> | Х       | 01     | eUSCI_B0 SPI slave in/master out       |

|                  | UCB0SOMI    | P1.3, P2.5 <sup>(1)</sup> | Х       | 01     | eUSCI_B0 SPI slave out/master in       |

|                  | TB1.CCI1A   | P2.0                      | 0       | - 01   | Timer TB1 CCR1 capture: CCI1A input,   |

|                  | TB1.1       | F2.0                      | 1       | 01     | compare: Out1 output                   |

| Timer B          | TB1.CCI2A   | P2.1                      | 0       | 01     | Timer TB1 CCR2 capture: CCI2A input,   |

| Timer_D          | TB1.2       | P2.1                      | 1       | 01     | compare: Out2 output                   |

|                  | TB1CLK      | P2.2                      | 0       | 10     | Timer clock input TBCLK for TB1        |

|                  | TB1TRG      | P2.3                      | 0       | 10     | TB1 external trigger input for TB1OUTH |

# Table 2. MSP430FR2311 Peripherals Not Available on MSP430FR2000 (continued)

<sup>(1)</sup> This is the remapped functionality controlled by the USCIBRMP bit of the SYSCFG2 register. Only one selected port is valid at any time.

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated