## SPI I/O Expander Using Low-Memory MSP430™ MCUs

# 🦉 Texas Instruments

## Introduction

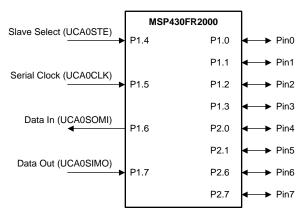

Many applications require simple I/Os functions such as blinking multiple LEDs; however, there may be not enough general-purpose I/O pins for the host microcontroller (MCU) or processor to perform these tasks. The synchronous peripheral interface (SPI) enables serial communication between the MSP430<sup>™</sup> microcontroller and host, which can be acting as an I/O expander with SPI communication. The MSP430FR2000 MCU can be a SPI slave using the eUSCI\_A0 to receive commands from the host and control the 8 general-purpose I/O pins.

The following functions can be expanded:

- SPI interface to expand with 8 simple I/O pins

- Set I/O direction

- Set I/O output value

- Read I/O input value

To get started, download project files and a code example demonstrating this functionality.

#### Implementation

A host processor acting as the master should be connected so it can write or read data from the eUSCI\_A0 of MSP430FR2000 MCU through the 4wire SPI bus [SPI clock (SCLK), MOSI, MISO, and CS/STE]. There are 8 pins being expanded from the SPI commands. Figure 1 shows the SPI IO EXPANDER block diagram interface.

Figure 1. SPI I/O Expander Block Diagram

The host processor SPI configuration is as follows:

- 4-pin SPI with STE/CS active low

- Clock polarity inactive state high

- Data is changed on the first UCLK edge and captured on the following edge

- Most significant bit (MSB) first, 8-bit character length

The slave transmit enable (STE) pin determines if the SPI is enabled and is active low by default. Communication is achieved by sending a 16-bit message, in which the first byte is the command and the second is the data. Then the MSP430FR2000 device sets the PxDIR or PxOUT registers to control the pin direction and output value if setting for output pin. If the host requests the input state of the 8 pins, the MSP430FR2000 MCU sends 8-bit data to the host, indicating the pin input state from the PxIN register.

The 16-bit message sent out by the host is transmitted with two bytes data on the SPI interface. The first byte is the master command, which tells the slave what operation should be done for the pins. Command options are Read, Write-DIR, and Write-OUT. Table 1 lists the 8-bit master command. The Read command instructs the slave to read the input value of all 8 pins and to send those values back to the host. The Write-DIR command instructs the slave to set the direction of all 8 pins with the following master data. The Write-OUT command instructs the slave to set the output value of all 8 pins with the master data in Table 1.

Table 1. Master Command: 8 Bits

|           | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----------|----|----|----|----|----|----|----|----|

| Read      | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Write-DIR | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| Write-OUT | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

The 8-bit master data (see Table 2) must follow the master command transmitted to the slave. For the Read command, all bits of the master data must be 0. For the Write-DIR command, the value of each bit is set in the PxDIR register bit of the mapped GPIO to set the direction of the pins. For the Write-OUT command, each bit in the PxOUT register bit of the mapped GPIO is set for output low or high.

## Table 2. Master Data: 8 Bits

|           | D7                                                | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----------|---------------------------------------------------|----|----|----|----|----|----|----|

| Read      | 0                                                 | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Write-DIR | Pin7 to Pin0: 0 = input, 1 = output               |    |    |    |    |    |    |    |

| Write-OUT | Pin7 to Pin0: $0 =$ output low, $1 =$ output high |    |    |    |    |    |    |    |

SPI I/O Expander Using Low-Memory MSP430™ MCUs

The 8-bit slave data (see Table 3) is sent back to the host to indicate the input values of all 8 pins. These values are read from the PxIN register from the mapped GPIO port of MSP430FR2000 MCU.

#### Table 3. Slave Data: 8 Bits

|      | D7                                          | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|---------------------------------------------|----|----|----|----|----|----|----|

| Read | Pin7 to Pin0: 0 = input low, 1 = input high |    |    |    |    |    |    |    |

#### Performance

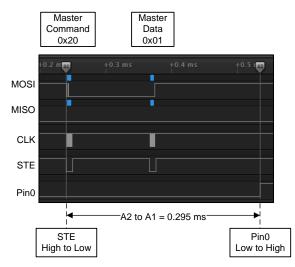

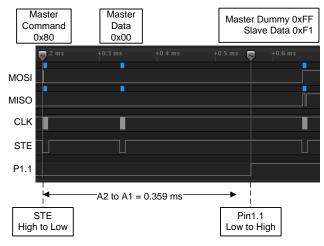

The host processor sends the master command and data to the MSP430FR2000 MCU using a specified bit rate. The bit rate in the following test results is approximately 1 MHz.

The time between the STE start of master command and the STE stop of master data depends on the SPI master configuration of host processor. In the following test results, the delay is approximately 0.136 ms.

The time for action of MSP430FR2000 MCU depends on the CPU clock frequency and the low-power mode (LPM) setting of the device. The following test results used the default 1-MHz CPU clock frequency and LPM3 for standby. The action time can be optimized by using a higher CPU clock frequency, which may increase code size to configure the CPU clock, as well as a lower low-power mode to let the CPU wake up from LPM mode more quickly.

#### Write-OUT action time

The testing for Write-OUT action time uses the host processor to set Pin0 to high. The time between the STE start of master command and the Pin0 low-tohigh edge is measured as Figure 2. Approximately 0.295 ms elapsed from when the host starts to send the command to when the slave has acted on it, which is the Write-OUT action time.

Figure 2. Write-OUT Action Time

MSP430 is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### Write-DIR action time

The Write-DIR action time is the same as the Write-OUT action time, because the MSP430FR2000 MCU performs the same action for both.

#### Read action time

The testing of the Read action time used the host processor to read the pin input values. For illustrative purposes only, the low-to-high edge on P1.1 (only for testing) of the MSP430FR2000 MCU was used to indicate that the slave data was loaded into the slave transmit buffer register UCA0TXBUF and was ready for reading by the host processor. The time between the STE start of the master command and the P1.1 low-to-high edge was measured as shown in Figure 3. Approximately 0.359 ms elapsed from when the host started to send the master command to when the slave was ready to respond. The master device can send a dummy byte (such as 0xFF) to read the slave data stored in the transmit buffer (UCA0TXBUF).

Figure 3. Read Action Time

## **Device Recommendations**

The device used in this example is part of the MSP430 Value Line Sensing portfolio of low-cost MCUs, designed for sensing and measurement applications. This example can be used with the devices shown in Table 4 with minimal code changes. For more information on the entire Value Line Sensing MCU portfolio, visit www.ti.com/MSP430ValueLine.

#### **Table 4. Device Recommendations**

| Part Number  | Key Features                            |  |  |  |  |

|--------------|-----------------------------------------|--|--|--|--|

| MSP430FR2000 | 0.5KB FRAM, 0.5KB RAM, eComp            |  |  |  |  |

| MSP430FR2100 | 1KB FRAM, 0.5KB RAM, 10-bit ADC, eComp  |  |  |  |  |

| MSP430FR2110 | 2KB FRAM, 1KB RAM, 10-bit ADC, eComp    |  |  |  |  |

| MSP430FR2111 | 3.75KB FRAM, 1KB RAM, 10-bit ADC, eComp |  |  |  |  |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated