# Optimizing Active Mode Current Consumption on MSP Devices

Dietmar Walther

Quality

1

## ABSTRACT

Today's advanced architectures of low-power microcontrollers have created a real challenge for the conscientious engineer. How does one, without an intimate knowledge of each competitor's architecture, discern spin from a true level-set of the expected power consumption? This application report focuses on active mode power consumption when the MSP CPU is executing loops. All other power-saving features like power modes, speed or frequency adjustments, and intelligent use of peripherals are not described in detail. The goal is to introduce the differences between the different MSP families with respect to architecture and memory interface. The focus of this document is to provide short and crisp answers to the question why the current consumption might differ from one code to another without changing obvious functions of the application software.

#### Contents

| 1 | Introdu    | uction                                  | 2  |  |  |  |  |  |  |

|---|------------|-----------------------------------------|----|--|--|--|--|--|--|

|   | 1.1        | F1xx, F2xx, and F4xx Families           | 2  |  |  |  |  |  |  |

|   | 1.2        | F5xx and F6xx Families                  | 3  |  |  |  |  |  |  |

|   | 1.3        | FR2xx, FR4xx, FR5xx, and FR6xx Families | 8  |  |  |  |  |  |  |

|   | 1.4        | P4xx (MSP432 <sup>™</sup> ) Family      | 9  |  |  |  |  |  |  |

| 2 | MSP43      | 30 Compileralign_for_power Option       | 9  |  |  |  |  |  |  |

|   | Conclusion |                                         |    |  |  |  |  |  |  |

| 4 | Refere     | nces                                    | 11 |  |  |  |  |  |  |

#### List of Figures

| 1  | 32-Bit Flash Fetch and JMP \$ Alignment                    | 3  |

|----|------------------------------------------------------------|----|

| 2  | ASM Test Case for Active Mode Consumption                  | 4  |

| 3  | Simple LED Blink Test Loop                                 | 4  |

| 4  | Assembly of Simple LED Blink Test Loop                     | 5  |

| 5  | Placement of the Delay Loops in the Memory Map             | 5  |

| 6  | Dynamic Current Consumption for Nonaligned Loops           | 6  |

| 7  | Manual Code Alignment to 32 Bit                            | 7  |

| 8  | Manual Code Alignment to 32 Bit                            | 7  |

| 9  | Current Consumption Specification MSP430FR5969             | 8  |

| 10 | Current Consumption Specification MSP432P401               | 9  |

| 11 | Code Alignment Using TI Compiler Option ""align_for_power" | 10 |

## Trademarks

MSP432, MSP430, Code Composer Studio, E2E are trademarks of Texas Instruments. ARM, Cortex are registered trademarks of ARM Limited. CoreMark is a registered trademark of EEMBC. All other trademarks are the property of their respective owners.

## 1 Introduction

Today's requirements for ultra-low power applications are continuously increasing. Therefore, large efforts during chip development have been made to achieve lower power consumption by using advanced architectures and better process nodes. Besides hardware-related aspects, coding can also play a significant role in achieving low power numbers in the end application. The focus of this paper is on code execution while the CPU is active. Features like low-power modes or utilizing peripherals to save energy are not considered in this application report. As the code development is mainly done by the user of a microcontroller and not the silicon vendor, this document provides some inputs about how MSP devices can be programmed for ultra-low power consumption, especially in active mode. Besides the active mode, also different low power modes are provided to further extend the power budget of MSP based applications.

This document does not deal with all flavors of using different low-power modes, utilizing advanced peripherals, or environmental impact like temperature or supply voltage. It clearly focuses on pure active mode current consumption driven by the CPU and simple code execution.

The following factors stay constant for all the considerations discussed later:

- Only active mode is used without any interrupts.

- No peripherals like ADC, DMA, GPIOs, or LEA are considered or used.

- Supply voltage, temperature, frequency, and subvoltage domains are not considered.

To address the above influential aspects, a much more complex and comprehensive explanation considering all the different device families would be required.

## 1.1 F1xx, F2xx, and F4xx Families

The MSP430F1xx, F2xx, and F4xx families are flash-based ultra-low-power microcontrollers having a 16bit memory interface together with a 16-bit CPU. This means for each data or instruction fetch, a memory access takes place. Therefore, a software loop of a defined cycle located at the same flash address always results in the same current consumption. There are two different factors influencing the active mode current consumption on MSP4301xx, 2xx, and 4xx devices:

- The access ratio between RAM and flash memory

- The address location of the executed code influencing the number of toggling address bus bits

The ratio of accesses between RAM and flash has the bigger impact and needs to be considered if active mode (AM) current consumption between devices is compared. The AM current consumption specification that is in the data sheet is defined as a 50/50 ratio. In the end, it is a simple loop that jumps from flash to RAM and back to flash at the standard frequency of approximately 1 MHz. If the ratio is increased for RAM accesses, the current consumption becomes lower, and if accesses for flash are increased, the current consumption becomes higher. However, no details about the RAM-to-flash ratio are documented because the real use cases have a larger number of combinations. Therefore a typical use case of 50/50% was used to characterize and specify the current consumption to reflect a typical use case scenario.

The second influencing factor is the number of toggling address lines, because this defines the number of charging processes inside the device; however, this has a less significant impact to current consumption. For example, if a "while(1)" loop (or "jmp \$" loop) is placed at address 0x7FFE. In this case, nearly all address bits toggle, because the MAB is loaded with the next address which is 0x8000. If the "while(1)" loop is placed instead at 0x8000 only one address line toggles when the MAB is loaded with 0x8002.

If a user wants to utilize the whole low-power capabilities of devices of these MSP device families, the above two aspects need to be considered. This can explain how different compiled codes can lead to slightly different current consumption if the executive part is placed at different addresses.

## 1.2 F5xx and F6xx Families

On the flash-based F5xx and F6xx families, the two factors mentioned in Section 1.1 are valid as well. However, one additional factor comes into play as well. Despite their extended 16-bit based CPU architecture, these devices have a 32-bit flash interface. This means for 16-bit word access to the flash, 32 bits of data are read and stored in the read buffer, which is then accessed by the CPU. Customers looking to recreate the active current consumption measurements (for example, in the MSP430F5438A data sheet) may be tempted to compile the following, seemingly correct application test case for the F5xx active mode current consumption: "while(1)" loop at 8 MHz. With the data sheet at their side, they would observe one of the following scenarios:

Introduction

- They measure a value that is much less than 230 µA/MHz and may attribute the delta to a loose specification or a good lot of silicon.

- They measure a value that is much greater than the documented 230 µA/MHz and may label the MSP430<sup>™</sup> MCU as violating the specification.

In either case, the customers face an inaccurate representation of the 5xx core's capabilities in active mode. This would be mainly due to the use of the while(1){ } loop, which is and should be recognized as a deprecated method of testing active current consumption.

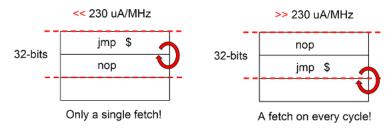

The reason why the "while(1)" loop is an insufficient test has to do with the method in which the 5xx accesses flash memory, 32 bits at a time. An empty "while(1)" loop compiles into the assembly instruction "jmp \$" which is a 16-bit instruction (0x3FFF). "jmp \$" tells the CPU to spin without executing anything, and the alignment of this instruction can make a big difference on the measured current consumption, making this not a meaningful test case.

The following paragraphs gives some insight into the details for seeing a different current consumption using different alignment for the "jmp \$" loop:

- If the "jmp \$" is the first instruction of the 32-bit fetch, the Program Counter (which auto-increments to the address of the next instruction) auto-increments within the data that has already been fetched to the read buffer, and the CPU recognizes there is no need to make an additional fetch from flash. The measured current consumption reflects only the CPU spinning in a loop doing nothing resulting in a value much less than 230 µA/MHz.

- If the "jmp \$" is the second instruction of the 32-bit fetch, then the Program Counter falls outside of the data that has already been fetched into the read buffer, so the CPU core continually fetches the next 32 bits from flash as it executes the instruction. The measured current consumption reflects the CPU spinning in a loop doing nothing, but accessing flash every time resulting in a value much greater than 230 µA/MHz.

- The address where the "jmp \$" instruction is executed plays a significant role with respect to the changing MAB bits that toggle during the execution. If the 16-bit instruction is located at 0x7FFE, all bits toggle during the transition to 0x8000, which leads to an increased current consumption.

- Also the data stored at the address after the "jmp \$" instruction influences the current consumption because of the toggling MDB. Here the worst case would be 0xC000 which is the opposite of 0x3FFF representing the "jmp \$" instruction.

Figure 1. 32-Bit Flash Fetch and JMP \$ Alignment

З

Introduction

www.ti.com

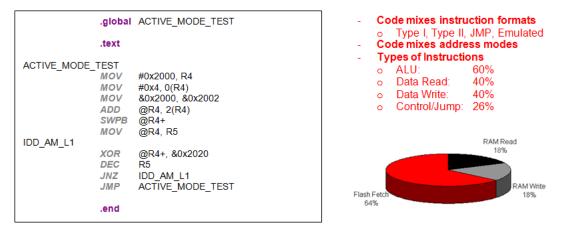

Any real-world application example falls somewhere between zero fetches and a fetch for every instruction executed. Hence a piece of code has been generated that more closely reflects the expected behavior of the core using the Code Composer Studio<sup>™</sup> IDE assembly format (see Figure 2). This code example mixes different instruction formats, address modes, and types to establish a code base that is representative of the F5xx core's capabilities. This is also the code example that is used to measure current consumption for the quoted data sheet parameters in the MSP430F5xx devices, including the integrated USB and RF families like the F552x and CC430.

Figure 2. ASM Test Case for Active Mode Consumption

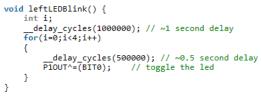

The above explained principle using a simple "while(1)" loop can be extended to slightly more complex loops. One example would be simple wait loops that are often used during standard C code development. On these loops, the 32-bit alignment plays a significant role as well. Even if the impact to the current consumption is not as large as compared to the "while(1)" loop, it is significant enough to be considered by the developer. As an example, a simple blinking LED loop with two delay loops is used. Figure 3 shows that the LED toggle loop consists of two delay elements. The first loop of 1-s delay at the beginning, and a second loop of 0.5-s delay in the LED toggle loop that is executed four times. The assumption is that the current consumption during the execution of each of the loops is identical. But this is only true if the alignment of these loops is done according to the 32-bit flash interface implemented in F5xx and F6xx devices.

Figure 3. Simple LED Blink Test Loop

For better understanding, it is important to look at the output of the compiler to see where the code is placed and how the compiler converted the C code into assembly code. From a translation point both loops are looking identical with respect to instruction set, looking to the assembly code in Figure 4.

|                                                                                                                                             |                                                                                                                        |         | blink 02                                                                                            | -Assembler-Le                                                                                                  | ftLEDBlink().txt                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                                                                                                                                             | leftLEDB.                                                                                                              | link(): |                                                                                                     |                                                                                                                |                                                                                |

| 0100ae:                                                                                                                                     | 141E                                                                                                                   |         | PUSHM.A                                                                                             | #2,R14                                                                                                         | Internation of the ASIana                                                      |

| 0100b0:                                                                                                                                     | 403D 10                                                                                                                | 08C     | MOV.W                                                                                               | #0x108c,R13                                                                                                    | <ul> <li>Initialization of the 1<sup>s</sup>loop</li> </ul>                    |

| 0100b4:                                                                                                                                     | 403E 0                                                                                                                 | 003     | MOV.W                                                                                               | #0x0003,R14                                                                                                    |                                                                                |

|                                                                                                                                             | \$1 \$5:                                                                                                               |         |                                                                                                     |                                                                                                                |                                                                                |

| 0100b8:                                                                                                                                     | 831D                                                                                                                   |         | DEC.W                                                                                               | R13                                                                                                            |                                                                                |

| 0100ba:                                                                                                                                     | 730E                                                                                                                   |         | SBC.W                                                                                               | R14                                                                                                            | 1 <sup>st</sup> sub-loop of 1s loop                                            |

| 0100bc:                                                                                                                                     | 23FD                                                                                                                   |         | JNE                                                                                                 | (0x00b8)                                                                                                       |                                                                                |

| 0100be:                                                                                                                                     | 930D                                                                                                                   |         | TST.W                                                                                               | R13                                                                                                            | and LL CAL                                                                     |

| 0100c0:                                                                                                                                     | 23FB                                                                                                                   |         | JNE                                                                                                 | (0x00b8)                                                                                                       | 2 <sup>nd</sup> sub-loop of 1s loop                                            |

| 0100c2:                                                                                                                                     | 161D                                                                                                                   |         | POPM.A                                                                                              | #2,R14                                                                                                         |                                                                                |

| 0100c4:                                                                                                                                     | 430F                                                                                                                   |         | CLR.W                                                                                               | R15                                                                                                            |                                                                                |

| 0100c6:                                                                                                                                     | 922F                                                                                                                   |         | CMP.W                                                                                               | #4,R15                                                                                                         |                                                                                |

| 0100c8:                                                                                                                                     | 3410                                                                                                                   |         | JGE                                                                                                 | (0x00ea)                                                                                                       |                                                                                |

| 010000.                                                                                                                                     | \$C\$L1:                                                                                                               |         | 000                                                                                                 | (020000)                                                                                                       |                                                                                |

| 0100ca:                                                                                                                                     | 141E                                                                                                                   |         | PUSHM.A                                                                                             | #2,R14                                                                                                         |                                                                                |

|                                                                                                                                             |                                                                                                                        |         |                                                                                                     |                                                                                                                |                                                                                |

|                                                                                                                                             |                                                                                                                        | 844     |                                                                                                     |                                                                                                                | Initialization of the O Ecloop                                                 |

| 0100cc:                                                                                                                                     | 403D 28                                                                                                                | 844     | MOV.W                                                                                               | #0x2844,R13                                                                                                    | <ul> <li>Initialization of the 0.5s loop</li> </ul>                            |

|                                                                                                                                             | 403D 28<br>431E                                                                                                        | 844     |                                                                                                     |                                                                                                                | <ul> <li>Initialization of the 0.5s loop</li> </ul>                            |

| 0100cc:<br>0100d0:                                                                                                                          | 403D 28<br>431E<br>\$1 \$6:                                                                                            | 844     | MOV.W<br>MOV.W                                                                                      | #0x2844,R13<br>#1,R14                                                                                          | Initialization of the 0.5s loop                                                |

| 0100cc:<br>0100d0:<br>0100d2:                                                                                                               | 403D 28<br>431E<br>\$1_\$6:<br>831D                                                                                    | 844     | MOV.W<br>MOV.W<br>DEC.W                                                                             | #0x2844,R13<br>#1,R14<br>R13                                                                                   |                                                                                |

| 0100cc:<br>0100d0:<br>0100d2:<br>0100d4:                                                                                                    | 403D 28<br>431E<br>\$1_\$6:<br>831D<br>730E                                                                            | 844     | MOV.W<br>MOV.W<br>DEC.W<br>SBC.W                                                                    | #0x2844,R13<br>#1,R14<br>R13<br>R14                                                                            | Initialization of the 0.5s loop<br>1 <sup>st</sup> sub-loop of 0.5s loop       |

| 0100cc:<br>0100d0:<br>0100d2:<br>0100d4:<br>0100d6:                                                                                         | 403D 28<br>431E<br>\$1_\$6:<br>831D<br>730E<br>23FD                                                                    | 844     | MOV.W<br>MOV.W<br>DEC.W<br>SBC.W<br>JNE                                                             | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)                                                                | 1 <sup>st</sup> sub-loop of 0.5s loop                                          |

| 0100dc:<br>0100d0:<br>0100d2:<br>0100d4:<br>0100d6:<br>0100d8:                                                                              | 403D 28<br>431E<br>\$1_\$6:<br>831D<br>730E<br>23FD<br>930D                                                            | 844     | MOV.W<br>MOV.W<br>DEC.W<br>SBC.W<br>JNE<br>TST.W                                                    | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)<br>R13                                                         |                                                                                |

| 0100d2:<br>0100d2:<br>0100d4:<br>0100d6:<br>0100d8:<br>0100da:                                                                              | 403D 28<br>431E<br>\$1_\$6:<br>831D<br>730E<br>23FD<br>930D<br>23FB                                                    | 844     | MOV.W<br>MOV.W<br>BEC.W<br>JNE<br>TST.W<br>JNE                                                      | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)<br>R13<br>(0x00d2)                                             | 1 <sup>st</sup> sub-loop of 0.5s loop                                          |

| 0100cc:<br>0100d0:<br>0100d2:<br>0100d4:<br>0100d6:<br>0100d8:<br>0100da:<br>0100dc:                                                        | 403D 28<br>431E<br>\$1_\$6:<br>831D<br>730E<br>23FD<br>930D<br>23FB<br>161D                                            | 844     | MOV.W<br>MOV.W<br>BEC.W<br>JNE<br>TST.W<br>JNE<br>POPM.A                                            | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)<br>R13                                                         | 1 <sup>st</sup> sub-loop of 0.5s loop                                          |

| 0100d2:<br>0100d2:<br>0100d4:<br>0100d4:<br>0100d8:<br>0100da:<br>0100da:<br>0100dc:<br>0100de:                                             | 403D 28<br>431E<br>\$1_\$6:<br>831D<br>730E<br>23FD<br>930D<br>23FB<br>161D<br>4303                                    |         | MOV.W<br>MOV.W<br>DEC.W<br>SBC.W<br>JNE<br>TST.W<br>JNE<br>POPM.A<br>NOP                            | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)<br>R13<br>(0x00d2)<br>#2,R14                                   | 1 <sup>st</sup> sub-loop of 0.5s loop<br>2 <sup>nd</sup> sub-loop of 0.5s loop |

| 0100cc:<br>0100d0:<br>0100d4:<br>0100d4:<br>0100d6:<br>0100da:<br>0100dc:<br>0100dc:<br>0100de:<br>0100de:                                  | 403D 28<br>431E<br>\$1_\$6:<br>831D<br>730E<br>23FD<br>930D<br>23FB<br>161D<br>4303<br>E3D2 02                         | 202     | MOV.W<br>MOV.W<br>DEC.W<br>SBC.W<br>JNE<br>TST.W<br>JNE<br>POPM.A<br>NOP<br>XOR.B                   | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)<br>R13<br>(0x00d2)<br>#2,R14<br>#1,&Port_A_P.                  | 1 <sup>st</sup> sub-loop of 0.5s loop<br>2 <sup>nd</sup> sub-loop of 0.5s loop |

| 0100cc:<br>0100d0:<br>0100d2:<br>0100d4:<br>0100d6:<br>0100d8:<br>0100da:<br>0100dc:<br>0100dc:<br>0100de0:<br>0100e0:                      | 403D 24<br>431E<br>\$1 \$6:<br>831D<br>23FD<br>930D<br>23FB<br>161D<br>4303<br>E3D2 02<br>531F                         |         | MOV.W<br>MOV.W<br>DEC.W<br>SBC.W<br>JNE<br>TST.W<br>JNE<br>POPM.A<br>NOP<br>XOR.B<br>INC.W          | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)<br>R13<br>(0x00d2)<br>#2,R14<br>#1,&Port_A_P<br>R15            | 1 <sup>st</sup> sub-loop of 0.5s loop<br>2 <sup>nd</sup> sub-loop of 0.5s loop |

| 0100cc:<br>0100d0:<br>0100d2:<br>0100d4:<br>0100d6:<br>0100da:<br>0100da:<br>0100dc:<br>0100dc:<br>0100e0:<br>0100e0:<br>0100e4:<br>0100e6: | 403D 28<br>431E<br>\$1_\$6:<br>831D<br>730E<br>23FD<br>930D<br>23FB<br>161D<br>4303<br>E3D2 02<br>531F<br>922F         |         | MOV.W<br>MOV.W<br>DEC.W<br>SBC.W<br>JNE<br>TST.W<br>JNE<br>POPM.A<br>NOP<br>XOR.B<br>INC.W<br>CMP.W | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)<br>R13<br>(0x00d2)<br>#2,R14<br>#1,&Port_A_P:<br>R15<br>#4,R15 | 1 <sup>st</sup> sub-loop of 0.5s loop<br>2 <sup>nd</sup> sub-loop of 0.5s loop |

| 0100cc:<br>0100d0:<br>0100d2:<br>0100d4:<br>0100d6:<br>0100d8:<br>0100da:<br>0100dc:<br>0100dc:<br>0100de0:<br>0100e0:                      | 403D 24<br>431E<br>\$1_\$6:<br>831D<br>730E<br>23FD<br>930D<br>23FB<br>161D<br>4303<br>E3D2 02<br>531F<br>922F<br>3BF0 |         | MOV.W<br>MOV.W<br>DEC.W<br>SBC.W<br>JNE<br>TST.W<br>JNE<br>POPM.A<br>NOP<br>XOR.B<br>INC.W          | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)<br>R13<br>(0x00d2)<br>#2,R14<br>#1,&Port_A_P<br>R15            | 1 <sup>st</sup> sub-loop of 0.5s loop<br>2 <sup>nd</sup> sub-loop of 0.5s loop |

| 0100cc:<br>0100d0:<br>0100d2:<br>0100d4:<br>0100d6:<br>0100da:<br>0100da:<br>0100dc:<br>0100dc:<br>0100e0:<br>0100e0:<br>0100e4:<br>0100e6: | 403D 28<br>431E<br>\$1_\$6:<br>831D<br>730E<br>23FD<br>930D<br>23FB<br>161D<br>4303<br>E3D2 02<br>531F<br>922F         |         | MOV.W<br>MOV.W<br>DEC.W<br>SBC.W<br>JNE<br>TST.W<br>JNE<br>POPM.A<br>NOP<br>XOR.B<br>INC.W<br>CMP.W | #0x2844,R13<br>#1,R14<br>R13<br>R14<br>(0x00d2)<br>R13<br>(0x00d2)<br>#2,R14<br>#1,&Port_A_P:<br>R15<br>#4,R15 | 1 <sup>st</sup> sub-loop of 0.5s loop<br>2 <sup>nd</sup> sub-loop of 0.5s loop |

Figure 4. Assembly of Simple LED Blink Test Loop

Considering the placement inside the memory, Figure 5 shows that the 1-s loop (first bold marked data) is aligned to 32 bit, while the 0.5-s loop (second bold marked data) is not. Each green or blue colored block represents a new access to the flash due to the implemented 32-bit read buffer sourcing the 16 bit CPU. Both of the loops consist of  $5 \times 16$ -bit words which always means that the flash needs to be accessed at least three times, because of the 32-bit read buffer between flash and CPU. The critical point is at which part of the loops the flash gets most accessed. The device architecture, in combination with the placement of the loops inside the flash memory, requires one additional flash access cycle (four times in total) in the 0.5-s delay loop, resulting in a higher current consumption.

| @100A( | )          |    |    |    |    |    |    |    |    |    |    |    |    |    |

|--------|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|

| xx xx  | xx         | xx | xx | xx | xx | xx | xx | хх | xx | xx | xx | xx | 1E | 14 |

| 3D 40  | 8C         | 10 | 3E | 40 | 03 | 00 | 1D | 83 | 0E | 73 | FD | 23 | 0D | 93 |

| FB 23  | 1D         | 16 | 0F | 43 | 2F | 92 | 10 | 34 | 1E | 14 | 3D | 40 | 44 | 28 |

| 1E 43  | <b>1</b> D | 83 | 0E | 73 | FD | 23 | 0D | 93 | FB | 23 | 1D | 16 | 03 | 43 |

| D2 E3  | 02         | 02 | 1F | 53 | 2F | 92 | F0 | 3В | 10 | 01 | xx | xx | xx | xx |

| q      |            |    |    |    |    |    |    |    |    |    |    |    |    |    |

Figure 5. Placement of the Delay Loops in the Memory Map

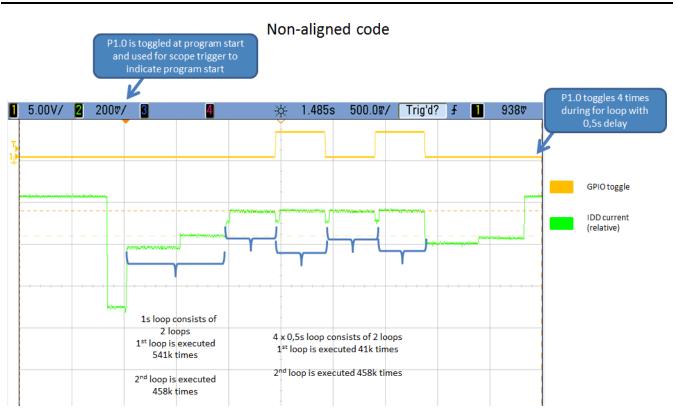

This results in a high current consumption of the 0.5-s loop. Figure 6 shows the dynamic current consumption measured over a 1- $\Omega$  shunt resistor at DVCC = 3.0 V.

Introduction

Figure 6. Dynamic Current Consumption for Nonaligned Loops

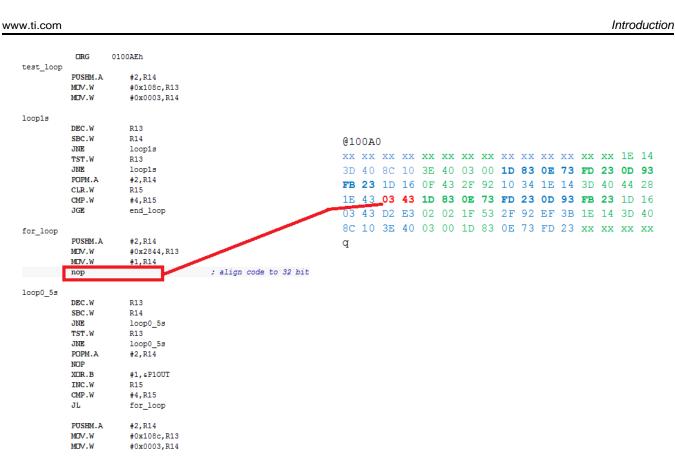

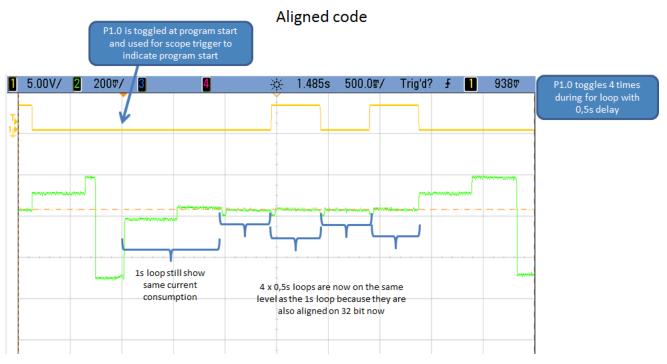

If the loop is "manually" aligned by simply inserting a "nop" (no operation instruction) inside the code, the current consumption is identical for both delay loops (see Figure 7).

## Figure 7. Manual Code Alignment to 32 Bit

This results in a similar current consumption of the 1-s delay loop and the 0.5-s delay loop (see Figure 8).

**TEXAS**

**NSTRUMENTS**

#### 1.3 FR2xx, FR4xx, FR5xx, and FR6xx Families

The FRxx family extends the read buffer concept already used on the F5xx and F6xx family and introduces 4 cache lines of 64-bit size, which act as an interface between FRAM memory and CPU. The cache is implemented in the FRAM controller which contains two cache sets. Each of these cache sets contains two lines that are preloaded with four words (64 bits) during one access cycle. An intelligent logic selects one of the cache lines to preload FRAM data and preserves recently accessed data in the other cache. If one of the four words stored in one of the cache lines is requested (a cache hit), no FRAM access occurs; instead, a cache request occurs. No wait state is needed for a cache request, and the data is accessed with full system speed. However, if none of the words that are available in the cache are requested (a cache miss), the wait state controls the CPU to ensure proper FRAM. This implemented in case the system clock frequency for the CPU or DMA may exceed the FRAM access and cycle time requirements.

This architecture also has a significant impact on current consumption. If the cache hit rate is high, the current consumption is lower, because the memory itself does not need to be accessed. Current consumption numbers are specified in the data sheet. Figure 9 shows an extract of the MSP430FR5969 data sheet. If the deprecated method of testing an active mode current ("while (1)" or "imp \$") is applied on this architecture, the principles described in the previous chapters do not apply to 100% accurate anymore. If the "jmp \$" instruction is located at the end of a cache buffer line, the current consumption is higher only the first time it is executed, because the content is loaded to a second cache line. Afterward the "while (1)" loop is completely executed out of cache, saving power. Therefore the "while (1)" or "jmp \$" instruction is not used to characterize and specify the current consumption in the MSP430 data sheets.

|                                                              |                                 |                 | FREQUENCY (f <sub>MCLK</sub> = f <sub>SMCLK</sub> ) |        |                            |        |                             |       |                             |        |                            |      |    |  |  |  |

|--------------------------------------------------------------|---------------------------------|-----------------|-----------------------------------------------------|--------|----------------------------|--------|-----------------------------|-------|-----------------------------|--------|----------------------------|------|----|--|--|--|

| PARAMETER                                                    | EXECUTION<br>MEMORY             | v <sub>cc</sub> | 1 M<br>0 wait s<br>(NWAIT)                          | states | 4 M<br>0 wait s<br>(NWAIT) | states | 8 Mi<br>0 wait s<br>(NWAITS | tates | 12 M<br>1 wait s<br>(NWAIT) | states | 16 M<br>1 waits<br>(NWAITS | UNIT |    |  |  |  |

|                                                              |                                 |                 | ТҮР                                                 | MAX    | ТҮР                        | МАХ    | ТҮР                         | MAX   | ТҮР                         | МАХ    | ТҮР                        | MAX  |    |  |  |  |

| I <sub>AM, FRAM_UNI</sub><br>(Unified memory) <sup>(3)</sup> | FRAM                            | 3.0 V           | 210                                                 |        | 640                        |        | 1220                        |       | 1475                        |        | 1845                       |      | μA |  |  |  |

| I <sub>am, fram</sub> (0%) <sup>(4)</sup> (5)                | FRAM<br>0% cache hit<br>ratio   | 3.0 V           | 370                                                 |        | 1 280                      |        | 2510                        |       | 2080                        |        | 2650                       |      | μA |  |  |  |

| I <sub>AM, FRAM</sub> (50%) <sup>(6)</sup> (6)               | FRAM<br>50% cache hit<br>ratio  | 3.0 V           | 240                                                 |        | 745                        |        | 1440                        |       | 1575                        |        | 1990                       |      | μA |  |  |  |

| l <sub>a M, FRA M</sub> (66%) <sup>(4)</sup> (6)             | FRAM<br>66% cache hit<br>ratio  | 3.0 V           | 200                                                 |        | 560                        |        | 1070                        |       | 1300                        |        | 1620                       |      | μA |  |  |  |

| I <sub>AM, FRAM</sub> (75%) <sup>(6)</sup> ©                 | FRAM<br>75% cache hit<br>ratio  | 3.0 V           | 170                                                 | 255    | 480                        |        | 890                         | 1085  | 11 55                       | 1310   | 1420                       | 1620 | μA |  |  |  |

| l <sub>a M, FRA M</sub> (100% <sup>(ຍ</sup> ) ອົງ            | FRAM<br>100% cache hit<br>ratio | 3.0 V           | 110                                                 |        | 235                        |        | 420                         |       | 640                         |        | 730                        |      | μA |  |  |  |

| I <sub>AM, RAM</sub> ®                                       | RAM                             | 3.0 V           | 130                                                 |        | 320                        |        | 585                         |       | 890                         |        | 1070                       |      | μA |  |  |  |

| l <sub>AM, RAMony</sub> () ຄ                                 | RAM                             | 3.0 V           | 100                                                 | 180    | 290                        |        | 555                         |       | 860                         |        | 1040                       | 1300 | μA |  |  |  |

#### 5.4 Active Mode Supply Current Into Vcc Excluding External Current over recommended operating free-air temperature (unless otherwise noted)<sup>(1) (2)</sup>

All inputs are tied to 0 V or to  $V_{CC}$ . Outputs do not source or sink any current. Characterized with program executing typical data processing.

f<sub>ACLK</sub> = 32768 Hz, f<sub>MCLK</sub> = f<sub>SMCLK</sub> = f<sub>DCD</sub> at specified frequency, except for 12 MHz. For 12 MHz, f<sub>DCD</sub> = 24 MHz and MCLK = f<sub>SMCLK</sub> = foco/2. At MCLK frequencies above 8 MHz, the FRAM requires wait states. When wait states are required, the effective MCLK frequency

(f<sub>MCLK.eff</sub>) decreases. The effective MCLK frequency also depends on the cache hit ratio. SMCLK is not affected by the number of wait es or the cache hit ratio.

States on the cache in ratio. The following equation can be used to compute  $f_{MCLK eff}$ :  $f_{MCLK eff} = f_{MCLK} / [wait states × (1 - cache hit ratio) + 1]$ For example, with 1 wait state and 75% cache hit ratio  $f_{MCK eff} = f_{MCLK} / [1 × (1 - 0.75) + 1] = f_{MCLK} / 1.25$

Program resides in FRAM. Data resides in SRAM. Average current dissipation varies with cache hit-to-miss ratio as specified. Cache hit ratio represents number cache accesses divided by the total number of FRAM accesses. For example, a 75% ratio implies three of every four accesses is from cache, and the remaining are FRAM accesses.

Tor typical curves. Each characterist uwi in the graph is computed using the reast subares memobilit besi linear fit using the typical data shown in Section 5.4.

Program and data reside entirely in RAM. All execution is from RAM.

Program and data reside entirely in RAM. All execution is from RAM. FRAM is off.

#### Figure 9. Current Consumption Specification MSP430FR5969

So the implementation of the cache architecture of  $4 \times 64$  bit would also help to decrease power consumption of larger loops like the delay loops described in Section 1.2. Nevertheless, it is recommended to consider the code alignment with respect to the cache architecture to achieve the highest cache hit ratio. By doing this you get advantages not only in power consumption but also in speed, because the device can operate without wait states at higher speed. This becomes true if the code is written in a size matching the cache size; for example, small delay loops that can be completely executed from the cache.

## 1.4 P4xx (MSP432<sup>™</sup>) Family

The MSP432 family is based on a ARM<sup>®</sup> Cortex<sup>®</sup>-M4F CPU which is one of the multiple main differentiators compared to the 16 bit MSP430 families mentioned before. The devices of the P4xx family have a read buffering concept implemented as well. This read buffer has a width of 128 bits, which are read once from the flash regardless of the access size of 8, 16, or 32 bits. The 128-bit data and its associated address is internally buffered by the flash controller. Therefore subsequent accesses (expected to be contiguous in nature) within the same 128-bit address boundary are serviced by the buffer, which is configurable from user's perspective (used or not used).

Therefore the real flash hit ratio plays a significant role as well, and loops contained within the 128-bit read buffer should be aligned accordingly to achieve lowest power.

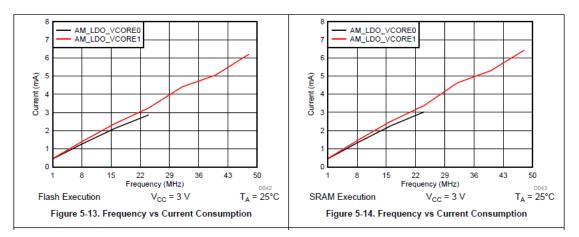

Because the flash-to-SRAM hit ratio still has an influence, the specification of the active mode current was divided into pure flash or SRAM execution. This gives the customer better data on how to design the application. Figure 10 shows an example how the differences for a simple while(1) program looks like if the device is operated with the LDO out of flash or SRAM.

### 5.16 Typical Characteristics of Active Mode Currents for While(1) Program

In addition, more focus was put on providing active mode current consumption for different typical and comparable code execution profiles like CoreMark<sup>®</sup>, prime number, or Fibonacci test programs.

## 2 MSP430 Compiler --align\_for\_power Option

An alternative approach is to utilize the compiler to let it take care about the code alignment also with respect to the placement of a standard "while (1)" loop. The TI MSP430 compiler v16.9.0.LTC delivered with the Code Composer Studio IDE provides an option called "--align\_for\_power". This new -- align\_for\_power compiler option enables power savings by aligning all functions and loops to 4-byte boundaries. When this option is specified, power savings are achieved if a small function or loop aligns to the 32-bit buffer for fetching code from flash. However, there is less benefit for larger functions and loops. See the *MSP430 Optimizing C/C++ Compiler User's Guide* for more details.

Copyright © 2016, Texas Instruments Incorporated

#### Conclusion

code without option

www.ti.com

For the F5xx and F6xx family, the option --align\_for\_power used in the compiler make sure that "while(1)" loops are always placed in the first word of a 32-bit read buffer. This ensures that the execution of the "while(1)" is always done from the 32-bit read buffer without additional flash access cycles. Figure 11 shows the differences in the machine code of specific bench test code and how the alignment works and that the "while (1)" loop (machine code = 0xFF3F) is always placed at the first word of the 32-bit read buffer, because it is aligned to 4 bytes.

code with option

|        | code without option |    |    |    |    |    |    |    |    |    |    |    | code with option |    |    |    |      |      |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |   |

|--------|---------------------|----|----|----|----|----|----|----|----|----|----|----|------------------|----|----|----|------|------|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|---|

| 0100D0 | 02                  | 02 | FF | 3F | 03 | 43 | B2 | 40 | C4 | 00 | 6C | 01 | 32               | DO | 40 | 00 | <br> | <br> | AF | 3B | E2 | D3 | 02  | 02 | 03 | 43 | FF | 3F | 03 | 43 | B2 | 40 | C4 | 00 | Î |

| 0100E0 | 82                  | 43 | 60 | 01 | 82 | 43 | 66 | 01 | 4C | 4C | 2C | 83 | 12               | 24 | 2C | 83 | <br> | <br> | 6C | 01 | 32 | DO | 40  | 00 | 82 | 43 | 60 | 01 | 82 | 43 | 66 | 01 | 4C | 4C |   |

| 0100F0 | 09                  | 24 | 2C | 82 | 14 | 20 | B2 | 40 | 60 | 00 | 62 | 01 | B2               | 40 | FF | 10 | <br> | <br> | 2C | 83 | 14 | 24 | 2C  | 83 | 0A | 24 | 2C | 82 | 16 | 20 | B2 | 40 | 60 | 00 |   |

| 010100 | 64                  | 01 | 0D | 3C | B2 | 40 | 50 | 00 | 62 | 01 | B2 | 40 | 7F               | 10 | 64 | 01 | <br> | <br> | 62 | 01 | B2 | 40 | FF  | 10 | 64 | 01 | 0F | 3C | 03 | 43 | B2 | 40 | 50 | 00 | 1 |

| 010110 | 06                  | 3C | B2 | 40 | 40 | 00 | 62 | 01 | B2 | 40 | 3F | 10 | 64               | 01 | 32 | C0 | <br> | <br> | 62 | 01 | B2 | 40 | 7 F | 10 | 64 | 01 | 07 | 3C | 03 | 43 | B2 | 40 | 40 | 00 | 1 |

| 010120 | 40                  | 00 | B2 | FO | FC | FF | 6E | 01 | A2 | C3 | 02 | 01 | 0D               | 14 | 3D | 40 | <br> | <br> | 62 | 01 | B2 | 40 | 3F  | 10 | 64 | 01 | 32 | CO | 40 | 00 | B2 | FO | FC | FF | 1 |

| 010130 | 0D                  | 00 | 1D | 83 | FE | 23 | 0D | 16 | 03 | 43 | 92 | B3 | 6E               | 01 | F1 | 23 | <br> | <br> | 6E | 01 | A2 | C3 | 02  | 01 | 0D | 14 | 3D | 40 | 0D | 00 | 1D | 83 | FE | 23 | 1 |

| 010140 | 82                  | 43 | 6A | 01 | B2 | 40 | 44 | 00 | 68 | 01 | B2 | 40 | 40               | 00 | 6A | 01 | <br> | <br> | 0D | 16 | 03 | 43 | 92  | B3 | 6E | 01 | F1 | 23 | 82 | 43 | 6A | 01 | B2 | 40 |   |

| 010150 | B2                  | FO | 3F | FF | 6C | 01 | 10 | 01 | 2A | 14 | 8F | 00 | 00               | 00 | 9F | 00 | <br> | <br> | 44 | 00 | 68 | 01 | B2  | 40 | 40 | 00 | 6A | 01 | B2 | FO | 3F | FF | 6C | 01 | 1 |

| 010160 | 00                  | 00 | 04 | 24 | 8C | 00 | 00 | 00 | B1 | 13 | 3E | 02 | 40               | 18 | 1A | 42 | <br> | <br> | 10 | 01 | 2A | 14 | 8F  | 00 | 00 | 00 | 9F | 00 | 00 | 00 | 04 | 24 | 8C | 00 |   |

| 010170 | 5C                  | 01 | 40 | 18 | B2 | 40 | 80 | 5A | 5C | 01 | 8F | 00 | 20               | 5C | 9F | 00 | <br> | <br> | 00 | 00 | B1 | 13 | 48  | 02 | 40 | 18 | 1A | 42 | 5C | 01 | 40 | 18 | B2 | 40 |   |

| 010180 | 2C                  | 5C | 13 | 24 | 89 | 00 | 3C | 5C | 88 | 00 | 4C | 5C | 0C               | 3C | 0C | 09 | <br> | <br> | 80 | 5A | 5C | 01 | 8F  | 00 | 20 | 5C | 9F | 00 | 2C | 5C | 13 | 24 | 89 | 00 | 1 |

| 010190 | 7F                  | 4C | 5F | 06 | 00 | 18 | 5F | 4F | 20 | 5C | Α9 | 00 | 04               | 00 | 0D | 09 | <br> | <br> | 3C | 5C | 88 | 00 | 4C  | 5C | 0C | 3C | 0C | 09 | 7F | 4C | 5F | 06 | 00 | 18 |   |

| 0101A0 | 4F                  | 13 | Α9 | 00 | 04 | 00 | D9 | 08 | F2 | 23 | 7A | C2 | ЗA               | DO | 80 | 5A | <br> | <br> | 5F | 4F | 20 | 5C | Α9  | 00 | 04 | 00 | 0D | 09 | 4F | 13 | Α9 | 00 | 04 | 00 |   |

| 0101B0 | 40                  | 18 | 82 | 4A | 5C | 01 | 8F | 00 | 00 | 00 | 9F | 00 | 00               | 00 | 09 | 24 | <br> | <br> | D9 | 08 | F2 | 23 | 7A  | C2 | 3A | DO | 80 | 5A | 40 | 18 | 82 | 4A | 5C | 01 | 1 |

| 0101C0 | 8A                  | 00 | 00 | 00 | 03 | 3C | 6A | 13 | AA | 00 | 04 | 00 | 9A               | 00 | 00 | 00 | <br> | <br> | 8F | 00 | 00 | 00 | 9F  | 00 | 00 | 00 | 09 | 24 | 8A | 00 | 00 | 00 | 03 | 3C |   |

| 0101D0 | FA                  | 23 | 28 | 16 | 10 | 01 | 1A | 14 | 7A | 4C | 24 | 3C | AC               | 00 | 01 | 00 | <br> | <br> | 6A | 13 | AA | 00 | 04  | 00 | 9A | 00 | 00 | 00 | FA | 23 | 28 | 16 | 10 | 01 | 1 |

| 0101E0 | 0E                  | 93 | 0D | 24 | 3F | 90 | 00 | 01 | 0A | 2C | 29 | 43 | 4F               | 4F | 8F | 10 | <br> | <br> | 1A | 14 | 7A | 4C | 24  | 3C | AC | 00 | 01 | 00 | 0E | 93 | 0D | 24 | 3F | 90 | 1 |

| 0101F0 | 7B                  | 4C | OF | DB | 19 | 83 | FA | 23 | 02 | 3C | 2F | 92 | 02               | 28 | 7B | 4C | <br> | <br> | 00 | 01 | 0A | 2C | 29  | 43 | 4F | 4F | 8F | 10 | 7B | 4C | OF | DB | 19 | 83 |   |

| 010200 | 01                  | 3C | CB | 0A | 1F | 83 | 3F | 93 | 0D | 24 | 4B | 4B | AD               | 00 | 01 | 00 | <br> | <br> | FA | 23 | 02 | 3C | 2F  | 92 | 02 | 28 | 7B | 4C | 01 | 3C | СВ | 0A | 1F | 83 | 1 |

| 010210 | CD                  | 4B | FF | FF | 1F | 83 | 3F | 93 | F9 | 23 | 04 | 3C | AD               | 00 | 01 | 00 | <br> | <br> | 3F | 93 | 0D | 24 | 4B  | 4B | AD | 00 | 01 | 00 | CD | 4B | FF | FF | 1F | 83 | 1 |

| 010220 | CD                  | 4F | FF | FF | 7F | 4C | OF | 9A | F9 | 23 | 7F | 4C | OF               | 93 | E5 | 23 | <br> | <br> | 3F | 93 | F9 | 23 | 04  | 3C | AD | 00 | 01 | 00 | CD | 4F | FF | FF | 7F | 4C |   |

| 010230 | 7F                  | 4C | 8F | 10 | 6B | 4C | OF | 5B | D1 | 23 | 19 | 16 | 10               | 01 | 1A | 14 | <br> | <br> | OF | 9A | F9 | 23 | 7F  | 4C | OF | 93 | E5 | 23 | 7F | 4C | 8F | 10 | 6B | 4C | 1 |

| 010240 | C9                  | 0C | 1B | 49 | 02 | 00 | 0A | 43 | 29 | 3C | CC | 0A | 3D               | 40 | 0C | 00 | <br> | <br> | OF | 5B | D1 | 23 | 19  | 16 | 10 | 01 | 1A | 14 | C9 | 0C | 1B | 49 | 02 | 00 | 1 |

| 010250 | B1                  | 13 | E2 | 02 | 2C | 52 | 4C | 0E | 4C | 0D | EC | 09 | 1E               | 4C | 08 | 00 | <br> | <br> | 0A | 43 | 29 | 3C | СС  | 0A | 3D | 40 | 0C | 00 | B1 | 13 | EC | 02 | 2C | 52 | 1 |

| 010260 | 8C                  | 93 | 0A | 00 | 0D | 0C | 3F | 0C | 04 | 00 | CC | OF | 12               | 20 | 0E | 93 | <br> | <br> | 4C | 0E | 4C | 0D | EC  | 09 | 1E | 4C | 80 | 00 | 8C | 93 | 0A | 00 | 0D | 0C | 1 |

| 010270 | 10                  | 20 | 8E | 00 | 20 | 5C | 9E | 00 |    |    |    | _  |                  |    |    |    |      |      | 3F | 0C | 04 | 00 | CC  | OF | 12 | 20 | 0E | 93 | 10 | 20 | 8E | 00 | 20 | 5C |   |

| 010280 | 00                  | 18 | 5E | 4E | 20 | 5C | AD | 00 | 01 | 00 | CC | 0D | CD               | OF | 4E | 13 | <br> | <br> | 9E | 00 | 2C | 5C | OF  | 24 | 6E | 4D | 5E | 06 | 00 | 18 | 5E | 4E | 20 | 5C |   |

| 010290 | 02                  | 3C | B1 | 13 | F8 | 02 | 1B | 49 | 02 | 00 | 1A | 53 | 0A               | 9B | D5 | 2B | <br> | <br> | AD | 00 | 01 | 00 | СС  | 0D | CD | OF | 4E | 13 | 02 | 3C | В1 | 13 | 02 | 03 | 1 |

| 0102A0 |                     |    |    |    |    |    |    | 00 |    |    |    |    |                  |    |    |    |      |      |    |    |    |    |     | 53 | 0A |    | D5 |    |    | 16 | 10 | 01 | 1F | 4C | 1 |

| 0102B0 | OF                  | 93 | 09 | 24 | AD | 00 | 01 | 00 | CD | 43 | FF | FF | 1F               | 83 | 0E | 73 | <br> | <br> | 01 | 00 | 1E | 4C | 03  | 00 | 0E | 93 | 02 | 20 | 0F | 93 | 09 | 24 | AD | 00 | 1 |

| 0102C0 |                     |    |    |    |    |    |    | 01 |    |    |    |    |                  |    |    |    |      |      | 01 |    |    |    |     |    | 1F |    |    | 73 |    |    |    | 93 |    | 23 | 1 |

| 0102D0 |                     |    |    |    |    | 04 |    |    |    |    |    |    |                  |    |    |    |      |      | 10 |    |    |    |     |    |    |    |    |    |    |    |    | 4D |    | 04 | 1 |

| 0102E0 |                     |    |    |    |    |    |    |    |    |    |    |    |                  |    |    |    | <br> |      | 1C |    |    |    |     |    |    |    |    | 41 |    |    |    |    | 32 | C2 | 1 |

| 0102F0 |                     |    |    |    |    |    |    |    |    |    |    |    |                  |    |    |    |      |      |    |    |    |    | C0  | 04 |    |    | C8 | 04 | 1C |    |    | 04 | 32 | 41 | 1 |

| 010300 |                     |    |    |    |    |    |    |    |    |    |    |    |                  |    |    |    |      |      |    |    |    |    |     | 93 | 06 |    |    | 00 | 01 |    |    |    |    | FF | ľ |

| 010310 |                     |    |    |    |    |    |    | 4F |    |    | _  | _  |                  |    |    |    | <br> |      |    |    |    |    |     |    |    |    | СС |    |    |    |    | 00 |    | 00 | 1 |

| 010320 |                     | 01 | D6 | 01 | 1C | 43 | 10 | 01 | 03 | 43 |    | _  |                  |    |    |    | <br> |      |    |    |    |    | -   |    |    | 03 | 1E | 43 | 80 | 01 | ΕO | 01 | 1C | 43 | 1 |

| 010330 |                     |    |    |    |    |    |    |    |    |    |    |    |                  |    |    |    | <br> | <br> | 10 | 01 | 03 | 43 | FF  | 3F |    |    |    |    |    |    |    |    |    |    | 1 |

|        |                     |    |    |    |    |    |    |    |    |    |    |    |                  |    |    |    |      |      |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |   |

Figure 11. Code Alignment Using TI Compiler Option ""--align\_for\_power--"

## 3 Conclusion

This paper proves that thanks to progress in ultra-low power microcontroller technology, such as different memory (flash or FRAM) access mechanisms, a comparison of low-power using yesterday's techniques – like the "while(1)" loop or by comparing low-power mode numbers – might be misleading. The ultra-low power challenge must be answered from a system-level perspective, and tested with use cases that leverage the capabilities of the technology in question. This application report provides a technical analysis of the MSP430 and MSP432 current consumption messaging to provide the appropriate framework for the interpretation and recreation of the data sheet specifications. It provides an overview over the different implementations across all MSP families and clearly shows that more advanced techniques are implemented on chip level to achieve lowest power consumption. It also clarifies that current consumption values in the data sheet represent typical values for common application scenarios.

### 4 References

- 1. MSP430FR58xx, MSP430FR59xx, MSP430FR68xx, and MSP430FR69xx Family User's Guide

- 2. MSP430FR59xx Mixed-Signal Microcontrollers

- 3. MSP432P4xx Family Technical Reference Manual

- 4. MSP432P401R, MSP432P401M Mixed-Signal Microcontrollers

- 5. TI E2E<sup>™</sup> Community thread: MSP430 Power Consumption

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products<br>Audio<br>Amplifiers<br>Data Converters<br>DLP® Products | www.ti.com/audio<br>amplifier.ti.com<br>dataconverter.ti.com<br>www.dlp.com | Applications<br>Automotive and Transportation<br>Communications and Telecom<br>Computers and Peripherals<br>Consumer Electronics | www.ti.com/automotive<br>www.ti.com/communications<br>www.ti.com/computers<br>www.ti.com/consumer-apps |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| DSP                                                                 | dsp.ti.com                                                                  | Energy and Lighting                                                                                                              | www.ti.com/energy                                                                                      |

| Clocks and Timers                                                   | www.ti.com/clocks                                                           | Industrial                                                                                                                       | www.ti.com/industrial                                                                                  |

| Interface                                                           | interface.ti.com                                                            | Medical                                                                                                                          | www.ti.com/medical                                                                                     |

| Logic                                                               | logic.ti.com                                                                | Security                                                                                                                         | www.ti.com/security                                                                                    |

| Power Mgmt                                                          | power.ti.com                                                                | Space, Avionics and Defense                                                                                                      | www.ti.com/space-avionics-defense                                                                      |

| Microcontrollers                                                    | microcontroller.ti.com                                                      | Video and Imaging                                                                                                                | www.ti.com/video                                                                                       |

| RFID                                                                | www.ti-rfid.com                                                             |                                                                                                                                  |                                                                                                        |

| OMAP Applications Processors                                        | www.ti.com/omap                                                             | TI E2E Community                                                                                                                 | e2e.ti.com                                                                                             |

| Wireless Connectivity                                               | www.ti.com/wirelessconne                                                    | ctivity                                                                                                                          |                                                                                                        |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated