# UCC25230 Bias Power-Supply Design Review

Hong Huang

Power Management Products

#### ABSTRACT

This application report reviews the design steps used in the evaluation module (EVM) UCC25230EVM-754. The EVM helps evaluate the UCC25230 pulse-width modulation (PWM) controller in a forwardflyback, or Flybuck<sup>TM</sup>, dc-dc converter topology for a 48-V telecom bias supply. The EVM is a dual-output converter with 1500-VDC isolation between the two outputs. Each output is typically rated as 12 V and 65 mA, for a total output power of 1.5 W.

#### Contents

| 1 | Design Specifications | 2 |

|---|-----------------------|---|

| 2 | Design Considerations | 3 |

| 3 | Design Steps          | 4 |

| 4 | Performance Test      | 8 |

| 5 | References            | 1 |

|   |                       |   |

### List of Figures

| 1 | EVM Schematics                | 3  |

|---|-------------------------------|----|

| 2 | Efficiency with IOUT1 = 50 mA | 8  |

| 3 | Efficiency with IOUT2 = 50 mA | 8  |

| 4 | Regulation with IOUT1 = 50 mA | 9  |

| 5 | Regulation with IOUT2 = 50 mA | 9  |

| 6 | Gain and Phase vs Frequency   | 10 |

#### List of Tables

| 1 | EVM Specifications                           | 2  |

|---|----------------------------------------------|----|

| 2 | Design Value of Loop-Compensation Parameters | 7  |

| 3 | Voltage Regulation at Corner Conditions      | 9  |

| 4 | Design Performance Summary                   | 10 |

Flybuck is a trademark of Texas Instruments. Coilcraft is a trademark of Coilcraft, Inc. All other trademarks are the property of their respective owners.

# 1 Design Specifications

Table 1 shows the specifications for the EVM, UCC25230EVM-754.

|                 |                          |                                | •   |     |     |           |

|-----------------|--------------------------|--------------------------------|-----|-----|-----|-----------|

| PARAMETER       |                          | TEST CONDITIONS                | MIN | TYP | MAX | UNIT      |

| INPUT C         | HARACTERISTICS           |                                |     |     |     |           |

| VIN             | Input voltage            |                                | 36  | 48  | 72  | VDC       |

| IIN             | Input current            | VIN = 36 V, IOUT = max         |     | 65  |     | mA        |

| OUTPUT          | CHARACTERISTICS          |                                |     |     |     |           |

| VOUT1           | Output voltage primary   | VIN = typ, IOUT = max          |     | 12  |     | VDC       |

| VOUT2           | Output voltage secondary | VIN = typ, IOUT = max          |     | 12  |     | VDC       |

|                 | Output voltage ripple    | VIN = typ, IOUT = max          |     |     | 50  | $mV_{PP}$ |

| IOUT1           | Output current primary   | VIN = min to max               |     |     | 65  | mA        |

| IOUT2           | Output current secondary | VIN = min to max               |     |     | 65  | mA        |

|                 | Output power             |                                |     |     | 1.5 | W         |

| SYSTEM          | S CHARACTERSTICS         |                                |     |     |     |           |

| f <sub>sw</sub> | Switching frequency      |                                |     | 380 |     | kHz       |

| η               | Full-load efficiency     | VIN = typ, IOUT = max          |     | 80  |     | %         |

|                 | Isolation level          | Primary side to secondary side | 1.5 |     |     | kVDC      |

|                 |                          |                                |     |     |     |           |

#### Table 1. EVM Specifications

## 2 Design Considerations

The design-targeted application is an auxiliary (bias) supply in 48-V telecom modular designs with isolation of 1500 VDC between the primary and secondary side. The application requires a small footprint and low profile. Traditionally, a low-dropout regulator (LDO) is used to initially bias the primary-side controller. After start-up, the bias is substituted with an auxiliary winding on the main transformer during normal operation. Secondary-side control has recently become more desirable because of the advantages it offers, such as the fast control-loop response (after eliminating the need of the optocoupler) and digital control with communication. Thus, the initial simple LDO bias solution becomes insufficient. In such cases, an independent bias power supply is required.

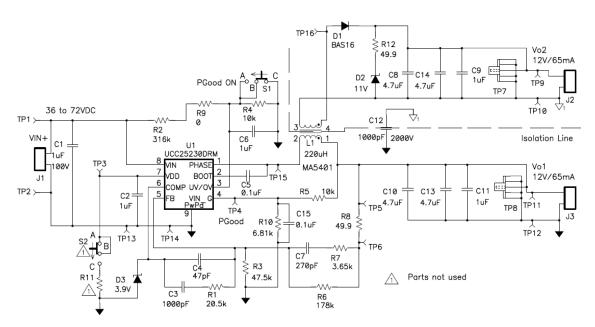

There are several factors regarding achievable performance when making trade-offs (for example, efficiency and energy losses, transient response, board space, cost, as well as design convenience and consistency). Detailed analysis and comparison are not the purpose of this application report; because increasingly more 48-V telecom modular designs prefer to have an independent bias power supply, the details described in this report are required when using the UCC25230. Figure 1 shows the proposed schematics for the design based on the UCC25230 data sheet.

**Figure 1. EVM Schematics**

Texas Instruments

(2)

## 3 Design Steps

## 3.1 Power-Stage Design

Two main parameters of the power stage are primary inductance and output filter capacitance because the converter main switches are integrated inside the device. Determining the primary inductance and filter capacitance are described in this section.

## 3.1.1 Determining the Primary Inductance

## 3.1.1.1 Step 1: Inductance Calculation

To maximize device capability, the design is made a bit differently from traditional procedures. The design is made to maximize the ripple current and minimize the inductance while keeping the average current in accordance with the specified 220 mA in the <u>UCC25230 data sheet</u>. It is important to design an acceptable minimal inductance in order to get the optimal physical inductor with a low profile and small footprint. The primary inductance design is based on Equation 1:

$$L_{PRI} = \frac{V_{O} \times (1 - D_{MIN})}{(2 \times \Delta \% \times I_{PRI}) \times f_{SW}} = \frac{V_{O} \times \left[1 - \frac{V_{O}}{V_{IN\_MAX}}\right]}{I_{PK\_PK} \times f_{SW}}$$

(1)

In Equation 1, I<sub>PRI</sub> is the maximum average current that is obtained from the total current of both the primary and secondary load currents (assuming that the windings are ideally coupled).

In our design,  $I_{PRI} = 65 \text{ mA} \times 2 = 130 \text{ mA}$ . Because the maximum peak current allowed is 220 mA, the peak-to-peak current can be determined as Equation 2:  $I_{PK-PK} = 2 \times (220 \text{ mA} - 130 \text{ mA}) = 180 \text{ mA}$

Because the switching frequency is fixed at 380 kHz,  $V_0 = 12$  V, and  $V_{IN\_MAX} = 72$  V, the minimum primaryside inductance can then be determined as Equation 3:

$$L_{PRI} = \frac{V_{O} \times \left[1 - \frac{V_{O}}{V_{IN\_MAX}}\right]}{I_{PK\_PK} \times f_{SW}} = \frac{12 V \times \left[1 - \frac{12 V}{72 V}\right]}{0.18 A \times 380 \times 10^{3} Hz} = 146.2 \ \mu H \Rightarrow 150 \ \mu H$$

(3)

Note that the minimum inductance of 150  $\mu$ H is the inductance achievable at 220 mA, not the inductance at a no-load condition.

## 3.1.1.2 Step 2: Turns-Ratio Calculation

For a coupled inductor, the turns-ratio is determined by Equation 4:

$$N_{L} = \frac{VOUT2}{VOUT1} = \frac{12 V}{12 V} = 1$$

(4)

An example of a physical inductor that meets these design results with 1500 VDC isolation is available from Coilcraft<sup>™</sup>, part number MA5401-AE.

## 3.1.2 Determining the Output Filter Capacitance

To determine the output filter capacitors, Equation 5 provides a basis:

$$C_{OUT} = \frac{\Delta T}{\frac{\Delta V}{\Delta I} - ESR} = \frac{D_{MAX} \times \frac{1}{f_{SW}}}{\frac{V_{RIPPLE}}{50\% \times I_{PRI}} - ESR} = \frac{\frac{V_0}{V_{IN\_MIN}} \times \frac{1}{f_{SW}}}{\frac{V_{RIPPLE}}{50\% \times I_{PRI}} - ESR}$$

(5)

In our intended application, X7R or X5R multilayer ceramic capacitors are typically used. These capacitors (with a typical value of approximately 1.0  $\mu$ F) have an equivalent serial resistance (ESR) value of approximately 10 m $\Omega$  to 50 m $\Omega$  at a switching frequency of 380 kHz. From Equation 5 and the design specifications,  $I_{PRI} = 130$  mA,  $V_{RIPPLE} = 50$  mV,  $V_O = 12$  V, and  $V_{IN\_MIN} = 36$  V, the output filter capacitance can be obtained as Equation 6:

$$C_{OUT} = \frac{\frac{V_{O}}{V_{IN\_MIN}} \times \frac{1}{f_{SW}}}{\frac{V_{RIPPLE}}{50\% \times I_{PPI}} - ESR} = \frac{\frac{12 V}{36 V} \times \frac{1}{380 \times 10^{3} Hz}}{\frac{0.05 V}{50\% \times 0.13 A} - 0.05 \Omega} = 1.22 \ \mu F$$

With some design margin and considering the voltage dependence of the ceramic capacitors, select capacitors rated at 4.7  $\mu$ F with a voltage rating of 16 V, or 2.2  $\mu$ F with a voltage rating of 25 V. As a good practice from experience, a high-frequency decoupling capacitor with a 0.1- $\mu$ F typical value is still required for the devices to be biased. Refer to Figure 1 for additional capacitance based on the bench test to ensure the output voltage ripple meets the design specifications.

## 3.1.3 Determining the Input Filter Capacitance

The input filter capacitors are designed with an equation similar to the output capacitors, as shown in Equation 7:

$$C_{IN} = \frac{\Delta T}{\frac{\Delta V}{\Delta I} - ESR} = \frac{\frac{V_{O}}{V_{IN\_MIN}} \times \frac{1}{f_{SW}}}{\frac{5\% \times V_{IN\_MIN}}{50\% \times I_{PRI}} - ESR} = \frac{\frac{12 V}{36 V} \times \frac{1}{380 \times 10^{3} Hz}}{\frac{5\% \times 36 V}{50\% \times 0.13 A} - 0.05 \Omega} = 0.032 \,\mu\text{F}$$

(7)

After considering the device internal-circuit requirements, voltage dependence and some design margin, select a 1.0-µF multilayer ceramic capacitor (X5R or X7R) with a voltage rating of 100 V.

(6)

## 3.2 Programming the Device

#### 3.2.1 Determining the Capacitors

There are five critical capacitors when programming the device: C1, C2, C5, C6, and C15.

C1 is the input capacitance. The <u>UCC25230 data sheet</u> specifies the minimum C1 value as 1.0  $\mu$ F. If the resulting value of C1 from the *Determining the Input Filter Capacitance* section is greater than 1.0  $\mu$ F, then use the greater value in the design. The voltage rating depends on the maximum input voltage. In typical 48-V telecom modular applications, a 100-V rating should be used.

C2 is the VDD decoupling capacitor and is 1.0  $\mu$ F, based on the <u>UCC25230 data sheet</u>. Because the VDD typical value is 9 V, a voltage rating of 16 V or greater should be used.

C5 is the bootstrap capacitor and is 1.0  $\mu$ F, based on the data sheet. The voltage rating for C5 is 16 V or greater, based on the voltage between the BOOT and PHASE pins, as specified in the data sheet.

C6 is a noise reduction capacitor with a value typically in the range of 0.1  $\mu$ F to 1.0  $\mu$ F. C6 also introduces turn-on delay. In most applications, this delay presents a desired feature that can allow for a settle-down input voltage transient.

C15 is also a noise reduction capacitor that helps eliminate VIN\_G jitter. The C15 typical value range is 0.1  $\mu F$  to 1.0  $\mu F.$

All of these capacitors should be of a multilayer, ceramic X7R or X5R type.

#### 3.2.2 Determining the Resistors

The resistors used around the device are divided in two groups: control loop without feedback, and control loop with feedback.

#### 3.2.2.1 Control Loop without Feedback Design

The resistors used in the control loop without feedback are R2 and R4 and set up the UV/OV pin. These resistors are used to determine the input voltage that makes VIN\_G valid. The VIN\_G signal notifies the system with the input voltage status when the input voltage reaches the preprogrammed threshold.

Because the threshold for UV on is 36 V of the input voltage and the VIN\_G maximum turn-on threshold is 1.10 V (based on the data sheet), it can be assumed that R4 = 10 k $\Omega$ . Thus, R2 can be calculated as Equation 8:

R2 = R4 ×

$$\frac{V_{IN} - V_{IN_G}}{V_{IN_G}}$$

= 10 kΩ ×  $\frac{36 V - 1.10 V}{1.10 V}$  = 317 kΩ ⇒ 316 kΩ

(8)

## 3.2.2.2 Control Loop with Feedback Design

The converter works in voltage mode control; therefore, it requires Type-III compensation to stabilize the feedback control loop. Type-II compensation can be used if the compromised performance allows. For Type-III compensation, a total of seven components are required, including the output voltage set-point resistors. For the Type-II compensation method, the total components required may be dropped to five. Because 0402 package components are typically used, the savings from cost and board space may not show a significant benefit and a concern of sacrificing performance may result. In this report, Type-III is used.

The compensation can be made in a simple way because the converter can be treated as a simple syncbuck converter. The main influence is the coupled inductor. On the primary side, the inductor presents with a parameter of inductance and an equivalent series resistance. The total output capacitance can be estimated by a summation of the total primary and secondary output filter capacitance. In this design, the total output capacitance is 20.8  $\mu$ F. The output filter inductance at full load is typically 160  $\mu$ H. After these values are known or approximated, the converter is actually equivalent to a sync-buck converter.

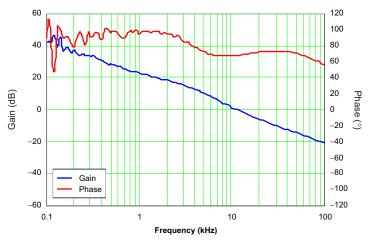

The K-factor method can be used to design the compensation parameters for the starting point. More details about the K-factor method can be found in reference 3 of the References section. The Bode plots of the modulator can be measured before the feedback loop design starts. This method is described in reference 4. The final values of each parameter are shown in Table 2.

| R1      | R3      | R6     | R7      | C3   | C4    | C7     |

|---------|---------|--------|---------|------|-------|--------|

| 20.5 kΩ | 47.5 kΩ | 178 kΩ | 3.65 kΩ | 1 nF | 47 pF | 270 pF |

The output voltage set point is determined by R3 and R6 with the device internal reference at 2.5 V. To validate this, use Equation 9:

$$VOUT1 = VOUT2 = \frac{R3 + R6}{R3} \times V_{REF} = \frac{47.5 \text{ k}\Omega + 178 \text{ k}\Omega}{47.5 \text{ k}\Omega} \times 2.5 \text{ V} = 11.87 \text{ V} \cong 12.0 \text{ V}$$

(9)

## 4 Performance Test

In this section, performance is shown from critical test results. More performance test results can be found in the UCC25230EVM-754 user's guide.

## 4.1 Power-Conversion Efficiency

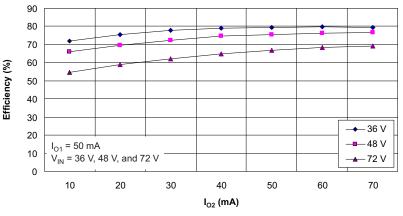

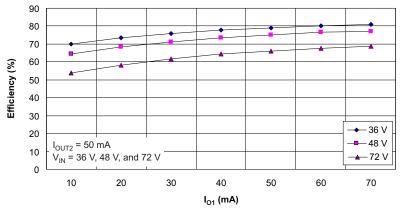

Efficiency can be determined with IOUT1 or IOUT2, as shown in Figure 2 and Figure 3, respectively.

Figure 2. Efficiency with IOUT1 = 50 mA

Figure 3. Efficiency with IOUT2 = 50 mA

## Performance Test

## 4.2 Voltage Regulation

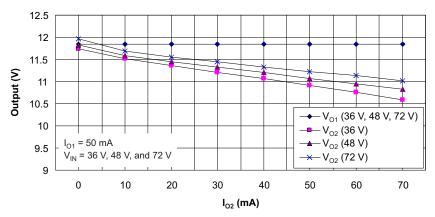

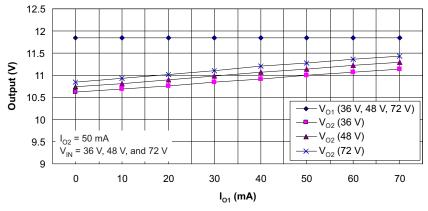

Voltage regulation can be determined with IOUT1 and IOUT2, as shown in Figure 4 and Figure 5, respectively.

Figure 4. Regulation with IOUT1 = 50 mA

Figure 5. Regulation with IOUT2 = 50 mA

Table 3 lists the voltage regulation at corner conditions.

| Table 3. Voltage Regulation | at Corner Conditions |

|-----------------------------|----------------------|

|-----------------------------|----------------------|

| V <sub>IN</sub> (V) | I <sub>01</sub> (mA) | I <sub>o2</sub> (mA) | V <sub>01</sub> (V) | V <sub>02</sub> (V) |

|---------------------|----------------------|----------------------|---------------------|---------------------|

|                     | 0                    | 0                    | 11.85               | 11.50               |

| 36                  | 0                    | 0 65                 |                     | 9.70                |

| 30                  | 65                   | 0                    | 11.95               | 12.10               |

|                     | 60                   | 65                   | 11.85               | 10.50               |

|                     | 72 0                 | 0                    | 11.85               | 11.75               |

| 70                  |                      | 65                   |                     | 10.25               |

| 12                  |                      | 0                    | 11.05               | 12.30               |

|                     | 100                  | 65                   | - 11.85             | 11.10               |

## 4.3 Feedback-Loop Compensation

Figure 6 shows the Bode plots at  $V_{IN}$  = 48 V and load = 50 mA of each output.

Figure 6. Gain and Phase vs Frequency

## 4.4 Design Performance Summary

Table 4 summarizes the design performance.

| PARAMETER                               | TEST CONDITIONS                                                                    | MIN  | TYP  | MAX   | UNIT                        |

|-----------------------------------------|------------------------------------------------------------------------------------|------|------|-------|-----------------------------|

| INPUT CHARACTERISTICS                   |                                                                                    | +    |      | +     |                             |

| Voltage range                           |                                                                                    | 36   | 48   | 72    | V                           |

| Maximum input current                   | $V_{IN}$ = 36 V and IOUT1 = IOUT2 = 65 mA                                          |      | 70   |       | mA                          |

| No load input current                   |                                                                                    |      | 8.5  |       | mA                          |

| OUTPUT CHARACTERISTICS                  |                                                                                    | ·    |      |       |                             |

| Output voltage, VOUT1                   | IOUT1 = 0 mA, IOUT2 = 65 mA                                                        | 11.5 | 11.8 | 12.5  | V                           |

| Oulput voltage, voor i                  | IOUT1 = 65 mA, IOUT2 = 0 mA                                                        | 11.5 | 11.8 | 12.5  | V                           |

|                                         | IOUT1 = 0 mA, IOUT2 = 100 mA                                                       | 9.5  | 10.0 | 11.0  | V                           |

| Output voltage, VOUT2                   | IOUT1 = 100 mA, IOUT2 = 0 mA                                                       | 9.5  | 12.0 | 12.5  | V                           |

| Output load current,<br>IOUT2 or IOUT2  |                                                                                    |      |      | 65    | mA                          |

| Output 1 voltage regulation             | Line regulation:<br>Input voltage = 36 V to 72 V<br>IOUT1 = IOUT2 = 100 mA         |      |      | 10    | mV                          |

| (regulated output)                      | Load regulation:<br>Input voltage = 48 V<br>IOUT1 = 0 mA to 100 mA, IOUT2 = 100 mA |      |      | 10    | mV                          |

| Output 2 voltage regulation             | Line regulation:<br>Input voltage = 36 V to 72 V<br>IOUT1 = IOUT2 = 65 mA          |      |      | 0.75  | V                           |

| (cross-regulated output)                | Load regulation:<br>Input voltage = 48 V<br>IOUT1 = 65 mA, IOUT2 = 0 mA to 65 mA   |      |      | -1.35 | V                           |

| Output voltage ripple (outputs 1 and 2) | At IOUT1 = IOUT2 = 65 mA                                                           |      | 45   | 60    | $\mathrm{mV}_{\mathrm{PP}}$ |

#### **Table 4. Design Performance Summary**

| MIN TYP       |                                  | 1                                              |

|---------------|----------------------------------|------------------------------------------------|

|               | MAX                              | UNIT                                           |

| -             |                                  |                                                |

| 380           | )                                | kHz                                            |

| 81            |                                  | %                                              |

| 80            | )                                | %                                              |

| 4.2           | 5.2                              | V                                              |

| 0.6 × 0.5 × 0 | ).15                             | Inches                                         |

| 2.2 × 1.4     |                                  | Inches                                         |

|               | 4.5                              | °C                                             |

| -             | 81<br>80<br>4.2<br>0.6 × 0.5 × 0 | 80<br>4.2 5.2<br>0.6 × 0.5 × 0.15<br>2.2 × 1.4 |

#### Table 4. Design Performance Summary (continued)

## 5 References

- 1. UCC25230 Data Sheet, SLUSAQ6A, 2011

- 2. UCC25230 Evaluation Module and User's Guide, SLUU670, 2011

- 3. George C. Chryssis, *High-Frequency Switching Power Supplies Theory and Design*, Second Edition, McGraw-Hill, 1989.

- 4. Hong Huang, Feedback Loop Design of an LLC Resonant Power Converter, Application Report, <u>SLUA582A</u>, 2010.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers             | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters        | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products          | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                    | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers      | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface              | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                  | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt             | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        | TI 505 0                        |                               |                                   |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated