# Space-Grade, 50-krad, Low-Side Bidirectional Current Sense Monitor

#### **Design Goals**

| Input                  |                        | Output                |                       | Supply | Common-Mode<br>Voltage | Error        | Total lonizing<br>Dose | Single Event<br>Immunity     |

|------------------------|------------------------|-----------------------|-----------------------|--------|------------------------|--------------|------------------------|------------------------------|

| I <sub>LOAD, MIN</sub> | I <sub>LOAD, MAX</sub> | V <sub>OUT, min</sub> | V <sub>OUT, max</sub> | Vs     | V <sub>CM</sub>        | Output Error | TID                    | SEL                          |

| -7.5 A                 | 7.5 A                  | 500 mV                | 3.5 V                 | 5 V    | 0 V                    | < 2%         | 50 krad (Si)           | 75 MeV × cm <sup>2</sup> /mg |

#### **Design Description**

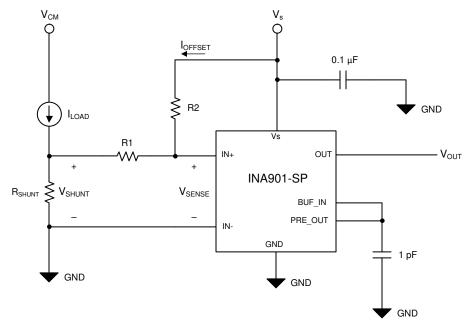

This circuit utilizes passive components (R1 and R2 in the following schematic) to produce a referred to input (RTI) offset that biases the sense input, and achieves bidirectional sensing from a unidirectional current sense amplifier, the INA901-SP. In this design, the normal operating load is from –7.5 A to 7.5 A, with a supply voltage of 5 V. This topology may be used for other supply voltages, but the equations corresponding to offset generation will change accordingly. In addition to this functionality, this circuit implements the INA901-SP, which is a Radiation-Hardness-Assured (RHA), 50-krad (Si) capable device at Low Dose Rate, that is also Single Event Latch-up (SEL) Immune to 75 MeV-cm²/mg at 125°C. The solution presented in this circuit is a low-side implementation, with a common-mode voltage of approximately 0 V.

## **Design Notes**

- 1. This topology is meant for low side implementation, where the IN– pin of the INA901-SP is referenced to GND. While other implementations may be successful, this design is unable to be implemented where  $V_{CM} > V_s$ , as the current must flow toward the IN+ pin to achieve the necessary offset. Therefore, the common-mode voltage of the IN+ pin must be less than that of the supply voltage to ensure valid operation.

- 2. The offset current created by the design process shows that, as a consequence, the offset voltage point deviates slightly with the sense voltage, producing a linear error along with the sense voltage.

- 3. Because this is a low-side implementation, the trade-offs that come with measuring on the low side are in effect here. This includes the inability of the load to detect ground faults.

- 4. When designing with the INA901-SP, be careful to ensure the full-scale input range of the device remains above 20 mV for best performance. If V<sub>SENSE</sub> is allowed below 20 mV, the device may produce additional errors inside of this operating condition. See the INA901-SP Radiation Hardened, –15-V to 65-V Common Mode, Unidirectional Current-Shunt Monitor data sheet for more information.

- 5. While this circuit provides the ability to measure in multiple directions, it does not change the fact that the INA901-SP is inherently a unidirectional device. This infers that one direction of current sensing will be more accurate than the other, as one direction will measure towards the offset voltage of the device, leading to increased error in this direction. The effects of this may be mitigated in part by the use of a one-point calibration, and is discussed later in this document.

#### **Design Steps**

- Design the Offset Current: The offset current will ultimately flow over R1 to create the RTI offset sense voltage, but is determined by the supply voltage and R2. Here, errors will be present due to:

- The input bias current of the IN+ pin will pull a few mA of current from the ideal calculation and this results in a negligible amount of error

- As shown in the design equation, the voltage present on the IN+ pin with respect to GND will also have bearing. It can be inferred (and confirmed in simulation) that this will result in a small linear error over the full-scale range as the generated shunt voltage moves this voltage on the IN+ pin. Here, we approximate this voltage as approximately equal to 0 V.

The offset current with this approximation is given by:

$$I_{OFFSET} = \frac{V_S - V_{IN} + }{R^2} = \frac{5 \text{ V}}{2 \text{ k}\Omega} = 2.5 \text{ mA}$$

Choose R<sub>SHUNT</sub> to Optimize Input Range: With the RTI offset designed, a shunt may now be chosen for the desired sensing range. For the INA901-SP, maintain the lower sensing bound to > 20 mV for optimal performance. This shows that the amount of sensing headroom from V<sub>REF</sub> is:

$$V_{SHUNT. max} = 98 \text{ mV} - 20 \text{ mV} = 78 \text{ mV}$$

From the desired –7.5 A design target, it is calculated that the maximum allowable shunt to achieve this goal is:

$$R_{SHUNT, max} = \frac{V_{SHUNT, max}}{I_{LOAD, max}} = \frac{78 \text{ mV}}{7.5 \text{ A}} = 10.4 \text{ m}\Omega$$

As the  $I_{LOAD}$  design target in the remaining direction is symmetric about  $V_{REF}$ , 10 m $\Omega$  is selected to complete the design. The final input  $V_{SENSE}$  swing is calculated with the following:

$$V_{SHUNT, min} + V_{OFFSET, RTI} \le V_{SENSE} \le V_{SHUNT, max} + V_{OFFSET, RTI}$$

$$-75 \text{ mV} + 98 \text{ mV} \le V_{SENSE} \le 75 \text{ mV} + 98 \text{ mV}$$

$$23 \text{ mV} \le V_{\text{SENSE}} \le 173 \text{ mV}$$

The expected corresponding output is as follows:

$$V_{SENSE, max} \times GAIN \le V_{OUT} \le V_{SENSE, max} \times GAIN$$

$$23 \text{ mV} \times 20 \frac{\text{V}}{\text{V}} \le \text{V}_{\text{OUT}} \le 173 \text{ mV} \times 20 \frac{\text{V}}{\text{V}}$$

$$460 \text{ mV} \le V_{OUT} \le 3.46 \text{ V}$$

Verify Shunt Derating is Sufficient: A necessary aspect of proper shunt design is ensuring that the design

choice has sufficient margin for power derating. As the device heats in the environment, the amount of power

the shunt is capable of dissipating is derated by a certain factor. For continuous sensing, this factor can be

as high as 0.6. Taking this into account, for the design, a shunt must be chosen that is rated for at least the

following:

$$P_{RATING} = \frac{P_{LOSS}}{Derating~Factor} = \frac{I_{LOAD,\,max}^2 \times R_{SHUNT}}{0.6} = \frac{7.5~A^2 \times 10~m\Omega}{0.6} = 937.5~mW$$

So for a successful design, a shunt of at least 1-W rated power is chosen for continuous sensing.

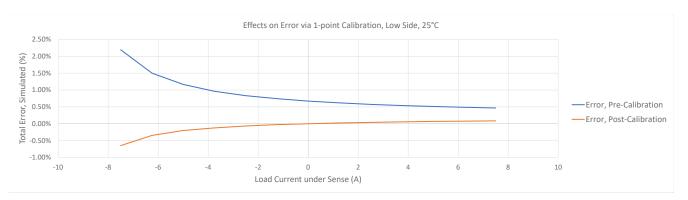

Examine Error. Calibrate if Necessary: As discussed in previous sections, it is expected that the current-sense amplifier will be more accurate in the direction of measurement as the output is driven toward supply. Less accurate measurements are expected as the sense voltage decreases, and errors from the offset voltage begin to dominate the measurement. A potential solution for this is to perform at least a one-point calibration in logic to reduce the effects of the offset voltage.

A one-point calibration is performed by applying the condition,  $V_{SHUNT}=0~\text{mV}$  to the system, capturing the actual value output by the INA901-SP, and maintaining the difference between this value and the calculated ideal in memory. The output of the device is then consistently shifted by this amount. An example of the effects of this are shown in the following simulated results.

#### **Design Simulations**

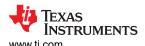

## DC Sweep Results, -7.5 A < I<sub>LOAD</sub> < 7.5 A

**INA901-SP Low-Side Bidirectional Circuit Performance Over Load**

Error Curves, Pre- and Post-Calibration From Simulation Data

Simulated results show that, as expected, there is a slight change to the offset current as the voltage of IN+ shifts with  $V_{SHUNT}$ . Calibration of the raw data results in a full-scale error of < 1%, thus meeting the design goal. It should be noted that parameters such as device offset and input bias currents in TINA-TI models reflect typical data sheet parameters, and additional error may be exhibited pre- and post-calibration due to variation in these parameters. For additional information on one-point calibration and examples involving real bench tested data, see the Bidirectional Topologies for the INA901-SP.

## **Design References**

See the TI Precision Labs, Current Sense Amplifiers video series.

## **Design Featured Current Sense Amplifier**

| INA901-SP                         |                                    |  |  |  |  |  |

|-----------------------------------|------------------------------------|--|--|--|--|--|

| IIVA901-OF                        |                                    |  |  |  |  |  |

| V <sub>S</sub>                    | 2.7 V to 16 V                      |  |  |  |  |  |

| V <sub>CM</sub>                   | –15 V to 65 V                      |  |  |  |  |  |

| V <sub>OUT</sub>                  | GND+3 mV to $V_S$ – 50 mV, typical |  |  |  |  |  |

| Vos                               | ±500 μV, typical                   |  |  |  |  |  |

| Iq                                | 350 μA, typical                    |  |  |  |  |  |

| I <sub>B</sub>                    | ±8 μA, typical                     |  |  |  |  |  |

| TID Characterization (ELDRS-Free) | 50 krad (Si)                       |  |  |  |  |  |

| SEL Immune to LET                 | 75 MeV-cm <sup>2</sup> /mg         |  |  |  |  |  |

| INA901-SP                         |                                    |  |  |  |  |  |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated