## Analog Engineer's Circuit Circuit for Protecting ADS124S08 ADC from EOS for RTD Measurement

# TEXAS INSTRUMENTS

#### Data Converters

Dale Li

| Specifi                                  | ication                                          | Minimum      | Maximum      |

|------------------------------------------|--------------------------------------------------|--------------|--------------|

| Overstress Signal                        | Voltage (V <sub>EOS</sub> )                      | –30 V        | +30 V        |

| Absolute Maximum Input Voltage           | Voltage – Analog Input<br>(V <sub>in_Abs</sub> ) | AVSS – 0.3 V | AVDD + 0.3 V |

| Rating – ADC<br>(AVDD = 5 V, AVSS = 0 V) | Current – Analog Input<br>(I <sub>in_Abs</sub> ) | –10 mA       | +10 mA       |

#### **Design Description**

This circuit shows a solution to protect ADS124S08 delta-sigma ADC from electrical overstress (EOS) for a resistance temperature detector (RTD) application. The protection circuit is designed to provide protection against a ±30-V DC continuous fault as well as a much higher transient fault. Protection against the ±30-V DC fault is needed in case the input terminals are inadvertently connected to the DC supply. The ±24 V is a standard DC supply in industrial systems, so ±30-V protection provides a design margin. The solution is developed for 3-wire RTD input with PT100 RTD sensor and the protection method can also be used for 2-wire, 4-wire RTD input and PT1000 RTD sensor. The protection circuitry includes an external transient voltage suppressor (TVS) diode and a current-limiting resistor to implement an external protection clamp for overstress signal and maintain a minimum impact on measurement accuracy. This circuit is useful in the temperature controller and analog input module of the *Programmable Logic Controller* in factory automation and control system. For protecting high-voltage SAR ADC from electrical overstress, see the *Input protection for high-voltage ADC circuit with TVS Diode* and *Circuit for protecting ADC with TVS diode and PTC fuse* circuit designs. For protecting low-voltage SAR ADC from electrical overstress, see *Circuit for protecting low-voltage SAR ADC from electrical overstress*, see *Circuit for protecting low-voltage SAR ADC from electrical overstress*, see *Circuit for protecting low-voltage SAR ADC from electrical overstress*, see *Circuit for protecting low-voltage SAR ADC from electrical overstress*, see *Circuit for protecting low-voltage SAR ADC from electrical overstress*, see *Circuit for protecting low-voltage SAR ADC from electrical overstress*, see *Circuit for protecting low-voltage SAR ADC from electrical overstress*, see *Circuit for protecting low-voltage SAR ADC from electrical overstress*, see *Circuit for protecting low-voltage SAR ADC from electrical overstress*,

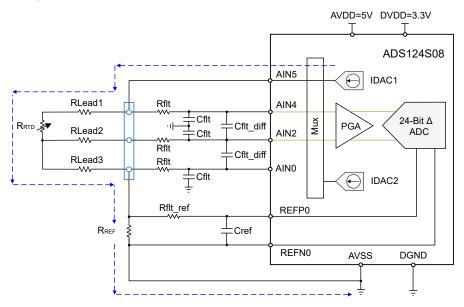

#### Typical Circuit for 3-Wire RTD Measurement Without Protection

#### **Design Goals**

| System Specification                   | Goal  | Measured               |  |

|----------------------------------------|-------|------------------------|--|

| Overstress Voltage                     | ±30 V | No damage on ADS124S08 |  |

| Accuracy (uncalibrated, –40°C to 85°C) | ±0.5% | < ±0.05%               |  |

#### **Design Notes**

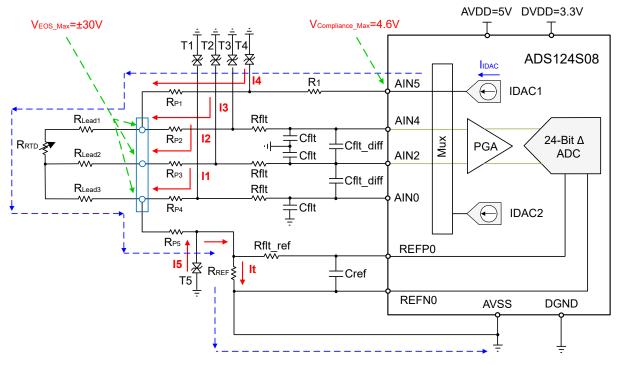

- 1. The SMBJ14CA bidirectional TVS diodes from Bourns<sup>®</sup> are selected to protect each input of the ADS124S08 from electrical overstress signals by considering:

- · Select SMBJ series TVS diode for proper package size and the ability of 600-W power dissipation

- Select bidirectional 14-V standoff voltage for minimum power dissipation on current-limiting resistors

- 2. The current-limiting resistors R<sub>P1</sub>, R<sub>P2</sub>, R<sub>P3</sub>, R<sub>P4</sub> and R<sub>P5</sub> are used to limit fault current for protecting the TVS diodes and ADC, also helping to clamp the input overstress signal on the diodes by selecting the proper resistor value. The high-resistance value of R<sub>P2</sub>, R<sub>P3</sub>, R<sub>P4</sub>, and R<sub>P5</sub> is exactly the same as the resistance value of R<sub>P1</sub> to avoid any additional errors caused by the resistance mismatch when the leakage current of TVS diodes flows through these resistors. Note that the R<sub>Lead1</sub>, R<sub>Lead2</sub>, and R<sub>Lead3</sub> in *Input Protection Circuity for ADC From Electrical Overstress* are equivalent lead wire resistance.

- 3. Keep the capacitance value of differential capacitor ≥ 10 × common-mode capacitor. Keep the bandwidth of differential filter ≥ 10 × data rate.

- 4. See the Electrical Overstress on Data Converters in the TI Precision Labs ADCs video series. This series discusses the details on protection solutions for different types of data converters including theoretical explanation, diode selection, current-limiting resistor selection, and test result.

Input Protection Circuity for ADC From Electrical Overstress

#### **Component Selection**

- The ADC input voltage range is set as the maximum voltage (V<sub>in\_Abs</sub>) before turning on the internal ESD diode. The input current range is the maximum current that the internal ESD diode can support continuously.

- 2. The maximum voltage on ADS124S08 is 5.3 V when the AVDD is 5 V, so any positive electrical overstress signal higher than which 5.3 V should be clamped for protecting the input of the ADS124S08. In this solution, the SMBJ14CA bidirectional TVS diode is selected to protect the ADC from an electrical overstress signal. This diode will break down between 15.6 V and 17.9 V and limit the input voltage. This voltage level exceeds the absolute maximum of the ADC, but current-limiting resistors in conjunction with the ADS124S08S internal ESD diodes will protect the device.

| Part Number | MFG    | Reverse<br>Standoff<br>Voltage (V <sub>R</sub> ) | Min  | Voltage (V <sub>BR</sub> )<br>Max | Clamping<br>Voltage Max<br>(V <sub>C</sub> at I <sub>PP</sub> ) | Reverse<br>Leakage<br>Max<br>(I <sub>R</sub> at V <sub>R</sub> ) | Peak pulse<br>Current<br>(I <sub>PP</sub> ) | Peak Power<br>Dissipation<br>(P <sub>PP</sub> ) | Steady State<br>Power<br>Dissipation<br>(P <sub>PP</sub> ) |

|-------------|--------|--------------------------------------------------|------|-----------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------|------------------------------------------------------------|

| SMBJ14CA    | Bourns | 14 V                                             | 15.6 | 17.9                              | 23.2 V                                                          | 1 µA                                                             | 25.9 A                                      | 600 W                                           | 5 W                                                        |

3. This design shows a protection solution for a single IDAC current, low-side external reference and 3-wire RTD measurement. The current-limiting resistor R<sub>P1</sub> in the IDAC channel AIN5 is more critical because the node voltage on the AIN5 pin is limited by the maximum compliance voltage which is 4.6 V for 5-V AVDD supply. A high-resistance value of R<sub>P1</sub> and R<sub>1</sub> is helpful to limit fault current and protect the ADC in a fault condition; however, the high-resistance value of these resistors increases the voltage on the AIN5 pin in a normal operation to violate the compliance voltage. The protection solution is designed to protect the ADC from miswiring ±24-V power supply to the input of RTD measurement circuit. The ±30-V fault signals are considered for a design margin. The absolute maximum input current rating of ADS124S08 is ±10 mA, so ±5-mA current is used for a margin and limit flowing into ADC input and ±25-mA total fault current is limited to flow through R<sub>P1</sub>.

| EOS Fault Voltage    |       | ADC Input Voltage (Abs) |        | ADC Input Current    |       | Fault Current          |        |

|----------------------|-------|-------------------------|--------|----------------------|-------|------------------------|--------|

| V <sub>EOS_max</sub> | +30 V | V <sub>in_max</sub>     | +5.3 V | I <sub>ADC_max</sub> | +5 mA | I <sub>fault_max</sub> | +25 mA |

| V <sub>EOS_min</sub> | –30 V | V <sub>in_min</sub>     | –0.3 V | I <sub>ADC_min</sub> | –5 mA | I <sub>fault_min</sub> | –25 mA |

The  $R_{P1}$  and  $R_1$  are determined by the largest resistor values from the following equations:

For positive overstress voltage +30 V,

$$R_{P1} \ge \frac{V_{EOS\_max} - V_{BR\_min}}{I_{fault\_max}} = \frac{30 V - 15.6 V}{25 mA} = 576 \Omega \text{ (round up to standard 590 }\Omega \text{)}$$

$$R_1 \ge \frac{V_{BR\_min} - V_{in\_max}}{I_{ADC\_max}} = \frac{15.6 V - 5.3 V}{5 mA} = 2.06 k\Omega \text{ (round up to standard 2.2 k}\Omega\text{)}$$

For negative overstress voltage -30 V,

$$R_{P1} \ge \frac{V_{EOS\_min} - \left(-V_{BR\_min}\right)}{I_{fault\_min}} = \frac{-30 \ V - \left(-15.6 \ V\right)}{-25 \ mA} = 576 \ \Omega \left(\text{round up to standard } 590 \ \Omega\right)$$

$$R_1 \ge \frac{-V_{BR\_min} - V_{in\_max}}{I_{ADC\ min}} = \frac{-15.6 \ V - \left(-0.3 \ V\right)}{-5 \ mA} = 3.06 \ k\Omega \left(\text{round up to standard } 3.4 \ k\Omega\right)$$

The larger value 3.4-k $\Omega$  resistor is selected for R<sub>1</sub> and a 590- $\Omega$  resistor is selected for R<sub>P1</sub>.

In the following equations, the dissipated power is calculated in  $R_1$  and  $R_{P1}$  during a negative electrical overstress fault event which is the worst case for these resistors. The objective is to make sure that the correct power rating is used on the resistors,  $R_1$  and  $R_{P1}$ .

$$P_{RP1} = \frac{\left(V_{EOS\_min} - \left(-V_{BR\_min}\right)\right)^2}{R_{P1}} = \frac{\left(-30 V - \left(-15.6 V\right)\right)^2}{590 \,\Omega} = 351 \, mW$$

Hence, the  $P_{RP1}$  is selected as 0.5 W for  $R_{P1}$  with extra design margin.

$$P_{R1} = \frac{\left(-V_{BR}\underline{min} - V_{in}\underline{min}\right)^2}{R_1} = \frac{\left(-15.6 \,V - \left(-0.3 \,V\right)\right)^2}{3.4 \,k\Omega} = 68.85 \,mW$$

Hence, the  $P_{R1}$  is selected as 0.1 W for  $R_1$  with extra design margin.

4. The resistance of the PT100 sensor is approximately 20 Ω at –200°C and 400 Ω at +850°C. The resistance of R<sub>REF</sub> is determined by the maximum voltage across the PT100 (R<sub>RTD</sub>) when the I<sub>IDAC</sub> current flows through the PT100. The 0.5-mA single I<sub>IDAC</sub> current from AIN5 is selected and configured to keep the error low which is caused by self-heating on the PT100. The PGA gain on the ADS124S08 is set to 4. The minimum voltage (V<sub>REF min</sub>) on the R<sub>REF</sub> is calculated by the following equations:

$V_{RTD_max} = I_{IDAC} \times R_{RTD_max} = 0.5 \ mA \times 400 \ \Omega = 0.2 \ V$

$V_{REF min} = V_{RTD max} \times Gain = 0.2 V \times 4 = 0.8 V$

The voltage ( $V_{REF}$ ) on the  $R_{REF}$  is set to 1 V for a margin. The resistance of  $R_{REF}$  is determined by the following equation:

$$R_{REF} = \frac{V_{REF}}{I_{DAC}} = \frac{1}{0.5} \frac{V}{mA} = 2 k\Omega$$

5. The input resistor in parallel with differential and common-mode capacitors in other channels is used to filter the noise from the front-end circuit. The exact resistor value is not critical because there is no compliance voltage limit on these channels and there is no IDAC current flowing through it.

$$R_{flt} > R_1 = 3.4 \, k\Omega$$

$$R_{flt} < 10 \, k\Omega$$

$$\Rightarrow R_{flt} = 4.99 \, k\Omega$$

$$f_{in_Diff} > 10 \times Data_Rate$$

$$Data_Rate = 200 \, Hz$$

$$\Rightarrow f_{in_Diff} = 3 \, kHz$$

$$C_{flt_diff} = \frac{1}{2\pi \times f_{in_diff} \times (R_{RTD} + 2 \times R_{flt} + 2 \times R_P)}$$

$$= \frac{1}{2\pi \times 3 \, kHz \times (400 \, \Omega + 2 \times 4.99 \, k\Omega + 2 \times 590 \, \Omega)} = 4.6 \, nF$$

Hence, a standard value 4.7 nF is selected for C<sub>flt diff</sub>.

$$C_{flt} = \frac{C_{flt\_diff}}{10} = \frac{4.7 nF}{10} = 470 pF$$

$$C_{ref} = C_{flt} = 470 pF$$

$R_{flt\_ref} = R_{flt} = 4.99 \, k\Omega$

#### Accuracy Measured on Hardware

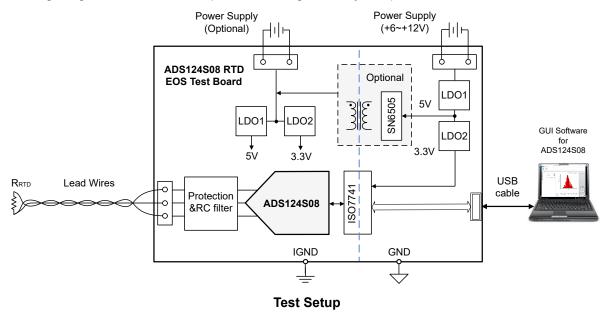

ADS124S08 Test Board With Input Protection Circuity shows the ADS124S08 EOS test hardware board which is designed for RTD measurement and is protected using the SMBJ14CA TVS diode from Bourns and TVS1401 bidirectional TVS diode from Texas Instruments. The isolated power supply and digital communication circuit on the test board are designed for EMC (electromagnetic compatibility) testing which are not covered in this document. The test board utilizes the onboard TM4C1294NCPDT Tiva<sup>™</sup> Arm<sup>®</sup> Processors to communicate with the ADC via serial peripheral interface (SPI) and provide communication with a PC over a universal serial bus (USB) interface. The software including the Delta-Sigma ADC EvaluaTIon Software installer and ADS124S08 Device Package installer from the EVM tool page are used to collect conversion data from the ADC and check the performance.

ADS124S08 Test Board With Input Protection Circuity

The following image shows the test setup for measuring accuracy and performance.

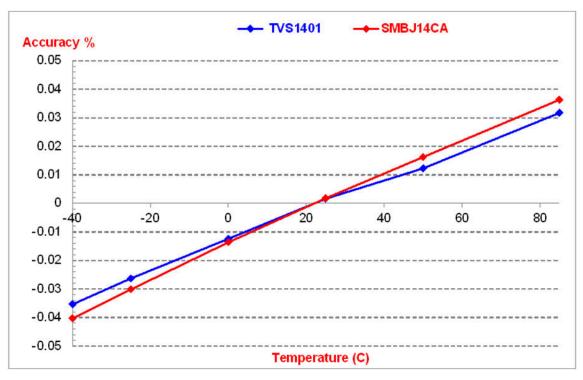

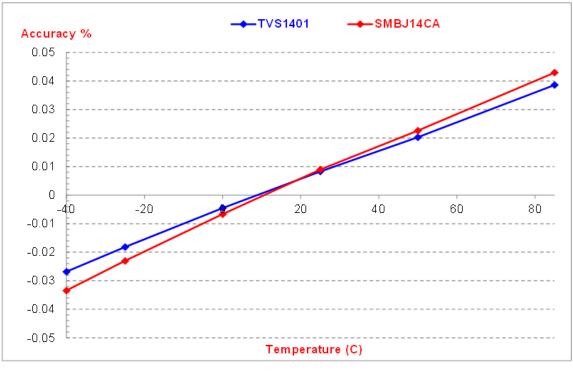

The next images show the measured accuracy performance for full and zero scale RTD values over ambient temperature from  $-40^{\circ}$ C to  $+85^{\circ}$ C. The purpose of this test is to confirm that the TVS diode leakage did not introduce a significant error across the system ambient temperature range. The test result shows the measured accuracy (<  $\pm 0.05\%$ ) with all the protection circuitry including TVS diodes and current-limiting resistors across the entire temperature range meets the expected accuracy ( $\pm 0.5\%$ ).

RTD Measurement Accuracy at RTD =  $100 \Omega (0^{\circ}C)$

#### **Resolution Measured on Hardware**

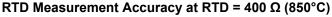

The next image shows the measured effective number of bits (ENOB) and noise-free resolution with bidirectional TVS diode TVS1401 from Texas Instruments. This test shows that the protection circuit has no significant impact on the ADC noise performance.

| Table Title                                                                      |             |                              |  |  |  |

|----------------------------------------------------------------------------------|-------------|------------------------------|--|--|--|

| Measured Result                                                                  | ENOB (Bits) | Noise-Free Resolution (Bits) |  |  |  |

| High Temp (+85°C)                                                                | 21.2        | 18.8                         |  |  |  |

| Room Temp (+25°C)                                                                | 21.3        | 19.0                         |  |  |  |

| Cold Temp (–40°C)                                                                | 21.5        | 19.1                         |  |  |  |

| Test Condition: low side reference, 3-wire RTD with TVS1401 protection solution. |             |                              |  |  |  |

| Measured Resolution  | for RTD = $100 \Omega$ With | TVS1401 at +85°C |

|----------------------|-----------------------------|------------------|

| modourou recondition |                             |                  |

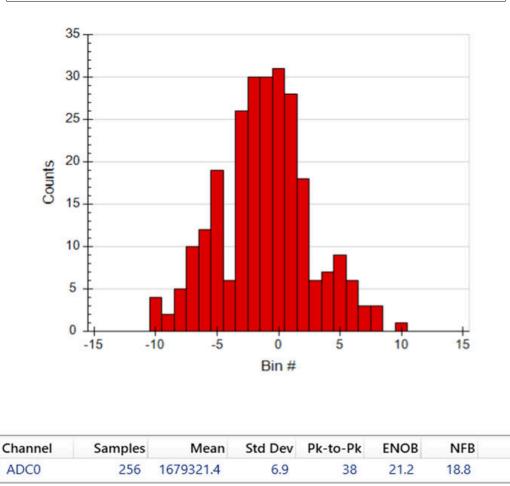

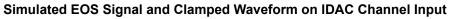

#### ADC Input Overvoltage Condition

The circuit was tested and verified with overstress DC signals. To see how the protection circuit works, an overstress sine wave signal ( $\pm$ 60 V<sub>peak-peak</sub>) is applied to the input of the EOS test board. Simulated EOS Signal and Clamped Waveform on IDAC Channel Input shows the clamped waveform which was captured on the AIN5 input of the ADS124S08. The external TVS diode has been turned on and the overdriven signal has been clamped to the voltage between –200 mV and +6.4 V. Note that the clamped waveform is captured on the IDAC channel input (AIN5), so the resistance value of R<sub>1</sub> is limited because of the compliance voltage limit on the ADS124S08. The R<sub>flt</sub> resistors on other channels of the ADS124S08 are not limited by the compliance voltage, so a large resistance value of R<sub>flt</sub> is used to limit the fault current to the ADC input and the overvoltage sine wave signal is clamped to be less than +5.3 V absolute maximum input voltage on the ADS124S08. The ADC device is successfully protected from external electrical overstress signal.

#### **Design Featured Devices**

| Device    | Key Features                                                                                    | Link      | Other Possible<br>Devices |

|-----------|-------------------------------------------------------------------------------------------------|-----------|---------------------------|

| ADS124S08 | Low power, low noise, 24-bit, 4-kSPS, 12-channel delta-sigma ADC with PGA and voltage reference | ADS124S08 | ADCS                      |

| ADS124S06 | Low power, low noise, 24-bit, 4-kSPS, 6-channel delta-sigma ADC with PGA and voltage reference  | ADS124S06 | ADCS                      |

| TVS1401   | 14-V bidirectional flat-clamp surge protection device                                           | TVS1401   | Circuit-Protection        |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated