# ISOW1044 具有集成式低发射、低噪声、高效直流/直流转换器的隔离式 CAN FD 收发器

### 1 特性

- 符合 ISO 11898-2:2016 物理层标准要求

- 支持经典 CAN: 1Mbps

- 针对 CAN FD 进行了优化: 2Mbps 和 5Mbps

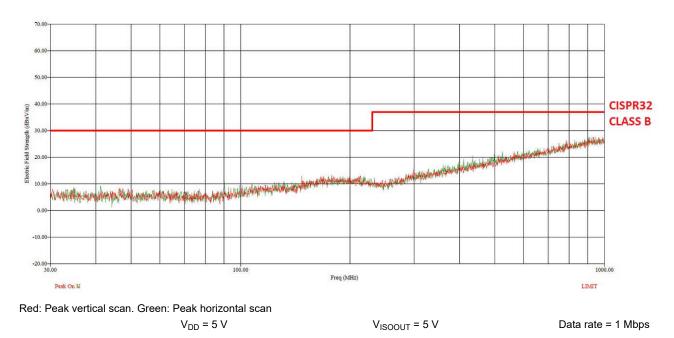

- 低发射、低噪声的集成式直流/直流转换器

- 符合 CISPR 32 和 EN 55032 B 类标准, 在双层 PCB 上具有大于 6dB 的裕度

- 25 MHz 的低频电源转换器可实现低噪声性能

- 其他 10Mbps GPIO 通道

- 高效率输出功率

- 典型效率:47%

- 隔离式输出电压精度:±5%

- 额外输出电流:20mA

- 用于 CAN 和直流/直流的独立电源

- 逻辑电源 (V<sub>IO</sub>): 1.71V 至 5.5V

- 电源转换器电源 (V<sub>DD</sub>): 4.5V 至 5.5V

- 支持故障保护的 CAN FD 收发器

- 直流总线故障保护电压: ±58V

- 接收器共模输入电压: ±12V

- 通过总线唤醒模式实现远程唤醒

- 典型循环延迟:167ns

- 增强型和基础型隔离选项

- 高 CMTI: 100 kV/µs(典型值)

- 具有以 GND2 为基准的高 ESD 总线保护

- HBM ESD: ±12kV

- IEC 61000-4-2 接触放电: ±8kV

- 工作温度范围: -40°C 至 125°C

- 电流限制和热关断

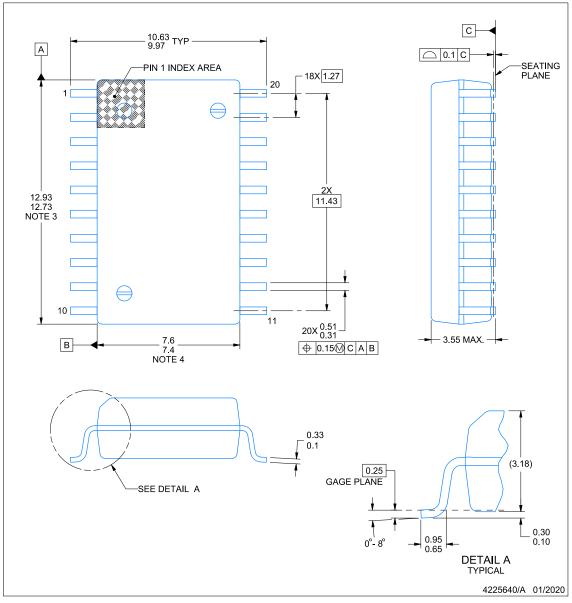

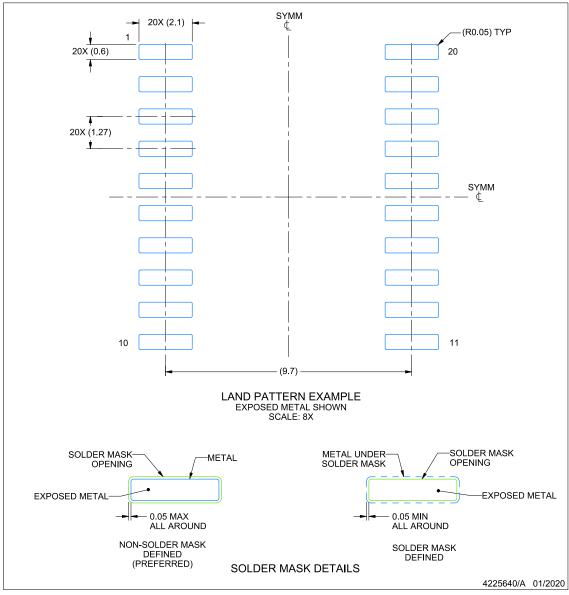

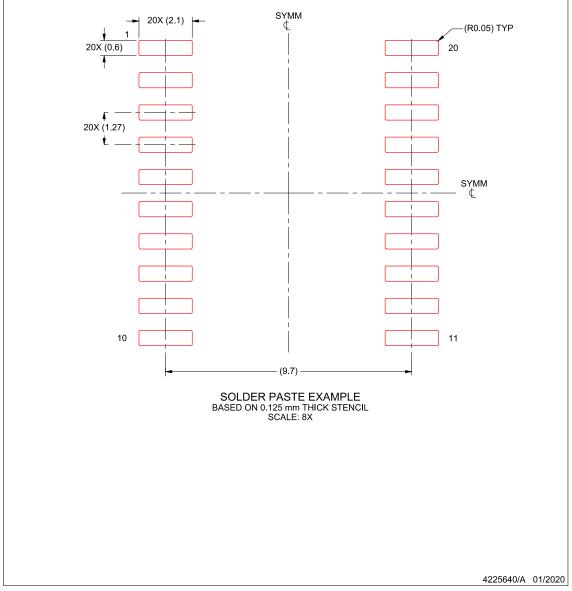

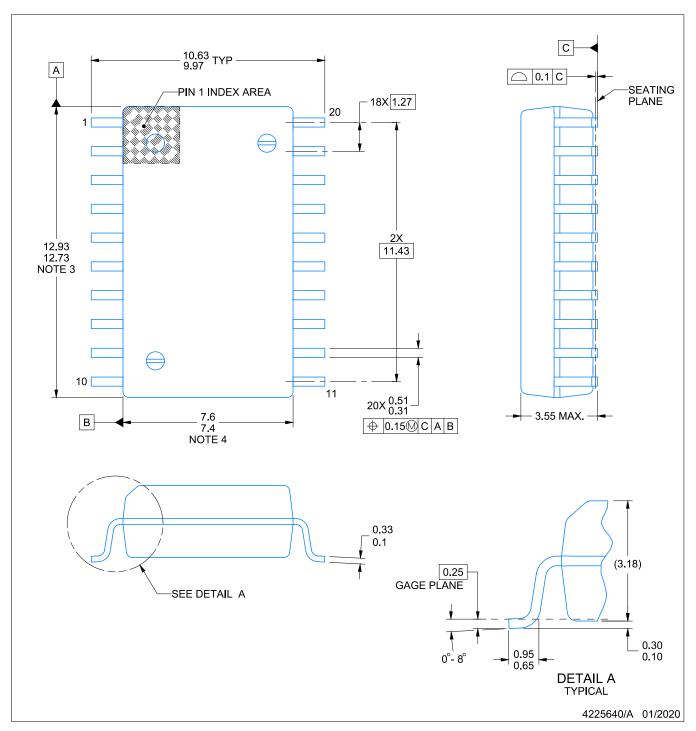

- 20 引脚宽体 SOIC 封装

- 安全相关认证(计划):

- 符合 DIN VDE V 0884-11:2017-01 标准的 VDE 增强型和基础型绝缘

- UL 1577 组件认证计划

- IEC 62368-1、IEC 61010-1、IEC 60601-1 和 GB 4943.1-2011 认证

### 2 应用

- 工厂自动化

- 楼宇自动化

- 工业运输

- 光伏逆变器,保护继电器

- 电机驱动器

## 3 说明

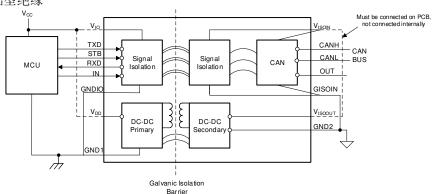

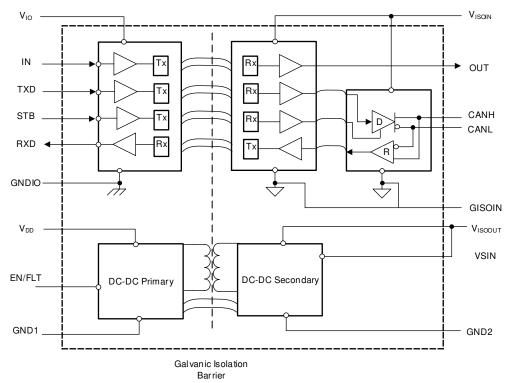

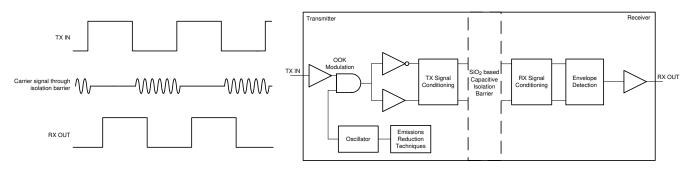

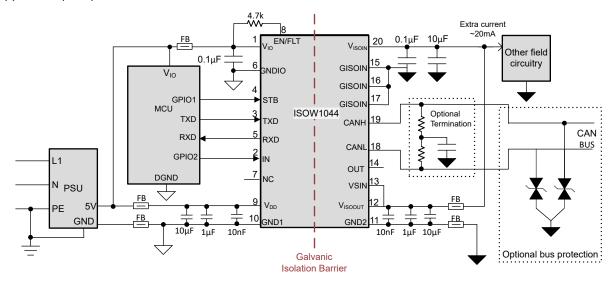

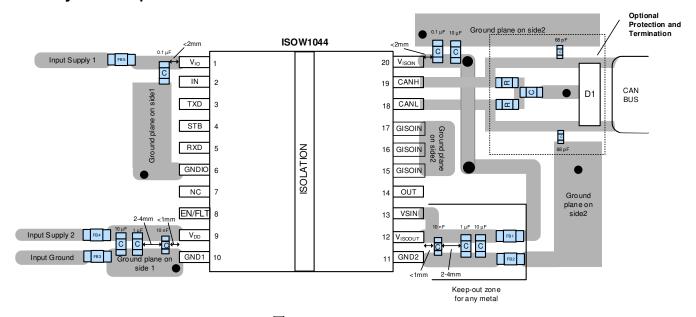

ISOW1044 器件是一款电隔离式控制器局域网 (CAN) 收发器,内置隔离式直流/直流转换器,无需在空间受 限的隔离式设计中使用单独的隔离式电源。低发射、隔 离式直流/直流转换器符合 CISPR 32 辐射发射 B 类标 准,在简单的两层 PCB 上仅使用两个铁氧体磁珠。额 外的 20mA 输出电流可用于为板上的其他电路供电。 该器件具有一个集成的 10Mbps GPIO 通道,有助于去 除额外用于诊断、LED 指示或电源监测的数字隔离器 或光耦合器。

####

| <b>奋</b> 竹作尽 |                                               |                                            |  |  |  |  |

|--------------|-----------------------------------------------|--------------------------------------------|--|--|--|--|

| 特性           | ISOW1044                                      | ISOW1044B                                  |  |  |  |  |

| 保护级别         | 增强型                                           | 基本型                                        |  |  |  |  |

| 浪涌测试电压       | 10kV <sub>PK</sub>                            | 7.8kV <sub>PK</sub>                        |  |  |  |  |

| 隔离额定值        | 5000V <sub>RMS</sub>                          | 5000V <sub>RMS</sub>                       |  |  |  |  |

| 工作电压         | 1000V <sub>RMS</sub> /1500<br>V <sub>PK</sub> | 1000V <sub>RMS</sub> /1500 V <sub>PK</sub> |  |  |  |  |

| 封装           | DFM (20)                                      | DFM (20)                                   |  |  |  |  |

| 封装尺寸(标称值)    | 12.83mm x 7.5mm                               | 12.83mm x 7.5mm                            |  |  |  |  |

简化版原理图

### **Table of Contents**

| 1 特性                                   | 1               | 10.2 Power Isolation                            | 21              |

|----------------------------------------|-----------------|-------------------------------------------------|-----------------|

| 2 应用                                   |                 | 10.3 Signal Isolation                           |                 |

| 3 说明                                   |                 | 10.4 CAN Transceiver                            | <mark>21</mark> |

| 4 Revision History                     |                 | 10.5 Functional Block Diagram                   | 23              |

| 5 说明(续)                                |                 | 10.6 Feature Description                        | <mark>23</mark> |

| 6 Device Comparison Table              |                 | 10.7 Device Functional Modes                    | <mark>27</mark> |

| 7 Pin Configuration and Functions      |                 | 10.8 Device I/O Schematics                      |                 |

| 8 Specifications                       |                 | 11 Application and Implementation               | 30              |

| 8.1 Absolute Maximum Ratings           |                 | 11.1 Application Information                    |                 |

| 8.2 ESD Ratings                        |                 | 11.2 Typical Application                        |                 |

| 8.3 Recommended Operating Conditions   |                 | 12 Power Supply Recommendations                 |                 |

| 8.4 ThermalInformation                 |                 | 13 Layout                                       |                 |

| 8.5 Power Ratings                      |                 | 13.1 Layout Guidelines                          |                 |

| 8.6 Insulation Specifications          | 7               | 13.2 Layout Example                             |                 |

| 8.7 Safety-Related Certifications      | 8               | 14 Device and Documentation Support             |                 |

| 8.8 Safety Limiting Values             |                 | 14.1 Documentation Support                      |                 |

| 8.9 Electrical Characteristics         |                 | 14.2 Receiving Notification of Documentation Up |                 |

| 8.10 Supply Current Characteristics    | 11              | 14.3 支持资源                                       |                 |

| 8.11 Switching Characteristics         | 12              | 14.4 Trademarks                                 |                 |

| 8.12 Insulation Characteristics Curves | 13              | 14.5 静电放电警告                                     |                 |

| 8.13 Typical Characteristics           | 14              | 14.6 术语表                                        | 36              |

| 9 Parameter Measurement Information    | 17              | 15 Mechanical, Packaging, and Orderable         |                 |

| 10 Detailed Description                | 21              | Information                                     | 36              |

| 10.1 Overview                          | <mark>21</mark> |                                                 |                 |

|                                        |                 |                                                 |                 |

## **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

## Changes from Revision \* (March 2021) to Revision A (December 2021)

Page

### 5 说明(续)

该器件支持传统 CAN 和 CAN FD 网络,数据速率高达 5 兆位/秒 (Mbps)。它提供 ±58V 直流总线故障保护功能和 ±12V 共模电压范围。信号和电源路径均按照 UL1577 进行 5kV<sub>RMS</sub> 隔离,并符合 VDE、CSA、TUV 和 CQC 的 增强型和基础型隔离要求。这些器件的总线引脚可承受高达 8kV 的 IEC 61000-4-2 静电放电 (ESD)。

ISOW1044 器件通过将 PCB 上的  $V_{IO}$  和  $V_{DD}$  连接到一起,可在 4.5V 至 5.5V 的单一电源电压下运行。如果需要较低的逻辑电平,这些器件支持 1.71V 至 5.5V 逻辑电源 ( $V_{IO}$ ),这些电源可与 4.5V 至 5.5V 的功率转换器电源 ( $V_{DD}$ ) 相互独立。这些器件支持从  $-40^{\circ}$ C 到 +125°C 的宽工作环境温度范围,并采用 20 引脚 DFM (SOIC-20 尺寸兼容封装),提供最小 8mm 的爬电距离和间隙。

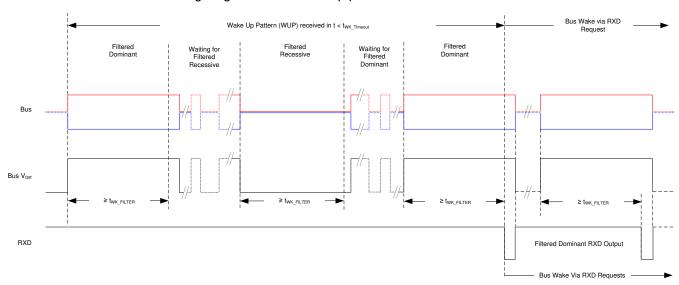

ISOW1044 支持待机模式,并且可通过符合 ISO 11898-2:2016 所定义唤醒模式 (WUP) 的 CAN 来唤醒。该器件还具有保护和诊断特性,支持热关断 (TSD)、TXD 显性超时 (DTO) 和电源欠压检测。

## **6 Device Comparison Table**

| PART NUMBER | ISOLATION  | PACKAGE       | BODY SIZE (NOM)   |

|-------------|------------|---------------|-------------------|

| ISOW1044    | Reinforced | 20-DFM (SOIC) | 12.83 mm x 7.5 mm |

| ISOW1044B   | Basic      | 20-DFM (SOIC) | 12.83 mm x 7.5 mm |

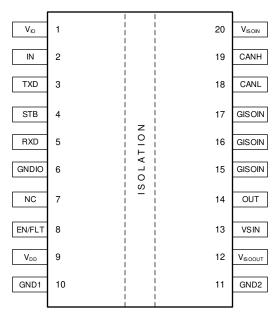

# 7 Pin Configuration and Functions

图 7-1. ISOW1044 20-pin DFM Top View

表 7-1. Pin Functions

| PIN                 |     | I/O | DECODIDATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|---------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| V <sub>IO</sub>     | 1   |     | Side 1 Logic supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| IN                  | 2   | I   | General purpose logic (GPIO) input (internal pull-down)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| TXD                 | 3   | I   | Driver enable. If this pin is floating, the driver is disabled (internal pull-down)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| STB                 | 4   | I   | Standby enable. Connect this pin to GNDIO in normal mode. If this pin is floating or logic high, driver is in standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| RXD                 | 5   | 0   | Receiver data output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| GNDIO               | 6   |     | Ground connection on side 1 for $V_{\text{IO}}$ . GNDIO and GND1 are not internally connected and need be shorted on PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| NC                  | 7   |     | Not connected internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

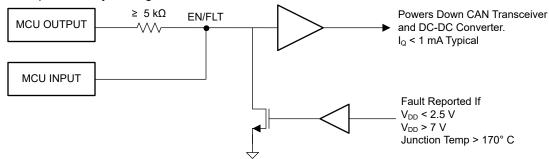

| EN/FLT              | 8   | I/O | <ul> <li>Multi-function power converter enable input pin or fault output pin. Can only be used as either an input pin or an output pin.</li> <li>If it's used as Power converter enable input pin, it enables and disables the integrated DC-DC power converter. Connect directly to microcontroller or through a series current limiting resistor to use as an enable input pin. DC-DC power converted is enabled when EN is high (connected to V<sub>IO</sub>) and disabled when low (connected to GND1). If EN is floating, DC-DC converter is enabled (internal pull-up resistor)</li> <li>If it's used as Fault output pin, it gives an alert signal if power converter is not operating properly. This pin is active low. Connect to microcontroller through a 5 k Ω or greater pull-up resistor in order to use as a fault outpin pin.</li> </ul> |  |  |

| $V_{DD}$            | 9   |     | Side 1 DC-DC converter power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| GND1                | 10  |     | Ground connections on side for $V_{\text{DD}}$ . GNDIO and GND1 are not internally connected and need be shorted on PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| GND2                | 11  |     | Ground connections on side for $V_{ISOOUT}$ . GND2 and GISOIN are not internally connected and need be shorted directly on PCB, or connected through a ferrite bead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| V <sub>ISOOUT</sub> | 12  |     | Isolated power converter output voltage. $V_{\text{ISOOUT}}$ and $V_{\text{ISOIN}}$ need be shorted directly on PCB, or connected through a ferrite bead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

## 表 7-1. Pin Functions (continued)

| P                  | PIN        |     | PIN I/O                                                                                                                                                 |  | DESCRIPTION |  |  |

|--------------------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| NAME               | NO.        | 1/0 | DESCRIPTION                                                                                                                                             |  |             |  |  |

| V <sub>SIN</sub>   | 13         | I   | Power converter input . Pin 12 and pin 13 need be shorted directly on PCB.                                                                              |  |             |  |  |

| OUT                | 14         | 0   | General purpose logic (GPIO) output (default output is low)                                                                                             |  |             |  |  |

| GISOIN             | 15, 16, 17 |     | Ground connections for V <sub>ISOIN</sub> . GND2 and GISOIN need be shorted directty on PCB, or connected through a ferrite bead.                       |  |             |  |  |

| CANL               | 18         | I/O | Low-level CAN bus line                                                                                                                                  |  |             |  |  |

| CANH               | 19         | I/O | High-level CAN bus line                                                                                                                                 |  |             |  |  |

| V <sub>ISOIN</sub> | 20         |     | Power supply input for CAN tranceiver. $V_{\text{ISOIN}}$ and $V_{\text{ISOOUT}}$ need be shorted directly on PCB, or connected through a ferrite bead. |  |             |  |  |

## 8 Specifications

## 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1) (2)

|                       |                                                           | MIN   | MAX                      | UNIT |

|-----------------------|-----------------------------------------------------------|-------|--------------------------|------|

| $V_{DD}$              | Power converter supply voltage                            | - 0.5 | 6                        | V    |

| V <sub>ISOIN</sub>    | Isolated supply voltage, input supply for CAN transceiver | - 0.5 | 6                        | V    |

| V <sub>ISOOUT</sub>   | Isolated supply voltage, Power converter output           | - 0.5 | 6                        | V    |

| V <sub>IO</sub>       | Logic supply voltage                                      | - 0.5 | 6                        | V    |

| V <sub>BUS</sub>      | Voltage on bus pins (CANH, CANL with respect to GND2)     | -58   | 58                       | V    |

| V <sub>BUS_DIFF</sub> | Max Differential voltage on bus pins (CANH-CANL)          | -45   | 45                       | V    |

| V                     | Logic I/O voltage level ( RXD, TXD, STB, EN, IN)          | - 0.5 | $V_{1O} + 0.5^{(3)}$     | V    |

| $V_{logic\_IO}$       | OUT                                                       | -0.5  | V <sub>ISOIN</sub> + 0.5 | V    |

| Io                    | Output current on RXD, OUT pins                           | - 15  | 15                       | mA   |

| T <sub>J</sub>        | Junction temperature                                      | - 40  | 150                      | °C   |

| T <sub>stg</sub>      | Storage temperature                                       | - 65  | 150                      | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the deviceat these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

- (2) All voltage values except differential I/O bus voltages are with respect to the local ground pin (GND1 or GND2). All voltage values except differential I/O bus voltages are peak voltage values.

- (3) The maximum voltage must not be greater than 6 V.

## 8.2 ESD Ratings

|                    |                         |                                                                                                |                                                | VALUE  | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------|--------|------|

|                    | Electrostatic           | Human body model (HBM), per ANSI/                                                              | All pins except bus pins                       | ±2000  |      |

| V <sub>(ESD)</sub> | discharge               | ESDA/JEDEC JS-001 <sup>(1)</sup>                                                               | CANH, CANL Bus pins w.r.t<br>GND2(pin15/16/17) | ±12000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC                                                          | C specification JESD22-C101 <sup>(2)</sup>     | ±1500  | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | per IEC61000-4-2 contact discharge,<br>CANH and CANL w.r.t. GND2                               |                                                | ±8000  | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | per IEC61000-4-2 contact discharge,<br>CANH and CANL w.r.t. GND1 (across<br>Isolation barrier) |                                                | ±8000  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD controlprocess.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         |                                          |                                   | MIN  | NOM  | MAX  | UNIT |

|-------------------------|------------------------------------------|-----------------------------------|------|------|------|------|

| V                       | Logic cupply voltage                     | 1.8-V operation                   | 1.71 |      | 1.89 | V    |

| V <sub>IO</sub>         | Logic supply voltage                     | 2.5-V, 3.3-V, and 5.5-V operation | 2.25 |      | 5.5  | v    |

| $V_{DD}$                | Power converter supply voltage           |                                   | 4.5  |      | 5.5  | V    |

| V <sub>DD(UVLO+)</sub>  | Supply threshold when Power converte     | er supply is rising               |      | 2.7  | 2.95 | V    |

| V <sub>DD(UVLO-)</sub>  | Supply threshold when Power converte     | er supply is falling              | 2.40 | 2.55 |      | V    |

| V <sub>HYS1(UVLO)</sub> | Power converter supply voltage hyster    | esis                              | 0.15 | 0.24 |      | V    |

| V <sub>IO(UVLO+)</sub>  | Rising threshold of Logic supply voltag  | е                                 |      |      | 1.7  | V    |

| V <sub>IO(UVLO-)</sub>  | Falling threshold of Logic supply voltag | le                                | 1    |      |      | V    |

| V <sub>HYS2(UVLO)</sub> | Logic supply voltage hysteresis          |                                   | 75   | 125  |      | mV   |

over operating free-air temperature range (unless otherwise noted)

| _                 |                                                                                                                                                                   | ·                             | MIN                   | NOM MAX               | UNIT |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|-----------------------|------|

| V <sub>IH</sub>   | High-level input voltage (TXD, STB, EN                                                                                                                            | I, and IN inputs)             | 0.7 × V <sub>IO</sub> | V <sub>IO</sub>       | V    |

| V <sub>IL</sub>   | Low-level input voltage (TXD, STB, EN                                                                                                                             | , and IN inputs)              | 0                     | 0.3 × V <sub>IO</sub> | V    |

|                   |                                                                                                                                                                   | V <sub>IO</sub> = 5V          | -4                    |                       | mA   |

| I <sub>OH</sub>   | High-level output current RXD                                                                                                                                     | V <sub>IO</sub> = 3.3V        | -2                    |                       | mA   |

|                   |                                                                                                                                                                   | V <sub>IO</sub> = 1.8 or 2.5V | -1                    |                       | mA   |

|                   |                                                                                                                                                                   | V <sub>IO</sub> = 5V          |                       | 4                     | mA   |

| I <sub>OL</sub>   | Low-level output current RXD                                                                                                                                      | V <sub>IO</sub> = 3.3V        |                       | 2                     | mA   |

|                   |                                                                                                                                                                   | V <sub>IO</sub> = 1.8 or 2.5V |                       | 1                     | mA   |

| I <sub>OH</sub>   | High-level output current OUT                                                                                                                                     | V <sub>DD</sub> =4.5 to 5.5V  | -4                    |                       | mA   |

| I <sub>OL</sub>   | Low-level output current OUT                                                                                                                                      | V <sub>DD</sub> =4.5 to 5.5V  |                       | 4                     | mA   |

| 1/t <sub>UI</sub> | Signaling rate                                                                                                                                                    | CAN                           |                       | 5                     | Mbps |

| DR                | Data rate for extra GPIO channel                                                                                                                                  | GPIO                          |                       | 10                    | Mbps |

| Tpwrup            | Power up time after applying input support of setpoint and data transmission can set of setpoint and data transmission can set of setpoint and data transmission. |                               |                       | 5                     | ms   |

| _                 | A b i b                                                                                                                                                           | ≤ 50% of bits are dominant    | - 40                  | 125                   | °C   |

| T <sub>A</sub>    | Ambient operating temperature                                                                                                                                     |                               | - 40                  | 105                   | °C   |

## 8.4 ThermalInformation

|                        |                                              | ISOW1044 |      |

|------------------------|----------------------------------------------|----------|------|

|                        | THERMAL METRIC(1)                            | DFM      | UNIT |

|                        |                                              | 20 PINS  |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 68.5     | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 20.9     | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 44.8     | °C/W |

| Ψ <sub>JT</sub>        | Junction-to-top characterization parameter   | 13       | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 44       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance |          | °C/W |

<sup>(1)</sup> For more informationabout traditional and new thermal metrics, see the Semiconductor and Package Thermal Metrics application report.

## 8.5 Power Ratings

|                 | PARAMETER                              | TEST CONDITIONS                                                                                       | MIN | TYP | MAX  | UNIT |

|-----------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| $P_D$           | Maximum power dissipation (both sides) | $V_{IO} = V_{DD} = 5.5 \text{ V}$ , STB= GND1, CAN Bus load                                           |     |     | 1060 | mW   |

| P <sub>D1</sub> | Maximum power dissipation (side-1)     | $R_L = 60 \Omega$ , TXD=repetitive pattern of 1 ms time period with 990 µs LOW time, 10 µs HIGH time, |     |     | 490  | mW   |

| P <sub>D2</sub> | Maximum power dissipation by (side-2)  | Extra load on V <sub>ISOOUT</sub> = 20 mA                                                             |     |     | 570  | mW   |

Product Folder Links: ISOW1044

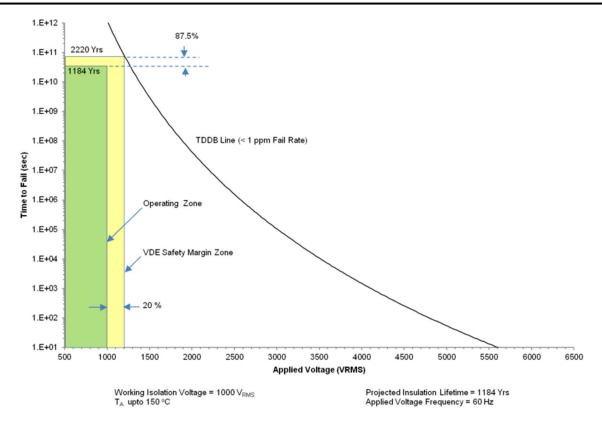

### 8.6 Insulation Specifications

|                   | PARAMETER                                                | TEST CONDITIONS                                                                                                                                                                                                                                            | VALUE              | UNIT             |

|-------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|

| GENERA            | L                                                        |                                                                                                                                                                                                                                                            |                    |                  |

| CLR               | External clearance <sup>(1)</sup>                        | Shortest terminal-to-terminal distance through air                                                                                                                                                                                                         | >8                 | mm               |

| CPG               | External creepage <sup>(1)</sup>                         | Shortest terminal-to-terminal distance across the package surface                                                                                                                                                                                          | >8                 | mm               |

| DTI               | Distance through the insulation                          | Minimum internal gap (internal clearance - capacitive signal isolation)                                                                                                                                                                                    | >17                | um               |

| DTI               | Distance through the insulation                          | Minimum internal gap (internal clearance- transformer power isolation)                                                                                                                                                                                     | >120               | um               |

| CTI               | Comparative tracking index                               | IEC 60112; UL 746A                                                                                                                                                                                                                                         | >600               | V                |

|                   | Material group                                           | According to IEC 60664-1                                                                                                                                                                                                                                   | 1                  |                  |

|                   | Output the second                                        | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                                                                 | I-IV               |                  |

|                   | Overvoltage Category                                     | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                                                                                                | I-III              |                  |

| DIN VDE           | V 0884-11:2017-01 <sup>(2)</sup>                         |                                                                                                                                                                                                                                                            |                    | _                |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage                | AC voltage (bipolar)                                                                                                                                                                                                                                       | 1500               | V <sub>PK</sub>  |

| V <sub>IOWM</sub> | Maximum working isolation voltage                        | AC voltage (sine wave) Time dependent dielectric breakdown (TDDB) test                                                                                                                                                                                     | 1000               | V <sub>RMS</sub> |

|                   |                                                          | DC voltage                                                                                                                                                                                                                                                 | 1500               |                  |

| V <sub>IОТМ</sub> | Maximum transient isolation voltage                      | $V_{TEST} = V_{IOTM}$ , t = 60s (qualification);<br>$V_{TEST} = 1.2 \times V_{IOTM}$ , t = 1s (100% production)                                                                                                                                            | 7071               | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage ISOW1044 <sup>(3)</sup>  | Test method per IEC 62368-1, 1.2/50 $\mu$ s waveform, $V_{TEST} = 1.6 \times V_{IOSM} = 10000 V_{PK}$ (qualification)                                                                                                                                      | 6250               | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage ISOW1044B <sup>(3)</sup> | Test method per IEC 62368-1, 1.2/50 µs waveform,<br>V <sub>TEST</sub> = 1.3 × V <sub>IOSM</sub> = 7800 V <sub>PK</sub> (qualification)                                                                                                                     | 6000               | V <sub>PK</sub>  |

|                   |                                                          | Method a: After I/O safety test subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60 \text{ s}$ ; $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_{m} = 10 \text{ s}$                                                                                                 | ≤5                 |                  |

| A <sub>pd</sub>   | Apparent charge <sup>(4)</sup>                           | Method a: After environmental tests subgroup 1, $V_{ini} = V_{IOTM}, t_{ini} = 60 \text{ s}; \\ ISOW1044: V_{pd(m)} = 1.6 \times V_{IORM}, t_m = 10 \text{ s. ISOW1044B:} \\ V_{pd(m)} = 1.2 \times V_{IORM}, t_m = 10 \text{ s}$                          | ≤5                 | pC               |

|                   |                                                          | Method b1: At routine test (100% production) and preconditioning (type test) $V_{ini} = 1.2 \times V_{IOTM}, \ t_{ini} = 1 \ s;$ ISOW1044: $V_{pd(m)} = 1.875 \times V_{IORM}, \ t_m = 1 \ s.$ ISOW1044B: $V_{pd(m)} = 1.5 \times V_{IORM}, \ t_m = 1 \ s$ | ≤5                 |                  |

| C <sub>IO</sub>   | Barrier capacitance, input to output <sup>(5)</sup>      | V <sub>IO</sub> = 0.4 sin (2 π ft), f = 1 MHz                                                                                                                                                                                                              | ~3.5               | pF               |

|                   |                                                          | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                             | > 10 <sup>12</sup> | Ω                |

| R <sub>IO</sub>   | Isolation resistance, input to output <sup>(5)</sup>     | $V_{IO}$ = 500 V, 100°C $\leqslant$ $T_A \leqslant$ 125°C                                                                                                                                                                                                  | > 10 <sup>11</sup> | Ω                |

|                   |                                                          | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                                                                                          | > 10 <sup>9</sup>  | Ω                |

|                   | Pollution degree                                         |                                                                                                                                                                                                                                                            | 2                  |                  |

|                   | Climatic category                                        |                                                                                                                                                                                                                                                            | 40/125/21          |                  |

| UL 1577           |                                                          |                                                                                                                                                                                                                                                            |                    |                  |

| V <sub>ISO</sub>  | Withstand isolation voltage                              | $V_{TEST} = V_{ISO}$ , t = 60 s (qualification); $V_{TEST} = 1.2 \times V_{ISO}$ , t = 1 s (100% production)                                                                                                                                               | 5000               | V <sub>RMS</sub> |

| * 180             | Thatoland Isolation Voltage                              | = 1 s (100% production)                                                                                                                                                                                                                                    | 3000               |                  |

- (1) Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of theisolator on the printed-circuit board do not reduce this distance. Creepage and clearance on aprinted-circuit board become equal in certain cases. Techniques such as inserting grooves and/orribs on a printed circuit board are used to help increase these specifications.

- (2) This coupler is suitable for safe electrical insulation (ISOW1044) and basic electrical insulation (ISOW1044B) only within the maximum operating ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- (3) Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- (4) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (5) All pins on each side of the barrier tied together creating atwo-terminal device

Copyright © 2023 Texas Instruments Incorporated

## 8.7 Safety-Related Certifications

| VDE                                                                                                                                                                                                                                                | CSA                                                                                                                                                                                                                                                                                                                                                                                                                | UL                                                                 | TUV                                                                                                       | CQC                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Plan to certifiy according to DIN VDE V 0884-11 :2017-01                                                                                                                                                                                           | Plan to certifiy according to<br>IEC 62368-1, IEC 61010-1<br>and IEC 60601-1                                                                                                                                                                                                                                                                                                                                       | Plan to certifiy under UL<br>1577 Component<br>Recognition Program | Plan to certifiy according to GB4943.1-2011                                                               | Plan to certifiy ccording to EN<br>61010-1:2010/ A1:2019 and EN<br>62368-1:2014                                                                                                                             |

| Maximum transient isolation voltage 7071 V <sub>PK</sub> ; Maximum repetitive peak isolation voltage, 1500 V <sub>PK</sub> ; Maximum surge isolation voltage, ISOW1044: 6250 V <sub>PK</sub> (Reinforced), ISOW1044B: 6000 V <sub>PK</sub> (Basic) | Per CSA62368-1:19, IEC 62368-1:2018 Ed. 3, CSA 61010-1-12+A1 and IEC 61010-1 3rd Ed., ISOW1044 (Reinforced): 600 V <sub>RMS</sub> , ISOW1044B (Basic): 1000 V <sub>RMS</sub> maximum working voltage (pollution degree 2, material group I, ambient temperature 90 °C), 1 MOPP (Means of Patient Protection) per CSA 60601-1:14. IEC 60601-1 (ISOW1044 only) Ed.3+A1, 250 V <sub>RMS</sub> maximum working voltage | Single protection, 5000<br>V <sub>RMS</sub>                        | Reinforced insulation, Altitude ≤ 5000 m, Tropical Climate, 700 V <sub>RMS</sub> maximum working voltage. | ISOW1044 (Reinforced): 5000 V <sub>RMS</sub> reinforced insulation per EN 61010-1:2010/A1:2019 and EN 62368-1:2014 up to working voltage of 600 V <sub>RMS</sub> . ISOW1044B (Basic): 1000 V <sub>RMS</sub> |

| Certification planned                                                                                                                                                                                                                              | Certification planned                                                                                                                                                                                                                                                                                                                                                                                              | Certification planned                                              | Certification planned                                                                                     | Certification planned                                                                                                                                                                                       |

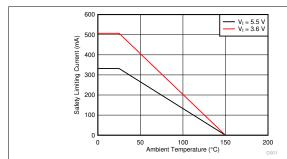

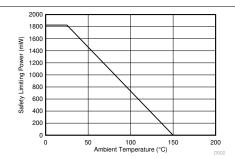

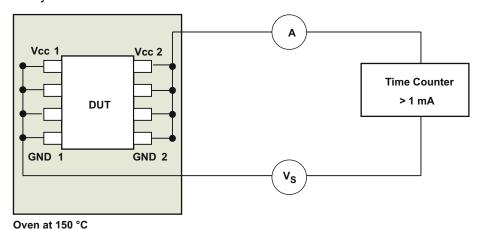

### 8.8 Safety Limiting Values

Safety limiting intends to minimize potential damage to the isolation barrier uponfailure of input or output circuitry.

|                | PARAMETER                                              | TEST CONDITIONS                                                                                                              | MIN | TYP | MAX  | UNIT                    |

|----------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------------------------|

|                | Safety input, output, or supply current <sup>(1)</sup> | R $_{\theta$ JA = 68.5 °C/W, V $_{I}$ = 5.5 V, T $_{J}$ = 150 °C, T $_{A}$ = 25 °C, See Figure 8-1                           |     |     | 332  | mA                      |

| Is             | Salety Input, output, or supply current                | R $_{0,\mathrm{JA}}$ = 68.5 °C/W, V $_\mathrm{I}$ = 3.6 V, T $_\mathrm{J}$ = 150 °C, T $_\mathrm{A}$ = 25 °C, See Figure 8-1 |     |     | 507  | IIIA                    |

| Ps             | Safety input, output, or total power <sup>(1)</sup>    | R $_{\theta}$ JA = 68.5 °C/W, T $_{J}$ = 150 °C, T $_{A}$ = 25 °C, See Figure 8-2                                            |     |     | 1826 | mA                      |

| T <sub>S</sub> | Safety temperature <sup>(1)</sup>                      |                                                                                                                              |     |     | 150  | $^{\circ}\! \mathbb{C}$ |

The maximum safety temperature,  $T_S$ , has the same value as the maximum junction temperature,  $T_J$ , specified for the device. The  $I_S$ and P<sub>S</sub> parameters represent the safety current and safety power respectively. The maximum limits of I<sub>S</sub> and P<sub>S</sub> should not

beexceeded. These limits vary with the ambient temperature,  $T_A$ . The junction-to-air thermal resistance,  $R_{\theta JA}$ , in the table is that of a device installed on a high-K test board forleaded surface-mount packages. Use these equations to calculate the value for each parameter:

$T_J = T_A + R_{\,0\,JA} \times P$ ,where P is the power dissipated in the device.  $T_{J(max)} = T_S = T_A + R_{\,0\,JA} \times P_S$ , where  $T_{J(max)}$  is the maximum allowed junction temperature.  $P_S = I_S \times V_I$ , where  $V_I$  is the maximum input voltage.

## **8.9 Electrical Characteristics**

over recommended operating conditions, typical values are at  $V_{DD}$  = 5V, GND1 = GNDIO, GND2 = GISOIN,  $V_{IO}$  = 3.3 V and  $T_{\Delta}$  =25°C (unless otherwise noted)

|                      | PARAMETER                                    | TEST CONDITIONS                                                                                                                 | MIN                                   | TYP                   | MAX  | UNIT |

|----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|------|------|

| Device               |                                              |                                                                                                                                 |                                       |                       |      |      |

| V <sub>ISOOUT</sub>  | Isolated Output supply voltage               | EN=V <sub>DD</sub> , STB, TXD, IN floating                                                                                      | 4.75                                  | 5                     | 5.25 | V    |

| lout                 | Extra current available on Visoout           | V <sub>DD</sub> = 4.5 to 5.5 V, CAN full loaded 60 Ω, TXD toggling 5 Mbps, IN toggling 10 Mbps                                  |                                       | 20                    |      | mA   |

| V <sub>OH</sub>      | Output high voltage on OUT pin               | V <sub>DD</sub> = 5 V ± 10%, I <sub>OH</sub> = -4 mA, IN = V <sub>IO</sub>                                                      | V <sub>ISOIN</sub> - 0.4              |                       |      | V    |

| V <sub>OL</sub>      | Output low voltage on OUT pin                | V <sub>DD</sub> = 5 V ± 10%, I <sub>OL</sub> = 4 mA, IN = GND2                                                                  |                                       |                       | 0.4  | V    |

| l <sub>1</sub>       | Input current, IN                            | IN at GND1 or V <sub>IO</sub>                                                                                                   | - 25                                  |                       | 25   | μA   |

| l <sub>l</sub>       | Input current, EN                            | EN at GND1 or V <sub>IO</sub>                                                                                                   | - 25                                  |                       | 25   | μA   |

| TXD TERM             | INAL                                         |                                                                                                                                 |                                       |                       |      |      |

| l <sub>1</sub>       | Input leakage current                        | TXD = V <sub>IO</sub> or GND1                                                                                                   | - 25                                  |                       | 25   | uA   |

| Cı                   | Input capacitance                            | VIN = $0.4 \times \sin(2 \times \pi \times 1E + 6 \times t) + 1.65 \text{ V},$<br>V <sub>IO</sub> = $3.3 \text{ V}$             |                                       | 2                     |      | pF   |

| RXD TERM             | IINAL                                        |                                                                                                                                 |                                       |                       | I.   |      |

|                      |                                              | $I_{O}$ = -4 mA for 4.5 V $\leqslant$ V $_{IO}$ $\leqslant$ 5.5 V, See $\cite{8}$ 9-4                                           | V <sub>IO</sub> - 0.4 \               | / <sub>IO</sub> - 0.2 |      | V    |

| ,                    |                                              | $I_{O}$ = -2 mA for 3.0 V $\leq$ V $_{IO}$ $\leq$ 3.6 V, See $\boxed{8}$ 9-4                                                    | V <sub>IO</sub> - 0.2 V <sub>IO</sub> | 0.06                  |      | V    |

| V <sub>OH</sub>      | High level output voltage                    | $I_{O}$ = -1 mA for 2.25 V $\leqslant$ V $_{IO}$ $\leqslant$ 2.75 V, See $\center{N}$ 9-4                                       | V <sub>IO</sub> - 0.1 V <sub>I</sub>  | o - 0.04              |      | V    |

|                      |                                              | $I_{O}$ = -1 mA for 1.71 V $\leq$ V $_{IO}$ $\leq$ 1.89 V, See $\boxtimes$ 9-4                                                  | V <sub>IO</sub> - 0.1 V <sub>I</sub>  | o - 0.04              |      | V    |

|                      |                                              | $I_{O}$ = 4 mA for 4.5 V $\leq$ V $_{IO}$ $\leq$ 5.5 V, See $\centure{2mm}$ 9-4                                                 |                                       | 0.2                   | 0.4  | ٧    |

| V <sub>OL</sub>      | Low level output voltage                     | $\rm I_O$ = 2 mA for 3.0 V $\leq \rm V_{IO} \leq$ 3.6 V, See § 9-4                                                              |                                       | 0.07                  | 0.2  | V    |

| v OL                 | Low level output voltage                     | $I_{O}$ = 1 mA for 2.25 V $\leqslant$ V $_{IO}$ $\leqslant$ 2.75 V, See $\centum{\centum{\color=100000in}{3}}$ 9-4              |                                       | 0.035                 | 0.1  | V    |

|                      |                                              | $I_{0}$ = 1 mA for 1.71 V $\leq$ V $_{IO}$ $\leq$ 1.89 V, See $\boxed{8}$ 9-4                                                   |                                       | 0.04                  | 0.1  | ٧    |

| STB Termi            | nal                                          |                                                                                                                                 |                                       |                       |      |      |

| lı .                 | Input leakage current                        | STB = V <sub>IO</sub> or GND1                                                                                                   | -25                                   |                       | 25   | uA   |

| Cı                   | Input capacitance                            | VIN = $0.4 \times \sin(2 \times \pi \times 1E + 6 \times t) + 1.65 \text{ V}$ , $V_{IO} = 3.3 \text{ V}$                        |                                       | 2                     |      | pF   |

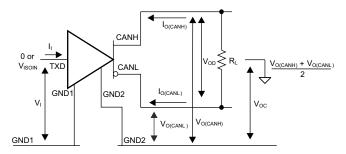

| DRIVER EL            | ECTRICAL CHARACTERISTIC                      | S                                                                                                                               |                                       |                       |      |      |

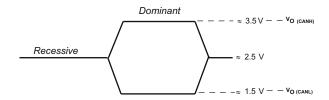

| v/                   | Bus output voltage(Dominant), CANH           | STB=GND1, TXD = 0 V, 50 $\Omega \leqslant R_L \leqslant$ 65 $\Omega$ , and $C_L$ = open, See $\[ \]$ 9-1and $\[ \]$ 9-2         | 2.75                                  |                       | 4.5  | V    |

| V <sub>O(DOM)</sub>  | Bus output voltage(Dominant), CANL           | STB=GND1, TXD = 0 V, 50 $\Omega \leqslant R_L \leqslant$ 65 $\Omega$ , and $C_L$ = open, See $\[ \]$ 9-1and $\[ \]$ 9-2         | 0.5                                   |                       | 2.25 | V    |

| V <sub>O(REC)</sub>  | Bus output voltage(recessive), CANH and CANL | STB=GND1, TXD = V <sub>IO</sub> and R <sub>L</sub> = open, See 图 9-1and 图 9-2                                                   | 2.0 0.5                               | x V <sub>ISOIN</sub>  | 3.0  | V    |

|                      | Differential output voltage(dominant)        | STB=GND1, TXD = 0 V, 45 $\Omega \leqslant R_L \leqslant 70$ $\Omega$ , and $C_L$ = open, See $\boxed{8}$ 9-1and $\boxed{8}$ 9-2 | 1.4                                   |                       | 3.3  | V    |

| V <sub>OD(DOM)</sub> | Differential output voltage(dominant)        | STB=GND1, TXD = 0 V, 50 $\Omega \le R_L \le 65$ $\Omega$ , and $C_L$ = open, See $\square$ 9-1and $\square$ 9-2                 | 1.5                                   |                       | 3.0  | V    |

| OD(DOW)              |                                              |                                                                                                                                 |                                       |                       |      |      |

over recommended operating conditions, typical values are at  $V_{DD}$  = 5V, GND1 = GNDIO, GND2 = GISOIN,  $V_{IO}$  = 3.3 V and  $T_A$  =25°C (unless otherwise noted)

|                         | PARAMETER                                                                             | TEST CONDITIONS                                                                                      | MIN     | TYP MAX | UNIT                |

|-------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------|---------|---------------------|

| \ /                     | Differential output voltage(recessive)                                                | TXD = VIO, $R_L$ = 60 $\Omega$ , and $C_L$ = open, See $\[ \]$ 9-1and $\[ \]$ 9-2                    | - 120.0 | 12.0    | mV                  |

| V <sub>OD(REC)</sub>    | Differential output voltage(recessive)                                                | TXD = VIO, R <sub>L</sub> = open, and C <sub>L</sub> = open, See 图 9-1and 图 9-2                      | - 50.0  | 50.0    | mV                  |

| V <sub>O(STB)</sub>     | Bus Output Voltage, CANH,<br>Standby mode                                             | STB = V <sub>IO,</sub> R <sub>L</sub> = open, See 图 9-1and 图 9-2                                     | - 100   | 100     | mV                  |

| V <sub>O(STB)</sub>     | Bus Output Voltage, CANL,<br>Standby mode                                             | STB = V <sub>IO</sub> , RL = open, See 图 9-1and 图 9-2                                                | - 100   | 100     | mV                  |

| V <sub>OD(STB)</sub>    | Bus Output Voltage, CANH-CANL, Standby mode                                           | STB=V <sub>IO</sub> , RL = open, See 图 9-1and 图 9-2                                                  | -200    | 200     | mV                  |

| V <sub>SYM_DC</sub>     | Output symmetry (V <sub>ISOIN</sub> - V <sub>O(CANL)</sub> )                          | $R_L$ = 60 $\Omega$ and $C_L$ = open, TXD = $V_{IO}$ or GND1, See $\boxed{8}$ 9-1and $\boxed{8}$ 9-2 | - 400.0 | 400.0   | mV                  |

| l                       | Short circuit current steady                                                          | -15 V < CANH < 40 V, CANL = open, and TXD = 0 V, See                                                 | - 115.0 |         | mA                  |

| l <sub>os(ss_dom)</sub> | state output current, dominant                                                        | -15 V < CANL < 40 V, CANH = open, and TXD = 0 V, See                                                 |         | 115.0   | mA                  |

| I <sub>OS(SS_REC)</sub> | Short circuit current steady state output current, recessive                          | -27 V < VBUS < 32 V, VBUS = CANH = CANL, and TXD = $V_{IO}$ , See $\[ \]$ 9-8                        | - 5.0   | 5.0     | mA                  |

| RECEIVER                | ELECTRICAL CHARACTERIS                                                                | rics                                                                                                 |         |         |                     |

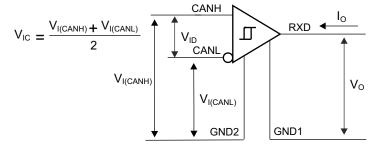

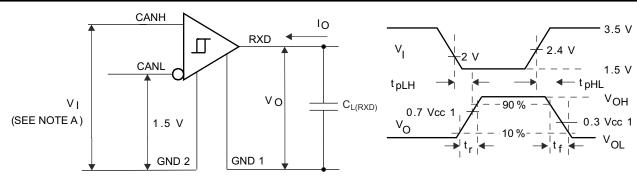

| V <sub>CM</sub>         | Input common mode range                                                               | See 图 9-4and 表 9-1                                                                                   | - 12    | 12      | V                   |

| V <sub>IT</sub>         | Differential input threshold voltage, normal mode                                     | -12 V $\leq$ V <sub>CM</sub> $\leq$ 12 V, STB = GND1, See 图 9-4and 表 9-1                             | 500.0   | 900.0   | mV                  |

| V <sub>IT(STB)</sub>    | Differential input threshold voltage, standby mode                                    | -12 V $\leq$ V <sub>CM</sub> $\leq$ 12 V, STB = V <sub>IO</sub>                                      | 400     | 1150    | mV                  |

| V <sub>HYS</sub>        | Hysteresis voltage for differential input threshold, normal mode                      | -12 V $\leq$ V <sub>CM</sub> $\leq$ 12 V, STB = GND1                                                 |         | 100     | mV                  |

| $V_{DIFF(DOM)}$         | Dominant state differential input voltage range, normal mode                          | -12 V $\leq$ V <sub>CM</sub> $\leq$ 12 V, STB = GND1, See 图 9-4and 表 9-1                             | 0.9     | 9       | ٧                   |

| $V_{DIFF(DOM)}$         | Dominant state differential input voltage range, standby mode                         | -12 V $\leq$ V <sub>CM</sub> $\leq$ 12 V, STB = V <sub>IO</sub> , See 图 9-4and 表 9-1                 | 1.15    | 9       | V                   |

| V <sub>DIFF(REC)</sub>  | Recessive state differential input voltage range, normal mode                         | -12 V $\leq$ V <sub>CM</sub> $\leq$ 12 V, STB = GND1, See 图 9-4and 表 9-1                             | - 4     | 0.5     | V                   |

| V <sub>DIFF(REC)</sub>  | Recessive state differential input voltage range, standby mode                        | -12 V ≤ V <sub>CM</sub> ≤ 12 V, STB = V <sub>IO</sub> , See 图<br>9-4and 表 9-1                        | - 4     | 0.4     | V                   |

| I <sub>OFF(LKG)</sub>   | power-off bus input leakage current                                                   | CANH = CANL = 5 V, V <sub>DD</sub> = V <sub>IO</sub> = GND1                                          |         | 5       | uA                  |

| Cı                      | Input capacitance to ground (CANH or CANL)                                            | TXD = V <sub>IO</sub>                                                                                |         | 20      | pF                  |

| C <sub>ID</sub>         | Differential input capacitance                                                        | $TXD = V_{IO}$                                                                                       |         | 10      | pF                  |

| R <sub>ID</sub>         | Differential input resistance                                                         | TXD = $V_{IO}$ ; -12 $V \le VCM \le +12 V$                                                           | 40      | 90      | $\mathbf{k} \Omega$ |

| R <sub>IN</sub>         | Input resistance (CANH or CANL)                                                       | TXD = $V_{10}$ ; -12 V $\leq$ VCM $\leq$ +12 V                                                       | 20      | 45      | kΩ                  |

| R <sub>IN(M)</sub>      | Input resistance matching: (1 - R <sub>IN(CANH)</sub> /R <sub>IN(CANL)</sub> ) x 100% | V <sub>CANH</sub> = V <sub>CANL</sub> = 5 V                                                          | - 1     | 1       | %                   |

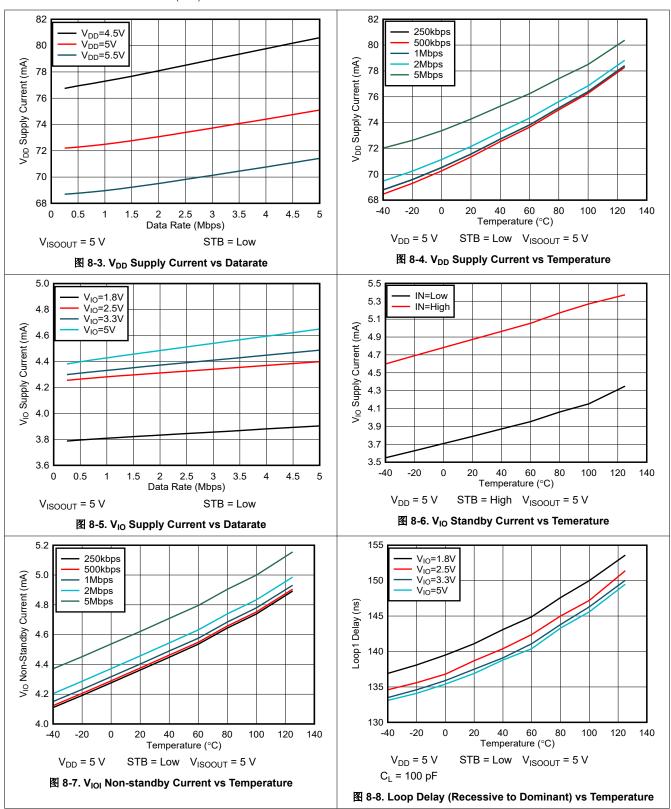

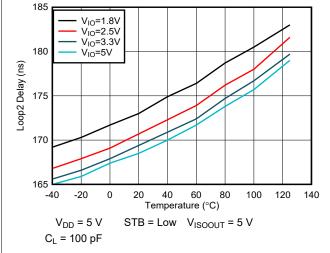

## **8.10 Supply Current Characteristics**

Typical values are at  $V_{DD}$ =5V,  $V_{IO}$ =3.3V, Min/Max over recommended operating conditions, GND1 = GNDIO, GND2 = GISOIN,  $V_{DD}$  = 4.5 V to 5.5 V(unless otherwise noted)

|                 | PARAMETER                      | TEST CONDITIONS                                                         | MIN | TYP  | MAX      | UNIT |

|-----------------|--------------------------------|-------------------------------------------------------------------------|-----|------|----------|------|

| Power           | converter disabled             |                                                                         |     |      | <u> </u> |      |

| I <sub>DD</sub> | Power converter supply current | EN = GND1, STB, TXD, IN floating                                        |     | 0.23 | 0.27     | mA   |

| I <sub>IO</sub> | Logic supply current           | EN = GND1, STB, TXD, IN floating                                        |     | 0.34 | 0.70     | mA   |

| Supply          | current: Normal Mode           |                                                                         |     |      |          |      |

| I <sub>DD</sub> | Power converter supply current | TXD = GND1, Bus dominant, $R_L$ = 60 $\Omega$                           |     | 124  | 211      | mA   |

| I <sub>DD</sub> | Power converter supply current | TXD = $V_{IO}$ , Bus recessive, $R_L = 60 \Omega$                       |     | 26   | 46       | mA   |

| I <sub>DD</sub> | Power converter supply current | TXD = 1Mbps 50% duty square wave, $R_L$ = 60 $\Omega$                   |     | 76   | 123      | mA   |

| I <sub>DD</sub> | Power converter supply current | TXD = 5 Mbps 50% duty square wave, $R_L$ = 60 $\Omega$                  |     | 78   | 136      | mA   |

| I <sub>IO</sub> | Logic supply current           | TXD = GND1, Bus dominant, V <sub>IO</sub> = 1.71 to 1.89 V              |     | 4.3  | 5.5      | mA   |

| I <sub>IO</sub> | Logic supply current           | TXD = GND1, Bus dominant, V <sub>IO</sub> = 2.25 to 5.5 V               |     | 4.9  | 6.0      | mA   |

| I <sub>IO</sub> | Logic supply current           | TXD = V <sub>IO</sub> , Bus recessive, V <sub>IO</sub> = 1.71 to 1.89 V |     | 3.3  | 5.4      | mA   |

| I <sub>IO</sub> | Logic supply current           | TXD = V <sub>IO</sub> , Bus recessive, V <sub>IO</sub> = 2.25 to 5.5 V  |     | 3.8  | 5.5      | mA   |

| I <sub>IO</sub> | Logic supply current           | TXD = 1 Mbps square wave 50% duty, V <sub>IO</sub> = 3 to 3.6V          |     | 4.4  | 5.3      | mA   |

| I <sub>IO</sub> | Logic supply current           | TXD = 5 Mbps square wave 50% duty, V <sub>IO</sub> = 3 to 3.6V          |     | 4.5  | 6.2      | mA   |

| Supply          | current: Standby mode          |                                                                         |     |      | •        |      |

| I <sub>DD</sub> | Power converter supply current | STB = $V_{IO}$ , $R_L = 60 \Omega$                                      |     | 16   | 23       | mA   |

| I <sub>IO</sub> | Logic supply current           | STB = V <sub>IO</sub> , V <sub>IO</sub> = 3 to 3.6 V                    |     | 2.7  | 3.5      | mA   |

## **8.11 Switching Characteristics**

Typical specifications are at  $V_{IO}$  = 3.3V,  $V_{DD}$  = 5V, GND1 = GNDIO, GND2 = GISOIN, Min/Max are over recommended operating conditions (unless otherwise noted)

|                            | conditions (unless otherwise noted)  PARAMETER                                                          | TEST CONDITIONS                                                                                                                                              | MIN | TYP | MAX | UNIT  |

|----------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| DEVICE S                   | SWITCHING CHARACTERISTICS                                                                               |                                                                                                                                                              |     |     |     |       |

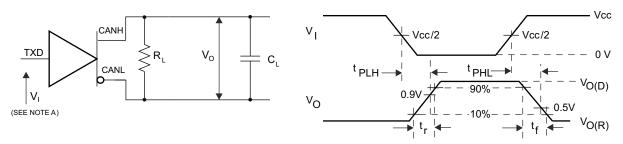

| t <sub>PROP(LOO</sub>      | Total loop delay, driver input TXD to receiver RXD, recessive to dominant                               | $R_L$ = 60 Ω, $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF;<br>input rise/fall time (10% to 90%) on TXD<br>= 1 ns; 1.71 V < V <sub>IO</sub> < 5.5 V, See $\[ \]$ 9-3 |     | 140 | 205 | ns    |

| t <sub>PROP(LOO</sub>      | Total loop delay, driver input TXD to receiver RXD, dominant to recessive                               | $R_L$ = 60 Ω, $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF; input rise/fall time (10% to 90%) on TXD =1 ns; 1.71 V < V <sub>IO</sub> <5.5 V, See $\boxed{8}$ 9-3     |     | 167 | 222 | ns    |

| t <sub>MODE</sub>          | Mode change time, from Normal to<br>Standby or from Standby to Normal                                   |                                                                                                                                                              |     |     | 20  | us    |

| t <sub>WK_FILTE</sub><br>R | Filter time for a valid wake-up pattern                                                                 |                                                                                                                                                              | 0.5 |     | 1.8 | us    |

| t <sub>WK_TIME</sub>       | Bus wake-up timeout value                                                                               |                                                                                                                                                              | 0.8 |     | 5   | ms    |

| CMTI                       | Common mode transient immunity                                                                          | TXD = V <sub>IO</sub> or GND1, V <sub>CM</sub> = 1200 V <sub>PK</sub> ,<br>See 图 9-9                                                                         | 85  | 100 |     | kV/µs |

| DRIVER S                   | SWITCHING CHARACTERISTICS                                                                               |                                                                                                                                                              |     |     |     |       |

| t <sub>pHR</sub>           | Propagation delay time, LOW to HIGH TXD edge to driver recessive (dominant to recessive)                |                                                                                                                                                              |     | 87  | 110 |       |

| t <sub>pLD</sub>           | Propagation delay time, HIGH TO LOW TXD edge to driver dominant (recessive to dominant)                 | $R_L$ = 60 $\Omega$ and $C_L$ = 100 pF; input rise/fall time (10% to 90%) on TXD =1 ns, See $\P$ 9-3                                                         |     | 78  | 105 | ns    |

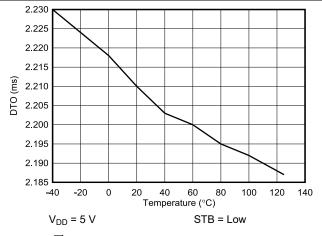

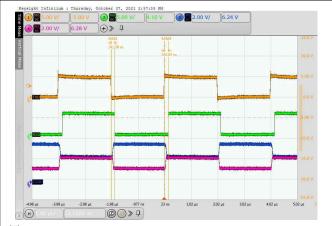

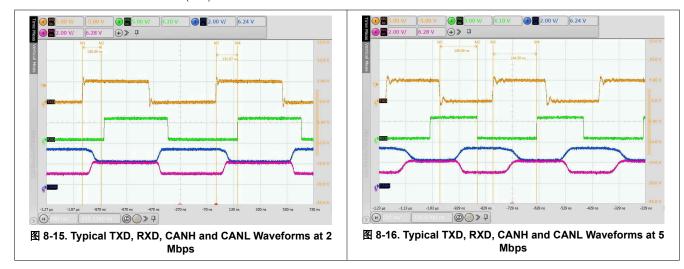

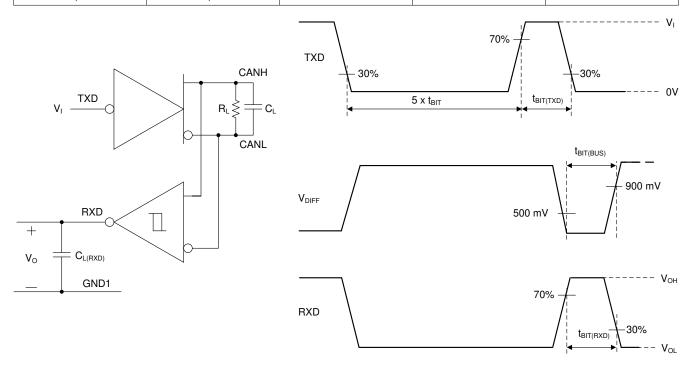

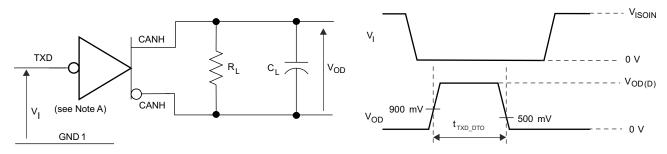

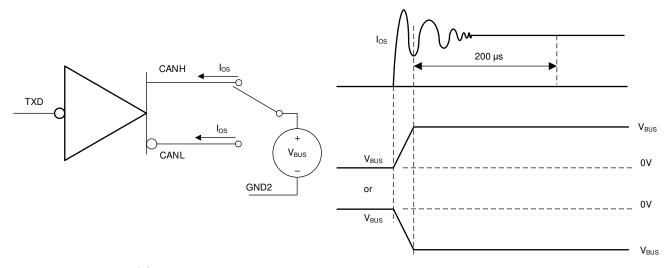

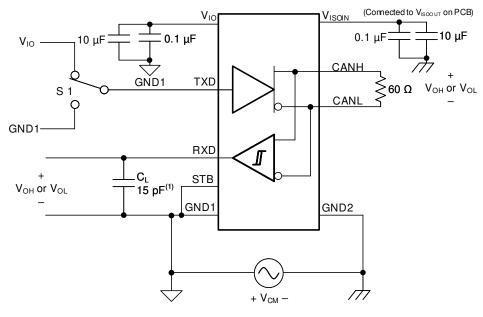

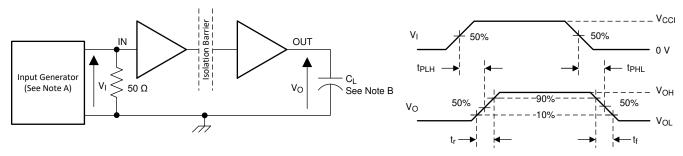

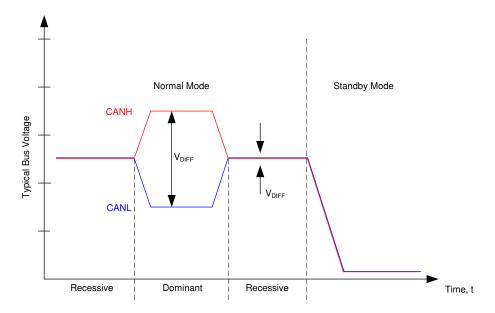

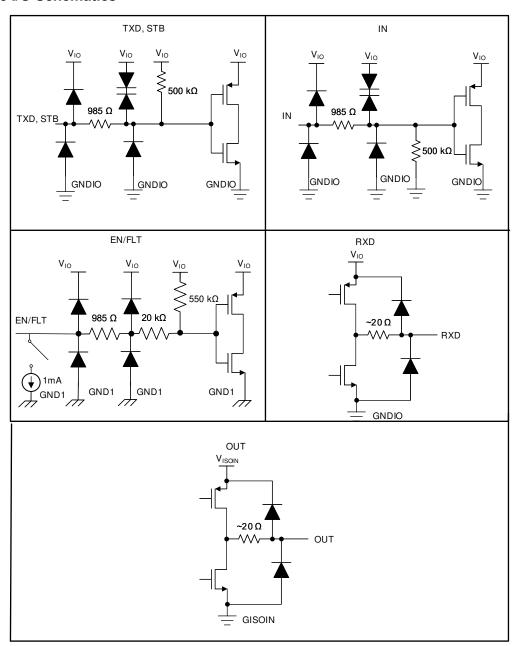

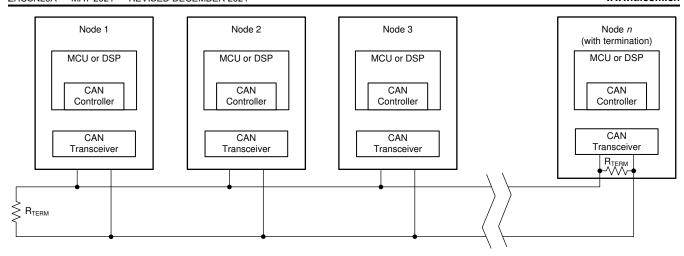

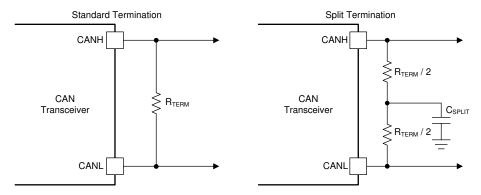

| t <sub>sk(p)</sub>         | pulse skew ( tpHR - tpLD )                                                                              |                                                                                                                                                              |     | 15  |     |       |