*Application Note*

# 使用 PSpice-for-TI 创建自动化 SPICE 设计

Carolina Walter

## 摘要

德州仪器 (TI) 提供两种 SPICE 仿真工具来帮助评估模拟电路的功能，即 TINA-TI 和 PSPICE-FOR-TI。TINA-TI 是一个灵活的程序，允许用户快速组装原理图并分析电路的响应。由于生态系统会记住所有后处理器设置（多个复杂的布线和公式），因此 PSpice®-for-TI 专为进行更大规模的电路分析而设计。

本文档提供了指导新用户的信息；本摘要中涉及的全部术语都将在后面定义。

确定仿真问题的过程后，只需设置一次 PSpice®-for-TI。电路、仿真配置文件、图和迹线的输出窗口设置以及关键测量值都保存到工程中。工程打开和重用越多，前期投资就越富有成效。

本应用手册讨论了如何创建自动化 SPICE 设计，从而确保运算放大器的稳定性。此过程可重复，用于任何依赖于 SPICE 且需要重复电路分析的评估。

## 内容

|                      |           |

|----------------------|-----------|

| <b>1 简介</b>          | <b>2</b>  |

| <b>2 可重复使用的原理图</b>   | <b>3</b>  |

| <b>3 创建一个工程</b>      | <b>4</b>  |

| 3.1 工程层次结构           | 5         |

| <b>4 原理图，用来提高可读性</b> | <b>6</b>  |

| 4.1 放置无源元件           | 6         |

| 4.2 参数               | 8         |

| 4.3 放置电源             | 11        |

| 4.4 接线               | 13        |

| 4.5 对用户体验进行管理        | 14        |

| <b>5 仿真配置文件设置</b>    | <b>16</b> |

| 5.1 帮助收敛             | 17        |

| 5.2 强大的后处理           | 19        |

| <b>6 总结</b>          | <b>27</b> |

| <b>7 参考资料</b>        | <b>29</b> |

## 商标

PSpice® and PSpice-for-TI® are registered trademarks of CADENCE DESIGN SYSTEMS, INC..

is a registered trademark of CADENCE DESIGN SYSTEMS, INC.

所有商标均为其各自所有者的财产。

## 1 简介

运算放大器的两个输入节点必须彼此相等，并且输出会相应地发生变化，以便实现这一点。当输出响应和反相反馈节点 (IN-) 之间存在引入延迟 (或相位滞后) 的元件时，输出会显示不稳定的振荡响应，尝试反复稳定至正确的值。

在图 1-1 中，预期响应为 100mV，但运算放大器的输出最初会过冲，然后进行过冲/欠冲校正，从而导致输出中出现振荡。

图 1-1. 运算放大器电路响应不稳定

反馈网络中通常引入相位滞后的一些方式是运算放大器的输出阻抗和容性负载，或运算放大器的输入电容和大反饋电阻。图 1-1 显示了导致不稳定的大容性负载示例。有关稳定性补偿理论的更多信息，请参阅 TI 高精度实验室培训：TIPL 稳定性视频系列。

稳定性补偿元件引入电路中以实现稳定的输出响应（相位裕度在  $45^\circ$  到  $90^\circ$  之间）。要找到合适的稳定性补偿值，必须对每个运算放大器和电路配置执行以下操作：

1. 在[伪开环配置](#)中构建仿真原理图。

2. 运行交流扫描。

3. 绘制电路的开环增益及相位图并测量相位裕度。

4. 使用频率响应中的参数来计算补偿值。

5. 实施补偿值并重新运行交流扫描以查看是否实现了所需相位裕度 ( $45^\circ$  至  $90^\circ$ )。

此过程需要大量的后处理计算及交流扫描重新运行。PSpice-for-TI® 通过记住输出窗口图的设置、相位裕度等关键测量值以及用于使用频率响应和原理图中的参数确定补偿值的公式，简化了这一过程。本文档介绍了如何使用在 PSpice-for-TI® 中内置的自动化设计，解决这一可重复问题。

## 2 可重复使用的原理图

确定可重复过程后，下一步是找到适用于大多数电路配置的原理图配置。

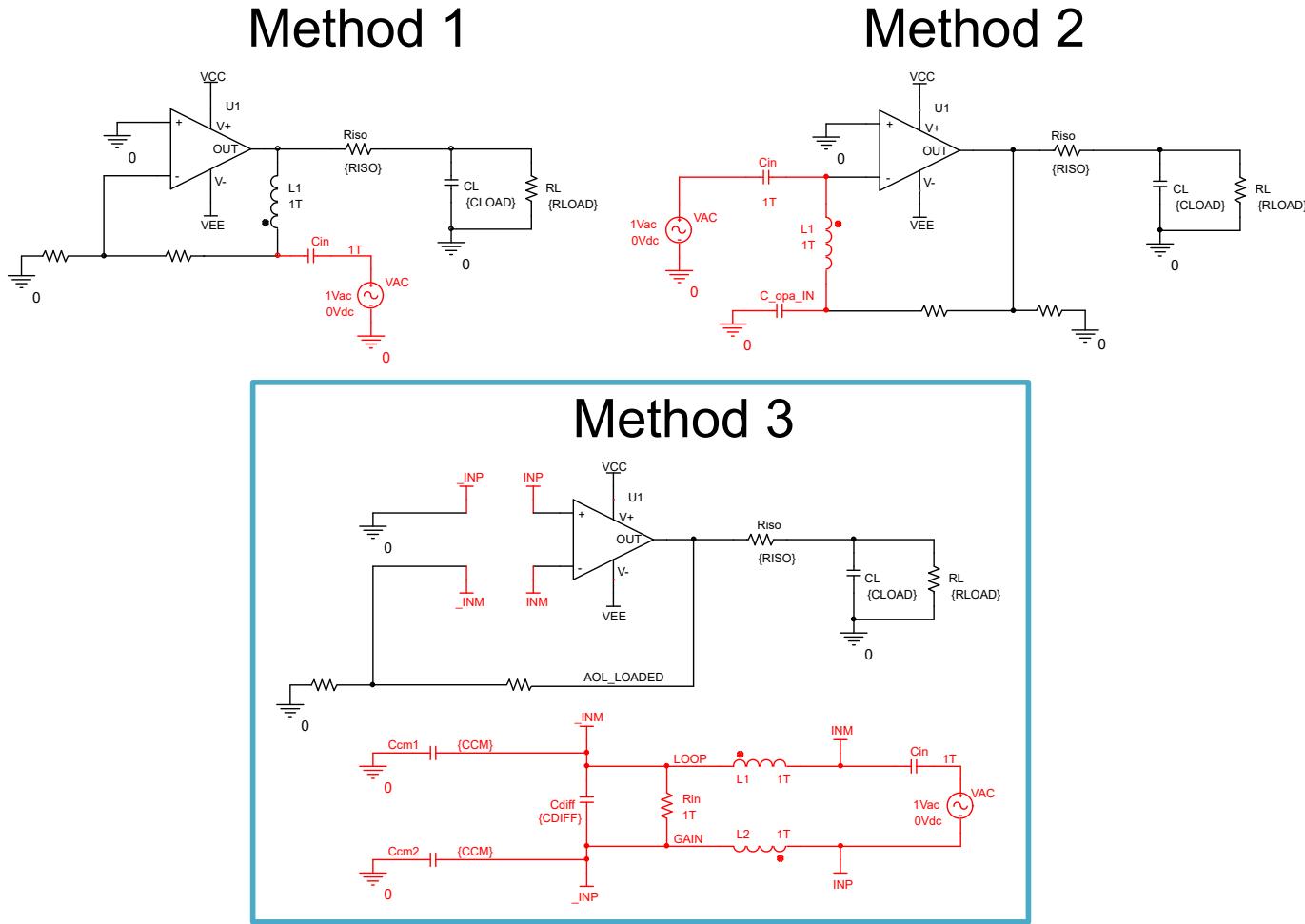

在此示例中，运算放大器最稳健的开环配置是方法 3 中所示的双断环路配置，其中考虑了运算放大器到反馈网络的输出阻抗与反馈网络之间的相互作用（方法 1 的缺点）；以及反馈网络与输入的寄生阻抗之间的相互作用（方法 2 的缺点）。

图 2-1. 运算放大器电路的伪开环配置方法

方法 3 是 PSpice®-for-TI 可重用性的首选，因为主要缺点是设置中原理图的复杂性。有关此方法的更多信息，请参阅 [ti.com](#) 上的“断开差分放大器上的环路”视频。

### 3 创建一个工程

本文档中的说明假设用户是 Cadence 环境新手，并从头开始逐步完成自动工程的创建。

如果用户之前已在 PSpice®-for-TI 中创建了工程和原理图，则可以选择跳转到 [节 4.5](#)。

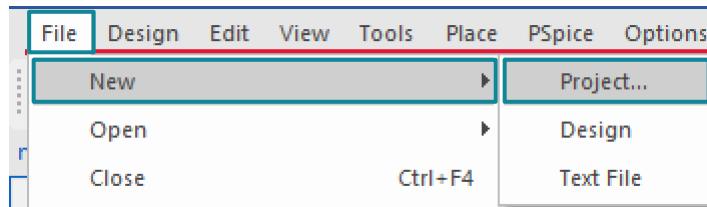

可以通过 *File > New > Project* 创建新工程。

图 3-1. 新工程选择

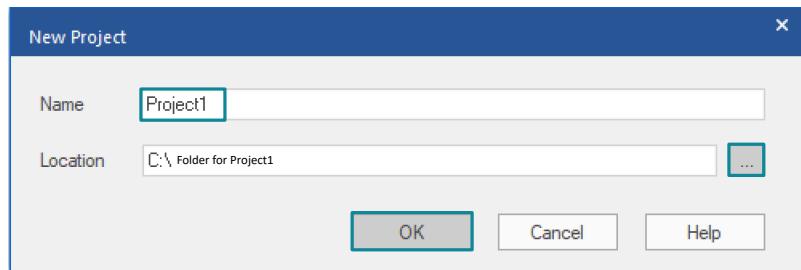

为新工程选择一个位置和名称，然后点击 *OK* 继续。为获得最佳实践，每个 PSpice®-for-TI 工程都将放置在新的文件夹中。

图 3-2. 新工程创建

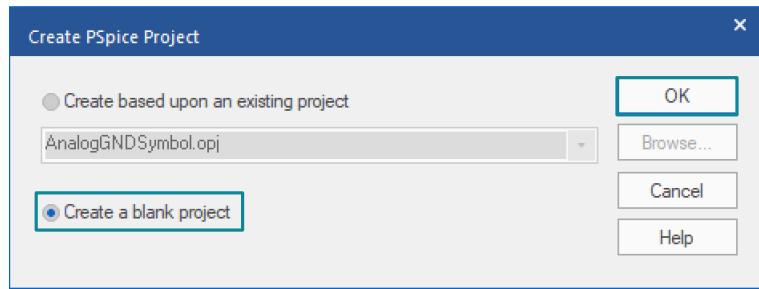

出现提示时，选择 *Create a blank project*，然后选择 *OK* 继续。请注意，基于现有工程创建有助于开发多个自动化工程；但这超出了本应用手册的范围。

图 3-3. 工程模板选择

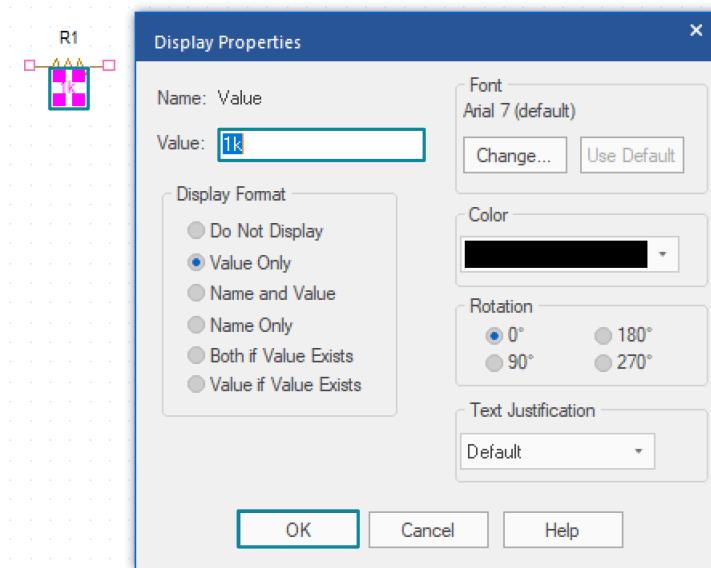

### 3.1 工程层次结构

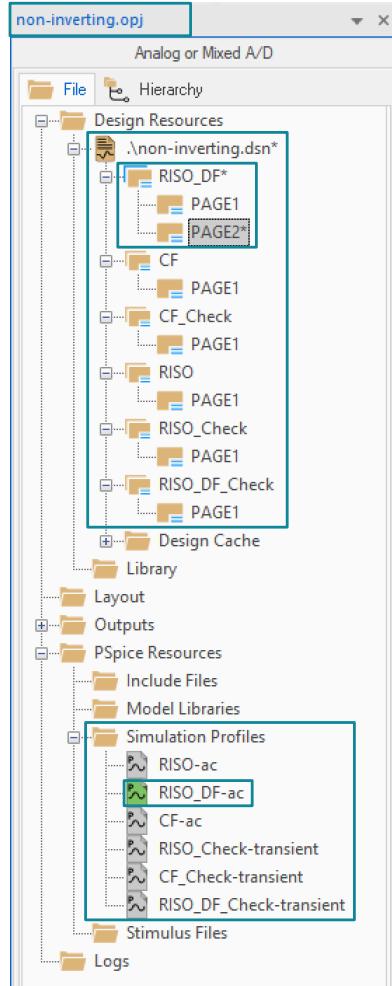

Cadence 环境包括一个工程 (.opj) , 其中包含可以具有多个原理图的设计 (.dsn)。每个原理图可以包含多个页面 , 并且可以具有多个关联的仿真配置文件。

在图 3-4 中所示的示例中 , *non-inverting.opj* 是一个包含设计文件 *non-inverting.dsn* 的工程。该设计文件包含六个原理图 , 其中 *RISO\_DF* 包含两个原理图页面 , 并具有一个标记为 *RISO\_DF\_AC* 的交流仿真配置文件。

图 3-4. 工程层次结构

## 4 原理图，用来提高可读性

PSpice®-for-TI 的原理图编辑器中有一些最佳实践，可让更多读者便利地使用。以下步骤讨论了如何组装可由多个用户读取的原理图，因此必须非常直观。

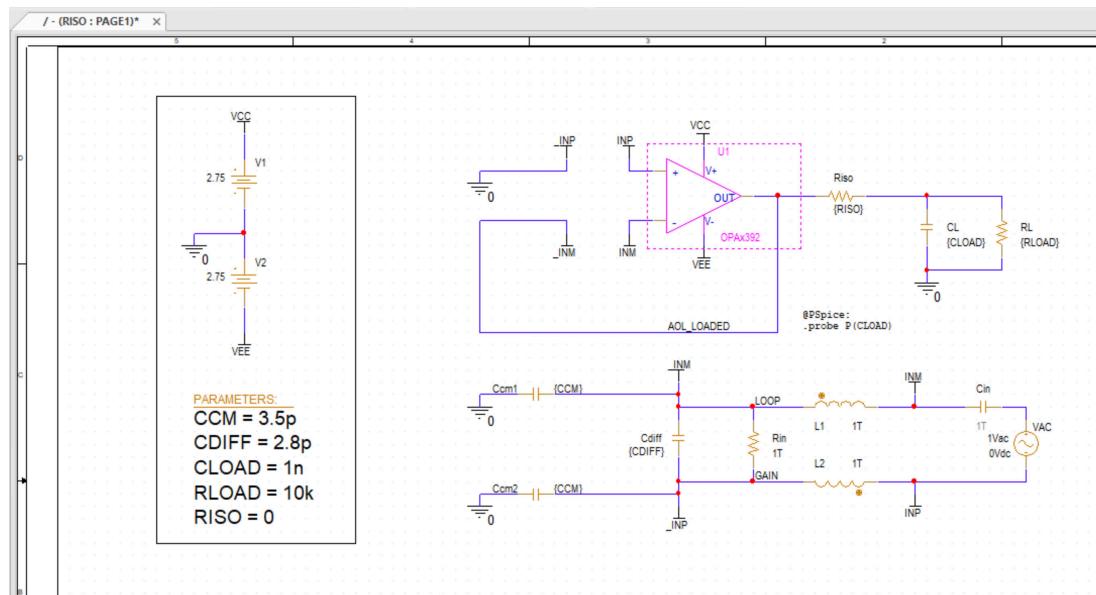

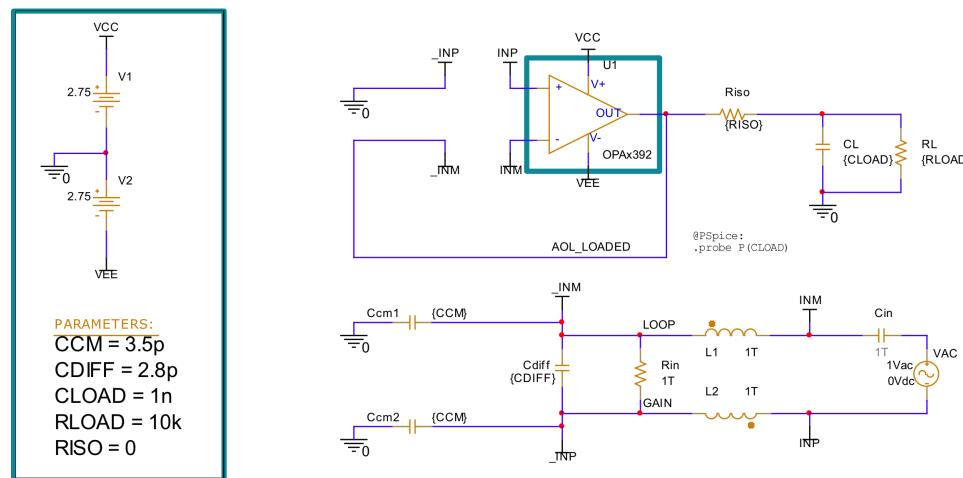

图 4-1. 最终原理图

### 4.1 放置无源元件

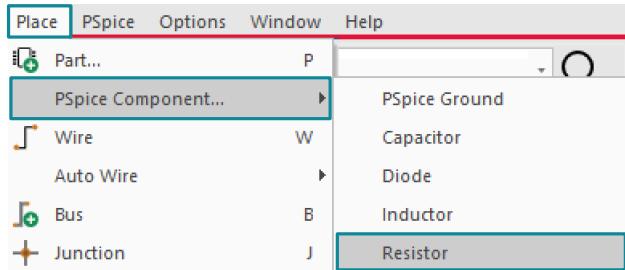

通过在 *Place > PSpice Component* 中导航并选择相关元件，可以放置无源元件。在图 4-2 中所示的示例里，在原理图中放置了一个电阻器。

图 4-2. 放置电阻器

图 4-3 显示了 R1 (之前放置的元件)、R2 (最后放置的元件，以粉色突出显示) 和悬空未命名元件 (鼠标所在)。按 *ESC* 键可停止放置多个元件。

图 4-3. 多种放置方式

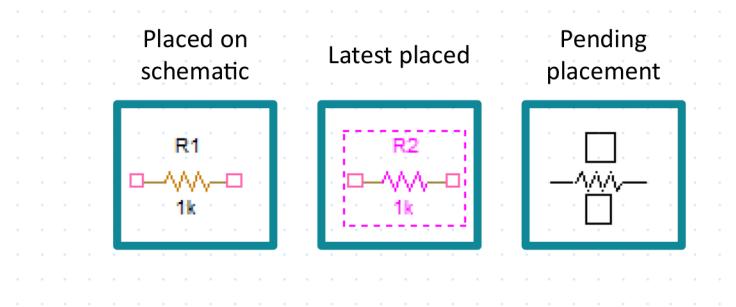

放置后，可以通过双击值来编辑元件值。

图 4-4. 更改单个值

键入新值并选择确定以实现。

## 4.2 参数

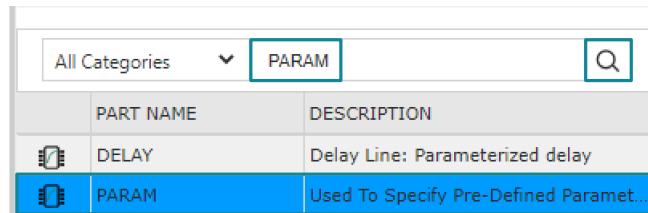

如果某个变量用于很多位置，则可以在原理图中将该变量作为参数来实现。通过 PSpice® 器件搜索（内置库）（可通过 *Place > PSpice Component... > Search...* 访问），搜索 PARAM 并双击以放置在原理图上。

图 4-5. 变量的“PARAM”

按“**ESC**”可停止多个放置。**图 4-6** 显示了放置在原理图上的 **PARAM** 元件。

## PARAMETERS:

图 4-6. 原理图上的 **PARAM** 元件

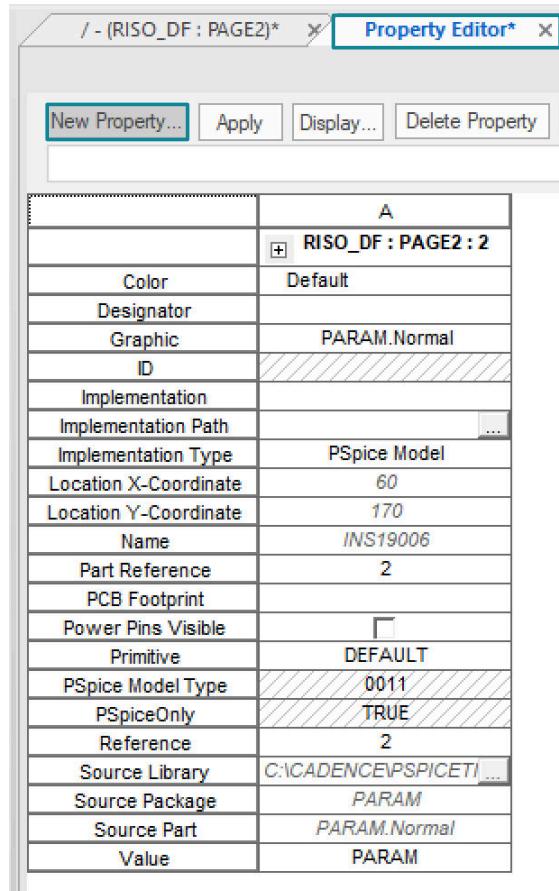

放置后，双击 **PARAMETERS** 元件以在另一个选项卡中打开属性编辑器。（可选）要以垂直方式显示属性（如**图 4-7** 中所示），请选择 **Pivot**。

图 4-7. **PARAM** 的属性编辑器

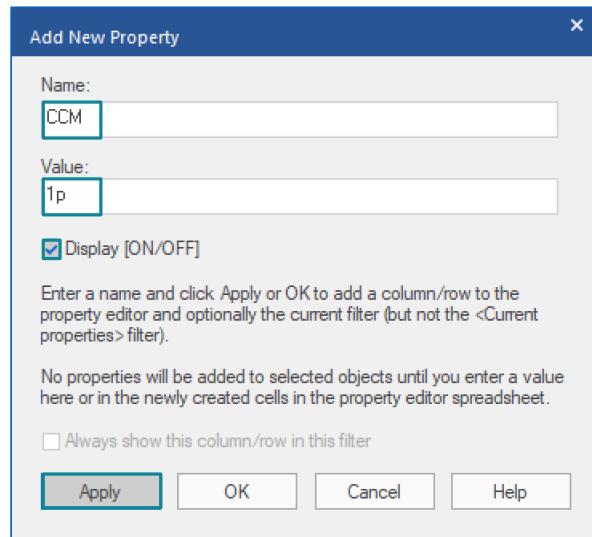

选择 **New Property...** 并为参数选择名称和默认值，如**图 4-8** 中所示。选中 **Display [On/Off]** 复选框以在原理图中显示新参数。选择 **Apply** 以继续添加多个参数。或者，选择 **OK** 只添加一个参数。

图 4-8. 将新属性添加到 **PARAM**

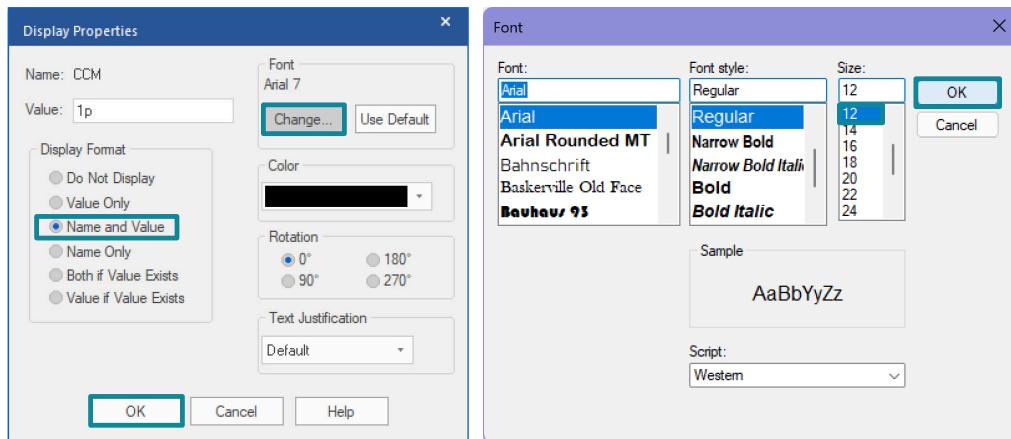

选择 **Display [ON/OFF]**，允许用户选择显示设置。将 **Display Format** 选择为 **Name and Value**。在投影仪上显示时，默认的字体和大小 Arial 7 很小。对于自动化工程，如果使用较大的字体实现，则在原理图中很容易找到常用参数。在图 4-9 所示的示例中，选择了字体大小 12。

图 4-9. 参数的显示及大小

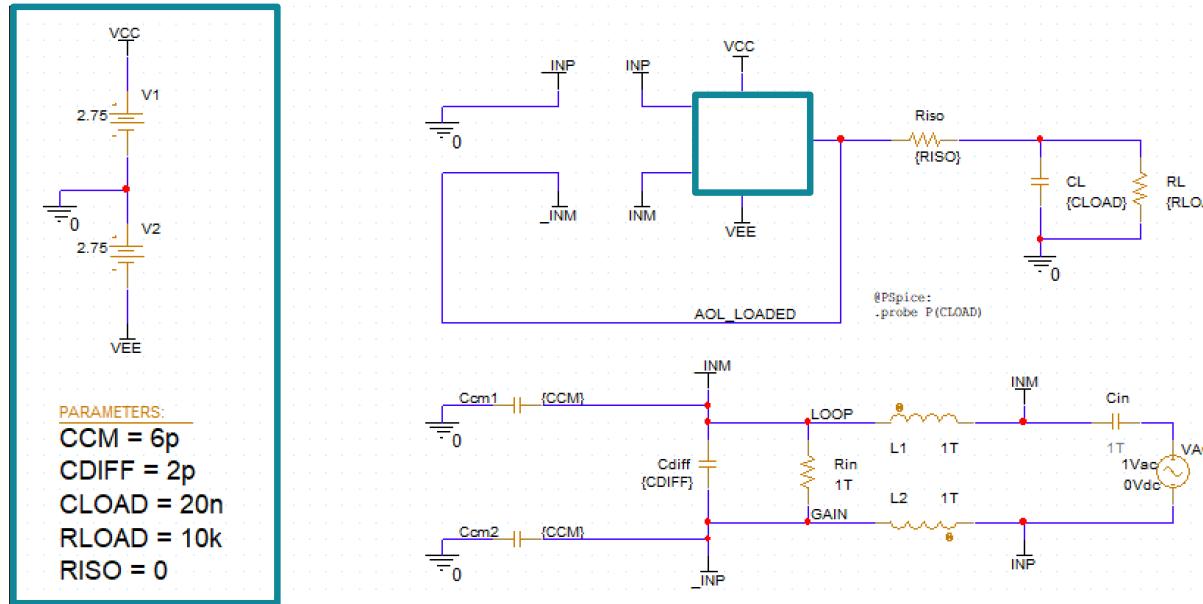

如前所述，如果添加多个参数，请选择 **Apply** 并根据需要创建任意数量的新参数。图 4-10 显示了添加的不同参数以及每个参数的默认值。

#### PARAMETERS:

**CCM = 1p**

**CDIFF = 3p**

**CLOAD = 1u**

**RLOAD = 10k**

**RISO = 0**

图 4-10. 多个参数

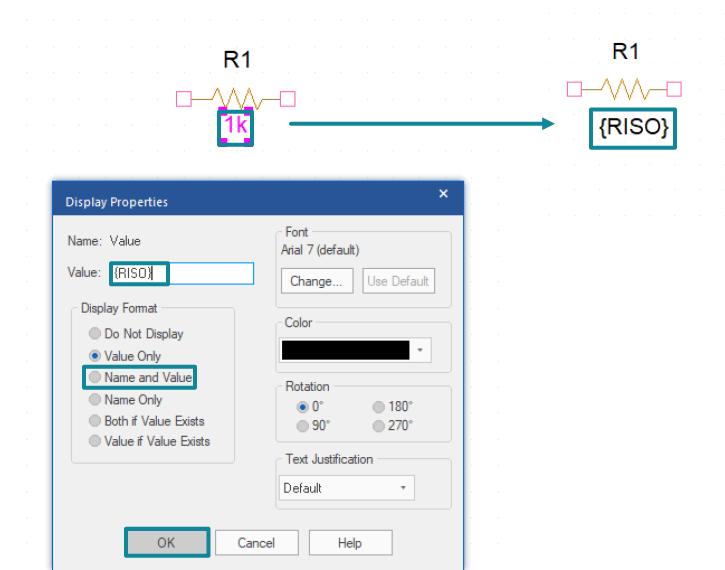

在原理图中声明参数后，用户可以通过在元件值中的名称周围放置花括号来调用该参数。在图 4-11 中，R1 的值从  $1\text{k}\Omega$  更改为对应于参数 RISO 的变量值。

图 4-11. 添加参数作为器件值

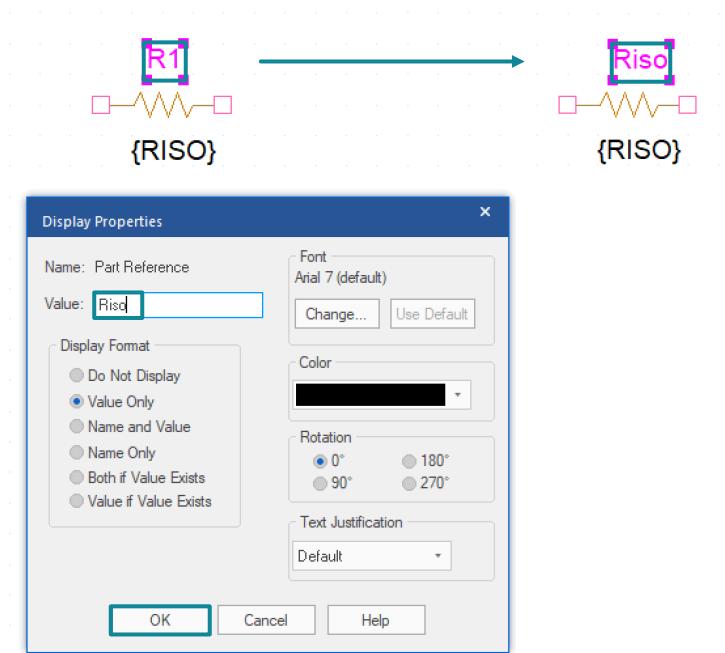

如果电路中的元件有常用名称，请更改器件参考以反映该名称。

图 4-12. 重命名器件参考

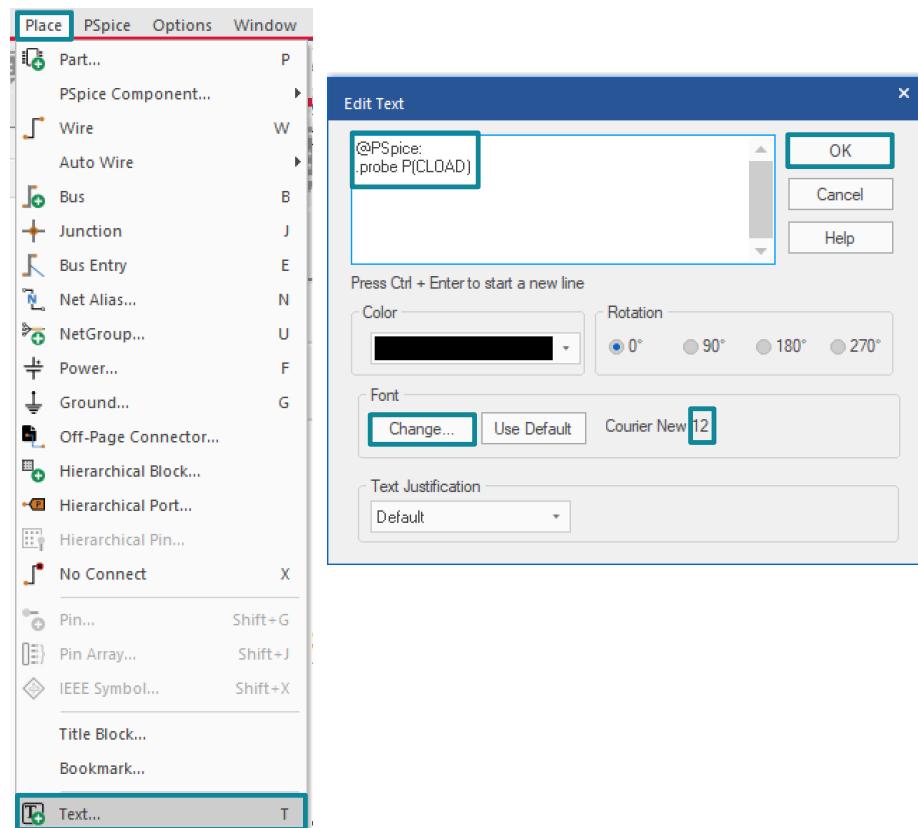

添加了一个探测器以用于要在输出模拟器窗口中调用的参数。要向参数添加探头，必须通过 *Place > Text* 或键盘快捷方式 T、@PSpice: .probe P(参数名称)，在原理图中添加以下文本。此实现的用例是在后处理公式中需要参数时，详见节 5.2。在图 4-13 中，计算中使用的参数是 CLOAD，可以根据需要对多个参数重复此过程。字体大小增加至 12。

图 4-13. 输出仿真窗口中所用的参数

### 4.3 放置电源

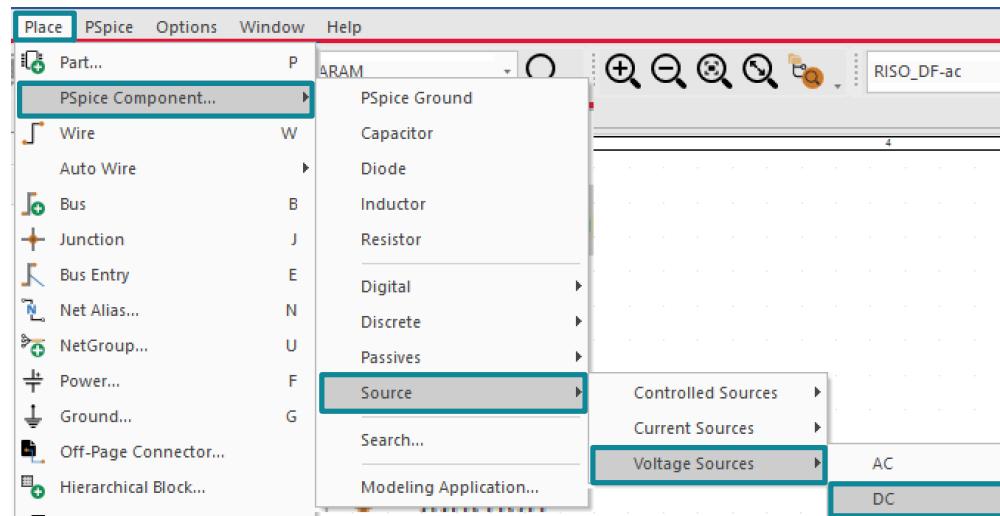

直流电源可通过以下路径放置：*Place > PSpice Component... > Source > Voltage Sources > DC*。

图 4-14. 放置直流电压

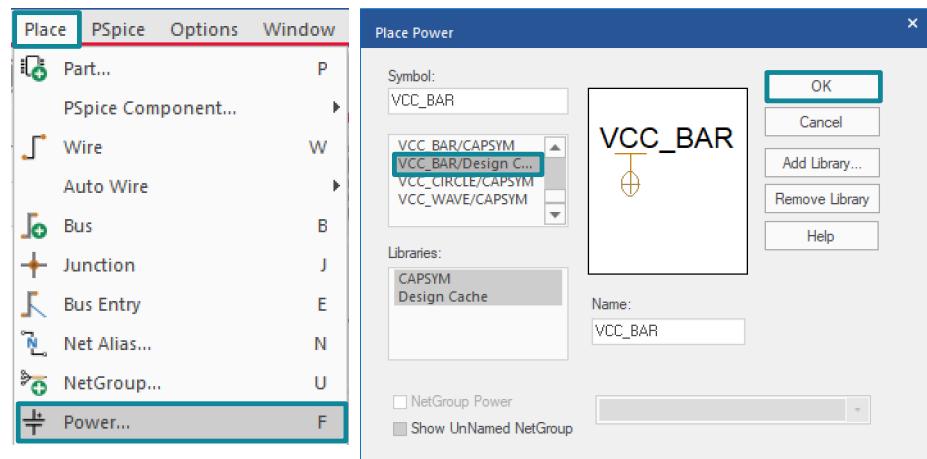

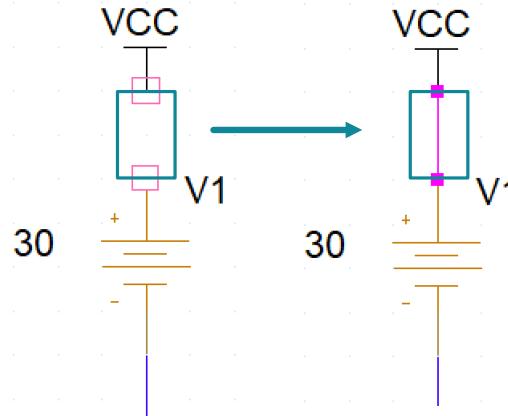

放置电源后，可以将电源网放置在原理图中的多个位置，以使用该电源。电源元件位于 *Place > Power* 或可通过键盘快捷方式 F 找到。有多个符号可用，图 4-15 中的示例使用 *VCC\_BAR*。

原理图，用来提高可读性

图 4-15. VCC\_BAR

## 4.4 接线

通过 *Place > Wire* 或键盘快捷方式 **W** 放置电线。单击原理图开始放置电线，每次单击都可以更改方向。要将两个元件连接在一起，只需单击方形连接器。

图 4-16. 电线放置

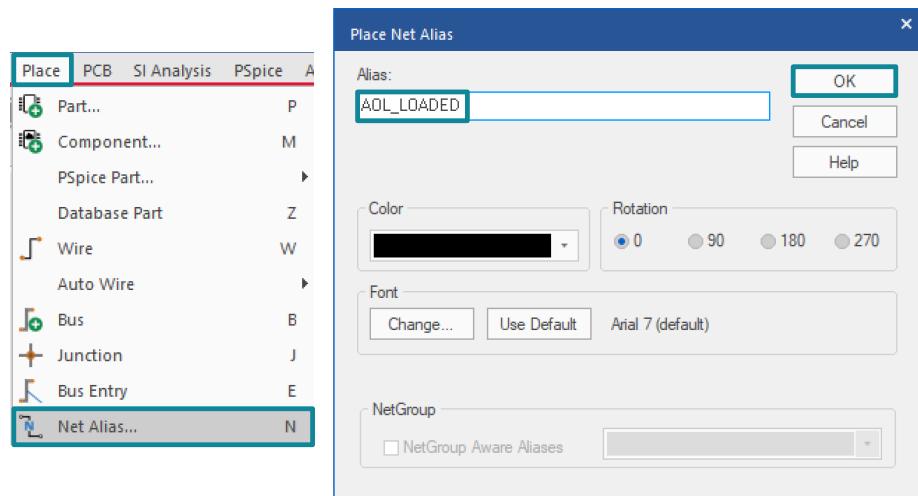

放置电线后，PSpice®-for-TI 会为每根电线分配一个字母数字网络别名。对于重要线路，请将网络别名重命名为可识别的名称。网络别名通过 *Place > Net Alias* 或键盘快捷方式 **N** 放置。键入别名并选择 **OK** 进行放置。网络别名仅存在于现有的电线上，也可用于将两根电线连接在一起，而无需实际连接它们。

图 4-17. 标记网

## 4.5 对用户体验进行管理

一旦所有元件都放置在一起并以直观的方式命名并连接在一起，就必须考虑用户体验。对于作者来说，显而易见的是，通常对全新用户更敏感；因此，工程的标记和隔离部分可以为新用户提供指导。

在该示例中，需要由用户更改的唯一变量位于图 4-18 左侧的框内。右侧的原理图连接与用户相关的变量（参数）相互作用，但在实际原理图中被覆盖的可能性较小。

图 4-18. 尽可能减少用户交互

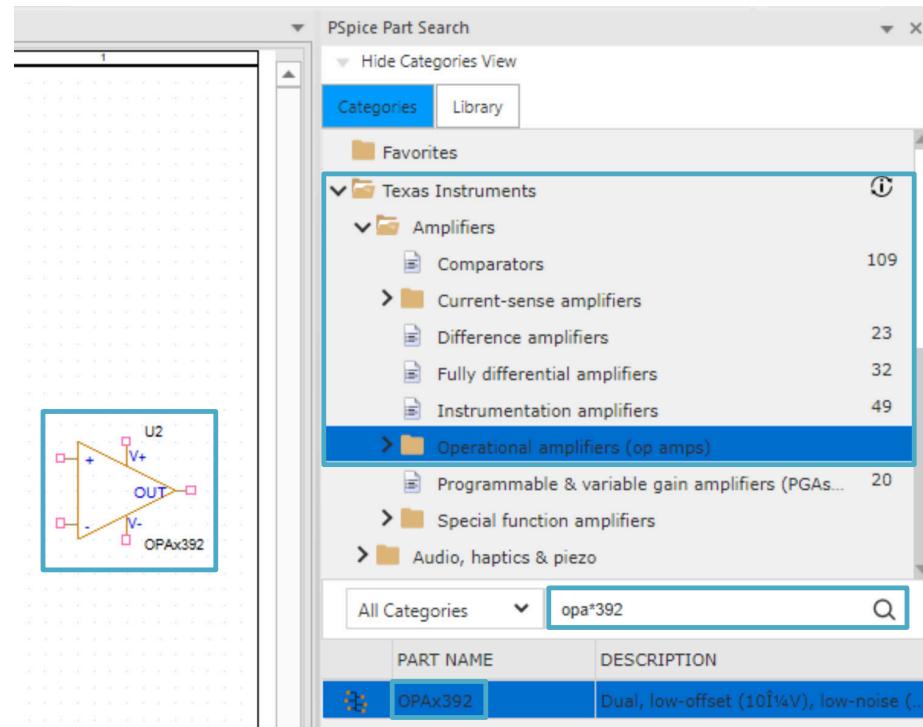

最后一个用户与电路的交互是在图 4-18 原理图的中间放置运算放大器。可以从 PSpice® 器件搜索（类似于参数）中，通过导航 *Texas Instruments > Amplifiers > Operational amplifiers (op amps)* 或通过搜索（位于 All Categories 下拉菜单旁边并带有放大镜）放置器件。可以在搜索中将星号 (\*) 用作通配符。双击以放置。

图 4-19. 通过集成库来放置 TI 元件

TI 运算放大器产品系列中超过 90% 的引脚方向如图 4-19 所示，同相输入 (IN+) 和正电源 (V+) 位于顶部。绘制原理图的方式允许用户简单地插入（如图 4-20 所示），而无需旋转或镜像。

图 4-20. 无修改的用户放置

## 5 仿真配置文件设置

原理图完成后，下一步是创建仿真配置文件。

如果用户在 PSpice®-for-TI 中创建了仿真配置文件，请先跳转到节 5.1。

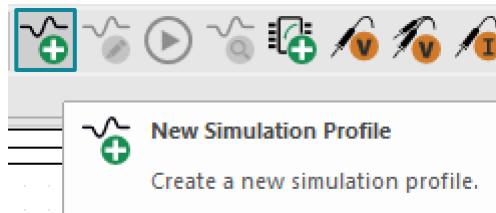

要创建新的仿真配置文件，请导航至 *PSpice > New Simulation Profile* 或使用任务栏中的新仿真配置文件图标（如图 5-1 所示）。

图 5-1. 新仿真配置文件图标

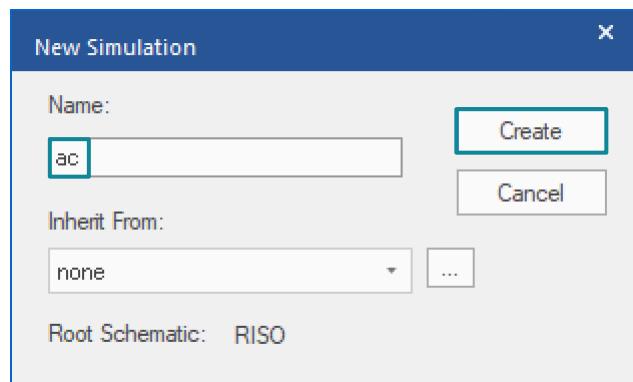

为仿真配置文件命名一个代表性名称，以便于识别。在图 5-2 中，仿真被命名为 **AC** 以表示交流扫描。选择 **Create** 继续。

图 5-2. 命名新仿真配置文件

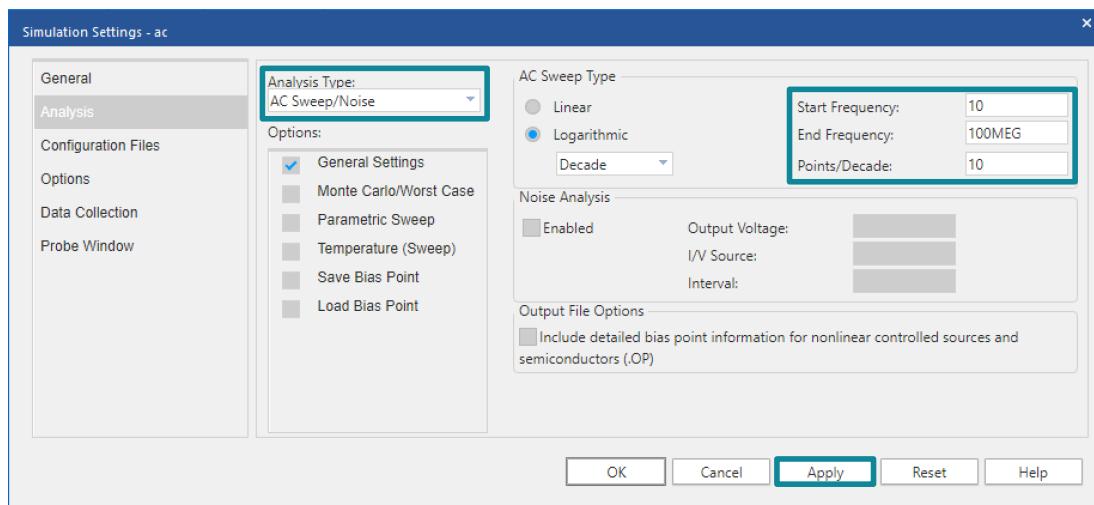

在示例中，分析在频域中完成；因此，在 **Analysis** 选项卡中选择 **AC Sweep/Noise** 作为分析类型。目标频率取决于放大器的带宽，在此示例中，从 10Hz 到 100MHz 的频率扫描以每十倍频程 10 个点进行。PSpice®-for-TI 要求声明 **MEG for mega ( $10^6$ )**，**M** 被确认为 milli ( $10^{-3}$ )。选择 **Apply** 保存此选项卡上的设置。

图 5-3. 交流扫描设置

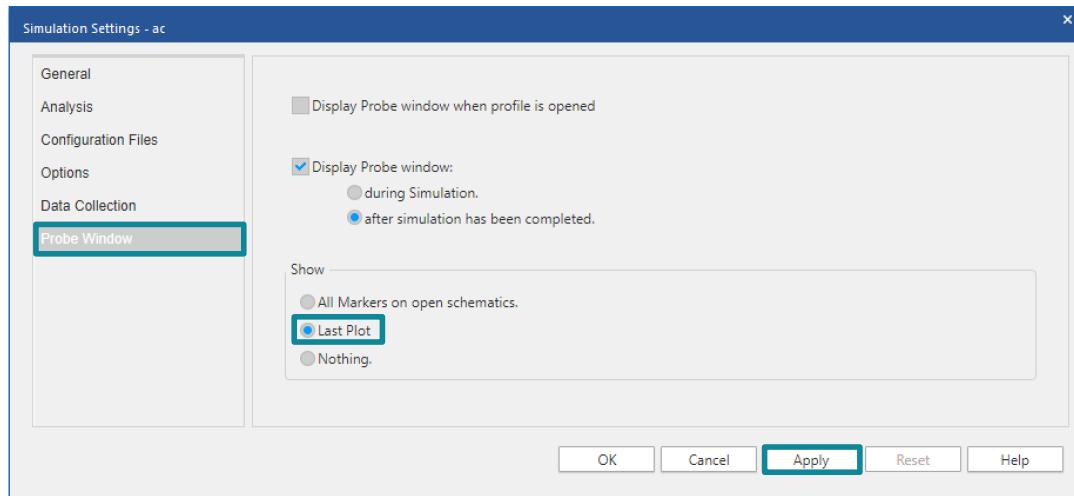

在 **Probe Window** 选项卡中，选择每次运行仿真时显示 *Last Plot*。得到的结果是仿真配置文件将设置（图和公式）保存于探测窗口中并应用于每次运行。选择 **Apply** 和 **OK** 可退出仿真配置文件设置。

图 5-4. 最后一个图

## 5.1 帮助收敛

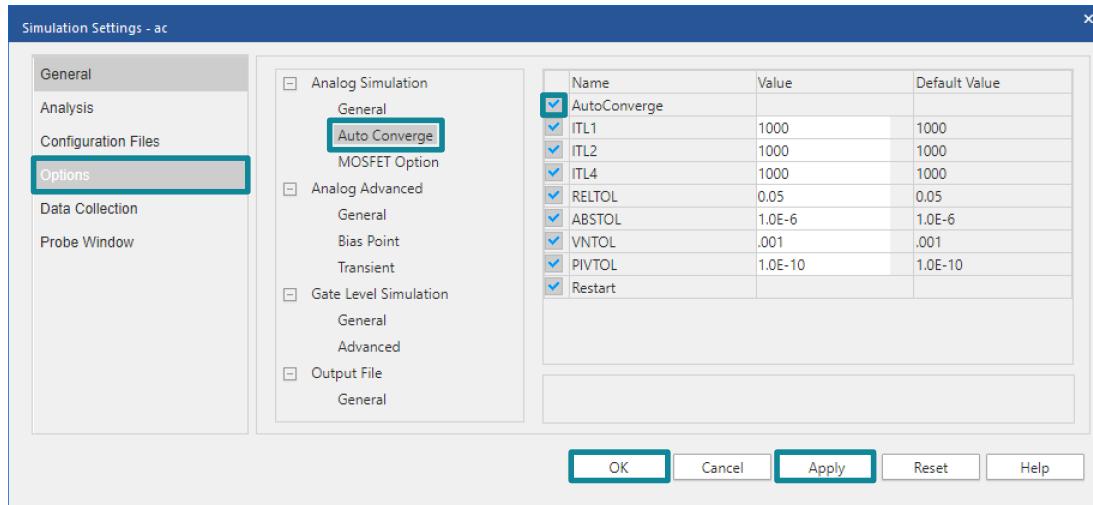

默认情况下，PSpice®-for-TI 未开启 **AutoConverge**。如果存在收敛问题，请查看器件的数据表，验证器件在线性工作条件下的设置和运行情况。

处理复杂工程时，即使在器件的线性工作条件下，仿真也需要一段时间（几分钟）。可以在仿真配置文件设置中打开 **AutoConverge** 以减少仿真时间。在 **Options tab > Analog Simulation > Auto Converge** 下，选择顶部 **AutoConverge** 文本框时将选择以下所有选项。

**AutoConverge** 可以在程序尝试达到收敛时降低仿真的准确性或者增加迭代次数。

图 5-5. 自动收敛

选择 **Apply** 以保存选项卡上的设置，选择 **OK** 以完成整个仿真配置文件的编辑。

### 5.1.1 应用建模

根据每个工程，仿真器在计算节点电压和电流时可能会遇到数字限制。

在本例中，交流输入旁边的大 (1T) 电容器必须添加一个寄生串联电阻以帮助实现收敛。这个小串联电阻提供最小电容器阻抗，避免仿真器计算流经电容器的非常大的电流。

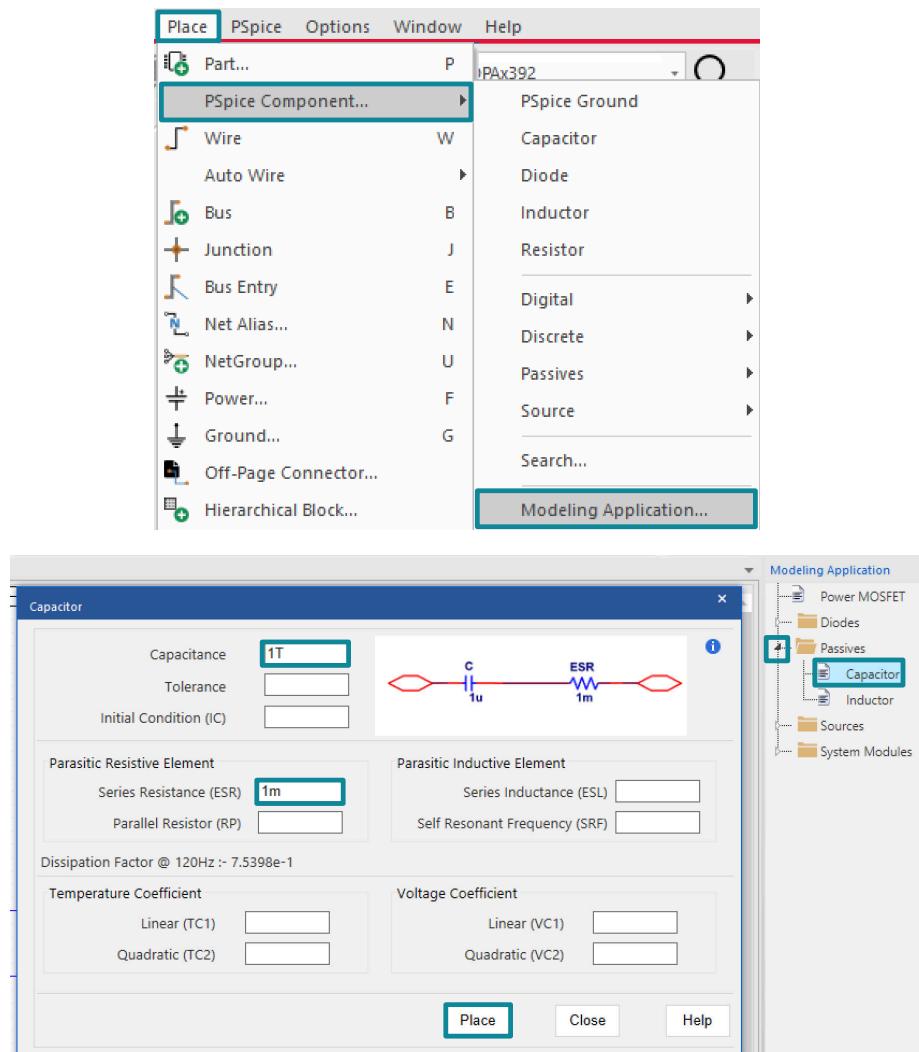

有两种方法可以实现此目的：(1) 可以将电阻器与电容器串联放置；或者 (2) 在应用建模中通过 *Place > PSpice Component...* 提供更巧妙的选项。在 *Capacitor* 中的 *Passives* 下，将 *Capacitance* 设置为 *1T*，将 *Series resistance (ESR)* 设置为 *1m*。这使得交流仿真响应在全部频率下都是平滑的。生成的放置电容器是灰色而非黑色，以突出显示修改。

图 5-6. 应用建模

## 5.2 强大的后处理

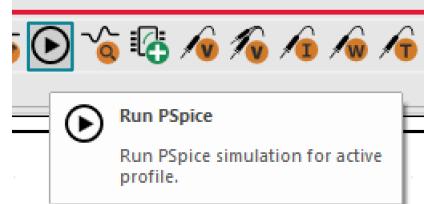

创建仿真配置文件后，默认情况下，仿真配置文件位于层次结构的顶部并显示为活动状态。可以通过 **PSpice > Run** 或者键盘快捷方式 F11 来评估有效的仿真配置文件。

图 5-7. 运行 PSpice® 仿真图标

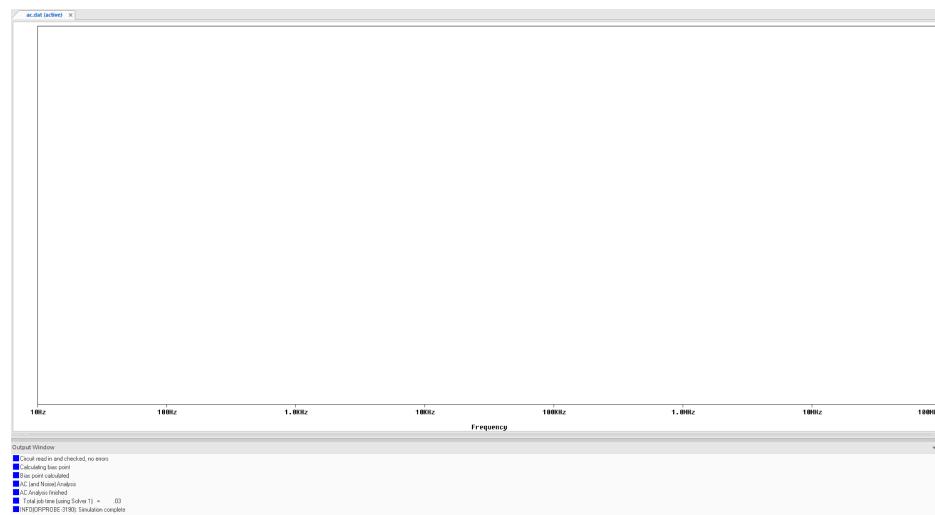

首次运行仿真时，预计等待时间比后续运行要长，因为 PSpice®-for-TI 正在从 [ti.com](http://ti.com) 更新最新的库。此时会打开一个新窗口，并显示一个空图，如图 5-8 所示。

图 5-8. 第一个输出为空图

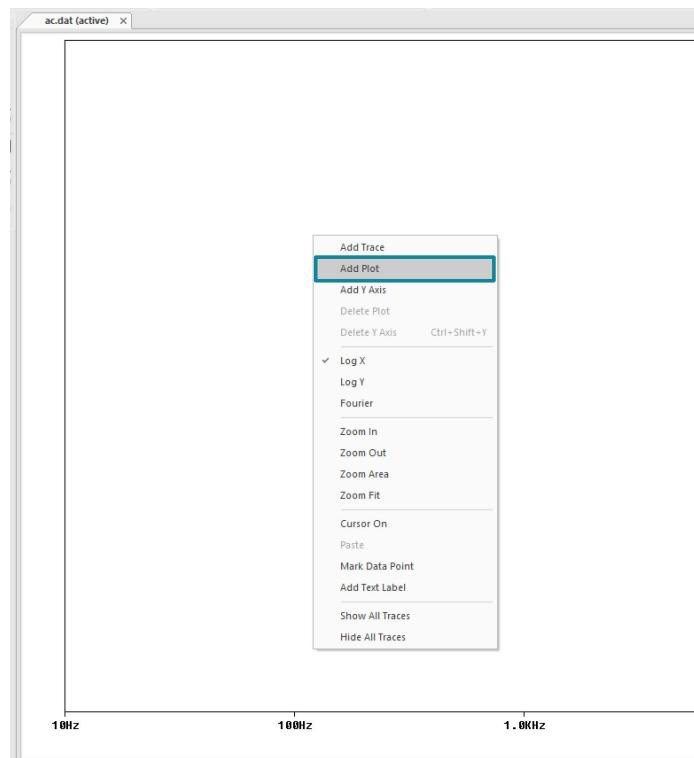

如图 5-9 中所示，右键点击图并选择 **Add Plot**，可以添加多个图。

图 5-9. 添加图

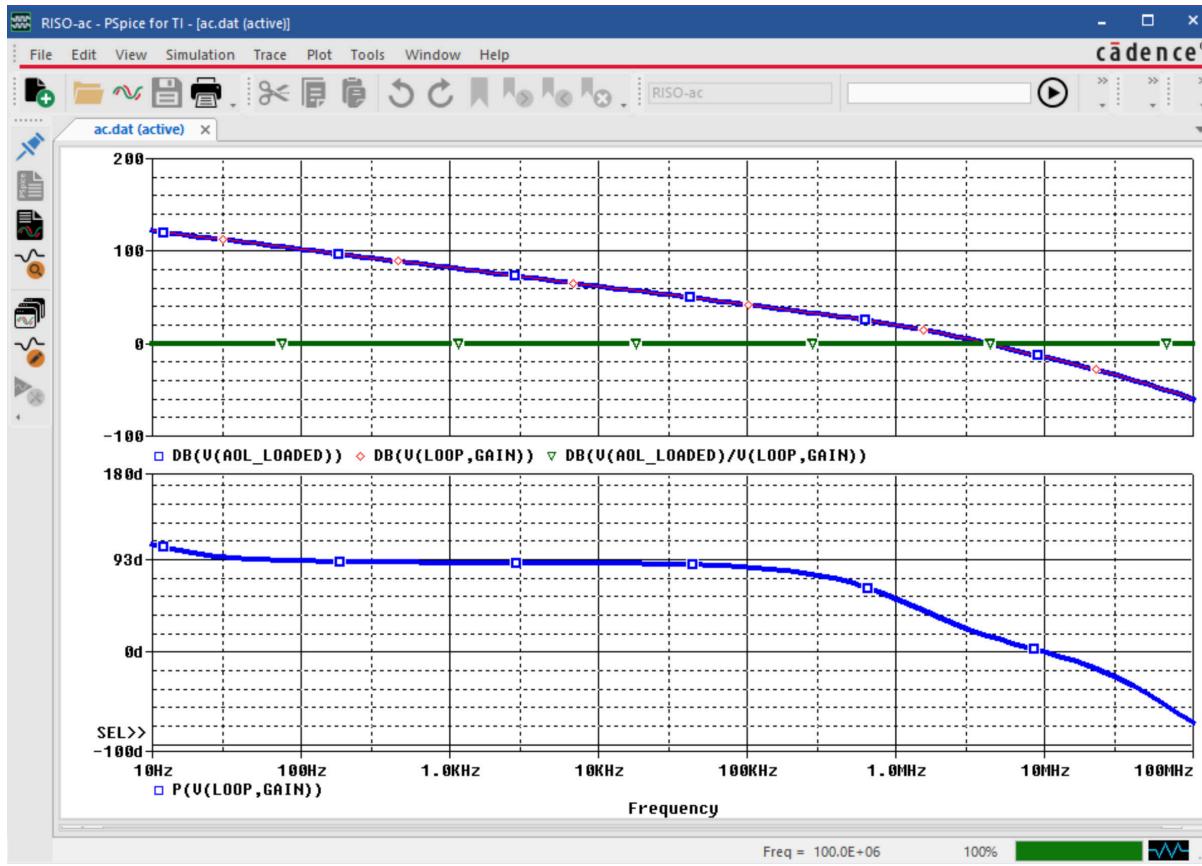

在此示例中，执行了频率扫描以观察电路的开环响应，以幅度 (dB) 和相位 (°) 为单位；因此，在仿真器的输出窗口中添加了两幅图。

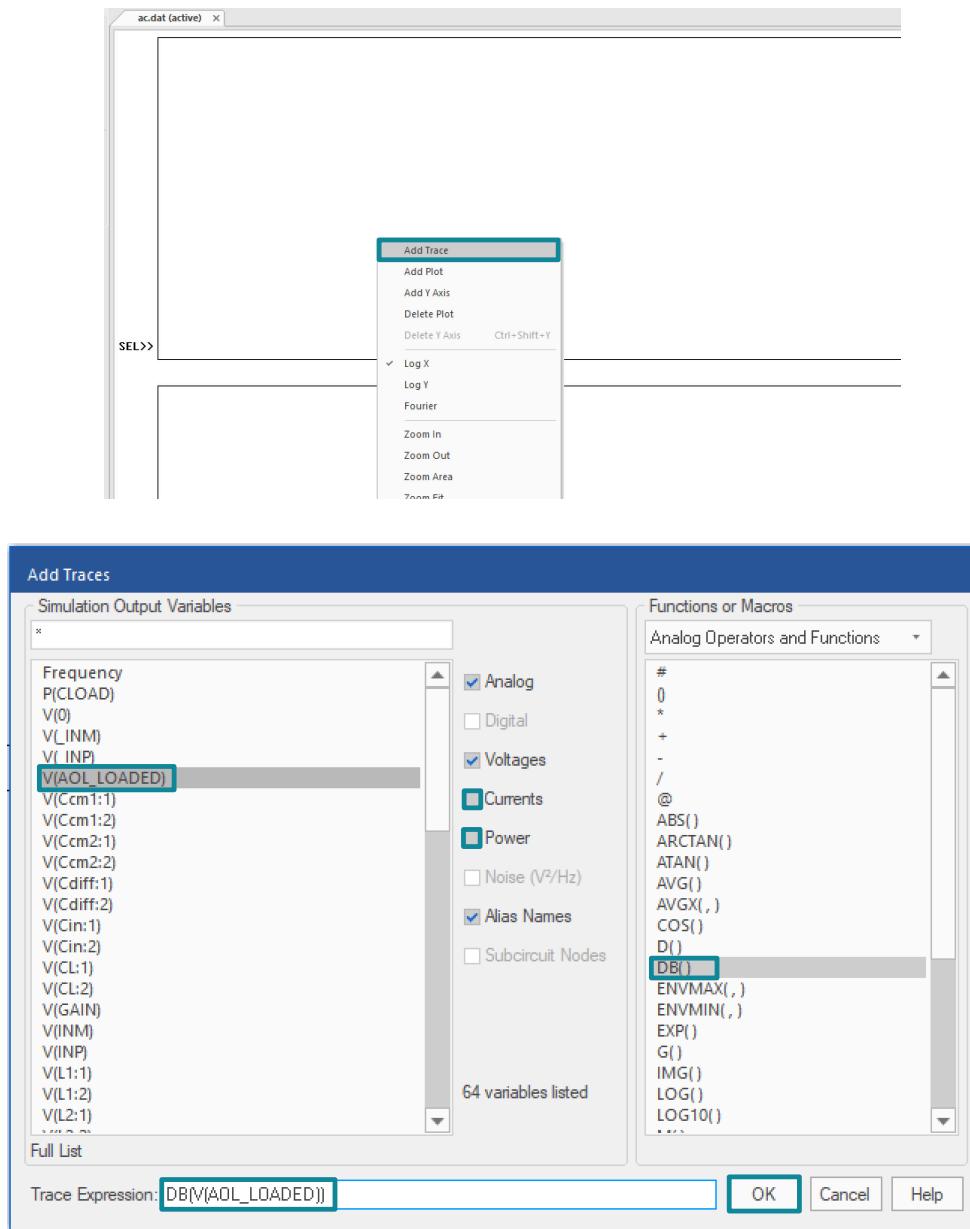

通常对于运算放大器的交流响应，上图为幅度 (dB)、下图为相位 (°)。要增加相关网络的幅度 (dB) 和相位 (°)，必须放置迹线。这可以通过右键单击所需的图并选择 **Add Trace** 来完成，如图 5-10 中所示。

图 5-10. 添加迹线

此时会出现一个对话框窗口，可在其中选择 *Simulation Output Variables* 和 “*Functions or Macros*”。

本例中，表 5-1 列出了所需的幅值 (dB) 及相位 (°) 迹线。

表 5-1. 迹线语法

|          | 迹线                                   | 表达式语法                          |

|----------|--------------------------------------|--------------------------------|

| 带负载的开环响应 | 带负载的运算放大器输出端电压 (以 dB 为单位)            | DB(V(AOL_LOADED))              |

| 环路增益     | 标记为“LOOP”和“GAIN”的网络上的电压 (以 dB 和度为单位) | DB(V(LOOP,GAIN))               |

|          |                                      | P(V(LOOP,GAIN))                |

| 1/β      | 开环响应与负载及环路增益之比                       | DB(V(AOL_LOADED)/V(LOOP,GAIN)) |

可以键入迹线表达式，也可以从图 5-10 中所示的可用选项中选择。或者，如果已按照前面文档图 4-17 所述对网络进行了标记，则可以直接将迹线从表 5-1 复制并粘贴到程序中。

包含所有迹线表达式的输出仿真窗口如图 5-11 所示，顶部图是幅度 (dB) 响应，底部图是相位 (°)。

图 5-11. 输出仿真窗口

在本例中，目标是提高相位裕度。这是通过评估开环响应的相位裕度并根据电路的交流响应计算补偿分量来实现的。

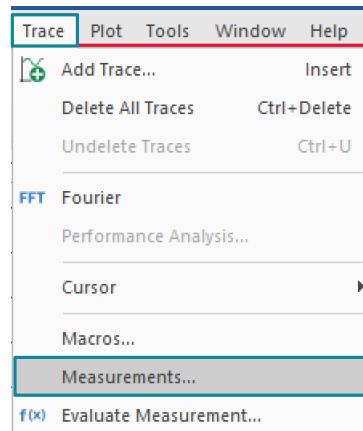

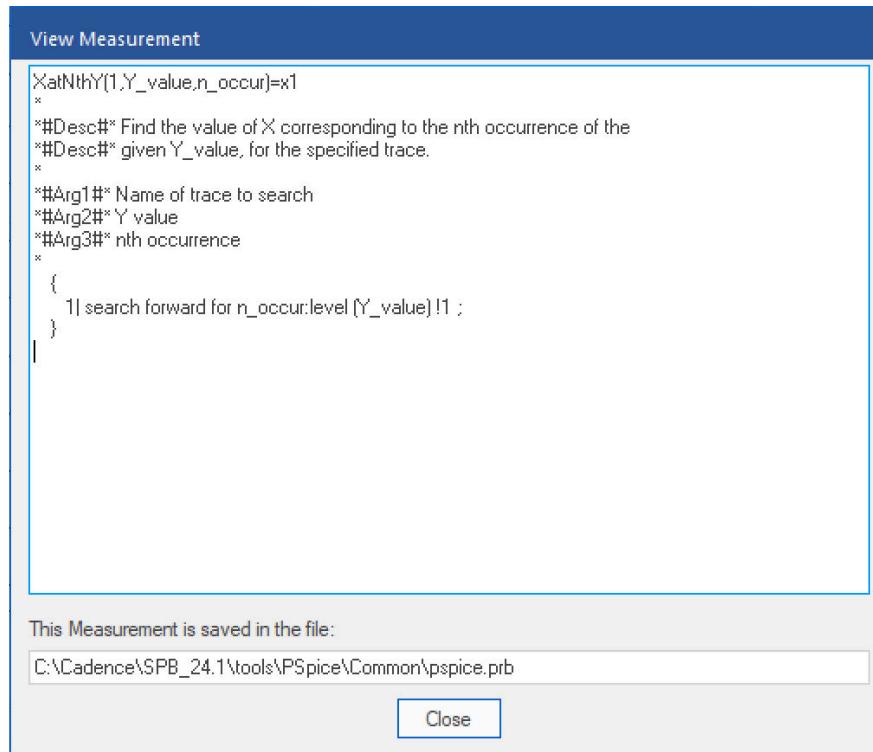

PSpice®-for-TI 内置了公式，语法可以在 *Trace* 子菜单 *Measurements* 选项中找到，如图 5-12 所示。在此示例中，使用了三个测量值，*PhaseMargin*、*XatNthY* 和 *Max*。

图 5-12. 测量值的语法定义

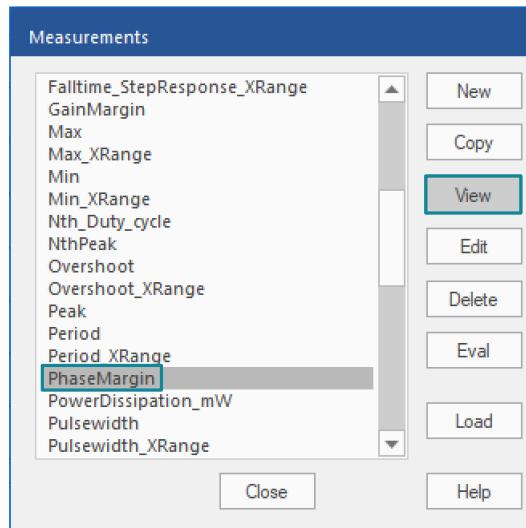

在 *Measurements* 窗口中选择相关选项，在此示例中，*PhaseMargin* 突出显示并选择了 *View*。

图 5-13. PhaseMargin 测量

所选的测量值、描述、测量参数的语法及文件路径将显示在对话框中。

图 5-14. 已定义 PhaseMargin 测量

相位裕度测量是幅度为 0dB 的频率下的相位。在 PSpice®-for-TI 中，实现此目的所用的方法是搜索迹线幅度（以 dB 为单位），直到值水平为 0，记录 x 值（频率）。然后于该频率下读取相位图的 y 值。

在图 5-14 中定义的测量中，y2 提供的相位裕度偏移 +180 度，这与运算放大器无关，因此评估的测量偏移 -180 度，从而得到  $\text{PhaseMargin}(\text{DB}(\text{Trace}), \text{P}(\text{Trace})) - 180$  的编写方程。

接下来，要找到运算放大器幅度输出为 0dB 和 20dB 的频率，请使用  $\text{XatNthY}$  测量。 $\text{XatNthY}$  测量在图 5-15 中定义为 x 对应于发生时给定的 y 值 — 其中 x 是频率 (Hz)，y 是幅度 (dB)。对于这两种情况，不会多次发生，因此仅考虑第一个情况。

图 5-15. 已定义 XatNthY 测量

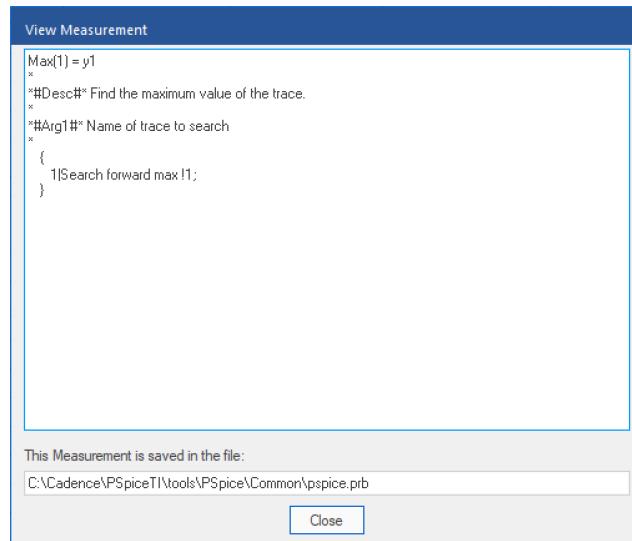

要计算 **RISO** 补偿，容性负载的值必须从原理图转移到输出仿真窗口，这是图 4-13 说明的实现。要将此探头包含在要评估的方程中，必须在参数 **CLOAD** 处对探头进行测量。考虑到电容值不随频率变化，使用图 5-16 中定义的最大测量值。

图 5-16. 已定义最大值测量

表 5-2 汇总了“相位裕度”（典型值为“RISO”）和保守的“RISO”值所需的公式语法。典型的“RISO”提供接近 45° 的相位裕度，保守的“RISO”提供接近 90° 的相位裕度。增大隔离电阻器的代价在于电流需求较高（阻性负载较小）的输出端电压误差。

$$R_{ISO} \left( \text{typical} \right) = \frac{1}{2\pi \times f_{AOL\_LOADED}} = 0dB \times C_{LOAD} \quad (1)$$

$$R_{ISO} \left( \text{conservative} \right) = \frac{1}{2\pi \times f_{AOL\_LOADED}} = 20\text{dB} \times C_{LOAD} \quad (2)$$

表 5-2. 测量公式及语法

| 测量           | 表达式语法                                                                 |

|--------------|-----------------------------------------------------------------------|

| 相位裕度         | PhaseMargin(DB(V(LOOP,GAIN)),P(V(LOOP,GAIN)))-180                     |

| RISO ( 典型值 ) | $1/(2*\pi^* \text{Max}(P(CLOAD))^* XatNthY(DB(V(AOL\_LOADED)),0,1))$  |

| RISO ( 保守 )  | $1/(2*\pi^* \text{Max}(P(CLOAD))^* XatNthY(DB(V(AOL\_LOADED)),20,1))$ |

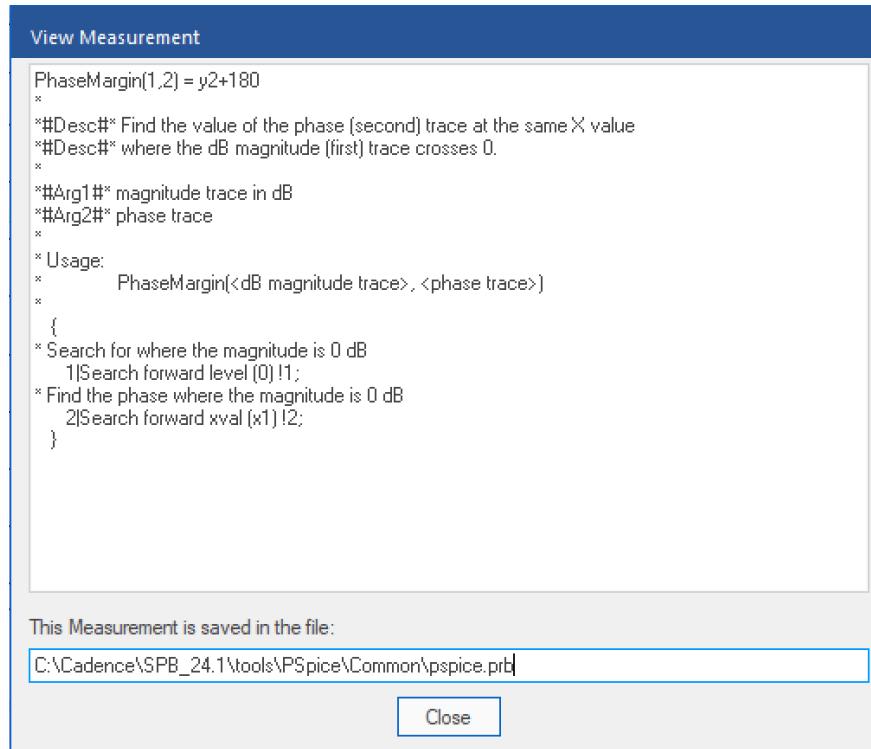

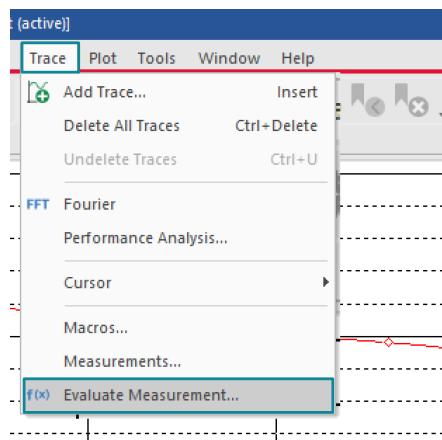

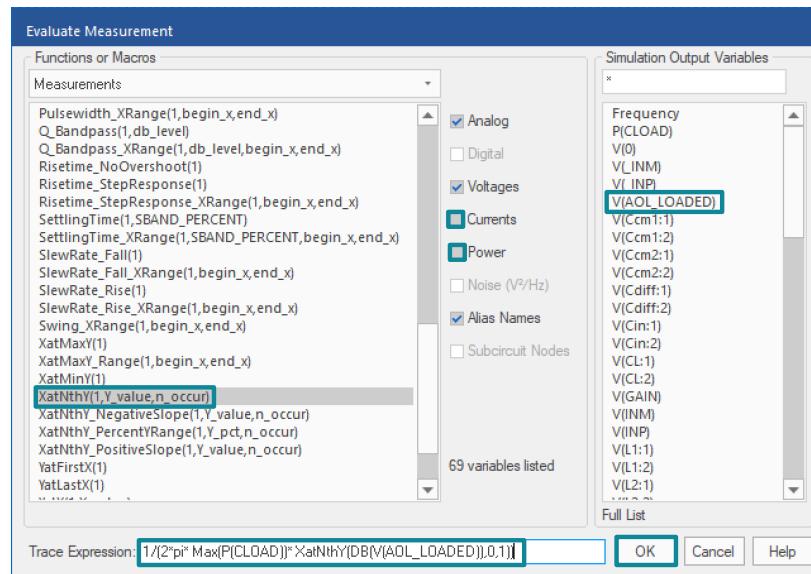

要将这些测量值添加到输出仿真窗口，请通过 *Trace* 子菜单选择 *Evaluate Measurement*。

图 5-17. 评估测量

可以输入迹线表达式，从可用选项中选择、也可以从表 5-2 中复制和粘贴。

图 5-18. 测量的迹线表达式评估

**Measurement Results** 窗口显示图 5-19 中所述的测量。每次运行迭代时都会显示输出窗口，其中包括图和测量值。

| Evaluate                            | Measurement                                                                  |

|-------------------------------------|------------------------------------------------------------------------------|

| <input checked="" type="checkbox"/> | PhaseMargin(DB(V(LOOP,GAIN)),P(V(LOOP,GAIN)))-180 Phase Margin               |

| <input checked="" type="checkbox"/> | 1/(2*pi* Max(P(CLOAD))* XatNthY(DB(V(AOL_LOADED)),0,1)) RISO (typical)       |

| <input checked="" type="checkbox"/> | 1/(2*pi* Max(P(CLOAD))* XatNthY(DB(V(AOL_LOADED)),20,1)) RISO (conservative) |

图 5-19. PSpice®-for-TI 语法中的公式

## 6 总结

自动化设计的所有要素均已详细讨论，包括但不限于：

- 要解决的问题

- 可重复使用的解决方案

- 如何创建 PSpice®-for-TI 工程

- 原理图，用来提高可读性

- 放置无源元件

- 利用参数

- 放置电源

- 如何接线和标记

- 对用户体验进行管理

- 仿真配置文件设置

- 帮助收敛

- 强大的后处理

组装完成后，可以使用此设计跨多个器件和条件快速解决问题。下面是整个文档讨论的实际应用示例。

OPAx392 放置于驱动 1nF 容性负载的原理图中。

图 6-1. OPA392 驱动 1nF 容性负载：无补偿

产生的相位裕度为 16 度，超出了 45° 和 90° 之间的稳定定义。

| Evaluate                            | Measurement                                                                        | Value     |

|-------------------------------------|------------------------------------------------------------------------------------|-----------|

| <input checked="" type="checkbox"/> | $\text{PhaseMargin(DB(V(LOOP,GAIN)),P(V(LOOP,GAIN)))-180}$                         | 16.35200  |

| <input checked="" type="checkbox"/> | $1/(2\pi \cdot \text{Max}(P(CLOAD)) \cdot \text{XatNthY(DB(V(AOL_LOADED)),0,1)))$  | 37.92552  |

| <input checked="" type="checkbox"/> | $1/(2\pi \cdot \text{Max}(P(CLOAD)) \cdot \text{XatNthY(DB(V(AOL_LOADED)),20,1)))$ | 153.34276 |

图 6-2. 建议使用 RISO 的不稳定相位裕度（典型值及保守值）

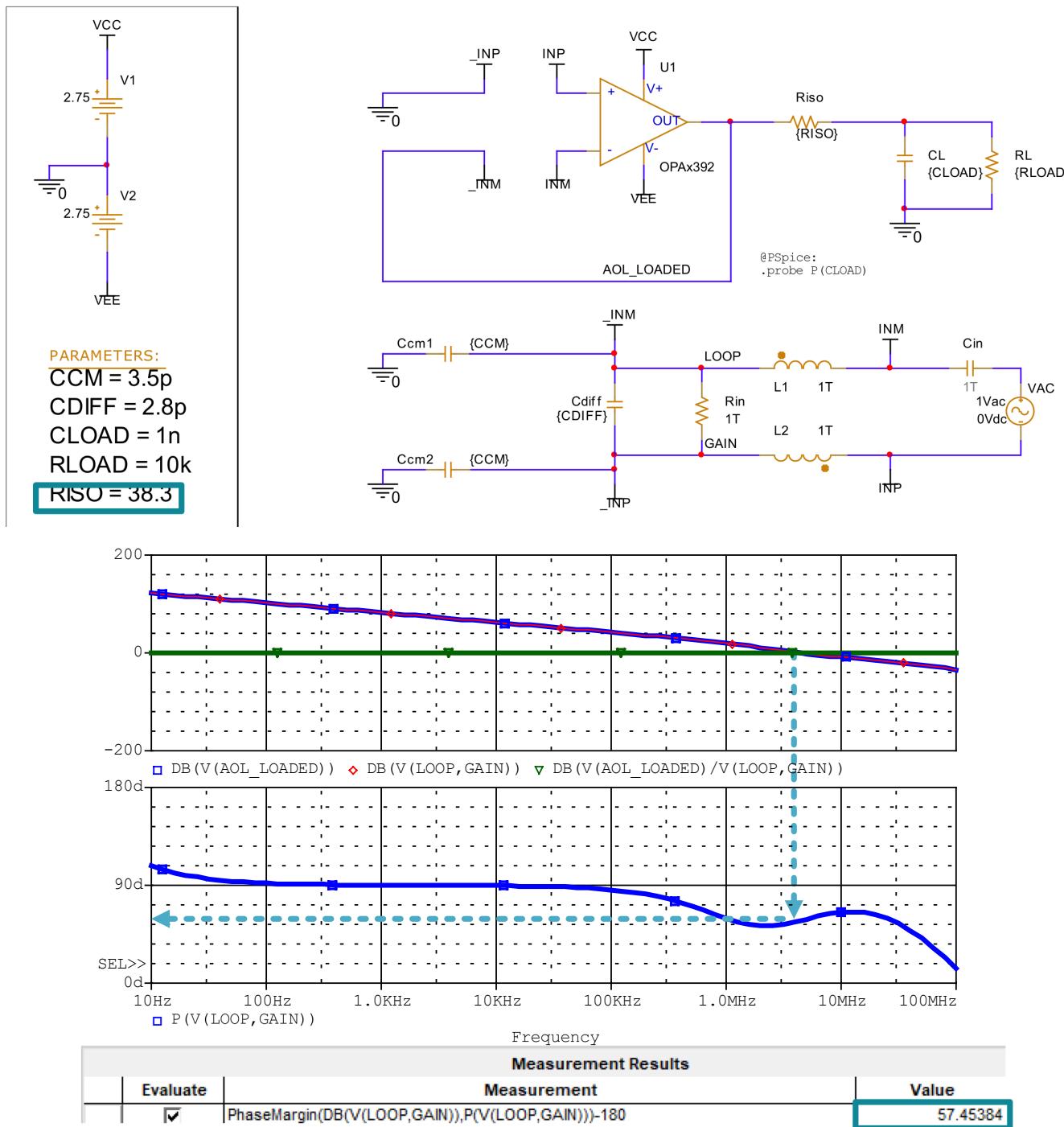

最低 RISO 建议为  $37.9\Omega$ ，保守 RISO 建议为  $153.3\Omega$ ，在下一次仿真迭代中， $38.3\Omega$  的 1% 常见电阻值用于 RISO。

生成的输出具有 57 度的相位裕度，这意味着输出容性负载由  $38.3\Omega$  的隔离电阻器适当补偿。

总结

图 6-3. OPA392 使用 RISO 补偿来驱动 1nF 容性负载

可以针对不同的运算放大器、不同的容性负载及不同的电路配置重复这种自动化设计，以帮助实现快速分辨率。本应用手册中讨论的自动化设计示例可以从此处下载：

- 0° 至 60°稳定性自动处理：增益为 1 (缓冲器)

- 0° 至 60°稳定性自动处理：同相增益

- 0° 至 60°稳定性自动处理：反相增益

- 0° 至 60°稳定性自动处理：差分放大器增益

## 7 参考资料

- 德州仪器 (TI) , [TINA-TI 仿真工具](#) , 基于 SPICE 的模拟仿真程序。

- [PSPICE-FOR-TI 仿真工具](#) , 仿真工具。

- 高精度实验室系列 : 运算放大器 , 视频系列。

- 断开差分放大器上的环路 , 视频系列。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#))、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025 , 德州仪器 (TI) 公司

最后更新日期 : 2025 年 10 月