## Technical Article **Cycle Scavenging on C2000™ MCUs, Part 2: ADC Zero**wait-state and Multiport Reads

Jitin George

As I explained in the first installment of this series, the idea of cycle scavenging is built into C2000<sup>™</sup> microcontrollers (MCUs), enabling them to minimize latency at every stage of real-time control without compromising performance.

I introduced the concept of real-time control and talked about minimizing the time delay between the sensing, processing and actuation stages as one of the biggest challenges that engineers face in designing these systems. I also talked about C2000 microcontrollers being the right fit for these kinds of challenges due to the multitude of built-in cycle scavenging features that enable them to meet the strict timing demands of real-time control. In this installment, I'll focus on the sensing stage and take a look at two cycle-scavenging features: zero-wait-state analog-to-digital converter (ADC) transfers and ADC multiport reads.

C2000 MCUs prioritize the data paths from the ADC registers to the CPU, thus enabling zero-wait-state sample transfers out of the ADCs in a single CPU cycle. In other words, as soon as the ADC conversion is complete, the result can transfer immediately to the CPU without wasting any cycles.

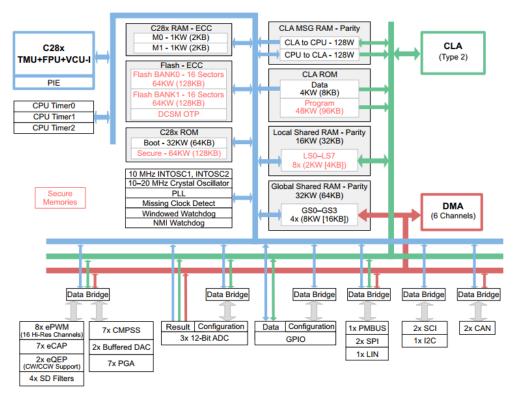

Multiport ADC reads is another important feature unique to C2000 MCUs. In order to understand how multiport ADC reads fit into the theme of cycle scavenging, see the F28004x block diagram shown in Figure 1.

Notice that while all peripherals have data bridges, the ADC result registers do not. This is very important from a cycle scavenging standpoint. The main purpose of a data bridge is to arbitrate between the masters

1

(central processing unit [CPU], control law accelerator [CLA] and direct memory access [DMA]). For example, if a situation arises where the DMA is moving words to/from the Serial Peripheral Interface (SPI) while the CPU tries to read the Local Interconnect Network (LIN) module in the same cycle, arbitration would occur because they share a data bridge. Such arbitration would result in one of the memory accesses being delayed by a cycle or so. If the ADC modules had a data bridge as well, there would be a delay every time multiple masters tried to access ADC results simultaneously. Such delays would adversely affect real-time control performance.

To avoid such delays in sensing, ADC registers have dedicated taps on each of the master buses, as shown in Figure 1. Thus, multiple masters can read the same or different results simultaneously as soon as they become available without any delay or arbitration, thereby saving cycles.

C2000 MCUs possess an array of features tuned to scavenge cycles at the sensing stage, but there's still more to come. In the next installment, I'll look at how ADC features like start-of-conversion timing and configurable ADC interrupt delays help with cycle scavenging.

## Additional Resources:

- Keep up to date with our cycle scavenging blog series.

- Read our Fast Current Loop blog post, "Achieve unprecedented current-loop performance from an off-theshelf MCU" and white paper, "A faster current loop pays off in servo motor control."

- Learn more about DesignDRIVE solutions for industrial servo and AC inverter drives.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated