# Application Report DS250DF230 Design Considerations for RTV (QFN) Package

# **TEXAS INSTRUMENTS**

#### ABSTRACT

The DS250DF230 is available in two package variants with identical features sets – BGA and QFN. Of the two variants, TI recommends designing with the latter 32-pin RTV (QFN) package variant due to improved thermal efficiency that improves heat dissipation from the package. This document facilitates design-ins with the recommended alternative QFN package variant.

### **Table of Contents**

| 1 Introduction                            | .2 |

|-------------------------------------------|----|

| 2 QFN Pinout and Schematic Considerations |    |

| 3 RTV (QFN) Layout Considerations         | .2 |

| 3.1 RTV (QFN) Footprint Recommendations.  |    |

| 3.2 RTV (QFN) Layout Example              |    |

|                                           |    |

#### **List of Figures**

| Figure 2-1. ZLS (BGA) 36-Package Pinout | 2 |

|-----------------------------------------|---|

| Figure 2-2. RTV (QFN) 32-Package Pinout | 2 |

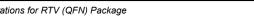

| Figure 3-1. Top Layer                   |   |

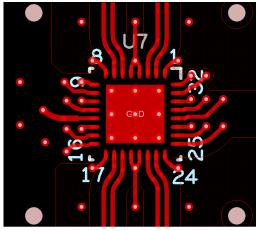

| Figure 3-2. Layer 1 GND                 |   |

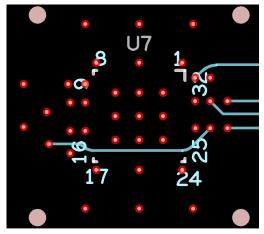

| Figure 3-3. Internal Low-Speed Signals  | 3 |

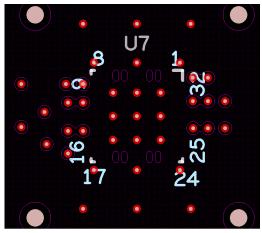

| Figure 3-4. VDD Layer                   |   |

| Figure 3-5. Bottom Layer                | 3 |

| ·                                       |   |

#### Trademarks

All trademarks are the property of their respective owners.

1

2

## 1 Introduction

The DS250DF230 is available in two package variants with identical features sets – BGA and QFN. Of the two variants, TI recommends designing with the latter 32-pin RTV (QFN) package variant due to improved thermal efficiency that improves heat dissipation from the package. As a result, the QFN provides superior thermal coefficient performance to facilitate outdoor applications where PCB temperatures may increase up to 105°C.

The DS250DF230EVM is currently only available for evaluation with the BGA package, as the high-speed performance and the feature set is identical between the two package variants. For new designs and existing designs with the BGA package, it is important to account for the differences in pinout, schematic, and layout considerations when transitioning to the QFN package. This document facilitates design-ins with the recommended alternative QFN package variant.

### 2 QFN Pinout and Schematic Considerations

GND NOX. OND SND GND DND DND TXOF TXON GND GND TX1P TX1N 5 4 1 READ EN N 9 32 ALL\_DONE\_N READ\_EN ALL\_DONE N GND GND GND GND F F CAL\_CLK\_IN 10 31 CAL\_CLK\_OUT VDD 11 30 VDD AL\_CLK CAL\_CL \_OUT THR/TEST1 SDA п п THR/TEST1 12 29 SDA mal Pad (DAP) TEST0 13 28 TEST0/RCK0 SDC c FN SMB SDC ADDB0 С 14 27 VDD VDD Legend в GND GND ADDR1 INT N GND GND в 15 Control/Status EN\_SMB 26 INT\_N ligh-Spe 25 ADDR0 ADDR1 16 Ground RX0P RX1P RX0N GND GND BX1N Δ 24 17 21 23 GND GND 3X1P 3X1N GND GND 3X0P Figure 2-1. ZLS (BGA) 36-Package Pinout

The following is a detailed comparison of differences between BGA and QFN packages.

Figure 2-1. ZLS (BGA) 36-Package Pinout

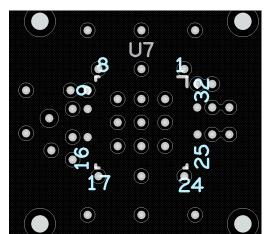

Figure 2-2. RTV (QFN) 32-Package Pinout

There are no differences from a schematic and pinout standpoint in terms of the number or availability of the high-speed, control/status, and power pins. The only difference in pin count is the number of GND connections. There are 12 balls on the BGA package routed to GND. There are 8 pins and a large thermal pad on the QFN package that are internally routed to GND.

# 3 RTV (QFN) Layout Considerations

The power supply recommendations and high-speed layout guidelines provided in the DS250DF230 data sheet are applicable for both BGA and QFN packages. Details in this section are specific to designing for the QFN package variant.

# 3.1 RTV (QFN) Footprint Recommendations

- Stencil parameters for the EP (Exposed Pad) such as aperture area ratio and the fabrication process have a significant impact on paste deposition. Inspection of the stencil prior to placement of the LLP (WQFN) package is highly recommended to improve board assembly yields. If the via and aperture openings are not carefully monitored, the solder may flow unevenly through the EP. Stencil parameters for aperture opening and via locations are shown in the RTV package drawing.

- The EP of the package should be connected to the ground plane through a 3x3 via array. These vias are solder-masked to avoid solder flowing into the plated-through holes during the board manufacturing process. Details about via dimensions are also shown in the RTV package drawing.

Copyright © 2021 Texas Instruments Incorporated

More information on the QFN style package is provided in QFN and SON PCB Attachment.

### 3.2 RTV (QFN) Layout Example

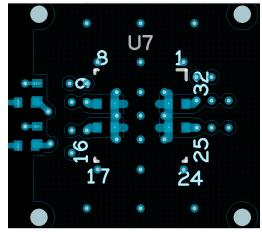

The example layout in this subsection demonstrates how all signals can be routed from the QFN using microstrip routing on a generic multi-layer stackup.

Figure 3-1. Top Layer

Figure 3-3. Internal Low-Speed Signals

Figure 3-2. Layer 1 GND

Figure 3-4. VDD Layer

Figure 3-5. Bottom Layer

3

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated