Detecting Short to Battery and Ground Conditions with TI Motor Gate Drivers

### of an overcurrent or fault condition. VDS monitors are used in gate drivers to detect overcurrent conditions and provide fault protection. This article covers how VDS monitors detect OCP conditions and explains how gate drivers with an SPI interface can use the location of an OCP condition to identify where the fault

ABSTRACT Overcurrent protection (OCP) is a key protection feature in preventing damage to motor systems. It is important for motor drivers to monitor the FETs closely and shut them down in a safe manner in the case

## Contents

| 1 | How VDS Monitors Detect OCP Conditions     | 2 |

|---|--------------------------------------------|---|

| 2 | Using VDS Monitors to Identify Fault Types | 2 |

| 3 | Conclusion                                 | 4 |

## List of Figures

| 1 | VDS Monitor Schematic | 2 |

|---|-----------------------|---|

| 2 | Short to VM Case 1    | 2 |

| 3 | Short to VM Case 2    | 2 |

| 4 | Short to GND Case 1   | 3 |

| 5 | Short to GND Case 2   | 3 |

| 6 | SH1 to SH2 Pin Short  | 3 |

|   |                       |   |

# List of Tables

| 1 \ | S Monitors Triggered Per Operating Mode | 4 |

|-----|-----------------------------------------|---|

|-----|-----------------------------------------|---|

# Trademarks

All trademarks are the property of their respective owners.

TEXAS INSTRUMENTS

occurred in the system.

# Detecting Short to Battery and Ground Conditions with TI Motor Gate Drivers

Gerardo Gaona

Application Report SLVAEV8-June 2020

Motor Drives

1

www.ti.com

#### 1 **How VDS Monitors Detect OCP Conditions**

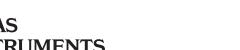

VDS monitors are connected at the drain and source of the FET. The voltage across the drain and source provides information on how much current is running through each FET. As shown in Figure 1, each FET has its own VDS monitor.

Figure 1. VDS Monitor Schematic

With TI motor gate drivers, designers can set VDS overcurrent protection threshold values based on the expected current through the FETs and failure conditions they are trying to protect against. This can be done many ways depending on the device used. For example, on DRV8705-Q1 it can be adjusted through VDS LVL register settings for the SPI interface. For hardware interfaces, designers can set the desired threshold values by connecting resistors to the appropriate pin. Specifications for resistor values and threshold values vary from one device to another and can be found in each device's datasheet.

In SPI devices, designers also have the option to set the OCP deglitch time. The duration of the overcurrent condition must be greater than the OCP deglitch time for an OCP condition to occur through the VDS register. OCP deglitch time preferences can vary depending on the time it takes to charge the FETs. The longer it takes to charge the FETs, the longer the OCP deglitch time is to ensure the FETs turn on and prevent false OCP conditions. For devices with a hardware interface, the OCP deglitch time falls within a range, specific to each device, which cannot be changed. In the event of an OCP condition, the FETs are disabled to prevent any damage. The specifics of a device's response and recovery from an OCP condition vary from one to device to another.

#### 2 Using VDS Monitors to Identify Fault Types

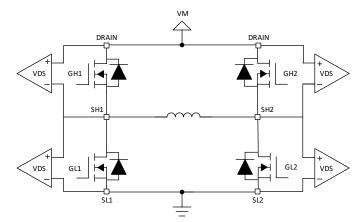

Once the desired specifications for VDS monitoring are set, the device is ready to detect faults. Three reasons an OCP condition occurs is the H-bridge outputs (SHx) are either shorted to ground, shorted to the supply voltage, or shorted to each other. The type of short can be identified depending on which VDS monitor detects the OCP condition.

The short to supply scenario is shown in Figure 2 and Figure 3. In Short to VM Case 1, if the motor were to drive in reverse (only GH2 and GL1 are on) the voltage at SH1 would be VM and the VDS monitor across GL1 would trigger an OCP event. Similarly, in Short to VM Case 2, if the motor were to drive forward (only GH1 and GL2 are on) the VDS monitor across GL2 would detect an OCP condition. In low side brake (only GL1 and GL2 are on) the OCP condition is detected by whichever low side FET is on the same side as the short to supply.

2

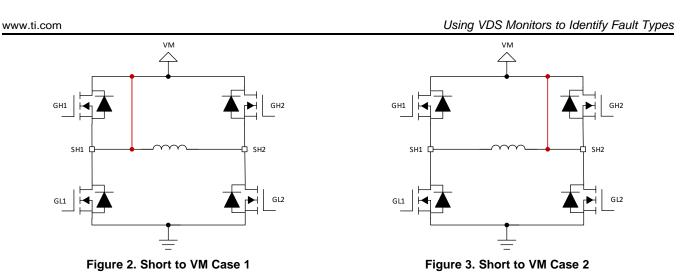

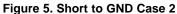

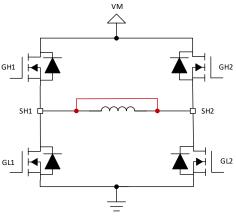

The Figure 4 and Figure 5 show the short to ground scenarios. If the motor were to drive forward (only GH1 and GL2 are on) in Short to GND Case 1, the high current through GH1 would trigger that FET's VDS monitor for an OCP event. Similarly, if the motor were to drive in reverse (only GH2 and GL1 are on) in the Short to GND Case 2 scenario, GH2's VDS monitor would trigger an OCP event.

Figure 4. Short to GND Case 1

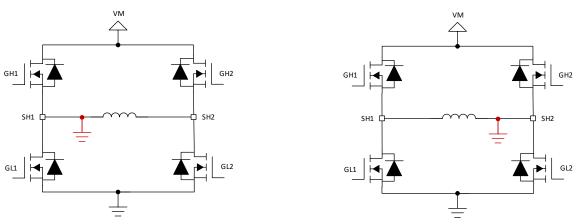

Lastly, the SHx pins can be shorted to each other due to poor soldering, poor terminal connections, or a short in the motor windings. In this scenario, the VDS monitors across any driving FET will detect an OCP condition. For example, when driving forward (only GH1 and GL2 are on) the VDS monitors across FETs GH1 and GL2 will detect an OCP condition.

Figure 6. SH1 to SH2 Pin Short

Detecting Short to Battery and Ground Conditions with TI Motor Gate Drivers

3

www.ti.com

Table 1 provides a recap on which VDS monitors detect an OCP condition under the different fault scenarios for each operating mode.

|                       | Operating Modes |                    |                    |                              |  |

|-----------------------|-----------------|--------------------|--------------------|------------------------------|--|

| Fault Type            | Coast Hi-Z      | Reverse (SH2M SH1) | Forward (SH1M SH2) | Brake Low-side Slow<br>Decay |  |

| Short to VM Case 1    | No Detect       | GL1                | No Detect          | GL1                          |  |

| Short to VM Case 2    | No Detect       | No Detect          | GL2                | GL2                          |  |

| Short to GND Case 1   | No Detect       | No Detect          | GH1                | No Detect                    |  |

| Short to GND Case 2   | No Detect       | GH2                | No Detect          | No Detect                    |  |

| SH1 to SH2 Pins Short | No Detect       | GH2 and GL1        | GH1 and GL2        | No Detect                    |  |

## Table 1. VDS Monitors Triggered Per Operating Mode

## 3 Conclusion

4

Monitoring overcurrent conditions with VDS monitors is an easy to way detect what type of short circuit condition occurred. With a SPI interface, designers can quickly identify the location of the overcurrent condition and take action appropriately to prevent any system damage and draw conclusions on what type of overcurrent condition occurred.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated