Sample &

Buy

#### UCC24636

Reference

Design

ZHCSES5A-MARCH 2016-REVISED MARCH 2016

# UCC24636 具有超低待机电流的同步整流器 (SR) 控制器

Technical

Documents

## 1 特性

- 针对 5V 至 24V 输出断续/转换模式反激转换器而优 化的二次侧 SR 控制器

- 通过伏秒平衡控制实现最高整流器效率

- 兼容一次侧同步整流器 (PSR) 和二次侧同步整流器 (SSR) 反激控制器

- 110µA 超低待机电流消耗

- 通过自动检测待机模式禁用 SR 开关以降低无负载 时的功耗

- SR 关断与 R<sub>DSON</sub> 和寄生电感无关

- 工作频率高达 130kHz

- 宽 VDD 范围: 3.6V 至 28V

- 自适应栅极驱动钳位

- 开路和短路引脚故障保护

## 2 应用

- 智能手机和平板电脑的 AC/DC 适配器

- 带有 Type-C 连接器的 USB 充电器

- 笔记本电脑和超极本适配器

- 工业用开关模式电源 (SMPS) 中的高效率反激转换器

- 服务器和台式机中的高效率辅助电源 应用

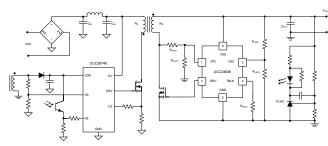

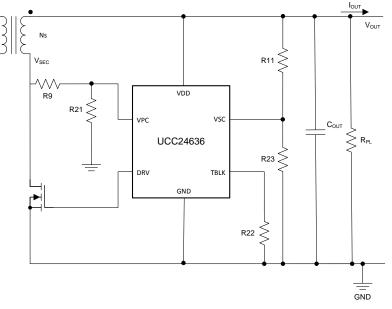

## 简化电路原理图

## 3 说明

Tools &

Software

UCC24636 SR 是一款紧凑型 6 引脚二次侧同步整流 器 MOSFET 控制器和驱动器,适用于在断续 (DCM) 和转换模式 (TM) 下工作的高效率反激转换器。与测量 SR MOSFET 漏极电压的传统 SR 控制器不同的 是,UCC24636 采用伏秒平衡控制方案来确定 SR MOSFET 的关闭转换;因此,SR 导通时间与 MOSFET R<sub>DSON</sub>、寄生电感或振铃无关,这在组件选 择和 PCB 布局布线方面给予了设计人员更大的灵活 性。该控制方法可为给定的 MOSFET 实现最长的 SR 导通时间和最高的整流器效率。

Support &

Community

2.2

该控制器内置智能特性,可在检测到转换器中无负载运行时自动进入待机模式。在待机模式下,它会禁用 SR MOSFET 并将其偏置电源电流降至 110uA,从而进一步降低总体系统待机功耗。该控制器具有较宽的 VDD 工作电压范围,允许直接从控制器输出获取偏置电压以实现输出电压固定或可变的设计。这消除了主变压器对辅助绕组的需求,从而简化电路设计并降低成本。

#### 器件信息<sup>(1)</sup>

| 器件型号     | 封装        | 封装尺寸(标称值)       |

|----------|-----------|-----------------|

| UCC24636 | SOT23 (6) | 2.92mm x 1.30mm |

|          |           |                 |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

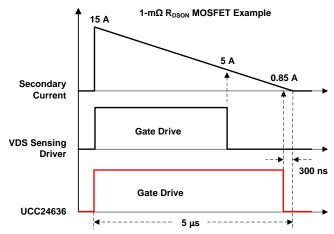

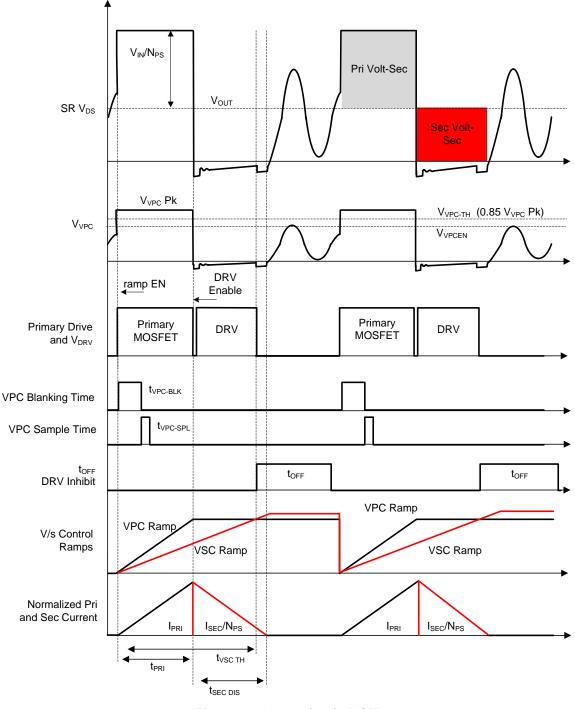

#### 栅极驱动时序与 VDS 感测 SR 驱动器间的关系

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# 目录

| 1 | 特性   |                                    |

|---|------|------------------------------------|

| 2 | 应用   |                                    |

| 3 | 说明   | 1                                  |

| 4 | 修订   | 历史记录 2                             |

| 5 | Dev  | ice Comparison Table 3             |

| 6 | Pin  | Configuration and Functions 3      |

| 7 | Spe  | cifications 4                      |

|   | 7.1  | Absolute Maximum Ratings 4         |

|   | 7.2  | ESD Ratings 4                      |

|   | 7.3  | Recommended Operating Conditions 4 |

|   | 7.4  | Thermal Information 4              |

|   | 7.5  | Electrical Characteristics5        |

|   | 7.6  | Timing Requirements 6              |

|   | 7.7  | Typical Characteristics 7          |

| 8 | Deta | ailed Description                  |

|   | 8.1  | Overview                           |

|   | 8.2  | Functional Block Diagram9          |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

#### Changes from Original (December 2015) to Revision A

已将器件状态从"产品预览"更改为"量产数据"并已发布完整数据表。......1

|    | 8.3  | Feature Description         | 10 |

|----|------|-----------------------------|----|

|    | 8.4  | Device Functional Modes     | 19 |

| 9  | App  | lication and Implementation | 20 |

|    | 9.1  | Application Information     | 20 |

|    | 9.2  | Typical Application         | 20 |

|    | 9.3  | Do's and Don'ts             | 27 |

| 10 | Pow  | ver Supply Recommendations  | 27 |

| 11 | Laye | out                         | 28 |

|    | 11.1 | Layout Guidelines           | 28 |

|    | 11.2 | Layout Example              | 29 |

| 12 | 器件   | 和文档支持                       | 30 |

|    | 12.1 | 器件支持                        | 30 |

|    | 12.2 | 文档支持                        | 30 |

|    | 12.3 | 商标                          | 30 |

|    | 12.4 | 静电放电警告                      | 30 |

|    | 12.5 | Glossary                    | 30 |

| 13 | 机械   | 、封装和可订购信息                   | 30 |

|    |      |                             |    |

#### TEXAS INSTRUMENTS

www.ti.com.cn

Page

## 5 Device Comparison Table

| PART NUMBER | CCM DEAD TIME CONTROL | t <sub>OFF</sub> (μs) | F <sub>SW(MAX)</sub> (kHz) |

|-------------|-----------------------|-----------------------|----------------------------|

| UCC24636    | No                    | 4.35                  | 130                        |

| UCC24630    | Yes                   | 2.5                   | 200                        |

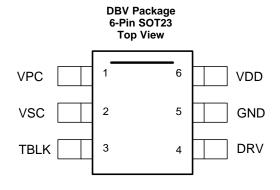

## 6 Pin Configuration and Functions

#### **Pin Functions**

| l   | PIN  | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |

|-----|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME | 10.                | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |

| 1   | VPC  | I                  | The <b>Voltage during Primary Conduction</b> pin is connected to a resistor divider from the SR MOSFET drain. This pin determines a sample of the primary-side MOSFET volt seconds during the primary on-time. This voltage programs a voltage controlled current source for the internal VPC ramp charging current.                     |

| 2   | VSC  | I                  | The <b>Voltage during Secondary Conduction</b> pin is connected to a resistor divider from the power-supply output. This pin determines a sample of the secondary-side output voltage used to determine SR MOSFET conduction time. This voltage programs a voltage controlled current source for the internal VSC ramp charging current. |

| 3   | TBLK | _                  | <b>TIME BLANK</b> pin is used to select the blanking time of the VPC rising edge. A programmable range from 200 ns to 2 µs is available to prevent false detection of the primary on-time due to ringing during DCM operation.                                                                                                           |

| 4   | DRV  | 0                  | <b>DRIVE</b> is an output used to drive the gate of an external synchronous rectifier N-channel MOSFET switching transistor, with source pin connected to GND.                                                                                                                                                                           |

| 5   | GND  | G                  | The <b>GROUND</b> pin is both the reference pin for the controller and the low-side return for the drive output. Special care should be taken to return all AC decoupling capacitors as close as possible to this pin and avoid any common trace length with analog signal return paths.                                                 |

| 6   | VDD  | Р                  | <b>VDD</b> is the bias supply input pin to the controller. A carefully placed bypass capacitor to GND is required on this pin.                                                                                                                                                                                                           |

(1) P = Power, G = Ground, I = Input, O = Output, I/O = Input/Output

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                    |                                                  | MIN  | MAX           | UNIT |

|--------------------|--------------------------------------------------|------|---------------|------|

| V <sub>VDD</sub>   | Bias supply voltage, VDD                         | -0.3 | 30            | V    |

| I <sub>DRV</sub>   | Continuous gate current sink, DRV                |      | 50            | mA   |

| I <sub>DRV</sub>   | Continuous gate current source, DRV              |      | -50           | mA   |

| I <sub>VPC</sub>   | Peak VPC pin current                             |      | -1.2          | mA   |

| V <sub>DRV</sub>   | Gate drive voltage at DRV                        | -0.3 | Self-limiting | V    |

| $V_{VPC}, V_{VSC}$ | Voltage range, VPC, VSC                          | -0.3 | 4.5           | V    |

| TJ                 | Operating junction temperature range             | -55  | 150           | °C   |

| TL                 | Lead temperature 0.6 mm from case for 10 seconds |      | 260           | °C   |

| T <sub>stg</sub>   | Storage temperature                              | -65  | 150           | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|        |               |                                                                                | VALUE | UNIT |

|--------|---------------|--------------------------------------------------------------------------------|-------|------|

| V      | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | M    |

| V(ESD) | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

JEDEC document JEP155 states that 2000-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 500-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±500 V may actually have higher performance.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                 |                                | MIN  | MAX | UNIT |

|---------------------------------|--------------------------------|------|-----|------|

| V <sub>VDD</sub>                | Bias supply operating voltage  | 3.75 | 28  | V    |

| C <sub>VDD</sub>                | VDD bypass capacitor           | 0.22 |     | μF   |

| TJ                              | Operating junction temperature | -40  | 125 | °C   |

| $V_{\text{VPC}},V_{\text{VSC}}$ | Operating range                | -0.3 | 2.2 | V    |

#### 7.4 Thermal Information

|                       |                                              | UCC24636    |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DBV (SOT23) | UNIT |

|                       |                                              | 6 PINS      |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 180         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 71.2        | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 44          | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 5.1         | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 13.8        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

UCC24636 ZHCSES5A – MARCH 2016 – REVISED MARCH 2016

www.ti.com.cn

#### 7.5 Electrical Characteristics

over operating free-air temperature, VDD = 12 V,  $T_A = -40^{\circ}$ C to 125°C,  $T_A = T_J$  (unless otherwise noted)

|                          | PARAMETER                                       | TEST CONDITION                                                                                                                     | MIN   | TYP   | MAX  | UNIT |

|--------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|------|

| SUPPLY INPUT             | Г                                               | - · · · ·                                                                                                                          |       |       |      |      |

| I <sub>RUN</sub>         | Supply current, run                             | $I_{DRV} = 0$ , run state, $F_{SW} = 0$ kHz                                                                                        |       | 0.9   | 1.2  | mA   |

| I <sub>STBY</sub>        | Supply current, standby                         | I <sub>DRV</sub> = 0, standby mode                                                                                                 |       | 110   | 160  | μA   |

| UNDER-VOLTA              | AGE LOCKOUT                                     |                                                                                                                                    |       |       |      |      |

| V <sub>VDD(on)</sub>     | VDD turn-on threshold                           | V <sub>VDD</sub> low to high                                                                                                       | 3.9   | 4     | 4.3  | V    |

| V <sub>VDD(off)</sub>    | VDD turn-off threshold                          | V <sub>VDD</sub> high to low                                                                                                       | 3.3   | 3.6   | 3.7  | V    |

| DRV                      |                                                 |                                                                                                                                    |       |       |      |      |

| R <sub>DRVLS</sub>       | DRV low-side drive resistance                   | I <sub>DRV</sub> = 100 mA                                                                                                          |       | 1     | 2    | Ω    |

| V <sub>DRVST</sub>       | DRV pull down in start-up                       | V <sub>DD</sub> = 0 to 2 V, I <sub>DRV</sub> = 10 µA                                                                               |       |       | 0.95 | V    |

| V <sub>DRCL</sub>        | DRV clamp voltage                               | V <sub>VDD</sub> = 30 V                                                                                                            | 11    | 13    | 15   | V    |

| V <sub>PMOS</sub>        | Disable PMOS high-side drive                    | $V_{\text{DD}}$ voltage to disable rail-to-rail drive, $V_{\text{DD}}$ rising                                                      | 9.3   | 10    | 10.5 | V    |

| V <sub>PMOS-HYS</sub>    | PMOS enable hysteresis                          | $V_{\text{DD}}$ voltage hysteresis to enable rail to rail drive, $V_{\text{DD}}$ falling                                           | 0.75  | 1     | 1.25 | V    |

| V <sub>DRHI</sub>        | DRV pull-up high voltage                        | V <sub>VDD</sub> = 5 V, I <sub>DRV</sub> = 15 mA                                                                                   | 4.6   | 4.75  | 5    | V    |

| VSC INPUT                |                                                 | · · · · ·                                                                                                                          |       |       | 1    |      |

| V <sub>VSCEN</sub>       | SR enable voltage                               | $V_{VSC} > V_{VSCEN}, V_{VSC}$ rising                                                                                              | 250   | 300   | 340  | mV   |

| V <sub>VSC-HYS</sub>     | SR enable hysteresis                            | V <sub>VSC</sub> falling                                                                                                           |       | 50    |      | mV   |

| V <sub>VSCDIS</sub>      | SR disable voltage                              |                                                                                                                                    | 220   | 250   | 280  | mV   |

| I <sub>VSC</sub>         | Input bias current                              | V <sub>VSC</sub> = 2 V                                                                                                             | -0.25 | 0     | 0.4  | μA   |

| VPC INPUT                |                                                 |                                                                                                                                    |       |       |      |      |

| V <sub>VPCEN</sub>       | SR enable voltage                               | V <sub>VPCEN</sub> < V <sub>VPC</sub>                                                                                              | 345   | 400   | 450  | mV   |

| V <sub>VPCDIS</sub>      | VPC threshold to disable SR                     | V <sub>VPC</sub> > V <sub>VPCDIS</sub>                                                                                             | 2.6   | 2.85  | 3.1  | V    |

| V <sub>VPC-TH</sub>      | Threshold of $V_{VPC}$ rising edge              | $V_{VPC} = 0.95 \text{ V}, V_{VPC-TH} = 0.85 \text{ x} V_{VPC}$<br>previous cycle                                                  | 0.76  | 0.808 | 0.86 | V    |

| V <sub>VPC-TH-CLP</sub>  | Clamp threshold of V <sub>VPC</sub> rising edge | V <sub>VPC</sub> = 2 V                                                                                                             | 0.9   | 1     | 1.1  | V    |

| I <sub>VPC</sub>         | Input bias current                              | V <sub>VPC</sub> = 2 V                                                                                                             | -0.25 | 0     | 0.4  | μA   |

| CURRENT EMU              | JLATOR                                          |                                                                                                                                    |       |       |      |      |

|                          |                                                 | $\label{eq:VVPC} \begin{array}{l} V_{VPC} = 1.25 \ V, \ t_{VPC} = 1 \ \mu s, \\ V_{VSC} = 1.25 \ V \end{array}$                    | 3.97  | 4.17  | 4.35 |      |

| Potio                    | K IK                                            | $\label{eq:VPC} \begin{array}{l} V_{VPC} = 1.25 \ \text{V}, \ t_{VPC} = 5 \ \mu\text{s}, \\ V_{VSC} = 1.25 \ \text{V} \end{array}$ | 3.95  | 4.17  | 4.37 |      |

| Ratio <sub>VPC_VSC</sub> | K <sub>VPC</sub> /K <sub>VSC</sub>              |                                                                                                                                    | 3.85  | 4.09  | 4.26 |      |

|                          |                                                 | $\label{eq:VPC} \begin{array}{l} V_{VPC} = 1.25 \ V, \ t_{VPC} = 1 \ \mu s, \\ V_{VSC} = 0.45 \ V \end{array}$                     | 3.85  | 4.07  | 4.28 |      |

## **Electrical Characteristics (continued)**

over operating free-air temperature, VDD = 12 V,  $T_A = -40^{\circ}C$  to 125°C,  $T_A = T_J$  (unless otherwise noted)

|                             | <b>o i</b> <i>i i i i</i>                                                         | / A 51                        |     | ,   |     |      |  |  |

|-----------------------------|-----------------------------------------------------------------------------------|-------------------------------|-----|-----|-----|------|--|--|

|                             | PARAMETER                                                                         | TEST CONDITION                | MIN | TYP | MAX | UNIT |  |  |

| STANDBY O                   | PERATION                                                                          |                               |     |     |     |      |  |  |

| n <sub>ENTO</sub>           | Number of switching cycles to enter standby operation during t <sub>ENTO</sub>    |                               |     | 64  |     |      |  |  |

| n <sub>EN</sub>             | Number of switching cycles to exit standby operation during $t_{\text{EN}}^{(1)}$ |                               |     | 32  |     |      |  |  |

| OVER TEMPERATURE PROTECTION |                                                                                   |                               |     |     |     |      |  |  |

| T <sub>(STOP)</sub>         | Thermal shutdown temperature                                                      | Internal junction temperature |     | 165 |     | °C   |  |  |

(1) The device exits standby operation as soon as  $n_{\text{EN}}$  occurs within  $t_{\text{EN}}.$

#### 7.6 Timing Requirements

over operating free-air temperature range, VDD = 12 V,  $T_A = -40^{\circ}C$  to 125°C,  $T_A = T_J$  (unless otherwise noted)

|                      | PARAMETER                                           | TEST CONDITION                                                                                                                | MIN  | TYP  | MAX  | UNIT |

|----------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| DRV                  |                                                     | •                                                                                                                             |      |      |      |      |

|                      | DD)/ high aide rise time                            | $V_{VDD}$ = 12 V, $C_L$ = 3.3 nF, $V_{DRV}$ = 2 V to 8 V                                                                      |      | 27   | 54   | ~~   |

| t <sub>R</sub>       | DRV high-side rise time                             | $V_{VDD}$ = 5 V, $C_L$ = 3.3 nF, $V_{DRV}$ = 1 V to 4 V                                                                       |      | 50   | 100  | ns   |

|                      | DRV low-side fall time                              | $V_{VDD}$ = 12 V, $C_L$ = 3.3 nF, $V_{DRV}$ = 8 V to 2 V                                                                      |      | 20   | 54   | ns   |

| t <sub>F</sub>       | DRV low-side fail time                              | $V_{VDD}$ = 5 V, $C_L$ = 3.3 nF, $V_{DRV}$ = 4 V to 1 V                                                                       |      | 15   | 50   | ns   |

| t <sub>DRVON</sub>   | Propagation delay to DRV High                       | $      V_{VPC} = 1 \ V \ to -0.05 \ V \ falling \ to \ DRV \ high, \\      V_{VDD} = 12 \ V, \ V_{DRV} = 0 \ V \ to \ 2 \ V $ |      | 80   | 160  | ns   |

| t <sub>DRVOFF</sub>  | Propagation delay to DRV Low                        | Test mode                                                                                                                     |      | 65   | 95   | ns   |

| VPC INPU             | т                                                   |                                                                                                                               |      |      |      |      |

| t <sub>VPC-SPL</sub> | VPC sampling time window                            |                                                                                                                               | 81   | 100  | 125  | ns   |

|                      | Minimum VPC pulse for SR DRV                        | $R_{TBLK} = 5 k\Omega$                                                                                                        | 169  | 203  | 239  | ns   |

| t <sub>VPC-BLK</sub> | operation                                           | $R_{TBLK} = 50 \ k\Omega$                                                                                                     | 0.85 | 1.01 | 1.18 | μs   |

| SR ON CO             | NTROL                                               |                                                                                                                               |      |      |      |      |

| t <sub>SRONMIN</sub> | SR minimum on time after VPC falling.               |                                                                                                                               | 300  | 350  | 425  | ns   |

| t <sub>OFF</sub>     | SR off blanking time from DRV falling.              |                                                                                                                               | 3.96 | 4.35 | 4.75 | us   |

| STANDBY              | OPERATION                                           |                                                                                                                               |      |      |      |      |

| t <sub>ENTO</sub>    | Time to disable SR operation, enter standby         | Time to disable DRV                                                                                                           | 11.5 | 12.8 | 14.1 | ms   |

| t <sub>EN</sub>      | Time to enable SR operation, exit standby operation | Time to enable DRV <sup>(1)</sup>                                                                                             | 2.3  | 2.56 | 2.82 | ms   |

(1) The device exits standby operation as soon as  $n_{\text{EN}}$  occurs within  $t_{\text{EN}}.$

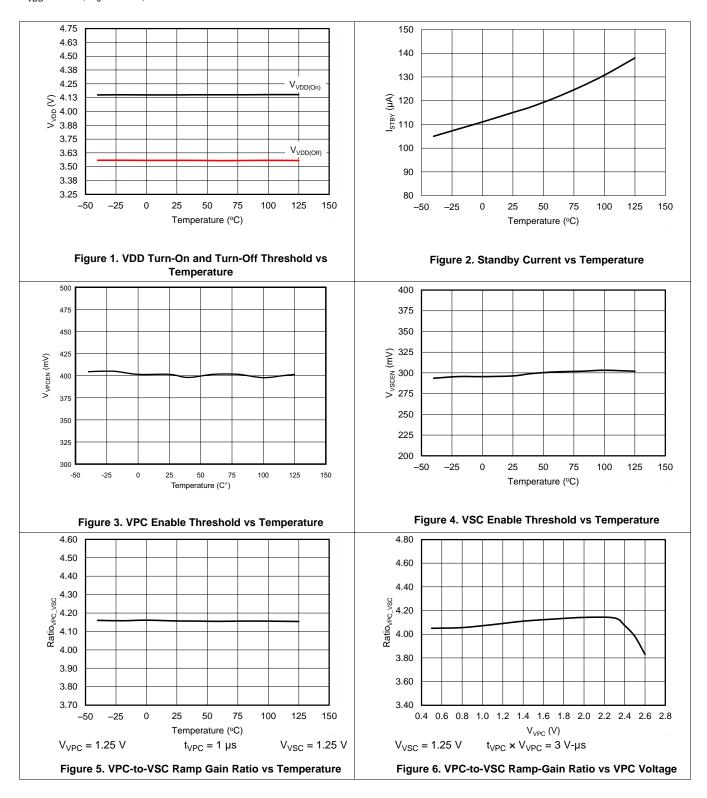

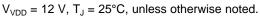

## 7.7 Typical Characteristics

$V_{VDD}$  = 12 V,  $T_J$  = 25°C, unless otherwise noted.

UCC24636 ZHCSES5A-MARCH 2016-REVISED MARCH 2016

www.ti.com.cn

## **Typical Characteristics (continued)**

## 8 Detailed Description

#### 8.1 Overview

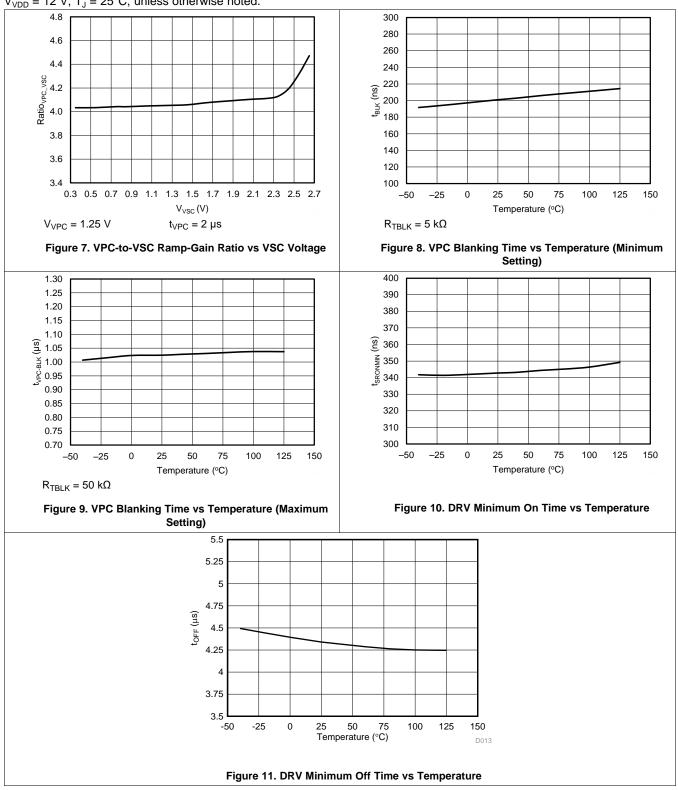

The UCC24636 SR controller is targeted for flyback converters operating in DCM and TM modes of operation. The control method to determine SR on time is based on the volt-second balance principle of primary and secondary conduction volt-second product. In converters operating in DCM and TM, the secondary current always returns to zero in each cycle. The inductor charge voltage and time product is equal to the discharge voltage and time product. The device uses internal current ramp emulators to predict the proper SR on time based on voltage and time information on the VPC and VSC pins.

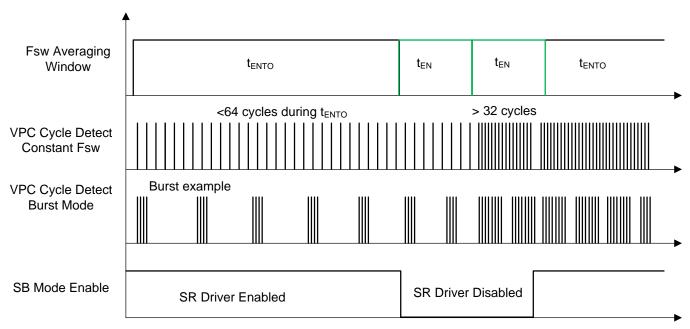

To achieve very low standby power in the converter, the UCC24636 has a standby mode of operation that disables the SR MOSFET drive and reduces the device bias current to  $I_{STBY}$ . The device monitors the average switching frequency of the converter to enter and exit the standby mode of operation, and is compatible with converters operating in burst mode or constant frequency in light-load mode.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

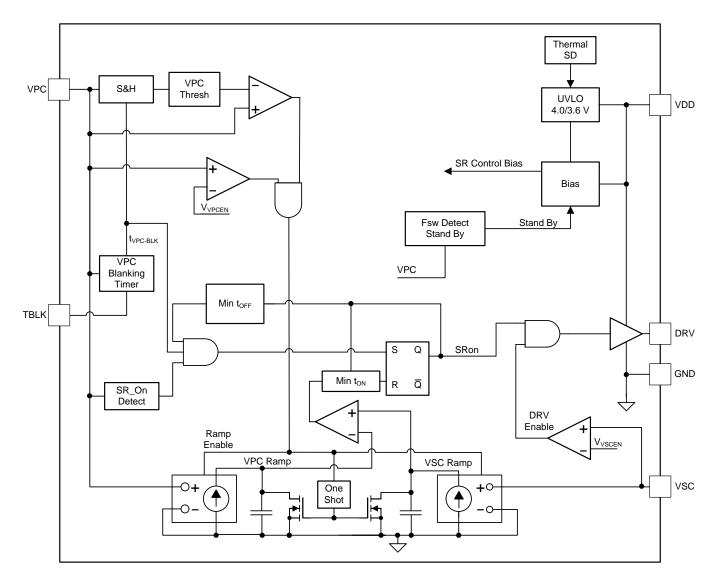

#### 8.3.1 Start Up and UVLO

The UCC24636 features a wide operating VDD range and low UVLO thresholds. The start up of the device is dependent on voltage levels on three pins: VDD, VPC and VSC. The VDD pin can be directly connected to the power supply output on converters from 5-V to 24-V nominal outputs. The start UVLO threshold is  $V_{VDD(on)}$ , 4.0 V typical, and stop threshold is  $V_{VDD(off)}$ , 3.6 V typical. The DRV output is not enabled unless the voltage on the VPC pin is greater than  $V_{VPCEN}$  for a time longer than  $t_{VPC-BLK}$  and the voltage on the VSC pin is greater than  $V_{VSCEN}$ . Once the VDD, VSC and VPC voltage and time thresholds are met, there is an internal initialization time before the DRV output is enabled.

Refer to Figure 12 for a startup sequence that illustrates the timing sequence and configurable DRV output based on VDD level. In most converter designs, the conditions for the VPC and VSC voltage to enable the device are met before the VDD start-voltage threshold, this is reflected in the timing diagram. When VDD exceeds  $V_{VDD(on)}$  UVLO threshold the device starts the initialization sequence of 150 µs to 250 µs illustrated as  $t_{INITIALIZE}$ . After the device initialization, there is a logic initialization of 20 µs at which time  $V_{TBLK}$  is enabled (high). At VDD <  $V_{PMOS}$  the driver high-side PMOS device is enabled and the DRV peak will be close to VDD. When VDD exceeds  $V_{PMOS}$  the PMOS device is disabled and the driver is operating as a high-side NMOS only and DRV is approximately 1.2 V to 1.5 V lower than VDD. As VDD continues to increase, the DRV output is limited to  $V_{DRCL}$  regardless of VDD up to the recommended maximum rating.

Figure 12. Start-Up Operation

#### **Feature Description (continued)**

#### 8.3.2 Volt-Sec SR Driver On-Time Control

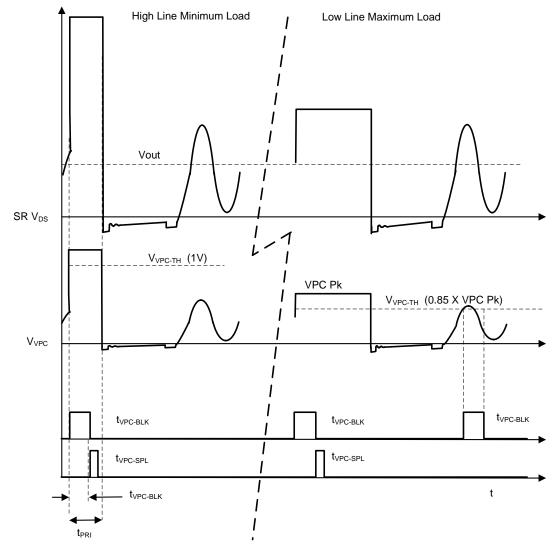

Refer to the timing diagrams in Figure 13 for functional details of the UCC24636 volt-sec on-time control.

Figure 13. Operation in DCM

#### UCC24636 ZHCSES5A – MARCH 2016–REVISED MARCH 2016

#### Feature Description (continued)

The UCC24636 uses the VPC and VSC pins to sense the SR MOSFET V<sub>DS</sub> voltage and converter V<sub>OUT</sub> voltage through resistor dividers. The information of V<sub>IN</sub>/N<sub>PS</sub>, t<sub>PRI</sub>, and V<sub>OUT</sub> can be obtained from the information on VPC and VSC pins. The SR MOSFET turn on is determined when the SR MOSFET body diode starts conducting and the VPC pin voltage falls to near zero; the SR MOSFET turn off is determined by the current emulator control ramps.

The UCC24636 volt-sec control generates the internal VPC ramp and VSC ramp to emulate the transformer Volt-Sec balancing as shown in Figure 13.

The secondary current discharge time,  $t_{SEC-DIS}$  can be determined indirectly. The primary volt-sec ramp and secondary volt-sec ramp both start when VPC rises above  $V_{VPC-EN}$  and  $V_{VPC-TH}$ . The charge currents for the VPC and VSC ramps are determined by the voltage on the VPC and VSC pins respectively.

When VPC is higher than  $V_{VPC-EN}$  and  $V_{VPC-TH}$  for t > t<sub>VPC-BLK</sub>, the VPC pulse is qualified as a primary conduction pulse and the SR can be enabled on the VPC falling edge. The VPC ramp continues to rise until the VPC falling edge based on the real time voltage on the VPC pin and holds the peak for the cycle. The DRV output is turned on during the VPC falling edge near zero volts, and DRV is turned off when the VSC rising ramp crosses the VPC ramp held level.

Both VPC and VSC ramps are reset to zero on each VPC rising edge above the V<sub>VPC-EN</sub> and V<sub>VPC-TH</sub> thresholds.

To discriminate primary on-time pulses from DCM ringing, there are voltage and time criteria that must be satisfied on the VPC pin to enable the DRV output. t<sub>VPC-BLK</sub> can be adjusted through the resistor on TBLK pin.

At the rising edge of VPC when the voltage exceeds  $V_{VPC-EN}$  and  $V_{VPC-TH}$  the blanking time  $t_{VPC-BLK}$  is initiated. At the end of  $t_{VPC-BLK}$ , the VPC voltage is sampled during  $t_{VPC-SPL}$  window, which is 100 ns nominal. Also at the end of  $t_{VPC-BLK}$ , the DRV output can be enabled.

The VPC voltage sampled during  $t_{VPC-SPL}$  determines the VPC dynamic threshold  $V_{VPC-TH}$  which is normally 85% of the sampled VPC voltage. The dynamic threshold provides the ability to reject the DCM ringing and detect the primary on-time. Noise immunity during the turn-on event of DRV at the falling edge of the VPC pin is enhanced by a minimum DRV on time of  $t_{SRONMIN}$ , which is 350 ns nominal.

During the falling edge of DRV, the t<sub>OFF</sub> timer is initiated which inhibits turn on of the SR until t<sub>OFF</sub> expires. This eliminates false turn on of DRV if the DCM ringing is close to ground.

#### Feature Description (continued)

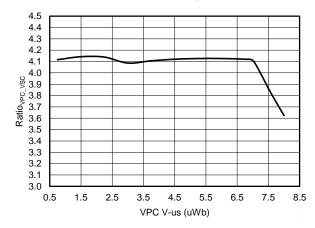

The UCC24636 is designed to operate in a variety of flyback converter applications over a wide operating range. The internal volt-sec control ramps do have a dynamic range limit based on volt-sec on the VPC pin. As shown in Figure 14, a Volt-sec product exceeding 7 V- $\mu$ s on the VPC pin will result in saturation of the VPC volt-sec control ramp. Operation beyond this point results in a DRV on-time less than expected. For example, if V<sub>VPC</sub> = 0.5 V, t<sub>VPC</sub> should be < 14  $\mu$ s, or if V<sub>VPC</sub> = 2.0 V, t<sub>VPC</sub> should be < 3.5  $\mu$ s, to operate within the dynamic range of the device. Assuming a converter operating in transition mode at low line and full load with a 50% duty cycle, the operating period is 28  $\mu$ s which results in a frequency that is under 40 kHz. The UCC24636 low-frequency operating range extends to the standby mode threshold of 5 kHz; but each switching cycle V<sub>VPC</sub> Volt-sec product should be less than 7 V- $\mu$ s.

The device can support switching frequencies exceeding 130 kHz but the following timing limits need to be confirmed to be compatible with the power train. The minimum primary on time when the device is expected to be active needs to be compatible with the minimum VPC blanking time  $(t_{VPC-BLK})$  setting of 203 ns plus the sampling window  $(t_{VPC-SPL})$  of 100 ns. The minimum secondary current conduction time should be greater than the minimum SR on time  $(t_{SRONMIN})$  of 350 ns. The minimum time from the SR drive turn off until the next SR drive turn on should be greater than the SR minimum off time  $(t_{OFF})$  of 4.35 µs.

Figure 14. Ratio<sub>VPC VSC</sub> vs VPC V-µs

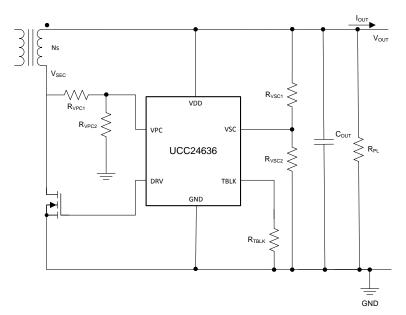

Figure 15. SR Controller Components

#### Feature Description (continued)

Determining the VPC and VSC divider resistors is based on the operating voltage ranges of the converter and Ratio<sub>VPC-VSC</sub> gain ratio. Referring to Figure 15, the following equation determines the VPC divider values.

For  $R_{VPC2}$ , a value of 10 k $\Omega$  is recommended for minimal impact on time delay, and low-resistor dissipation. A higher  $R_{VPC2}$  value reduces resistor divider dissipation but may increase the DRV turn-on delay due to the time constant of ~2 pF pin capacitance and divider resistance. A lower  $R_{VPC2}$  value can be used with the tradeoff of higher dissipation in the resistor divider. A factor of 10% over the VPC threshold,  $V_{VPCEN}$ , is shown in Equation 1 for design margin.

$$R_{VPC1} = \frac{\left[\left(\frac{V_{IN(min)}}{N_{PS}} + V_{OUT(min)}\right) - V_{VPCEN} \times 1.1\right] \times R_{VPC2}}{V_{VPCEN} \times 1.1}$$

where

- $V_{IN(min)}$  is the converter minimum primary bulk capacitor voltage.

- V<sub>OUT(min)</sub> is the minimum converter output voltage in normal operation.

- V<sub>VPCEN</sub> is the VPC enable threshold, use the specified maximum value.

- N<sub>PS</sub> is the transformer primary to secondary turns ratio.

The operating voltage range on the VPC pin should be within the range of 0.45 V <  $V_{VPC}$  < 2.2 V. Referring to Figure 6, if  $V_{VPC}$  is greater than 2.3 V the linear dynamic range is exceeded and Ratio<sub>VPC\_VSC</sub> is reduced; in this condition the DRV on time is less than expected. If  $V_{VPC}$  is greater than 2.6 V for 500 ns, a fault is generated and DRV is disabled for the cycle, refer to Pin Fault Protection. To ensure the maximum voltage is within range confirm with Equation 2.

$$V_{\text{VPC(max)}} = \frac{\left(\frac{V_{\text{IN(max)}}}{N_{\text{PS}}} + V_{\text{OUT(max)}}\right) \times R_{\text{VPC2}}}{R_{\text{VPC1}} + R_{\text{VPC2}}}$$

where

- V<sub>IN(max)</sub> is the converter maximum primary bulk capacitor voltage.

- V<sub>OUT(max)</sub> is the maximum converter output voltage at OVP.

N<sub>PS</sub> is the transformer primary-to-secondary turns ratio.

The program voltage on the VSC pin is determined by the VPC divider ratio and the device's parameter Ratio\_{VPC\_VSC}. The current emulator ramp gain is higher on the VPC pin by the multiple Ratio\_{VPC\_VSC}, so the VSC resistor divider ratio is reduced by the same Ratio\_{VPC\_VSC} accordingly. Determine the VSC divider resistors using Equation 3 below. To minimize resistor divider dissipation, a recommended range for R<sub>VSC2</sub> is 25 k $\Omega$  to 50 k $\Omega$ . Higher R<sub>VSC2</sub> values results in increasing offset due to VSC input current, I<sub>VSC</sub>. Lower R<sub>VSC2</sub> values increases the resistor divider dissipation. To ensure DRV turn off slightly before the secondary current reaches zero, 10% margin is shown for initial values. Use a nominal value of 4.15 for Ratio\_{VPC\_VSC}.

$$R_{VSC1} = \left[ \left( \frac{\frac{R_{VPC1} + R_{VPC2}}{R_{VPC2}}}{R_{atio_{VPC} - VSC} \times 1.1} \right) - 1 \right] \times R_{VSC2}$$

where

Ratio<sub>VPC\_VSC</sub> is the device parameter VPC and VSC gain ratio, use a value of 4.15.

(3)

(1) n to

(2)

14

(4)

(5)

(6)

(7)

#### Feature Description (continued)

The operating voltage on the VSC pin should be within the range of 0.3 V <  $V_{VSC}$  < 2.2 V. Referring to Figure 7, if  $V_{VSC}$  is greater than 2.3 V, the linear dynamic range is exceeded and Ratio<sub>VPC\_VSC</sub> is increased; in this condition the DRV on time is more than expected, resulting in possible negative current conduction. To ensure the VSC voltage is within range, confirm with Equation 4 and Equation 5.

$$\frac{R_{VSC2}}{R_{VSC1} + R_{VSC2}} \times V_{OUT(min)} \ge 0.3V$$

$$\frac{R_{VSC2}}{R_{VSC1} + R_{VSC2}} \times V_{OUT(max)} \le 2.2 V$$

where

- V<sub>OUT(min)</sub> is the minimum converter output operating voltage of the SR controller.

- V<sub>OUT(max)</sub> is the maximum converter output operating voltage of the voltage at OVP.

Discrimination of ringing during DCM operation from valid primary on-time is achieved by a dynamic VPC rising threshold and programmable blanking time. The dynamic threshold  $V_{VPC-TH}$  is 85% typical ratio of the previous VPC pin peak voltage. Referring to Figure 13, the VPC pin voltage is sampled after the VPC voltage is greater than  $V_{VPCEN}$  and  $V_{VPC-TH}$  for t >  $t_{VPC-BLK}$ . The function of the dynamic threshold  $V_{VPC-TH}$  is to reject the ringing in DCM operation from the primary conduction pulses. The dynamic threshold has an active range from the minimum  $V_{VPCEN}$  voltage to a maximum of 1-V clamp. The blanking time is programmable from 200 ns to 2 µs in order to accommodate a variety of converter designs.

Refer to Figure 16 for guidance on selecting the blanking time. The blanking time should be selected as long as reasonable and still accommodate the minimum primary on-time at light-load condition and high-line voltage. In the high-line minimum load condition, select a blanking time that meets the following criteria (Equation 6) to accommodate tolerance of the blanking time and the  $t_{VPC-SPL}$  sampling time window.

$$t_{VPC-BLK} = (t_{PRI} \times 0.85) - 120 \text{ ns}$$

For rejection of DCM ringing, the blanking time should be longer than the time that the ring is above the  $V_{VPC-TH}$  dynamic threshold, which is 85% of the minimum SR VDS peak voltage. Determine these criteria at low line and maximum load condition. It is recommended that the transformer turns ratio be selected such that the secondary reflected voltage is < 85% of  $V_{IN(min)}$  bulk capacitor voltage at the highest load when DCM operation occurs at the low line input condition.

To determine the resistor value for t<sub>VPC-BLK</sub> use Equation 7 to select from a range of 200 ns to 2 µs.

$$R_{TBLK} = \frac{t_{VPC-BLK} - 100 \text{ ns}}{18 \text{ pF}}$$

where

• t<sub>VPC-BLK</sub> is the target blanking time.

Additional discrimination for proper SR timing control is provided by the  $t_{OFF}$  function. Refer to Figure 13 for the timing details. After the DRV turn off, the DRV is inhibited from turning on again until the  $t_{OFF}$  timer expires. This protects against SR false turn on from SR V<sub>DS</sub> DCM ringing below ground.

TEXAS INSTRUMENTS

www.ti.com.cn

## Feature Description (continued)

Figure 16. VPC Blanking Time Criteria

#### **Feature Description (continued)**

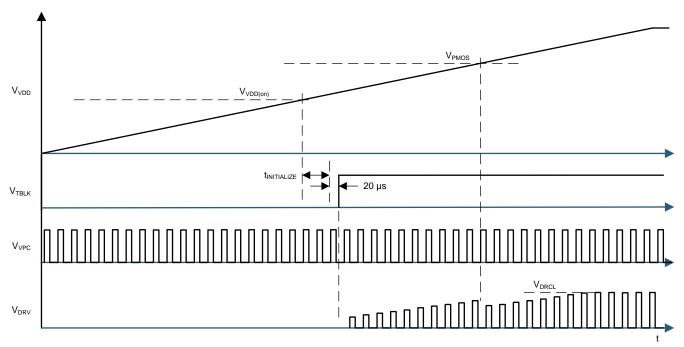

#### 8.3.3 Standby Operation

To minimize power consumption at very light load and standby conditions, the UCC24636 disables the SR DRV output and enters a low current operating state. The criteria for operating in standby mode or normal operation are determined by the average frequency detected on the VPC pin. The frequency detection is compatible with burst mode operation or continuous low frequency FM operation. At start up the device is in normal operation to enable DRV to the SR MOSFET. If < 64 cycles occur in  $t_{ENTO}$ ,12.8 ms typical, the device disables the DRV output and enters low-current operating mode with bias current of  $I_{STBY}$ . In standby mode the criteria to enter normal operating mode is when > 32 cycles occur within  $t_{EN}$ , 2.56 ms typical. The device enters normal operation as soon as the 32 cycles occur to reduce the response time exiting standby operation. The average frequency of entering standby mode is 5 kHz typical, and the average frequency of exiting standby mode is 12.5 kHz typical. Refer to Figure 17 for an illustration of standby mode timing.

Figure 17. Standby Mode Operation

#### Feature Description (continued)

#### 8.3.4 Pin Fault Protection

The UCC24636 controller includes fault protection in the event of open pin, shorted pin to ground and abnormal out of range operation.

#### 8.3.4.1 VPC Pin Overvoltage

In the event that there is an abnormal high level on the VPC pin for a period beyond expected transformer leakage spike duration, the DRV output is disabled on a cycle-to-cycle basis. If the voltage on the VPC pin exceeds  $V_{VPCDIS}$ , 2.6 V minimum, for 500 ns the SR is not enabled until the next valid cycle.

#### 8.3.4.2 VPC Pin Open

In the event of an open circuit VPC pin, the device defaults to a zero VPC input signal condition which results in disabling DRV operation.

#### 8.3.4.3 VSC Pin Open

In the event of an open circuit VSC pin, the device defaults to a zero VSC input signal condition which results in disabling DRV operation.

#### 8.3.4.4 TBLK Pin Open

In the event of an open circuit TBLK pin, the device disables DRV operation.

#### 8.3.4.5 VPC and VSC Short to Ground

Since the VPC and VSC enable thresholds must be satisfied for DRV operation, DRV is inherently disabled.

#### 8.3.4.6 TBLK Pin Short to Ground

A shorted TBLK pin results in a minimum setting for  $t_{VPC-BLK}$  blanking time.

#### 8.4 Device Functional Modes

According to VDD voltage, VSC voltage, and VPC voltage and frequency, the device can operate in different modes.

#### 8.4.1 Start-Up

During start-up when VDD is less than  $V_{VDD(on)}$  the device is disabled. When VDD exceeds the  $V_{VDD(on)}$  UVLO threshold the I<sub>DD</sub> goes to I<sub>RUN</sub> and the device begins the start sequence detailed in Start Up and UVLO.

#### 8.4.2 Normal Operation

When VDD exceeds  $V_{VDD(on)}$ , the VPC voltage exceeds  $V_{VPC-EN}$  and  $V_{VPC-TH}$ , and the VSC voltage exceeds  $V_{VSCEN}$  the DRV output is active. If the switching frequency is above the standby criteria of > 5 kHz the device is in normal operation determining the DRV time based on volt-sec control.  $I_{DD}$  will be  $I_{RUN}$ .

1. The device operates in volt-sec control based on the VPC and VSC volt-sec control ramps.

#### 8.4.3 Standby Operation

If the number of VPC pulses is less than  $n_{ENTO}$ , 64, during  $t_{ENTO}$  the device enters standby mode. DRV operation stops and most device functions are shut down.  $I_{DD}$  is  $I_{STBY}$  during standby operation. To exit standby mode the number of VPC pulses must exceed  $n_{EN}$ , 32, during  $t_{EN}$ .  $I_{DD}$  returns to  $I_{RUN}$  and the DRV output starts after the initialization time as outlined in Figure 12.

#### 8.4.4 Conditions to Stop Operation

The following conditions can disable DRV operation; I<sub>DD</sub> is I<sub>RUN</sub> during these conditions.

- 1. VPC overvoltage: When  $V_{VPC} > V_{VPCDIS}$  for >500 ns the DRV output is disabled for the cycle.

- 2. VSC undervoltage: When  $V_{VSC} < V_{VSCEN}$ , the DRV output is disabled.

- 3. VPC undervoltage: When  $V_{VPC} < V_{VPCEN}$ , the DRV output is disabled.

TEXAS INSTRUMENTS

www.ti.com.cn

#### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

The UCC24636 is a high performance controller driver for N-channel MOSFET power devices used for secondary-side synchronous rectification. The UCC24636 is designed to operate as a companion device to a primary-side controller to help achieve efficient synchronous rectification in switching power supplies. The controller features a high-speed driver and provides appropriately timed logic circuitry that seamlessly generates an efficient synchronous rectification system. With its current emulator architecture, the UCC24636 has enough versatility to be applied in DCM and TM operation. The UCC24636 SR on-time adjustability allows optimizing for PSR and SSR applications. Additional features such as pin fault protection, dynamic VPC threshold sensing, and voltage sense blanking time and make the UCC24636 a robust synchronous controller.

#### 9.2 Typical Application

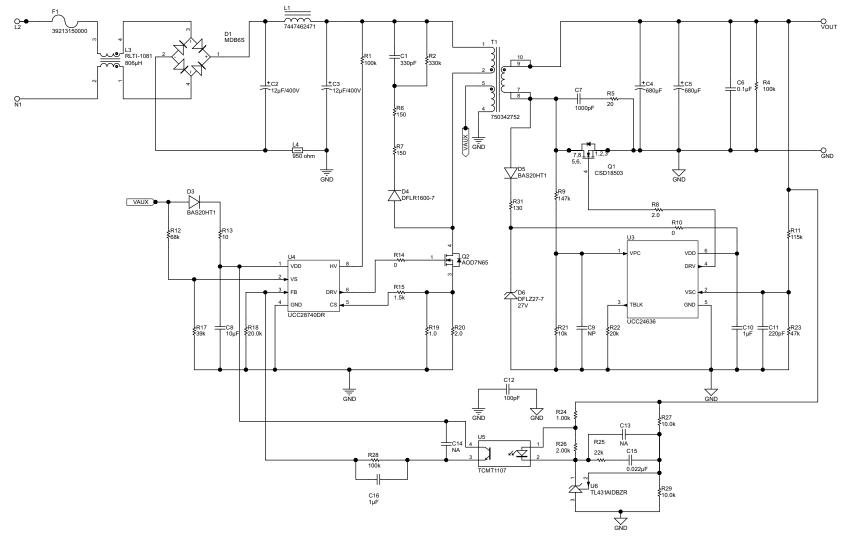

#### 9.2.1 AC-to-DC Adapter, 5 V, 15 W

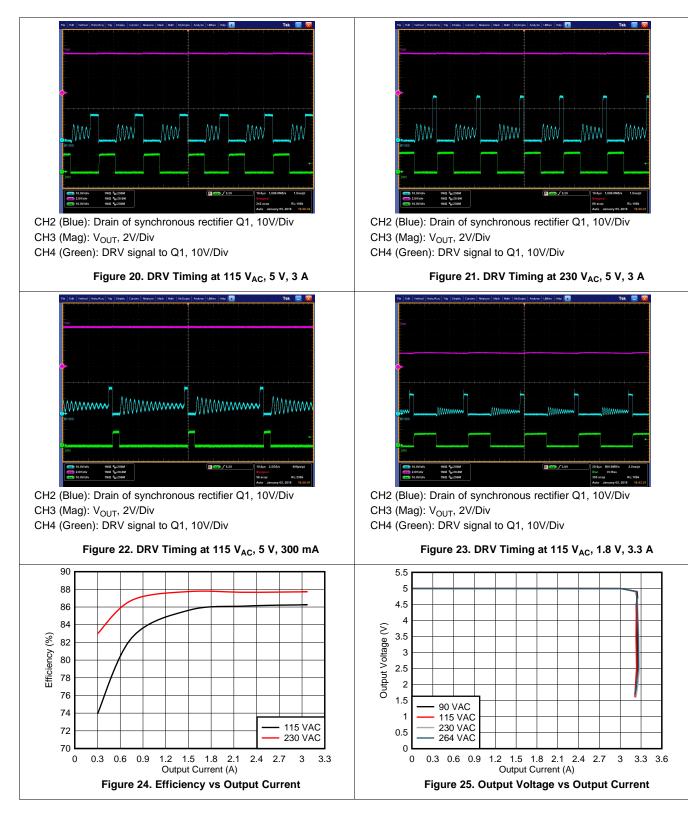

This design example describes the design of a 15-W off-line flyback converter providing 5 V at 3-A maximum load and operating from a universal AC input. The design uses the UCC28740 AC-to-DC valley-switching primary-side controller in a DCM type flyback converter and achieves over 86% full-load efficiency with the use of the secondary side UCC24636 synchronous rectifier controller.

- The design requirements are detailed in Design Requirements

- The design procedure for selecting the component circuitry for use with the UCC24636 is detailed in Calculation of Component Values.

- Test results shown in Application Waveforms And Curves highlight the unique advantages of using the UCC24636.

UCC24636 ZHCSES5A – MARCH 2016 – REVISED MARCH 2016

#### 9.2.2 Design Requirements

For this design example, use the parameters listed in Table 1.

#### Table 1. Performance Specifications AC-to-DC Charger 5 V, 15 W

|                       | PARAMETER                 | TEST CONDITIONS                                                                                              | MIN   | NOM     | MAX | UNIT |

|-----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------|-------|---------|-----|------|

| INPUT CHA             | ARACTERISTICS             |                                                                                                              |       | I       |     |      |

| V <sub>ACIN</sub>     | Input voltage             |                                                                                                              | 90    | 115/230 | 265 | VRMS |

| f <sub>LINE</sub>     | Frequency                 |                                                                                                              | 47    | 50/60   | 64  | Hz   |

| V <sub>AC(uvlo)</sub> | Brownout voltage          | $I_{OUT} = I_{OUT(nom)}$                                                                                     |       | 72      |     | VRMS |

| V <sub>AC(run)</sub>  | Brownout recovery voltage |                                                                                                              |       | 85      |     | VRMS |

| I <sub>IN</sub>       | Input current             | $V_{ACIN} = V_{ACIN(min)}, I_{OUT} = I_{OUT(nom)}$                                                           |       | 335     |     | mA   |

| OUTPUT C              | HARACTERISTICS            |                                                                                                              |       |         |     |      |

| V <sub>OUT</sub>      | Output voltage            | $V_{ACIN} = V_{ACIN(min)}$ to $V_{ACIN(max)}$ ,<br>$I_{OUT} = 0$ to $I_{OUT(nom)}$                           | 4.9   | 5.0     | 5.1 | V    |

| I <sub>OUT(nom)</sub> | Nominal output current    | $V_{ACIN} = V_{ACIN(min)}$ to $V_{ACIN(max)}$                                                                |       | 3.0     |     | А    |

| I <sub>OUT(min)</sub> | Minimum output current    | $V_{ACIN} = V_{ACIN(min)}$ to $V_{ACIN(max)}$                                                                |       | 0       |     | А    |

| ΔV <sub>OUT</sub>     | Output voltage ripple     | $V_{ACIN} = V_{ACIN(min)}$ to $V_{ACIN(max)}$ ,<br>$I_{OUT} = 0$ to $I_{OUT(nom)}$                           |       | 80      |     | mV   |

| P <sub>OUT</sub>      | Output power              | $V_{ACIN} = V_{ACIN(min)}, I_{OUT} = I_{OUT(nom)}$                                                           |       | 15      |     | W    |

| SYSTEM C              | HARACTERISTICS            |                                                                                                              |       |         |     |      |

| η <sub>avg</sub>      | Average efficiency        | V <sub>ACIN</sub> = V <sub>ACIN(nom)</sub> , I <sub>OUT</sub> = 25%, 50%, 75%, 100% of I <sub>OUT(nom)</sub> | 85%   | 87%     |     |      |

| η <sub>10%</sub>      | 10% Load efficiency       | $V_{ACIN} = V_{ACIN(nom)}$ , $I_{OUT} = 10\%$ of $I_{OUT(nom)}$                                              | 73.5% | 82.5%   |     |      |

| P <sub>NL</sub>       | No load power             | $V_{ACIN} = V_{ACIN(nom)}, I_{OUT} = 0$                                                                      |       | 14      | 22  | mW   |

#### 9.2.3 Calculation of Component Values

Figure 19. UCC24636 Circuit Design

For ease of understanding, Figure 19 is a modified version of Figure 15 where the component reference designators are the same as the schematic drawing of Figure 18.

#### 9.2.3.1 VPC Input

For designs operating in constant current (CC) with low  $V_{OUT}$ , there are two cases to examine. At maximum power,  $V_{IN(MIN)}$  will be lower but  $V_{OUT}$  is nominal. In constant current operation,  $V_{OUT}$  is the minimum but  $V_{IN(MIN)}$  will be higher. Determine R9 for both conditions, and choose the lowest value.

For minimal power dissipation, select:

R21=10kΩ

Nominal  $V_{OUT}$ , maximum power, minimum  $V_{IN}$  case

$$R9 = \frac{\left[\left(\frac{V_{IN(min)}}{N_{PS}} + V_{OUT}\right) - V_{VPC\_EN} \times 1.1\right] \times R21}{V_{VPC\_EN} \times 1.1}$$

$$V_{OUT} = 5 V$$

$$N_{PS} = 15$$

$$V_{IN(min)} = 65 V$$

$$V_{VPC\_EN} = 0.45 V$$

$$R9 = 179 \text{ k}\Omega$$

(8)

TEXAS INSTRUMENTS

www.ti.com.cn

(9)

(10)

Minimum  $V_{\mbox{\scriptsize OUT}},$  constant current operation case

$$R9 = \frac{\left[\left(\frac{V_{IN(min)CC}}{N_{PS}} + V_{OUT(min)}\right) - V_{VPC\_EN} \times 1.1\right] \times R21}{V_{VPC\_EN} \times 1.1}$$

$V_{OUT(min)} = 1.8 V$

V<sub>IN(min)CC</sub>=89V

R9 = 146 kΩ

Select standard value based on 146  $k\Omega$  result.

#### With R9 = 147 $k\Omega$ :

$$V_{VPC(max)} = \frac{(\frac{V_{IN(max)}}{NPS} + V_{OUT(max)}) \times R21}{R9 + R21}$$

$$V_{VPC(max)} = 1.95 V$$

Therefore,  $V_{\text{VPC}}$  is within the recommended range of 0.45 V to 2.2 V.

#### 9.2.3.2 VSC Input

The value of R23 is recommended to be with the range of 25 k $\Omega$  to 50 k $\Omega$ .

There is a 10% margin included for the initial value calculation of R11 to provide timing margin during initial operation verification.

$$R23 = 47 \ k\Omega$$

$$R11 = \left[ \left( \frac{\frac{R9 + R21}{R9}}{Ratio_{VPC_VSC} \times 1.1} \right) - 1 \right] \times R23$$

$$R11 = 115 k\Omega$$

With **R11 = 115 k** $\Omega$ , the operating range of the VSC pin is:

$$V_{VSC(min)} = \left[ \left( \frac{R23}{R11 + R23} \right) \right] \times V_{OUT(min)}$$

$$V_{VSC(min)} = 0.52 V$$

$$V_{VSC(max)} = \left[ \left( \frac{R23}{R11 + R23} \right) \right] \times V_{OUT(max)}$$

$$V_{VSC(max)} = 1.74 V$$

(13)

Therefore,  $V_{VSC}$  is within the recommended range of 0.3 V to 2.2 V.

The UCC24636 SR timing can be optimized (SR on time increased) by increasing the R115 value after initial operation confirmation. The Ratio<sub>VPC\_VSC</sub> parameter has a positive tolerance of 5.3%. Using 1% divider resistors for VPC and VSC should allow reducing the 10% initial SR timing margin.

#### 9.2.3.3 TBLK Input

The blanking time is set with resistor R22.

Select the blanking time to meet the following criteria based on 660-ns minimum primary on-time at high line.

$t_{VPC-BLK} = (t_{PRI} \times 0.85) - 120 \text{ ns}$

$$R22 = \frac{t_{VPC-BLK} - 100 \text{ ns}}{18 \text{ pF}}$$

(14)

A value of R22 = 20 k $\Omega$  results in a blanking time of approximately 460 ns.

(11)

TEXAS INSTRUMENTS

www.ti.com.cn

#### 9.2.4 Application Waveforms And Curves

#### 9.3 Do's and Don'ts

- Do operate the device within the recommended operating maximum parameters. Consider output overvoltage conditions when determining stress.

- Do consider the guideline for setting the blanking time resistor value illustrated in Figure 16.

- Do not use the UCC24636 in CCM flyback converter designs. For CCM designs, use the UCC24630 with the CCM dead time control function.

- Do not use the UCC24636 in LLC converters as they can operate in CCM.

- Do not add capacitance to the TBLK pin.

- Do not add significant external capacitance to the VPC pin as there will be increased delay of the signal. If filtering is necessary a recommended maximum capacitance is 15 pF with a lower resistor divider network value of 10 kΩ.

#### **10 Power Supply Recommendations**

The VDD operating range allows direct connection to converter outputs from 5 V to 24 V. Since the driver and control share the same VDD and ground, it is recommended to place a good quality ceramic capacitor as close as possible to VDD and GND pins. To reduce VDD noise and eliminate high-frequency ripple current injected from the converter output, it is recommended to place a small resistance of 2.2  $\Omega$  to 10  $\Omega$  between the converter output and VDD. The device can tolerate VDD rise times from 100 µs to very long rise times typical of constant current chargers. The start-up sequence will always be as shown in Figure 12. VDD can be connected to an external bias to extend the device's operating range to be compatible with converter output voltages below 3.5 V or above 24 V.

UCC24636

ZHCSES5A - MARCH 2016 - REVISED MARCH 2016

#### 11 Layout

#### 11.1 Layout Guidelines

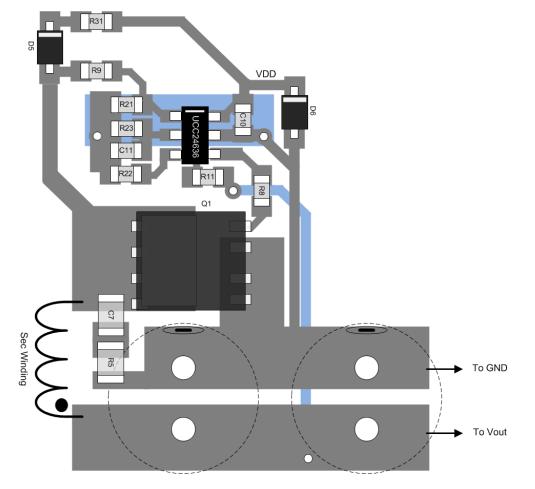

In general, try to keep all high current loops as short as possible. Keep all high current/high frequency traces away from other traces in the design. If necessary, high-frequency/high-current traces should be perpendicular to signal traces, not parallel to them. Shielding signal traces with ground traces can help reduce noise pick up. Always consider appropriate clearances between the high-voltage connections and any low-voltage nets.

#### 11.1.1 VDD Pin

The VDD pin must be decoupled to GND with good quality, low ESR, low ESL ceramic bypass capacitors with short traces to the VDD and GND pins. To eliminate high-frequency ripple current in the SR control circuit, it is recommended to place a small value resistance of 2.2  $\Omega$  to 10  $\Omega$  between VDD and the converter output voltage.

#### 11.1.2 VPC Pin

The trace between the resistor divider and the VPC pin should be as short as possible to reduce/eliminate possible noise coupling. The lower resistor of the resistor divider network connected to the VPC pin should be returned to GND with short traces. Avoid adding any significant external capacitance to the VPC pin so that there is no delay of signal. If filtering is necessary a recommended maximum capacitance is 15 pF with a lower resistor divider network value of 10 k $\Omega$ . Avoid high dV/dt traces close to the VPC pin and connection trace such as the SR MOSFET drain and DRV output.

#### 11.1.3 VSC Pin

The trace between the resistor divider and the VSC pin should be as short as possible to reduce/eliminate possible noise coupling. The lower resistor of the resistor divider network connected to the VSC pin should be returned to GND with short traces. External capacitance can be added to the VSC pin for noise filtering. The maximum capacitance consideration is a time constant of the capacitor and the resistor divider resistance that is less than 1/4 the minimum rise time of the converter output during startup. Avoid high dV/dt traces close to the VSC pin and connection trace such as the SR MOSFET drain and DRV output.

#### 11.1.4 GND Pin

The GND pin is the power and signal ground connection for the controller. The effectiveness of the filter capacitors on the signal pins depends upon the integrity of the ground return. Place all decoupling capacitors as close as possible to the device pins with short traces. The device ground and power ground should meet at the output bulk capacitor's return. Try to ensure that high frequency/high current from the power stage does not go through the signal ground.

#### 11.1.5 TBLK Pin

The programming resistor is placed on TBLK to GND, with short traces. The value may have to be adjusted based on the time delay required. Avoid high dV/dt traces close to the TBLK pin and connection trace such as the SR MOSFET drain and DRV output.

#### 11.1.6 DRV Pin

The track connected to DRV carries high dv/dt signals. Minimize noise pickup by routing the trace to this pin as far away as possible from tracks connected to the device signal inputs, VPC, VSC, and TBLK.

## 11.2 Layout Example

INSTRUMENTS

www.ti.com.cn

## 12 器件和文档支持

12.1 器件支持

#### 12.1.1 器件命名规则

#### 12.1.1.1 术语定义 (用于设计示例)

- V<sub>IN(min)</sub> = 65V: 最高功率时转换器一次侧大容量电容的最低电压

- V<sub>IN(min)CC</sub> = 89V: CC 工作模式下 V<sub>OUT(min)</sub> 时转换器一次侧大容量电容的最低电压

- V<sub>IN(max)</sub> = 370V:转换器一次侧大容量电容的最高电压

- V<sub>OUT(min)</sub> = 1.8V: UCC24636 的最低转换器输出工作电压

- V<sub>OUT(max)</sub> = 6V: UCC24636 的最高转换器输出工作电压

- V<sub>VPC EN</sub> = 0.45V: 同步整流器使能电压

- V<sub>VPC(max)</sub> = 2.2V: VPC 的最高线性工作电压

- N<sub>PS</sub> = 15: 变压器一次侧绕组与二次侧绕组匝数比

- Ratio<sub>VPC VSC</sub> = 4.15: 电流模拟器增益 K<sub>VPC</sub>/K<sub>VSC</sub>

- t<sub>VPC BLK</sub>:保证同步整流器正常工作的最少 VPC 脉冲

## 12.2 文档支持

#### 12.2.1 相关文档

相关文档请参见以下部分:

- 《使用 UCC24636EVM 二次侧同步整流器控制器二极管替代产品演示板》(文献编号: SLUUBE7)

- 《UCC24636 设计计算器》(文献编号: SLUC604)

- 《UCC24630 具有超低待机电流的同步整流控制器》(文献编号: SLUSC82)

- 《UCC28740 具有光电耦合器反馈的恒压、恒流反激控制器(文献编号: SLUSBF3)

#### 12.3 商标

#### 12.4 静电放电警告

▲ 这些装置包含有限的内置 ESD 保护。存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损 伤。

#### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

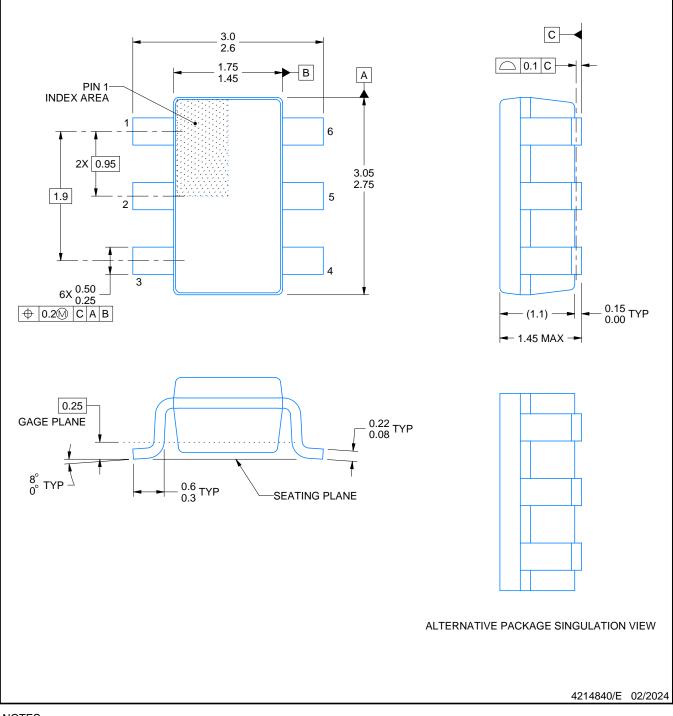

## 13 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。这些信息是针对指定器件可提供的最新数据。这些数据会在无通知且不对 本文档进行修订的情况下发生改变。欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| UCC24636DBVR     | ACTIVE        | SOT-23       | DBV                | 6    | 3000           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | U636                    | Samples |

| UCC24636DBVT     | ACTIVE        | SOT-23       | DBV                | 6    | 250            | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | U636                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

# PACKAGE OPTION ADDENDUM

10-Dec-2020

# **DBV0006A**

# **PACKAGE OUTLINE**

# SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.25 per side.

- 4. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation.

- 5. Refernce JEDEC MO-178.

# **DBV0006A**

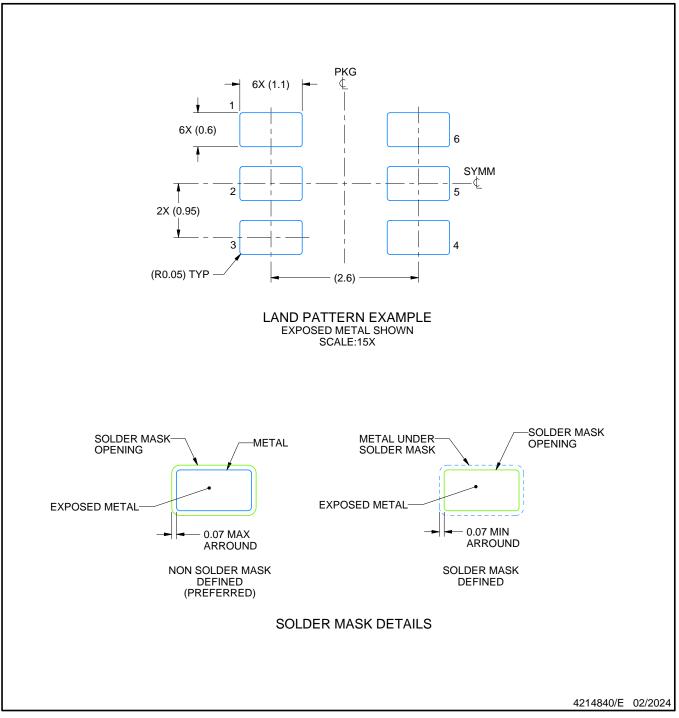

# **EXAMPLE BOARD LAYOUT**

## SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

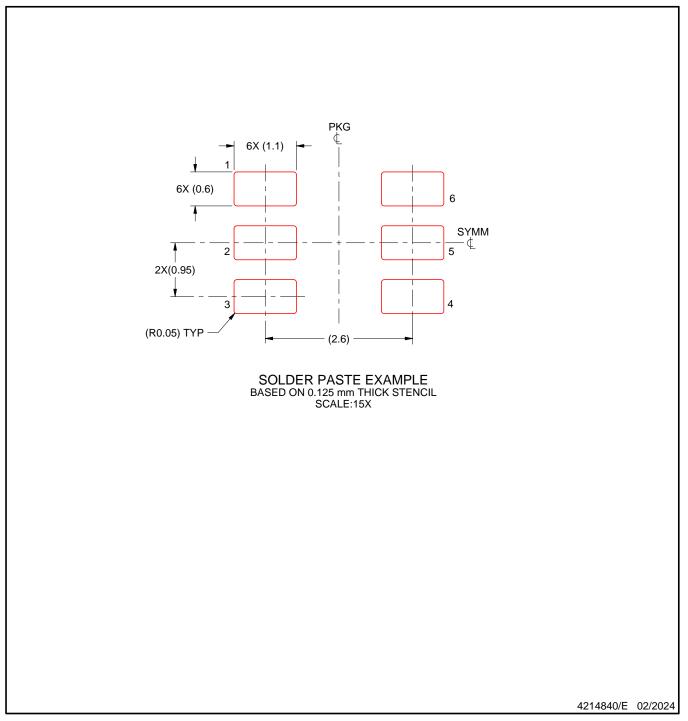

# **DBV0006A**

# **EXAMPLE STENCIL DESIGN**

# SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司