UC1843A-SP

ZHCSFS3A - DECEMBER 2016-REVISED FEBRUARY 2019

# UC1843A-SP QML V 类 耐辐射电流模式 PWM 控制器

# 1 特性

- 符合 QML V 类 (QMLV) 标准, SMD 5962-86704

- 5962P8670409Vxx:

- 抗辐射加固保障 (RHA) 能力高达 30-krad(Si) 总电离剂量 (TID)

- 通过了 45krad/LDR (10mrad/s) 测试条件(符合 MIL-STD-883 测试方法 1019.9 的 3.13.3.b 小节定义的 1.5 倍过量测试)下的功能性测试且在规定的后辐射参数限值范围内

- 展现出低剂量率灵敏度的同时在 30krad 总剂量水平下仍保持在 MIL-STD-883、TM1019 所允许的预辐射电气限制范围内

- 经过优化适用于离线和 DC-DC 转换器

- 低启动电流 (< 0.5mA)

- 修整的振荡器放电电流

- 自动前馈补偿

- 逐脉冲电流限制

- 增强型负载响应特性

- 带滞后的欠压闭锁 (UVLO) 保护

- 双脉冲抑制

- 高电流推挽式输出

- 内部调整的带隙参考

- 500kHz 工作频率

- 低 Ro 误差放大器

### 2 应用

- DC-DC 转换器

- 支持多种拓扑结构:

- 反激、正激、降压、升压

- 推挽、半桥、全桥(采用外部接口电路时)

- 支持军用温度范围(-55°C至 125°C)

# 3 说明

UC1843A-SP 控制 IC是与 UC184x 系列引脚兼容的抗辐射加固版。 该器件提供了控制电流模式开关电源所必需的特性,并改进了多种 功能。额定启动电流低于0.5mA,振荡器放电电流调整为8.3mA。UVLO 期间,输出级在低于1.2V 的电压下至少具有10mA的灌电流能力(V<sub>CC</sub>高于5V)。

器件比较表显示了该系列各成员器件间的不同之处。要 订购辐射改进型版本(如已提供),请参考相应的产品 数据表。

#### 器件信息(1)

| 器件型号       | 封装        | 封装尺寸 (标称值)      |  |

|------------|-----------|-----------------|--|

|            | CDIP (8)  | 6.67mm x 9.60mm |  |

| UC1843A-SP | LCCC (20) | 8.89mm x 8.89mm |  |

|            | CFP (10)  | 6.48mm x 7.02mm |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

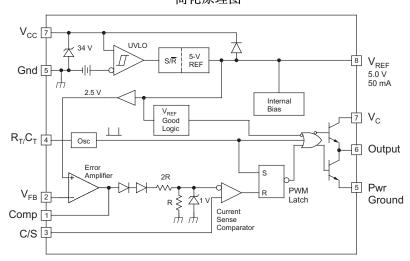

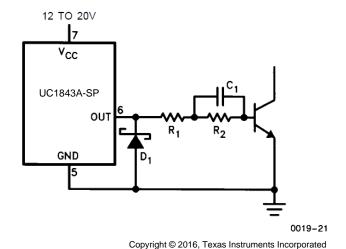

# 简化原理图

Copyright © 2016, Texas Instruments Incorporated

#### 目录 Device Functional Modes...... 12 2 Application and Implementation ...... 13 4 修订历史记录 ...... 2 5 Device Comparison Table...... 3 10 Power Supply Recommendations ...... 21 Pin Configuration and Functions ...... 3 Specifications......4 Absolute Maximum Ratings ...... 4 12 器件和文档支持.......24 Recommended Operating Conditions ...... 4 7.3 7.4 Thermal Information ...... 4 社区资源.......24 Electrical Characteristics......5 商标.......24 Detailed Description ...... 7 机械、封装和可订购信息......24 Functional Block Diagram ...... 7

# 4 修订历史记录

| C | hanges from Original (December 2016) to Revision A Page |    |  |  |  |

|---|---------------------------------------------------------|----|--|--|--|

| • | Changed the Pin Configuration images                    | 3  |  |  |  |

| • | Changed CT (pF) To: CT (μF) in Equation 1               | 15 |  |  |  |

# 5 Device Comparison Table

| PART NO. | UVLO ON | UVLO OFF | MAXIMUM DUTY CYCLE |

|----------|---------|----------|--------------------|

| UC1842A  | 16 V    | 10 V     | <100%              |

| UC1843A  | 8.5 V   | 7.9 V    | <100%              |

| UC1844A  | 16 V    | 10 V     | <50%               |

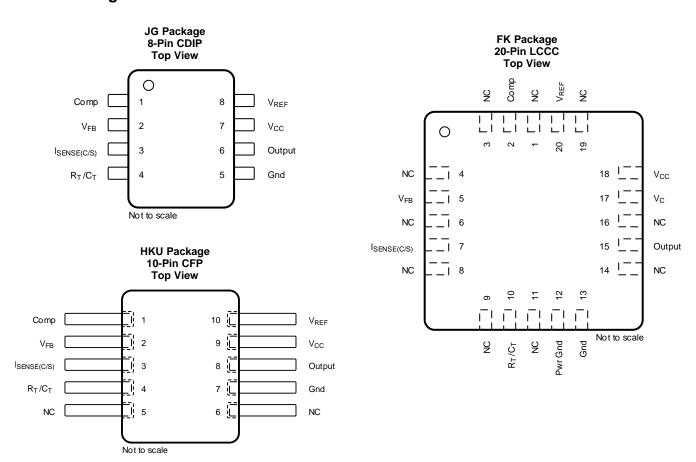

# 6 Pin Configuration and Functions

# **Pin Functions**

|                                | FIII FUICUOIIS |                                     |      |     |                                            |  |  |

|--------------------------------|----------------|-------------------------------------|------|-----|--------------------------------------------|--|--|

|                                | PIN            |                                     |      |     | DECODIDEION                                |  |  |

| NAME                           | CDIP           | LCCC                                | CFP  | I/O | DESCRIPTION                                |  |  |

| Comp                           | 1              | 2                                   | 1    | I   | Error amplifier output.                    |  |  |

| $V_{FB}$                       | 2              | 5                                   | 2    | I   | Voltage feedback input to error amplifier. |  |  |

| I <sub>SENSE(C/S)</sub>        | 3              | 7                                   | 3    | I   | Current sense comparator input pin.        |  |  |

| R <sub>T</sub> /C <sub>T</sub> | 4              | 10                                  | 4    | I   | RC time constant input to oscillator.      |  |  |

| NC                             | _              | 1, 3, 4, 6, 8, 9,<br>11, 14, 16, 19 | 5, 6 | _   | No connect.                                |  |  |

| Pwr Gnd                        | _              | 12                                  | _    | _   | Output section ground.                     |  |  |

| Gnd                            | 5              | 13                                  | 7    | _   | Ground.                                    |  |  |

| Output                         | 6              | 15                                  | 8    | 0   | Regulated output.                          |  |  |

| V <sub>C</sub>                 | _              | 17                                  | _    | _   | Output section supply voltage.             |  |  |

| V <sub>CC</sub>                | 7              | 18                                  | 9    | _   | Unregulated supply voltage.                |  |  |

| $V_{REF}$                      | 8              | 20                                  | 10   | 0   | 5-V internally generated reference.        |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings (1)(2)

over operating free-air temperature (unless otherwise noted)

|                  |                                                       | MIN    | MAX     | UNIT |

|------------------|-------------------------------------------------------|--------|---------|------|

| $V_{CC}$         | Supply voltage, low-impedance source                  |        | 30      | V    |

| VI               | Input voltage (V <sub>FB</sub> , I <sub>SENSE</sub> ) | -0.3   | 6.3     | V    |

|                  | Supply current                                        | Self I | imiting |      |

| Io               | Output current                                        |        | ±1      | Α    |

|                  | Error amplifier output sink current                   |        | 10      | mA   |

|                  | Output energy (capacitive load)                       |        | 5       | μJ   |

| $P_{D}$          | Power dissipation (T <sub>A</sub> = 25°C)             |        | 1       | W    |

| T <sub>stg</sub> | Storage temperature                                   | -65    | 150     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|             |                         |                                                        | VALUE | UNIT |

|-------------|-------------------------|--------------------------------------------------------|-------|------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±4000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range ( $T_A = T_J = -55^{\circ}\text{C}$  to 125°C), unless otherwise noted

|          |                                                         | MIN | MAX | UNIT |

|----------|---------------------------------------------------------|-----|-----|------|

| $V_{CC}$ | Supply voltage                                          | 12  | 25  | V    |

|          | Sink/source output current (continuous or time average) | 0   | 200 | mA   |

|          | Reference load current                                  | 0   | 20  | mA   |

### 7.4 Thermal Information

|                      |                                              |           | UC1843A-SP |           |      |  |

|----------------------|----------------------------------------------|-----------|------------|-----------|------|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | JG (CDIP) | FK (LCCC)  | HKU (CFP) | UNIT |  |

|                      |                                              | 8 PINS    | 20 PINS    | 10 PINS   |      |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 103       | _          | 51.9      | °C/W |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 9.6       | 9.0        | 6.6       | °C/W |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 69.2      | _          | 31.5      | °C/W |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 13.9      | _          | 5.42      | °C/W |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 73        | _          | 31        | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> All voltages are with respect to ground. Currents are positive in, negative out of the specified terminal.

#### 7.5 Electrical Characteristics

$V_{CC} = 15 \text{ V}^{(1)}, R_T = 10 \text{ k}\Omega, C_T = 3.3 \text{ nF}, T_A = T_J = -55^{\circ}\text{C}$  to 125°C (unless otherwise noted)

| PARAMETER                    | TEST C                                                    | CONDIT                                               | TIONS                       | MIN  | TYP  | MAX  | UNIT  |

|------------------------------|-----------------------------------------------------------|------------------------------------------------------|-----------------------------|------|------|------|-------|

| REFERENCE                    | I                                                         |                                                      |                             |      |      |      |       |

| Output voltage               | $T_J = 25^{\circ}C, I_O = 1 \text{ mA}$                   | $T_J = 25^{\circ}C, I_O = 1 \text{ mA}$              |                             |      | 5    | 5.06 | V     |

| Line regulation              | V <sub>IN</sub> = 12 to 25 V                              |                                                      |                             |      | 6    | 20   | mV    |

| Load regulation              | I <sub>O</sub> = 1 to 20 mA                               |                                                      |                             |      | 6    | 25   | mV    |

| Temperature stability (2)(3) |                                                           |                                                      |                             |      | 0.2  | 0.4  | mV/°C |

| Total output variation (2)   | Over line, load, and ter                                  | mperatu                                              | ıre                         | 4.9  |      | 5.1  | V     |

| Output noise voltage         | 10 Hz ≤ $f$ ≤ 10 kHz, T <sub>J</sub>                      | = 25°C = ر                                           |                             |      | 50   |      | μV    |

| Long-term stability          | 1000 hours, T <sub>A</sub> = 125°0                        | C <sup>(2)</sup>                                     |                             |      | 5    | 25   | mV    |

| Short-circuit output current |                                                           |                                                      |                             | -30  | -100 | -180 | mA    |

| OSCILLATOR                   |                                                           |                                                      |                             |      |      |      |       |

| Initial accuracy             | $T_J = 25^{\circ}C^{(4)}$                                 |                                                      |                             | 47   | 52   | 57   | kHz   |

| Voltage stability            | V <sub>CC</sub> = 12 to 25 V                              |                                                      |                             |      | 0.2% | 1%   |       |

| Temperature stability        | $T_J = -55^{\circ}\text{C to } 125^{\circ}\text{C}^{(2)}$ | )                                                    |                             |      | 5%   |      |       |

| Amplitude peak-to-peak       | V pin 4 <sup>(2)</sup>                                    |                                                      |                             |      | 1.7  |      | V     |

| Discharge comment            | V nin 4 0 V(5)                                            |                                                      | T <sub>J</sub> = 25°C       | 7.8  | 8.3  | 8.8  | mA    |

| Discharge current            | $V pin 4 = 2 V^{(5)}$                                     |                                                      | T <sub>J</sub> = Full range | 7.5  |      | 8.8  | mA    |

| ERROR AMPLIFIER              |                                                           |                                                      |                             |      |      |      |       |

| Input voltage                | V <sub>Comp</sub> = 2.5 V                                 |                                                      |                             | 2.45 | 2.50 | 2.55 | V     |

| Input bias current           |                                                           |                                                      |                             |      | -0.3 | -1   | μА    |

| Open-loop voltage gain       | $V_O = 2 \text{ to } 4 \text{ V}$                         |                                                      |                             | 65   | 90   |      | dB    |

| Unity-gain bandwidth         | $T_J = 25^{\circ}C^{(2)}$                                 |                                                      |                             | 0.7  | 1    |      | MHz   |

| PSRR                         | $V_{CC} = 12 \text{ to } 25 \text{ V}$                    |                                                      |                             | 60   | 70   |      | dB    |

| Output sink current          | V <sub>FB</sub> = 2.7 V, V <sub>Comp</sub> = 1            | .1 V                                                 |                             | 2    | 6    |      | mA    |

| Output source current        | $V_{FB} = 2.3 \text{ V}, V_{Comp} = 5$                    | 5 V                                                  |                             | -0.5 | -0.8 |      | mA    |

| High-level output voltage    | $V_{FB} = 2.3 \text{ V}, R_L = 15 \text{ kg}$             | Ω to gro                                             | ound                        | 5    | 6    |      | V     |

| Low-level output voltage     | $V_{FB} = 2.7 \text{ V}, R_L = 15 \text{ kg}$             | $V_{FB}$ = 2.7 V, $R_L$ = 15 k $\Omega$ to $V_{REF}$ |                             |      | 0.7  | 1.1  | V     |

| CURRENT SENSE                | <del></del>                                               |                                                      |                             |      |      |      |       |

| Gain <sup>(6)(7)</sup>       |                                                           |                                                      |                             | 2.85 | 3    | 3.15 | V/V   |

| Maximum input signal         | V <sub>Comp</sub> = 5 V <sup>(6)</sup>                    |                                                      |                             | 0.9  | 1    | 1.1  | V     |

| PSRR                         | V <sub>CC</sub> = 12 to 25 V <sup>(6)</sup>               |                                                      |                             |      | 70   |      | dB    |

| Input bias current           |                                                           |                                                      |                             |      | -2   | -10  | μΑ    |

| Delay to output              | $V_{ISENSE} = 0$ to 2 $V^{(2)}$                           |                                                      |                             |      | 150  | 300  | ns    |

- (1) Adjust  $V_{CC}$  above the start threshold before setting at 15 V.

- (2) Parameters ensured by design and/or characterization, if not production tested.

- (3) Temperature stability, sometimes referred to as average temperature coefficient, is described by the equation:

Temperature Stability = V<sub>REF</sub> (max) V<sub>REF</sub> (min) / T<sub>J</sub> (max) T<sub>J</sub> (min). V<sub>REF</sub> (max) and V<sub>REF</sub> (min) are the maximum and minimum reference voltage measured over the appropriate temperature range. Note that the extremes in voltage do not necessarily occur at the extremes in temperature.

- (4) Output frequency equals oscillator frequency for the UC1842A-SP and UC1843A-SP.

- (5) This parameter is measured with  $R_T = 10 \text{ k}\Omega$  to  $V_{REF}$ . This contributes approximately 300  $\mu$ A of current to the measurement. The total current flowing into the  $R_T$  or  $C_T$  pin will be approximately 300  $\mu$ A higher than the measured value.

- (6) Parameter measured at trip point of latch with  $V_{FB} = 0 \text{ V}$ .

- (7) Gain defined as:  $G = \Delta V_{Comp} / \Delta V_{ISENSE}$ ;  $V_{ISENSE} = 0$  to 0.8 V.

# **Electrical Characteristics (continued)**

$V_{CC}$  = 15  $V^{(1)}$ ,  $R_T$  = 10 k $\Omega$ ,  $C_T$  = 3.3 nF,  $T_A$  =  $T_J$  = -55°C to 125°C (unless otherwise noted)

| PARAMETER                              | TEST CONDITIONS                                  | MIN | TYP  | MAX  | UNIT |

|----------------------------------------|--------------------------------------------------|-----|------|------|------|

| OUTPUT                                 |                                                  | ·   |      |      |      |

| Output low-level voltage               | I <sub>SINK</sub> = 20 mA                        |     | 0.1  | 0.4  | V    |

| Output low-level voltage               | $I_{SINK} = 200 \text{ mA}$                      |     | 1.5  | 2.2  | V    |

| Output high lovel veltage              | I <sub>SOURCE</sub> = -20 mA                     | 13  | 13.5 |      | V    |

| Output high-level voltage              | I <sub>SOURCE</sub> = -200 mA                    | 12  | 13.5 |      | v    |

| Rise time                              | $C_L = 1 \text{ nF}, T_J = 25^{\circ}C^{(2)}$    |     | 50   | 150  | ns   |

| Fall time                              | $C_L = 1 \text{ nF}, T_J = 25^{\circ}C^{(2)}$    |     | 50   | 150  | ns   |

| UVLO saturation                        | $V_{CC} = 5 \text{ V}, I_{SINK} = 10 \text{ mA}$ |     | 0.7  | 1.2  | V    |

| UNDERVOLTAGE LOCKOUT                   |                                                  |     |      |      |      |

| Start threshold                        |                                                  | 7.8 | 8.4  | 9    | V    |

| Minimum operation voltage after turnon |                                                  | 7   | 7.6  | 8.2  | V    |

| PWM                                    |                                                  |     |      |      |      |

| Maximum duty cycle                     |                                                  | 94% | 96%  | 100% |      |

| Minimum duty cycle                     |                                                  |     |      | 0%   |      |

| TOTAL STANDBY CURRENT                  |                                                  | ·   |      |      |      |

| Start-up current                       |                                                  |     | 0.3  | 0.5  | mA   |

| Operating supply current               | V <sub>FB</sub> = V <sub>ISENSE</sub> = 0 V      |     | 11   | 17   | mA   |

| V <sub>CC</sub> Zener voltage          | $I_{CC} = 25 \text{ mA}$                         | 30  | 34   |      | V    |

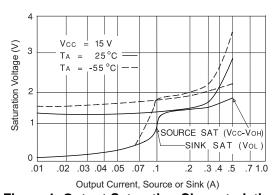

# 7.6 Typical Characteristics

**Figure 1. Output Saturation Characteristics**

# 8 Detailed Description

#### 8.1 Overview

The UC1843A-SP control IC is a pin-for-pin compatible improved version of the UC184x family. Providing the necessary characteristics to control current-mode switched-mode power supplies, this device has improved features. Start-up current is specified to be less than 0.5 mA and oscillator discharge is trimmed to 8.3 mA. During UVLO, the output stage can sink at least 10 mA at less than 1.2 V for V<sub>CC</sub> over 5 V.

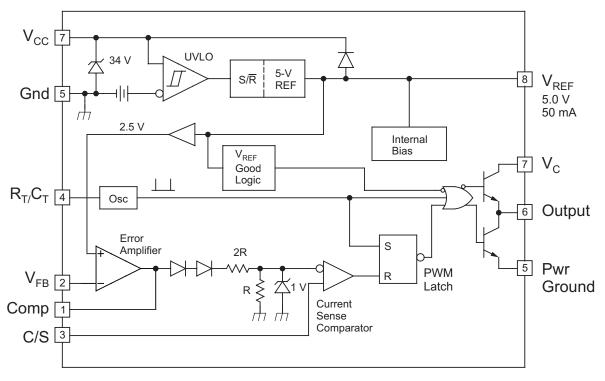

# 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

# 8.3 Feature Description

UC1843A-SP is a current mode controller, used to support various topologies such as forward, flyback, buck, boost and using an external interface circuit will also support half-bridge, full-bridge, and push-pull configurations.

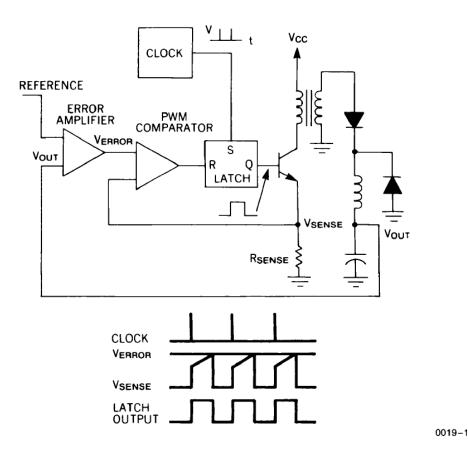

Figure 2 shows the two-loop current-mode control system in a typical buck regulator application. A clock signal initiates power pulses at a fixed frequency. The termination of each pulse occurs when an analog of the inductor current reaches a threshold established by the error signal. In this way, the error signal actually controls peak inductor current. This contrasts with conventional schemes in which the error signal directly controls pulse width without regard to inductor current.

Several performance advantages result from the use of current-mode control. First, an input voltage feed-forward characteristic is achieved; that is, the control circuit instantaneously corrects for input voltage variations without using up any of the error amplifier's dynamic range. Therefore, line regulation is excellent and the error amplifier can be dedicated to correcting for load variations exclusively.

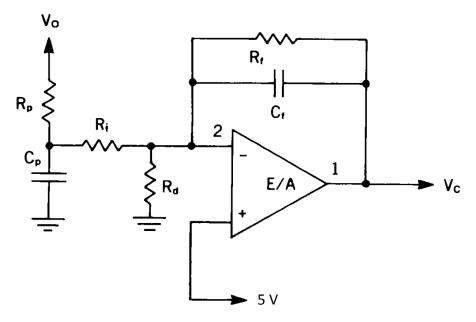

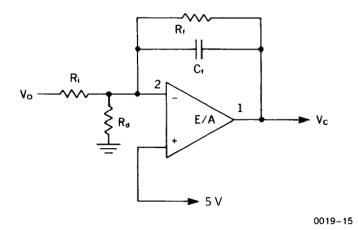

Figure 2. Two-Loop Current-Mode Control System

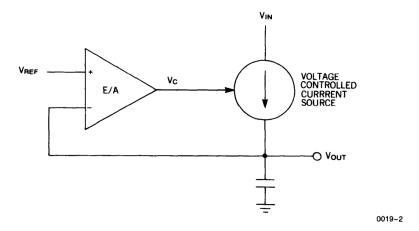

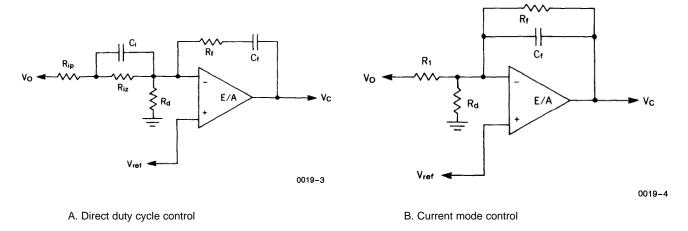

For converters in which inductor current is continuous, controlling peak current is nearly equivalent to controlling average current. Therefore, when such converters employ current-mode control, the inductor can be treated as an error-voltage-controlled-current-source for the purposes of small-signal analysis (see Figure 3). The two-pole control-to-output frequency response of these converters is reduced to a single-pole (filter capacitor in parallel with load) response. One result is that the error amplifier compensation can be designed to yield a stable closed-loop converter response with greater gain bandwidth than would be possible with pulse-width control, giving the supply improved small-signal dynamic response to changing loads. A second result is that the error amplifier compensation circuit becomes simpler, as shown in Figure 4.

Capacitor Ci and resistor Ri, in Figure 4(A), add a low-frequency zero, which cancels one of the two control-to-output poles of non-current-mode converters. For large signal load changes, in which converter response is limited by inductor slew rate, the error amplifier saturates while the inductor is catching up with the load. During this time, Ci charges to an abnormal level. When the inductor current reaches its required level, the voltage on Ci causes a corresponding error in supply output voltage. The recovery time is  $R_{iz}C_{i}$ , which may be long. However, the compensation network of Figure 4(B) can be used where current-mode control has eliminated the inductor pole. Large-signal dynamic response is then greatly improved due to the absence of Ci.

Current limiting is greatly simplified with current-mode control. Pulse-by-pulse limiting is, of course, inherent in the control scheme. Furthermore, an upper limit on the peak current can be established by simply clamping the error voltage. Accurate current limiting allows optimization of magnetic and power semiconductor elements while ensuring reliable supply operation.

Finally, current-mode controlled power stages can be operated in parallel with equal current sharing. This opens the possibility of a modular approach to power supply design.

Figure 3. Inductor Looks Like a Current Source to Small Signals

Figure 4. Required Error Amplifier Compensation for Continuous Inductor Current Designs

#### 8.3.1 UVLO

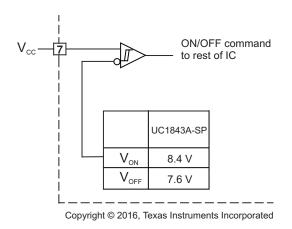

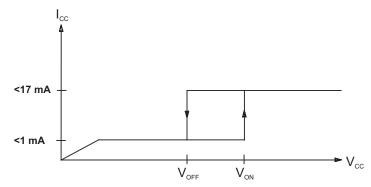

The UVLO circuit ensures that  $V_{CC}$  is adequate to make the UC1843A-SP fully operational before enabling the output stage. Figure 5 shows that the UVLO turnon and turnoff thresholds are fixed internally at 16 V and 10 V, respectively. The 6-V hysteresis prevents  $V_{CC}$  oscillations during power sequencing.

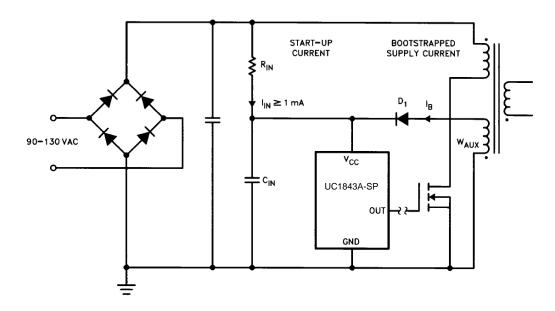

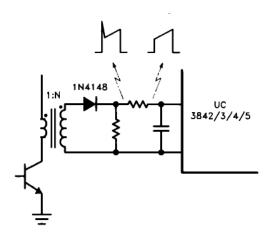

Figure 6 shows supply current requirements. Start-up current is < 1 mA for efficient bootstrapping from the rectified input of an off-line converter, as shown in Figure 7. During normal circuit operation,  $V_{CC}$  is developed from auxiliary winding, WAux, with  $D_1$  and  $C_{IN}$ . However, at start-up,  $C_{IN}$  must be charged to 16 V through  $R_{IN}$ . With a start-up current of 1 mA,  $R_{IN}$  can be as large as 100 k $\Omega$  and still charge  $C_{IN}$  when VAc = 90-V RMS (low line). Power dissipation in  $R_{IN}$  would then be less than 350 mW even under high line (VAc = 130-V RMS) conditions.

During UVLO, the output driver is in a low state. While it does not exhibit the same saturation characteristics as normal operation, it can easily sink 1 mA, enough to ensure the MOSFET is held off.

Figure 5. UVLO Turnon TurnOff Threshold

During UVLO, the output driver is biased to sink minor amounts of current.

Figure 6. Supply Current Requirements

0019-8

Copyright © 2016, Texas Instruments Incorporated

Figure 7. Providing Power to the UC1843A-SP

#### 8.3.2 Reference

As highlighted in the *Functional Block Diagram*, UC1843A-SP incorporates a 5-V internal reference regulator with ±2% set point variation over temperature.

#### 8.3.3 Totem-Pole Output

The UC1843A-SP PWM has a single totem-pole output which can be operated to  $\pm 1$ -A peak for driving MOSFET gates, and a  $\pm 200$  mA average current for bipolar power U-100A transistors. Cross conduction between the output transistors is minimal, the average added power with  $V_{IN} = 30$  V is only 80 mW at 200 kHz.

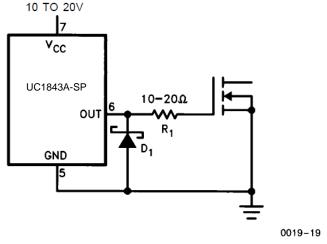

Limiting the peak current through the IC is accomplished by placing a resistor between the totem-pole output and the gate of the MOSFET. The value is determined by dividing the totem-pole collector voltage  $V_C$  by the peak current rating of the IC's totem-pole. Without this resistor, the peak current is limited only by the dV/dT rate of the totem-pole switching and the FET gate capacitance.

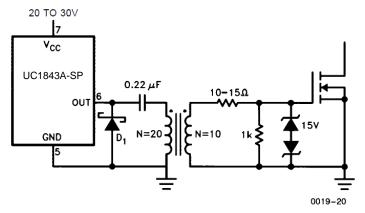

The use of a Schottky diode from the PWM output to ground prevents the output voltage from going excessively below ground, causing instabilities within the IC. To be effective, the diode selected should have a forward drop of less than 0.3 V at 200 mA. Most 1- to 3-A Schottky diodes exhibit these traits above room temperature. Placing the diode as physically close to the PWM as possible enhances circuit performance. Implementation of the complete drive scheme is shown in Figure 8 through Figure 10. Transformer-driven circuits also require the use of the Schottky diodes to prevent a similar set of circumstances from occurring on the PWM output. The ringing below ground is greatly enhanced by the transformer leakage inductance and parasitic capacitance, in addition to the magnetizing inductance and FET gate capacitance. Circuit implementation is similar to the previous example.

Figure 8 through Figure 10 show suggested circuits for driving MOSFETs and bipolar transistors with the UC1843A-SP output. The simple circuit of Figure 8 can be used when the control IC is not electrically isolated from the MOSFET turnon and turnoff to  $\pm 1$  A. It also provides damping for a parasitic tank circuit formed by the FET input capacitance and series wiring inductance. Schottky diode,  $D_1$ , prevents the output of the IC from going far below ground during turnoff.

Figure 9 shows an isolated MOSFET drive circuit which is appropriate when the drive signal must be level shifted or transmitted across an isolation boundary. Bipolar transistors can be driven efficiently with the circuit of Figure 10. Resistors  $R_1$  and  $R_2$  fix the on-state base current while capacitor  $C_1$  provides a negative base current pulse to remove stored charge at turnoff.

Because the UC1843A-SP series has only a single output, an interface circuit is needed to control push-pull, half-bridge, or full-bridge topologies. The UC1706 dual output driver with internal toggle flip-flop performs this function. *Typical Application* shows a typical application for these two ICs. Increased drive capability for driving numerous FETs in parallel, or other loads can be accomplished using one of the UC1705/6/7 driver ICs.

Copyright © 2016, Texas Instruments Incorporated

Figure 8. Direct MOSFET Drive

Copyright © 2016, Texas Instruments Incorporated

Figure 9. Isolated MOSFET Drive

Figure 10. Bipolar Drive With Negative turnoff Bias

## 8.4 Device Functional Modes

The UC1843A-SP uses fixed frequency, peak current mode control. An internal oscillator initiates the turn on of the driver to high-side power switch. The external power switch current is sensed through an external resistor and is compared via internal comparator. The voltage generated at the COMP pin is stepped down via internal resistors (as shown in the functional block diagram). When the sensed current reaches the stepped down COMP voltage, the high-side power switch is turned off.

# 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

UC1843A-SP can be used as a controller to design various topologies such as buck, boost, flyback, and forward. Using an external interphase circuit can also support push-pull, half-bridge and full-bridge topologies.

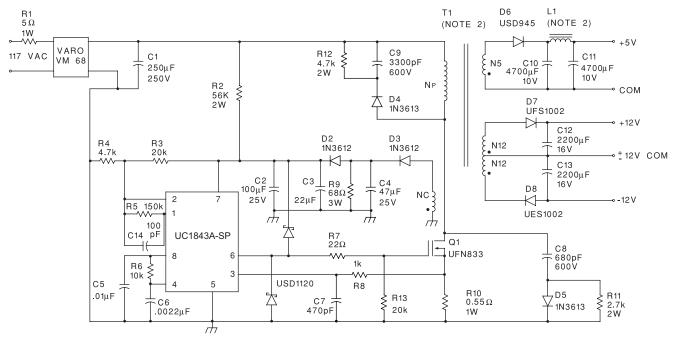

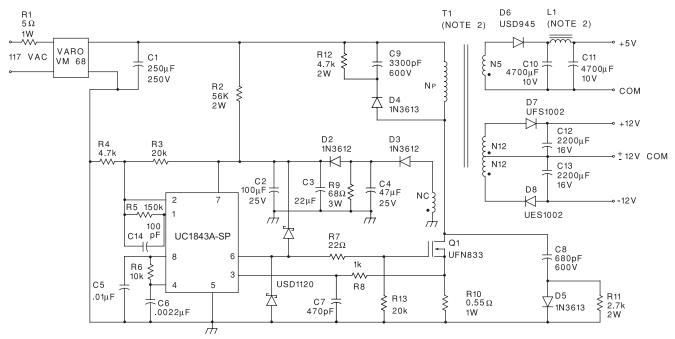

# 9.2 Typical Application

Copyright © 2016, Texas Instruments Incorporated

Figure 11. Typical Application Schematic

#### 9.2.1 Design Requirements

See Table 1 for parameter values.

Table 1. Design Parameters<sup>(1)</sup>

| DESIGN PARAMETER       | VALUE                                                           |

|------------------------|-----------------------------------------------------------------|

| Input voltage          | 95 VAC to 130 VAC                                               |

| Line isolation         | 3750 V                                                          |

| Switching frequency    | 40 kHz                                                          |

| Efficiency (full load) | 70%                                                             |

| Output voltage (A)     | +5 V, ±5%; 1-A to 4-A load; Ripple voltage: 50-mV P-P max       |

| Output voltage (B)     | +12 V, ±3%; 0.1-A to 0.3-A load; Ripple voltage: 100-mV P-P max |

| Output voltage (C)     | -12 V, ±3%; 0.1-A to 0.3-A load; Ripple voltage: 100-mV P-P max |

(1) See Figure 11 for reference.

# 9.2.2 Detailed Design Procedure

See Table 2 for component values.

Table 2. Components<sup>(1)</sup>

| COMPONENT | VALUE          |  |

|-----------|----------------|--|

| R1        | 5 Ω, 1 W       |  |

| R2        | 56 kΩ, 2 W     |  |

| R3        | 20 kΩ          |  |

| R4        | 4.7 kΩ         |  |

| R5        | 150 kΩ         |  |

| R6        | 10 kΩ          |  |

| R7        | 22 Ω           |  |

| R8        | 1 kΩ           |  |

| R9        | 68 Ω           |  |

| R10       | 0.55 Ω, 1 W    |  |

| R11       | 2.7 kΩ, 2 W    |  |

| R12       | 4.7 kΩ, 2 W    |  |

| R13       | 20 kΩ          |  |

| C1        | 250 μF, 250 V  |  |

| C2        | 100 μF, 25 V   |  |

| C3        | 22 μF          |  |

| C4        | 47 μF, 25 V    |  |

| C5        | 0.1 μF         |  |

| C6        | 0.0022 μF      |  |

| C7        | 470 pF         |  |

| C8        | 680 pF, 600 V  |  |

| C9        | 3300 pF, 600 V |  |

| C10       | 4700 μF, 10 V  |  |

| C11       | 4700 μF, 10 V  |  |

| C12       | 2200 μF, 10 V  |  |

| C13       | 2200 μF, 10 V  |  |

| C14       | 100 pF         |  |

| D2        | 1N3612         |  |

| D3        | 1N3612         |  |

| D4        | 1N3613         |  |

| D5        | 1N3613         |  |

| D6        | USD945         |  |

| D7        | UFS1002        |  |

| D8        | UES1002        |  |

| Q1        | UFN833         |  |

<sup>(1)</sup> See Figure 11 for reference.

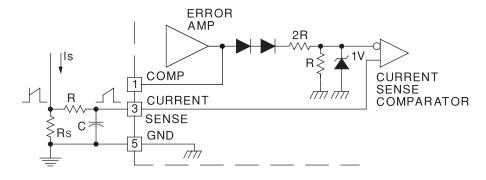

Peak Current (Is) is determined by the formula:

$$I_{SMAX}' \frac{1.0 \text{ V}}{R_S}$$

A small RC filter may be required to suppress switch transients.

Figure 12. Current-Sense Circuit

Copyright © 2016, Texas Instruments Incorporated

NOTE: A fraction of the oscillator ramp can be resistively summed with the current sense signal to provide slope compensation for converters requiring duty cycles over 50%.

Capacitor, C, forms a filter with R2 to suppress the leading edge switch spikes.

Figure 13. Slope Compensation

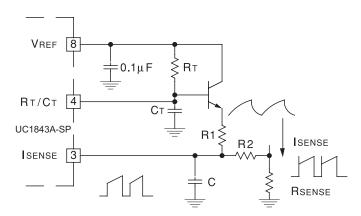

#### 9.2.2.1 Oscillator

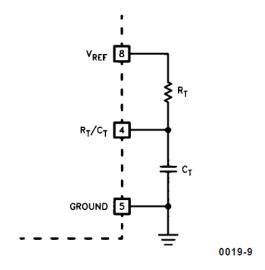

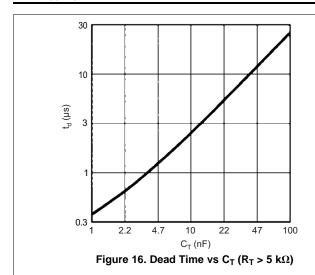

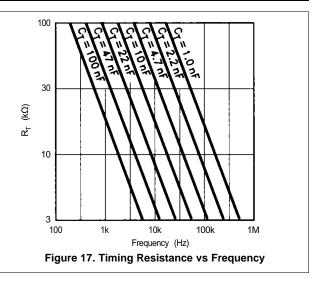

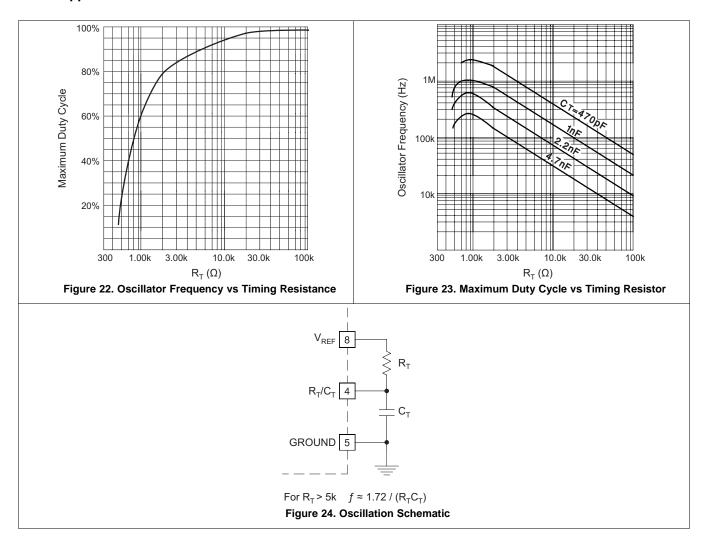

The UC1843A-SP oscillator is programmed as shown in Figure 15. Timing capacitor  $C_T$  is charged from VREF (5 V) through the timing resistor  $R_T$ , and discharged by an internal current source. The first step in selecting the oscillator components is to determine the required circuit dead time. Once obtained, Figure 16 is used to pinpoint the nearest standard value of  $C_T$  for a given dead time. Next, the appropriate  $R_T$  value is interpolated using the parameters for  $C_T$  and oscillator frequency. Figure 17 shows the  $R_T/C_T$  combinations versus oscillator frequency. The timing resistor can be calculated from the following formula.

$$f_{\rm osc} \, ({\rm kHz}) = \frac{1.72}{{\rm RT} \, ({\rm k}\Omega) \times {\rm CT} \, (\mu {\rm F})}$$

(1)

Figure 14. E/A Compensation Circuit for Continuous Boost and Flyback Topologies

The UC1843A-SP has an internal divide-by-two flip-flop driven by the oscillator for a 50% maximum duty cycle. Therefore, their oscillators must be set to run at twice the desired power supply switching frequency.

Figure 15. Oscillator Programming

# 9.2.2.2 Current Sensing and Limiting

The UC1843A-SP current sense input is configured as shown in Figure 18. Current-to-voltage conversion is done externally with ground-referenced resistor  $R_S$ . Under normal operation, the peak voltage across  $R_S$  is controlled by the E/A according to the following relation:

$$I_{P} = \frac{V_{C} - 1.4 \text{ V}}{3 \text{ R}_{S}}$$

where

$R_S$  can be connected to the power circuit directly or through a current transformer, as Figure 18 shows. While a direct connection is simpler, a transformer can reduce power dissipation in  $R_S$ , reduce errors caused by the base current, and provide level shifting to eliminate the restraint of ground-referenced sensing. The relation between  $V_C$  and peak current in the power stage is given by:

$$i_{(pk)} = N \left( \frac{V_{R_S(pk)}}{R_S} \right) = \frac{N}{3 R_S} (V_C - 1.4 V)$$

where

For purposes of small-signal analysis, the control-to-sensed-current gain is:

$$\frac{i_{(pk)}}{V_C} = \frac{N}{3 R_S} \tag{4}$$

When sensing current in series with the power transistor, as shown in Figure 18, the current waveform often has a large spike at its leading edge. This spike is due to rectifier recovery and/or inter-winding capacitance in the power transformer. If unattenuated, this transient can prematurely terminate the output pulse. As shown, a simple RC filter is usually adequate to suppress this spike. The RC time constant should be approximately equal to the current spike duration (usually a few hundred nanoseconds).

The inverting input to the UC1843A-SP current-sense comparator is internally clamped to 1 V (Figure 18). Current limiting occurs if the voltage at pin 3 reaches this threshold value, that is, the current limit is defined by:

$$i_{max} = \frac{N \times 1 \ V}{R_{S}} \tag{5}$$

0019-13

Figure 18. Transformer-Coupled Current Sensing

#### 9.2.2.3 Error Amplifier

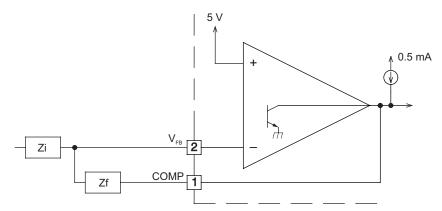

The error amplifier (E/A) configuration is shown in Figure 19. The non-inverting input is not brought out to a pin, but is internally biased to 5 V  $\pm$ 2%. The E/A output is available at pin 1 for external compensation, allowing the user to control the converter's closed-loop frequency response.

Figure 20 shows an E/A compensation circuit suitable for stabilizing any current-mode controlled topology except for flyback and boost converters operating with inductor current. The feedback components add a pole to the loop transfer function at  $f_p = \frac{1}{2} \pi R_F$ .  $R_F$  and  $C_F$  are chosen so that this pole cancels the zero of the output filter capacitor ESR in the power circuit.  $R_I$  and  $R_F$  fix the low-frequency gain. They are chosen to provide as much gain as possible while still allowing the pole formed by the output filter capacitor and load to roll off the loop gain to unity (0 dB) at  $f \approx f_{SWITCHING}$  / 4. This technique ensures converter stability while providing good dynamic response.

Figure 19. E/A Configuration

Figure 20. Compensation

The E/A output sources 0.5 mA and sinks 2 mA. A lower limit for RF is given by:

$$R_{F(MIN)} \approx \frac{V_{EA\ OUT\ (MAX)} - 2.5\ V}{0.5\ mA} = \frac{6\ V - 2.5\ V}{0.5\ mA} = 7\ k\Omega \tag{6}$$

E/A input bias current (2-µA max) flows through R<sub>I</sub>, resulting in a DC error in output voltage (VO) given by:

$$\Delta V_{O(MAX)} = (2 \mu A) R_1 \tag{7}$$

Therefore, the designer should keep the value of R<sub>I</sub>, as low as possible.

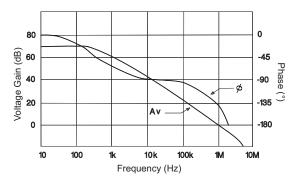

Figure 21 shows the open-loop frequency response of the UC1843A-SP E/A. The gain represents an upper limit on the gain of the compensated E/A. Phase lag increases rapidly as frequency exceeds 1 MHz due to second-order poles at about 10 MHz and above.

Continuous-inductor-current boost and flyback converters each have a right-half-plane zero in their transfer function. An additional compensation pole is needed to roll off loop gain at a frequency less than that of the RHP zero.  $R_P$  and  $C_P$  in the circuit of Figure 14 provide this pole.

Figure 21. Error Amplifier Open-Loop Frequency Response

# 9.2.3 Application Curves

# 10 Power Supply Recommendations

The devices are designed to operate from an input voltage supply range between 8 V and 40 V. This input supply should be well regulated. If the input supply is located more than a few inches from the UC1843A-SP converter, additional bulk capacitance may be required in addition to the ceramic bypass capacitors. A tantalum capacitor with a value of 47  $\mu$ F is a typical choice; however, this may vary depending upon the output power being delivered.

Copyright © 2016, Texas Instruments Incorporated

Power supply specifications:

- 1. Input voltage: 95 VAC to 130 VAC (50 Hz/60 Hz)

- 2. Line isolation: 3750 V

- 3. Switching frequency: 40 kHz

- 4. Efficiency full load: 70%

- 5. Output voltage:

- a. +5 V, ±5%; 1- to 4-A load, ripple voltage: 50 mVP-P max

- b. +12 V, ±3%; 0.1- to 0.3-A load, ripple voltage: 100 mVP-P max

- c. -12 V,  $\pm 3\%$ ; 0.1- to 0.3-A load, ripple voltage: 100 mVP-P max

Figure 25. Offline Flyback Regulator

# 11 Layout

## 11.1 Layout Guidelines

Always try to use a low-EMI inductor with a ferrite-type closed core. Some examples would be toroid and encased E core inductors. Open core can be used if they have low-EMI characteristics and are located a farther away from the low-power traces and components. Make the poles perpendicular to the PCB as well if using an open core. Stick cores usually emit the most unwanted noise.

# **Layout Guidelines (continued)**

#### 11.1.1 Feedback Traces

Try to run the feedback trace as far as possible from the inductor and noisy power traces. The designer should also make the feedback trace as direct as possible and somewhat thick. These two guidelines sometimes involve a trade-off, but keeping the trace away from inductor EMI and other noise sources is the more critical guideline. Run the feedback trace on the side of the PCB opposite of the inductor with a ground plane separating the two.

### 11.1.2 Input/Output Capacitors

When using a low-value ceramic input filter capacitor, locate it as close as possible to the VIN pin of the IC. This eliminates as much trace inductance effects as possible and gives the internal IC rail a cleaner voltage supply. Some designs require the use of a feed-forward capacitor connected from the output to the feedback pin as well, usually for stability reasons. In this case, it should also be positioned as close as possible to the IC. Using surface mount capacitors also reduces lead length and lessens the chance of noise coupling into the effective antenna created by through-hole components.

#### 11.1.3 Compensation Components

External compensation components for stability should also be placed close to the IC. TI recommends to also use surface mount components for the same reasons discussed for the filter capacitors. These should not be located very close to the inductor either.

#### 11.1.4 Traces and Ground Planes

Make all of the power (high-current) traces as short, direct, and thick as possible. It is good practice on a standard PCB to make the traces an absolute minimum of 15 mils (0.381 mm) per ampere. The inductor, output capacitors, and output diode should be as close as possible to each other. This helps reduce the EMI radiated by the power traces due to the high-switching currents through them. This also reduces lead inductance and resistance, which in turn reduces noise spikes, ringing, and resistive losses that produce voltage errors. The grounds of the IC, input capacitors, output capacitors, and output diode (if applicable) should be connected close together directly to a ground plane. It would also be a good idea to have a ground plane on both sides of the PCB. This reduces noise by reducing ground loop errors and absorbing more of the EMI radiated by the inductor.

For multi-layer boards with more than two layers, a ground plane can be used to separate the power plane (where the power traces and components are) and the signal plane (where the feedback and compensation and components are) for improved performance. On multi-layer boards, vias are required to connect traces and different planes. It is a good practice to use one standard via per 200 mA of current if the trace needs to conduct a significant amount of current from one plane to the other. Arrange the components so that the switching current loops curl in the same direction. Due to the way switching regulators operate, there are two power states: one state when the switch is on and one when the switch is off. During each state there is a current loop made by the power components that are currently conducting. Place the power components so that during each of the two states the current loop is conducting in the same direction. This prevents magnetic field reversal caused by the traces between the two half-cycles and reduces radiated EMI.

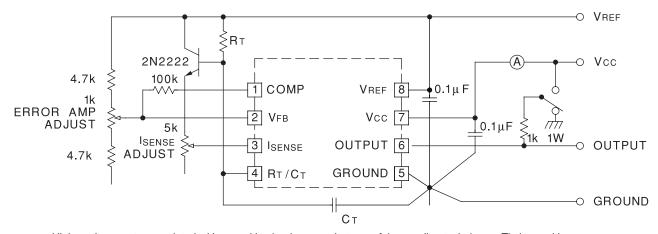

# 11.2 Layout Example

High peak currents associated with capacitive loads necessitate careful grounding techniques. Timing and bypass capacitors should be connected close to pin 5 in a single point ground. The transistor and 5k potentiometer are used to sample the oscillator waveform and apply an adjustable ramp to pin 3.

Figure 26. Open-Loop Laboratory Test Fixture

### 12 器件和文档支持

## 12.1 接收文档更新通知

要接收文档更新通知,请导航至 Tl.com.cn 上的器件产品文件夹。单击右上角的通知我进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

### 12.2 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的 《使用条款》。

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.3 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.4 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 12.5 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、缩写和定义。

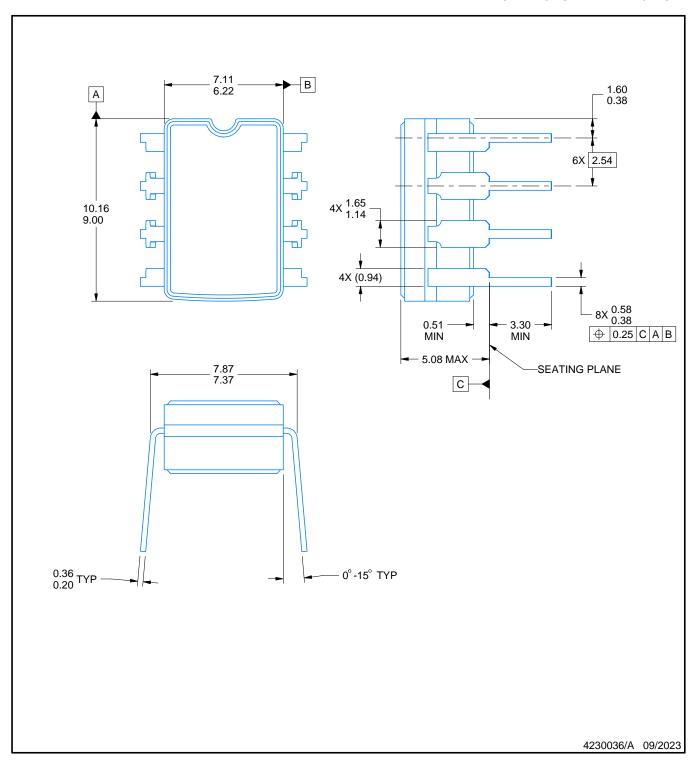

# 13 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知,且不会对此文档进行修订。如需获取此数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com 30-Apr-2024

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan               | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5)                 | Samples |

|------------------|--------|--------------|--------------------|------|----------------|------------------------|-------------------------------|--------------------|--------------|-----------------------------------------|---------|

| 5962-8670406VPA  | ACTIVE | CDIP         | JG                 | 8    | 50             | Non-RoHS<br>& Green    | SNPB                          | N / A for Pkg Type | -55 to 125   | 8670406VPA<br>UC1843A                   | Samples |

| 5962-8670406VXA  | ACTIVE | LCCC         | FK                 | 20   | 55             | Non-RoHS<br>& Green    | SNPB                          | N / A for Pkg Type | -55 to 125   | 5962-<br>8670406VXA<br>UC1843AL<br>QMLV | Samples |

| 5962-8670409VPA  | ACTIVE | CDIP         | JG                 | 8    | 50             | Non-RoHS<br>& Green    | SNPB                          | N / A for Pkg Type | -55 to 125   | 8670409VPA<br>UC1843A-SP                | Samples |

| 5962P8670409VPA  | ACTIVE | CDIP         | JG                 | 8    | 50             | Non-RoHS<br>& Green    | SNPB                          | N / A for Pkg Type | -55 to 125   | P8670409VPA<br>UC1843A-SP               | Samples |

| 5962P8670409VYC  | ACTIVE | CFP          | HKU                | 10   | 25             | RoHS-Exempt<br>& Green | NIAU                          | N / A for Pkg Type | -55 to 125   | P8670409VYC<br>UC1843A-SP               | Samples |

<sup>&</sup>lt;sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 30-Apr-2024

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF UC1843A-SP:

Catalog: UC1843A

■ Enhanced Product : UC1843A-EP

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Enhanced Product Supports Defense, Aerospace and Medical Applications

CERAMIC DUAL IN-LINE PACKAGE

## NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This package can be hermetically sealed with a ceramic lid using glass frit.

- 4. Index point is provided on cap for terminal identification. 5. Falls within MIL STD 1835 GDIP1-T8

CERAMIC DUAL IN-LINE PACKAGE

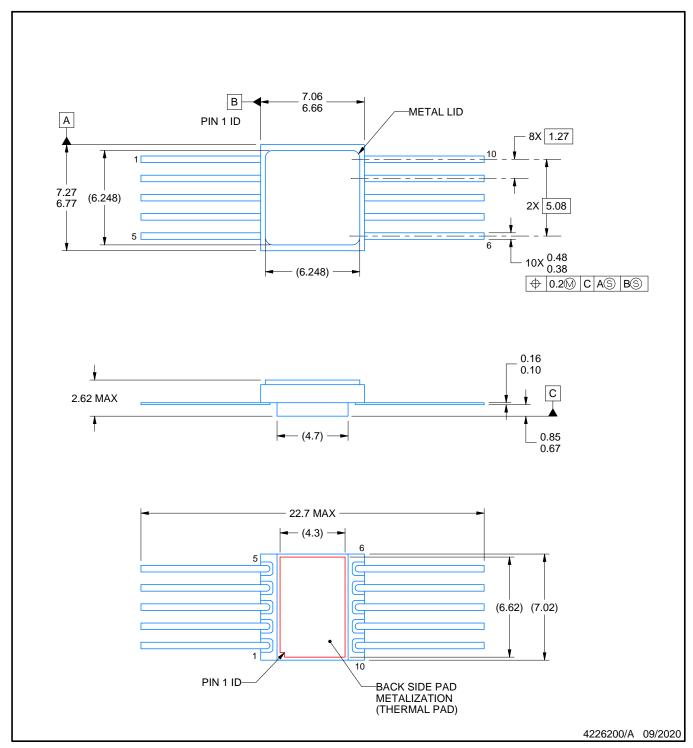

CERAMIC DUAL FLATPACK

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

This package is hermetically sealed with a metal lid.

- 4. The terminals are gold plated.

- 5. This drawing does not comply with MIL STD 1835. Do not use this package for compliant product.6. Metal lid is connected to back side pad metalization.

CERAMIC DUAL FLATPACK

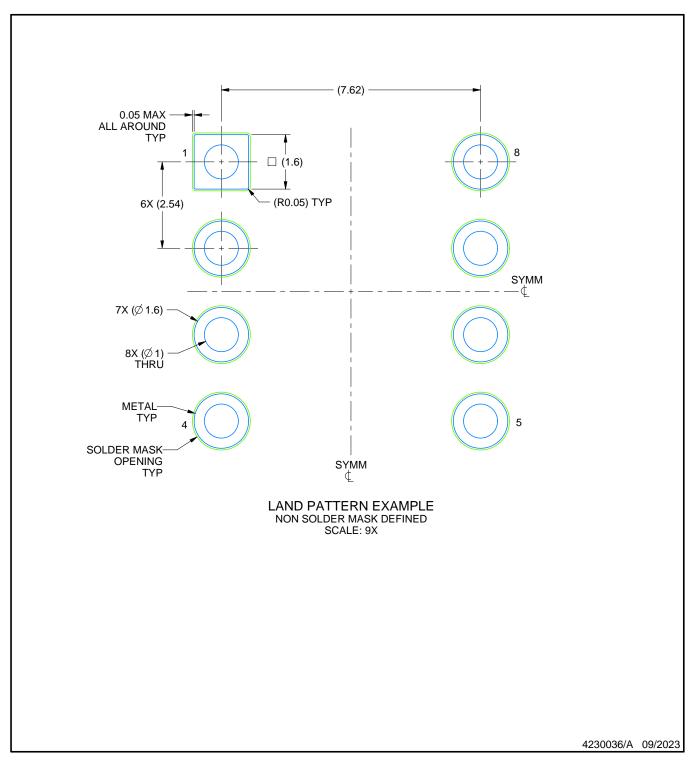

HEATSINK LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:15X

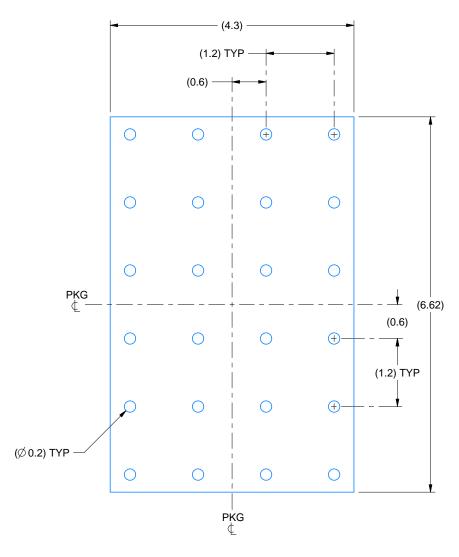

8.89 x 8.89, 1.27 mm pitch

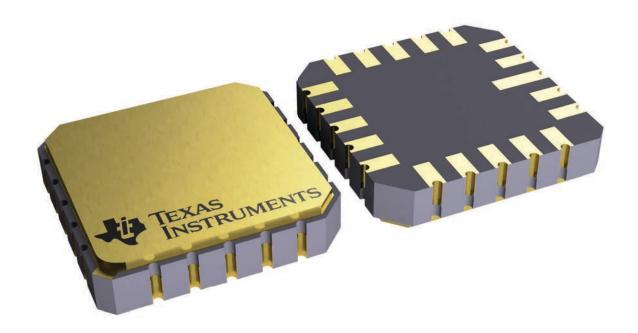

LEADLESS CERAMIC CHIP CARRIER

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司