## 250mA, Low Quiescent Current, Ultra-Low Noise, High PSRR Low-Dropout Linear Regulator

Check for Samples: TPS73433-Q1, TPS73401-Q1

#### **FEATURES**

- Qualified for Automotive Applications

- 250mA Low Dropout Regulator with EN

- Low I<sub>Q</sub>: 44µA

- Multiple Output Voltage Versions Available:

- Fixed 3.3V Outputs

- Adjustable Outputs from 1.25V to 6.2V

- High PSRR: 60dB at 1kHz

Ultra-Low Noise: 28µV<sub>RMS</sub>

Fast Start-Up Time: 45µs

- Stable with a Low-ESR, 2.0µF Typical Output Capacitance

- Excellent Load/Line Transient Response

- 2% Overall Accuracy (Load/Line/Temp)

- ThinSOT-23 Package

#### DESCRIPTION

The TPS734xx-Q1 family of low-dropout (LDO), low-power linear regulators offers excellent ac performance with very low ground current. High power-supply rejection ratio (PSRR), low noise, fast start-up, and excellent line and load transient response are provided while consuming a very low 44µA (typical) ground current. The TPS734xx-Q1 is stable with ceramic capacitors and uses an advanced BiCMOS fabrication process to yield a typical dropout 125mV at 250mA output. TPS734xx-Q1 uses a precision voltage reference and feedback loop to achieve overall accuracy of 2% over all load, line, process, and temperature variations. It is fully specified from  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$  and is offered in a low-profile ThinSOT-23 package that are ideal for wireless handsets, printers, and WLAN cards.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SBVS185 – DECEMBER 2011 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### Table 1. ORDERING INFORMATION<sup>(1)</sup>

| PRODUCT         | V <sub>out</sub> | PACKAGE MARKING |  |  |

|-----------------|------------------|-----------------|--|--|

| TPS73433TDDCRQ1 | 3.3V             | PXTQ            |  |  |

| TPS73401TDDCRQ1 | Adjustable       | Preview         |  |  |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

#### ABSOLUTE MAXIMUM RATINGS(1)

Over operating temperature range (unless otherwise noted).

| PARAMETER                                            | TPS734xx-Q1                        | UNIT                          |  |  |  |  |

|------------------------------------------------------|------------------------------------|-------------------------------|--|--|--|--|

| V <sub>IN</sub> range                                | -0.3 to +7.0                       | V                             |  |  |  |  |

| V <sub>EN</sub> range                                | -0.3 to V <sub>IN</sub> +0.3       | V                             |  |  |  |  |

| V <sub>OUT</sub> range                               | -0.3 to V <sub>IN</sub> +0.3       | V                             |  |  |  |  |

| V <sub>FB</sub> range                                | -0.3 to V <sub>FB</sub> (TYP) +0.3 | V                             |  |  |  |  |

| Peak output current                                  | Internally limited                 |                               |  |  |  |  |

| Continuous total power dissipation                   | See Dissipation Rati               | See Dissipation Ratings Table |  |  |  |  |

| Junction temperature range, T <sub>J</sub>           | -55 to +150                        | °C                            |  |  |  |  |

| Storage junction temperature range, T <sub>STG</sub> | -55 to +150                        | °C                            |  |  |  |  |

| ESD rating, HBM                                      | 2                                  | kV                            |  |  |  |  |

| ESD rating, CDM                                      | 1                                  | kV                            |  |  |  |  |

| ESD rating, MM                                       | 100                                | V                             |  |  |  |  |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

#### **DISSIPATION RATINGS**

| BOARD                 | PACKAGE | R <sub>θJC</sub> | $R_{	heta JA}$ | DERATING FACTOR<br>ABOVE T <sub>A</sub> = +25°C | T <sub>A</sub> < +25°C | T <sub>A</sub> = +70°C | T <sub>A</sub> = +85°C |  |

|-----------------------|---------|------------------|----------------|-------------------------------------------------|------------------------|------------------------|------------------------|--|

| Low-K <sup>(1)</sup>  | DDC     | 90°C/W           | 280°C/W        | 3.6mW/°C                                        | 360mW                  | 200mW                  | 145mW                  |  |

| High-K <sup>(2)</sup> | DDC     | 90°C/W           | 200°C/W        | 5.0mW/°C                                        | 500mW                  | 275mW                  | 200mW                  |  |

<sup>(1)</sup> The JEDEC low-K (1s) board used to derive this data was a 3in × 3in (7,62cm × 7,62cm), two-layer board with 2-ounce (56,699g) copper traces on top of the board.

<sup>(2)</sup> The JEDEC high-K (2s2p) board used to derive this data was a 3in × 3in (7,62cm × 7,62cm), multilayer board with 1-ounce (28,35g) internal power and ground planes and 2-ounce (56,699g) copper traces on top and bottom of the board

#### **ELECTRICAL CHARACTERISTICS**

Over operating temperature range ( $T_A = -40^{\circ}C$  to +105°C),  $V_{IN} = V_{OUT(TYP)} + 0.3V$  or 2.7V, whichever is greater;  $I_{OUT} = 1mA$ ,  $V_{EN} = V_{IN}$ ,  $C_{OUT} = 2.2\mu F$ ,  $C_{NR} = 0.01\mu F$ , unless otherwise noted. For TPS73401-Q1,  $V_{OUT} = 3.0V$ . Typical values are at  $T_A = +25^{\circ}C$ .

|                                   | PARAMETER                                                                        |                                                   | TEST CONDITIONS                                                     | MIN                   | TYP                  | MAX      | UNIT          |

|-----------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------|-----------------------|----------------------|----------|---------------|

| $V_{IN}$                          | Input voltage range <sup>(1)</sup>                                               |                                                   |                                                                     | 2.7                   |                      | 6.5      | V             |

| $V_{FB}$                          | Internal reference (TPS734                                                       | 01-Q1)                                            |                                                                     | 1.184                 | 1.208                | 1.232    | V             |

| V <sub>OUT</sub>                  | Output voltage range (TPS73401-Q1)                                               |                                                   |                                                                     | $V_{FB}$              |                      | 6.3      | V             |

| V <sub>OUT</sub>                  | Output accuracy Nominal T <sub>A</sub>                                           |                                                   | T <sub>A</sub> = +25°C                                              | -1.0                  |                      | +1.0     | %             |

| V <sub>OUT</sub>                  | Output accuracy <sup>(1)</sup>                                                   | Over V <sub>IN</sub> ,<br>I <sub>OUT</sub> , Temp | $V_{OUT} + 0.3V \le V_{IN} \le 6.5V$<br>$1mA \le I_{OUT} \le 250mA$ | -2.0                  | ±1.0                 | +2.0     | %             |

| $\Delta V_{OUT}\%/\Delta V_{IN}$  | Line regulation <sup>(1)</sup>                                                   |                                                   | $V_{OUT(NOM)} + 0.3V \le V_{IN} \le 6.5V$                           |                       | 0.02                 |          | %/V           |

| $\Delta V_{OUT}\%/\Delta I_{OUT}$ | Load regulation                                                                  |                                                   | 500μA ≤ I <sub>OUT</sub> ≤ 250mA                                    |                       | 0.005                |          | %/mA          |

| $V_{DO}$                          | Dropout voltage<br>(V <sub>IN</sub> = V <sub>OUT(NOM)</sub> - 0.1V)              |                                                   | I <sub>OUT</sub> = 250mA                                            |                       | 125                  | 219      | mV            |

| I <sub>CL</sub>                   | Output current limit                                                             |                                                   | $V_{OUT} = 0.9 \times V_{OUT(NOM)}$                                 | 300                   | 580                  | 900      | mA            |

| $I_{GND}$                         | Ground pin current                                                               |                                                   | 500μA ≤ I <sub>OUT</sub> ≤ 250mA                                    |                       | 45                   | 65       | μΑ            |

| I <sub>SHDN</sub>                 | Shutdown current (I <sub>GND</sub> )                                             |                                                   | V <sub>EN</sub> ≤ 0.4V                                              |                       | 0.15                 | 1.0      | μΑ            |

| $I_{FB}$                          | Feedback pin current (TPS                                                        | 73401-Q1)                                         |                                                                     | -0.5                  |                      | 0.5      | μΑ            |

| PSRR                              |                                                                                  |                                                   | f = 100Hz                                                           |                       | 60                   |          | dB            |

|                                   | Power-supply rejection ratio                                                     |                                                   | f = 1kHz                                                            |                       | 56                   |          | dB            |

|                                   | $V_{IN} = 3.85V$ , $V_{OUT} = 2.85V$ , $C_{NR} = 0.01 \mu F$ , $I_{OUT} = 100 m$ |                                                   | f = 10kHz                                                           |                       | 41                   |          | dB            |

|                                   | , , , ,                                                                          |                                                   | f = 100kHz                                                          |                       | 28                   |          | dB            |

| $V_N$                             | Output noise voltage                                                             |                                                   | $C_{NR} = 0.01 \mu F$                                               | 1                     | 1 x V <sub>OUT</sub> |          | $\mu V_{RMS}$ |

| ٧N                                | BW = 10Hz to 100kHz, $V_{Ol}$                                                    | <sub>T</sub> = 2.8V                               | C <sub>NR</sub> = none                                              | 95 x V <sub>OUT</sub> |                      |          | $\mu V_{RMS}$ |

|                                   | Startup time,                                                                    |                                                   | C <sub>NR</sub> = none                                              |                       | 45                   |          | μs            |

| Т                                 | $V_{OUT} = 0 \sim 90\%$                                                          |                                                   | $C_{NR} = 0.001 \mu F$                                              |                       | 45                   |          | μs            |

| $T_{STR}$                         | $V_{OUT} = 2.85V,$<br>$R_L = 14\Omega, C_{OUT} = 2.2\mu F$                       |                                                   | $C_{NR} = 0.01 \mu F$                                               |                       | 50                   |          | μs            |

|                                   | $R_L = 1452, C_{OUT} = 2.2 \mu F$                                                |                                                   | $C_{NR} = 0.047 \mu F$                                              |                       | 50                   |          | μs            |

| $V_{EN(HI)}$                      | Enable high (enabled)                                                            |                                                   |                                                                     | 1.2                   |                      | $V_{IN}$ | V             |

| $V_{EN(LO)}$                      | Enable low (shutdown)                                                            |                                                   |                                                                     | 0                     |                      | 0.4      | V             |

| I <sub>EN(HI)</sub>               | Enable pin current, enabled                                                      | <u></u>                                           | $V_{EN} = V_{IN} = 6.5V$                                            |                       | 0.03                 | 1.0      | μΑ            |

| <b>T</b>                          | Thermal chutdown tempers                                                         | atura.                                            | Shutdown, temperature increasing                                    |                       | 165                  |          | °C            |

| T <sub>SD</sub>                   | Thermal shutdown tempera                                                         | iluie                                             | Reset, temperature decreasing                                       |                       | 145                  |          | °C            |

| T <sub>A</sub>                    | Operating temperature                                                            |                                                   |                                                                     | <b>–</b> 40           |                      | +105     | °C            |

| 11)/1.0                           | Undervoltage lock-out                                                            |                                                   | V <sub>IN</sub> rising                                              | 1.90                  | 2.20                 | 2.65     | V             |

| UVLO                              | Hysteresis                                                                       |                                                   | V <sub>IN</sub> falling                                             |                       | 70                   |          | mV            |

<sup>(1)</sup> Minimum  $V_{IN} = V_{OUT} + V_{DO}$  or 2.7V, whichever is greater.

SBVS185 – DECEMBER 2011 www.ti.com

#### **DEVICE INFORMATION**

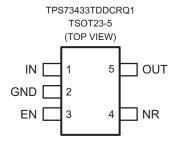

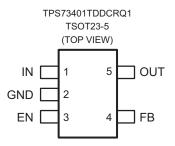

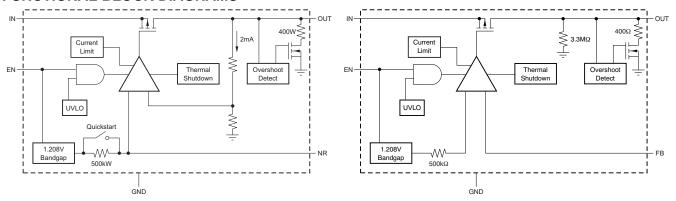

#### **FUNCTIONAL BLOCK DIAGRAMS**

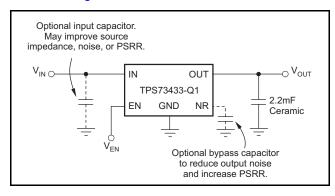

Figure 1. Fixed Voltage Versions

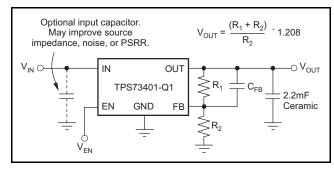

Figure 2. Adjustable Voltage Versions

Instruments

#### **PIN CONFIGURATIONS**

#### **PIN DESCRIPTIONS**

| TPS734xx-Q1 |     | DESCRIPTION                                                                                                                                                                            |

|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | DDC | DESCRIPTION                                                                                                                                                                            |

| IN          | 1   | Input supply.                                                                                                                                                                          |

| GND         | 2   | Ground. The pad must be tied to GND.                                                                                                                                                   |

| EN          | 3   | Driving the enable pin (EN) high turns on the regulator. Driving this pin low puts the regulator into shutdown mode. EN can be connected to IN if not used.                            |

| NR          | 4   | Fixed voltage versions only; connecting an external capacitor to this pin bypasses noise generated by the internal bandgap. This allows output noise to be reduced to very low levels. |

| FB          | 4   | Adjustable version only; this is the input to the control loop error amplifier, and is used to set the output voltage of the device.                                                   |

| OUT         | 5   | Output of the regulator. A small capacitor (total typical capacitance ≥ 2.0µF ceramic) is needed from this pin to ground to assure stability.                                          |

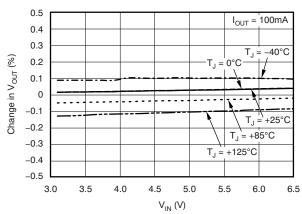

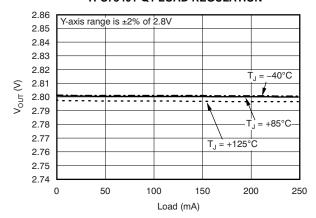

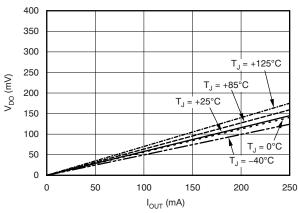

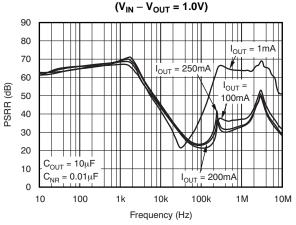

#### TYPICAL CHARACTERISTICS

Over operating temperature range ( $T_A = -40^{\circ}\text{C}$  to +105°C);  $V_{IN} = V_{OUT(TYP)} + 0.3V$  or 2.7V, whichever is greater;  $I_{OUT} = 1\text{mA}$ ,  $V_{EN} = V_{IN}$ ,  $C_{OUT} = 2.2\mu\text{F}$ ,  $C_{NR} = 0.01\mu\text{F}$ , unless otherwise noted. For TPS73401-Q1,  $V_{OUT} = 3.0V$ . Typical values are at  $T_A = +25^{\circ}\text{C}$ .

#### **TPS73401-Q1 LINE REGULATION**

Figure 3.

#### **TPS73401-Q1 LOAD REGULATION**

Figure 4.

#### TPS73401-Q1 DROPOUT VOLTAGE vs OUTPUT CURRENT

Figure 5.

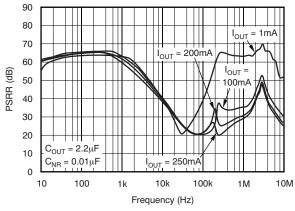

#### POWER-SUPPLY RIPPLE REJECTION vs FREQUENCY

Figure 6.

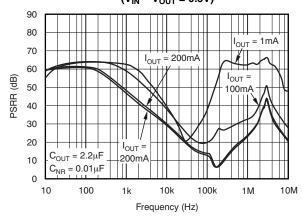

## POWER-SUPPLY RIPPLE REJECTION vs FREQUENCY $(V_{IN} - V_{OUT} = 0.5V)$

Figure 7.

## POWER-SUPPLY RIPPLE REJECTION vs FREQUENCY $(V_{IN} - V_{OUT} = 0.3V)$

Figure 8.

#### APPLICATION INFORMATION

TPS734xx-Q1 family of LDO regulators combines the high performance required of many RF and precision analog applications with ultra-low current consumption. High PSRR is provided by a high gain, high bandwidth error loop with good supply rejection at very low headroom  $(V_{IN} - V_{OLIT})$ . Fixed voltage versions provide a noise reduction pin to bypass noise generated by the bandgap reference and to improve PSRR while a quick-start circuit fast-charges this capacitor at startup. combination of high performance and low ground current also make the TPS734xx-Q1 an excellent choice for portable applications. All versions have thermal and over-current protection and are fully specified from -40°C to +105°C.

Figure 9 shows the basic circuit connections for fixed voltage models. Figure 10 gives the connections for the adjustable output version (TPS73401-Q1).  $R_1$  and  $R_2$  can be calculated for any output voltage using the formula in Figure 10.

Figure 9. Typical Application Circuit for Flxed Voltage Versions

Figure 10. Typical Application Circuit for Adjustable Voltage Versions

#### **Input and Output Capacitor Requirements**

Although an input capacitor is not required for stability, it is good analog design practice to connect a 0.1µF to 1µF low equivalent series resistance (ESR) capacitor across the input supply near the regulator. The ground of this capacitor should be connected as close as the ground of output capacitor; a capacitor value of 0.1µF is enough in this condition. When it is difficult to place these two ground points close together, a 1µF capacitor is recommended. This capacitor counteracts reactive input sources and improves transient response, noise rejection, and ripple rejection. A higher-value capacitor may be necessary if large, fast rise-time load transients are anticipated, or if the device is located several inches from the power source. If source impedance is not sufficiently low, a 0.1µF input capacitor may be necessary to ensure stability.

The TPS734xx-Q1 is designed to be stable with standard ceramic output capacitors of values  $2.2\mu F$  or larger. X5R and X7R type capacitors are best because they have minimal variation in value and ESR over temperature. Maximum ESR of the output capacitor should be <  $1.0\Omega$ , so output capacitor type should be either ceramic or conductive polymer electrolytic.

## Feedback Capacitor Requirements (TPS73401-Q1 only)

The feedback capacitor, C<sub>FB</sub>, shown in Figure 10 is required for stability. For a parallel combination of R<sub>1</sub> and R<sub>2</sub> equal to 250kΩ, any value from 3pF to 1nF can be used. Fixed voltage versions have an internal 30pF feedback capacitor that is quick-charged at start-up. The adjustable version does not have this quick-charge circuit, so values below 5pF should be used to ensure fast startup; values above 47pF can be used to implement an output voltage soft-start. Larger value capacitors also improve noise slightly. TPS73401-Q1 is stable unity-gain in configuration (OUT tied to FB) without CFB.

#### **Output Noise**

In most LDOs, the bandgap is the dominant noise source. If a noise reduction capacitor ( $C_{NR}$ ) is used with the TPS734xx-Q1, the bandgap does not contribute significantly to noise. Instead, noise is dominated by the output resistor divider and the error amplifier input. To minimize noise in a given application, use a 0.01 $\mu$ F noise reduction capacitor; for the adjustable version, smaller value resistors in the output resistor divider reduce noise. A parallel combination that gives  $2\mu$ A of divider current has the same noise performance as a fixed voltage version.

To further optimize noise, equivalent series resistance of the output capacitor can be set to approximately  $0.2\Omega$ . This configuration maximizes phase margin in the control loop, reducing total output noise by up to 10%.

Noise can be referred to the feedback point (FB pin) such that with  $C_{NR}=0.01\mu F$ , total noise is given approximately by Equation 1:

$$V_{N} = \frac{11\mu V_{RMS}}{V} \times V_{OUT}$$

(1)

The TPS73401-Q1 adjustable version does not have the noise-reduction pin available, so ultra-low noise operation is not possible. Noise can be minimized according to the above recommendations.

## Board Layout Recommendations to Improve PSRR and Noise Performance

To improve ac performance such as PSRR, output noise, and transient response, it is recommended that the board be designed with separate ground planes for  $V_{\text{IN}}$  and  $V_{\text{OUT}}$ , with each ground plane connected only at the GND pin of the device. In addition, the ground connection for the bypass capacitor should connect directly to the GND pin of the device.

#### **Internal Current Limit**

The TPS734xx-Q1 internal current limit helps protect the regulator during fault conditions. During current limit, the output sources a fixed amount of current that is largely independent of output voltage. For reliable operation, the device should not be operated in current limit for extended periods of time.

The PMOS pass element in the TPS734xx-Q1 has a built-in body diode that conducts current when the voltage at OUT exceeds the voltage at IN. This current is not limited, so if extended reverse voltage operation is anticipated, external limiting may be appropriate.

#### **Shutdown**

The enable pin (EN) is active high and is compatible with standard and low voltage TTL-CMOS levels. When shutdown capability is not required, EN can be connected to IN.

#### **Dropout Voltage**

The TPS734xx-Q1 uses a PMOS pass transistor to achieve low dropout. When  $(V_{\text{IN}} - V_{\text{OUT}})$  is less than the dropout voltage  $(V_{\text{DO}})$ , the PMOS pass device is in its linear region of operation and the input-to-output resistance is the  $R_{\text{DS},\ \text{ON}}$  of the PMOS pass element. Because the PMOS device behaves like a resistor in dropout,  $V_{\text{DO}}$  approximately scales with output current.

As with any linear regulator, PSRR and transient response are degraded as  $(V_{\text{IN}} - V_{\text{OUT}})$  approaches dropout. This effect is shown in the Typical Characteristics section.

#### **Startup and Noise Reduction Capacitor**

Fixed voltage versions of the TPS734xx-Q1 use a quick-start circuit to fast-charge the noise reduction capacitor,  $C_{NR}$ , if present (see the Functional Block Diagrams). This architecture allows the combination of very low output noise and fast start-up times. The NR pin is high impedance so a low leakage  $C_{NR}$  capacitor must be used; most ceramic capacitors are appropriate in this configuration.

Note that for fastest startup,  $V_{\text{IN}}$  should be applied first, then the enable pin (EN) driven high. If EN is tied to IN, startup is somewhat slower. Refer to the Typical Characteristics section. The quick-start switch is closed for approximately 135 $\mu$ s. To ensure that  $C_{\text{NR}}$  is fully charged during the quick-start time, a 0.01 $\mu$ F or smaller capacitor should be used.

#### **Transient Response**

As with any regulator, increasing the size of the output capacitor reduces over/undershoot magnitude but increases duration of the transient response. In the adjustable version, adding  $C_{FB}$  between OUT and FB improves stability and transient response. The transient response of the TPS734xx-Q1 is enhanced by an active pull-down that engages when the output overshoots by approximately 5% or more when the device is enabled. When enabled, the pull-down device behaves like a  $400\Omega$  resistor to ground.

#### **Undervoltage Lock-Out (UVLO)**

The TPS734xx-Q1 utilizes an undervoltage lock-out circuit to keep the output shut off until internal circuitry is operating properly. The UVLO circuit has a de-glitch feature so that it typically ignores undershoot transients on the input if they are less than 50µs duration.

#### Minimum Load

The TPS734xx-Q1 is stable and well-behaved with no output load. To meet the specified accuracy, a minimum load of 1mA is required. Below 1mA at junction temperatures near +125°C, the output can drift up enough to cause the output pull-down to turn on. The output pull-down limits voltage drift to 5% typically but ground current could increase by approximately  $50\mu A$ . In typical applications, the junction cannot reach high temperatures at light loads because there is no appreciable dissipated power. The specified ground current would then be valid at no load conditions in most applications.

#### Thermal Information

#### **Thermal Protection**

Thermal protection disables the output when the junction temperature rises to approximately +165°C, allowing the device to cool. When the junction temperature cools to approximately +145°C the output circuitry is again enabled. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits the dissipation of the regulator, protecting it from damage as a result of overheating.

Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate heatsink. For reliable operation, junction temperature should be limited to +125°C maximum. To estimate the margin of safety in a complete design increase (including heatsink), the temperature until the thermal protection is triggered; use worst-case loads and signal conditions. For good reliability, thermal protection should trigger at least +35°C above the maximum expected ambient condition of your particular application. configuration produces a worst-case junction temperature of +125°C at the highest expected ambient temperature and worst-case load.

The internal protection circuitry of the TPS734xx-Q1 has been designed to protect against overload conditions. It was not intended to replace proper heatsinking. Continuously running the TPS734xx-Q1 into thermal shutdown degrades device reliability.

#### **Power Dissipation**

The ability to remove heat from the die is different for package presenting different each type, considerations in the PCB layout. The PCB area around the device that is free of other components moves the heat from the device to the ambient air. Performance data for JEDEC low- and high-K boards are given in the Dissipation Ratings table. Using heavier copper increases the effectiveness in removing heat from the device. The addition of plated through-holes to heat-dissipating lavers improves the heatsink effectiveness.

Power dissipation depends on input voltage and load conditions. Power dissipation is equal to the product of the output current time the voltage drop across the output pass element, as shown in Equation 2:

$$P_{D} = (V_{IN} - V_{OUT}) \cdot I_{OUT}$$

(2)

#### **Package Mounting**

Solder pad footprint recommendations for the TPS734xx-Q1 are available from the Texas Instruments web site at www.ti.com.

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins            | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|---------------------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                           |                       |      | (4)                           | (5)                        |              |                  |

| TPS73433TDDCRQ1       | Active | Production    | SOT-23-<br>THIN (DDC)   5 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 105   | PXTQ             |

| TPS73433TDDCRQ1.B     | Active | Production    | SOT-23-<br>THIN (DDC)   5 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 105   | PXTQ             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

#### **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Sep-2024

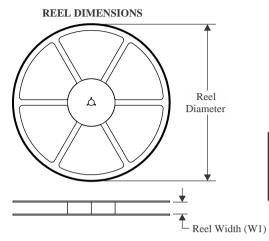

#### TAPE AND REEL INFORMATION

# TAPE DIMENSIONS KO P1 BO W Cavity A0

| _  | Tanana and a same and a same and a same and a same a s |

|----|----------------------------------------------------------------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width                                                          |

| В0 | Dimension designed to accommodate the component length                                                         |

| K0 | Dimension designed to accommodate the component thickness                                                      |

| W  | Overall width of the carrier tape                                                                              |

| P1 | Pitch between successive cavity centers                                                                        |

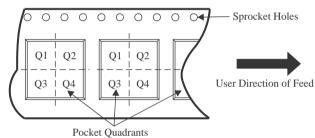

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          |                 | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS73433TDDCRQ1 | SOT-23-<br>THIN | DDC                | 5 | 3000 | 179.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

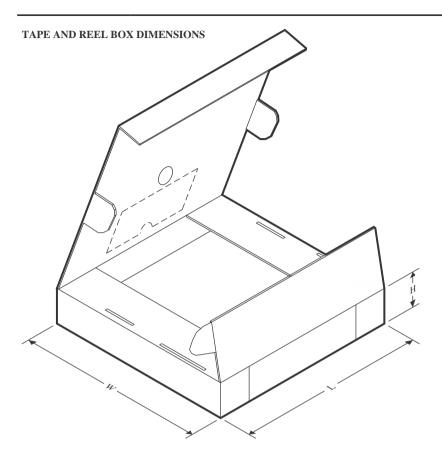

#### **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Sep-2024

#### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS73433TDDCRQ1 | SOT-23-THIN  | DDC             | 5    | 3000 | 213.0       | 191.0      | 35.0        |

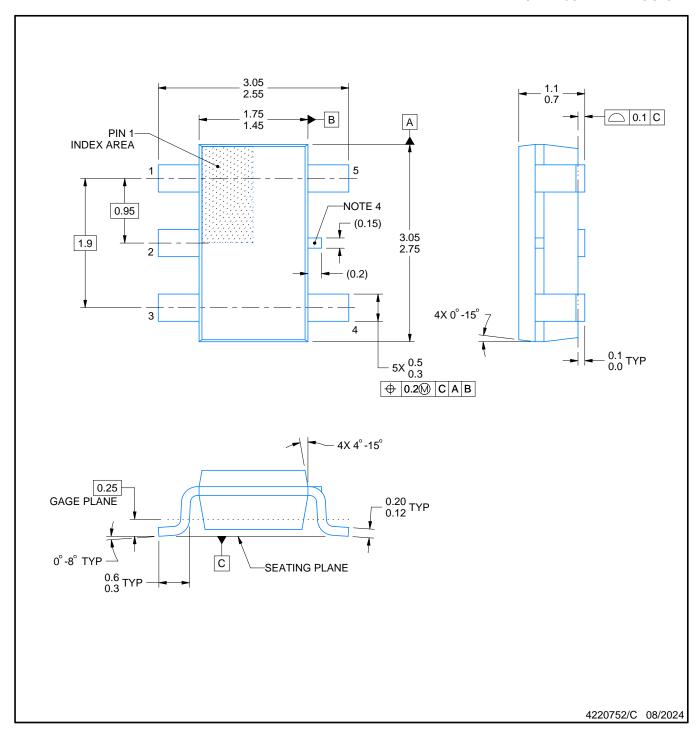

SMALL OUTLINE TRANSISTOR

#### NOTES:

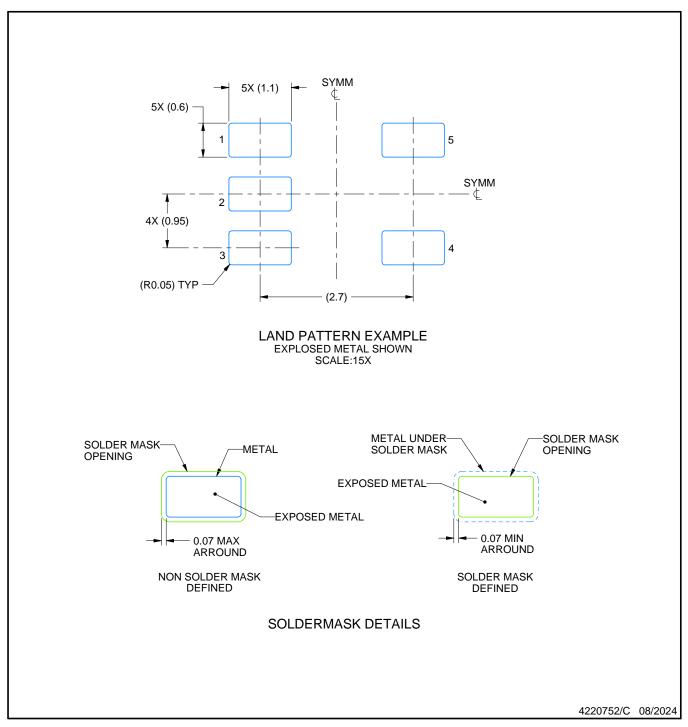

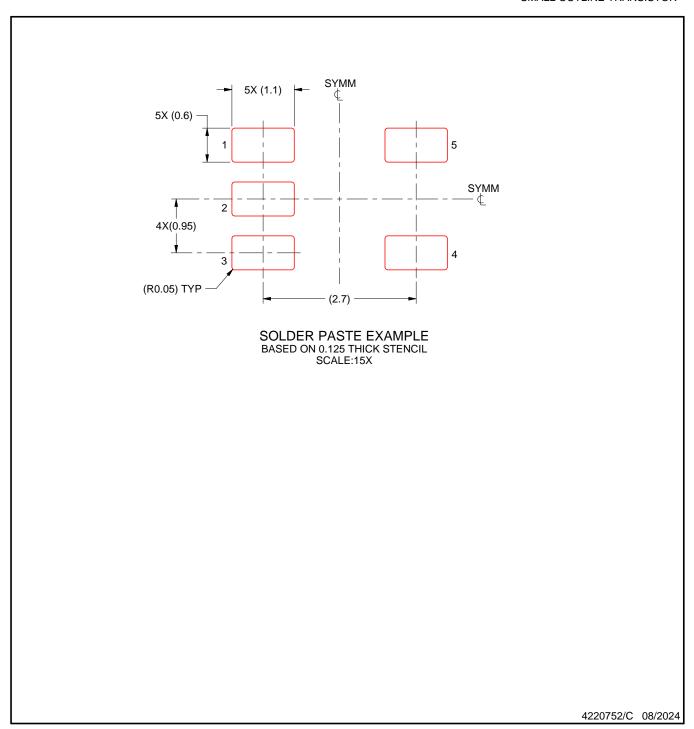

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

Reference JEDEC MO-193.

- 4. Support pin may differ or may not be present.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 4. Publication IPC-7351 may have alternate designs.

- 5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

7. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025