# **TPS65735** PMU 用于有源快门**3D** 眼镜

# **Data Manual**

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Literature Number: ZHCS357 June 2011 ZHCS357-JUNE 2011

# 内容

| 1 | 介绍                  |           |                                               | <u>5</u>      |

|---|---------------------|-----------|-----------------------------------------------|---------------|

|   | 1.1                 | 特性        |                                               | <u>5</u>      |

|   | 1.2                 | 说明        |                                               | <u>5</u>      |

|   | 1.3                 | 引脚说明      | 月                                             | <u>6</u>      |

| 2 | 1.4<br><b>POW</b> I |           | 即分布<br>NAGEMENT CORE                          |               |

|   | 2.1                 | Recomr    | mended Operating Conditions                   | 8             |

|   | 2.2                 | Absolute  | e Maximum Ratings                             | <u>8</u>      |

|   | 2.3                 | Therma    | I Information                                 | 9             |

|   | 2.4                 | Quiesce   | ent Current                                   | 9             |

|   | 2.5                 | Electrica | al Characteristics                            | 9             |

|   | 2.6                 | System    | Operation                                     | _             |

|   |                     | 2.6.1     | System Power Up                               | <u>13</u>     |

|   |                     | 2.6.2     | System Operation Using Push Button Switch     | <u>14</u>     |

|   |                     | 2.6.3     | System Operation Using Slider Switch          |               |

|   | 2.7                 |           | Charger Operation                             |               |

|   |                     | 2.7.1     | Battery and TS Detection                      | $\overline{}$ |

|   |                     | 2.7.2     | Battery Charging                              |               |

|   |                     |           | 2.7.2.1 Pre-charge                            | _             |

|   |                     |           | 2.7.2.2 Charge Termination                    |               |

|   |                     |           | 2.7.2.3 Recharge                              |               |

|   |                     |           | 2.7.2.4 Charge Timers                         |               |

|   | 2.8                 | 2.7.3     | Charger Status (nCHG_STAT Pin)                | _             |

|   | 2.0                 | 2.8.1     | LDO Internal Current Limit                    |               |

|   | 2.9                 |           | Converter Operation                           | _             |

|   | 2.0                 | 2.9.1     | Boost Thermal Shutdown                        | _             |

|   |                     | 2.9.2     | Boost Load Disconnect                         |               |

|   | 2.10                |           | Bridge Analog Switches                        | _             |

|   |                     | 2.10.1    | H-Bridge Switch Control                       |               |

|   | 2.11                | Power N   | Management Core Control                       | _             |

|   |                     | 2.11.1    | SLEEP / Power Control Pin Function            | <u>22</u>     |

|   |                     | 2.11.2    | COMP Pin Functionality                        | <u>22</u>     |

|   |                     | 2.11.3    | SW_SEL Pin Functionality                      | <u>23</u>     |

|   |                     | 2.11.4    | SWITCH Pin                                    | <u>23</u>     |

|   |                     | 2.11.5    | Slider Switch Behavior                        | <u>23</u>     |

|   |                     | 2.11.6    | Push-Button Switch Behavior                   | 24            |

| 3 | APPL                | ICATIO    | N INFORMATION                                 | <u> 26</u>    |

|   | 3.1                 | Applicat  | tions Schematic                               | <u>26</u>     |

|   | 3.2                 |           | ng System Quiescent Current (I <sub>Q</sub> ) |               |

|   | 3.3                 | Boost C   | Converter Application Information             |               |

|   |                     | 3.3.1     | Setting Boost Output Voltage                  |               |

|   |                     | 3.3.2     | Boost Inductor Selection                      | _             |

|   | _                   | 3.3.3     | Boost Capacitor Selection                     |               |

|   | 3.4                 | Bypassi   | ing Default Push-Button SWITCH Functionality  | <u>28</u>     |

# 图片列表

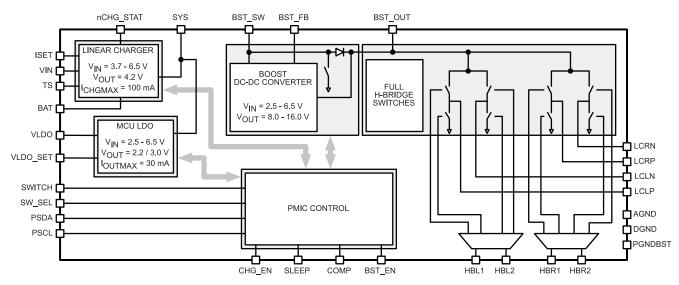

| 1-1  | TPS65735 的简化原理框图                                          | <u>5</u>  |

|------|-----------------------------------------------------------|-----------|

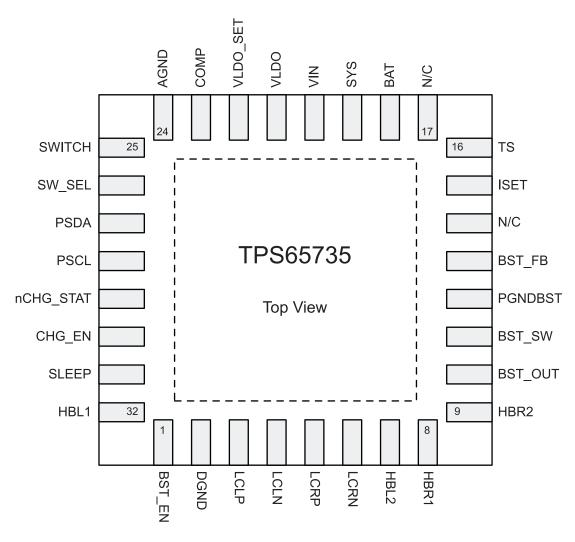

| 1-2  | TPS65735 封装引脚分布                                           | 7         |

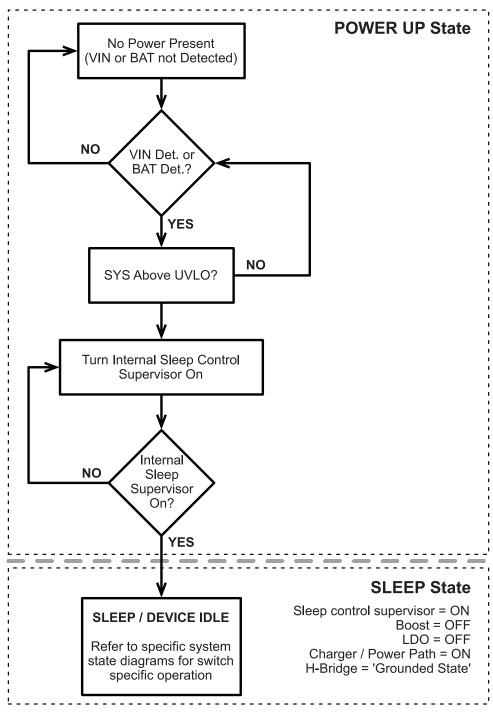

| 2-1  | System Power Up State Diagram                             | <u>14</u> |

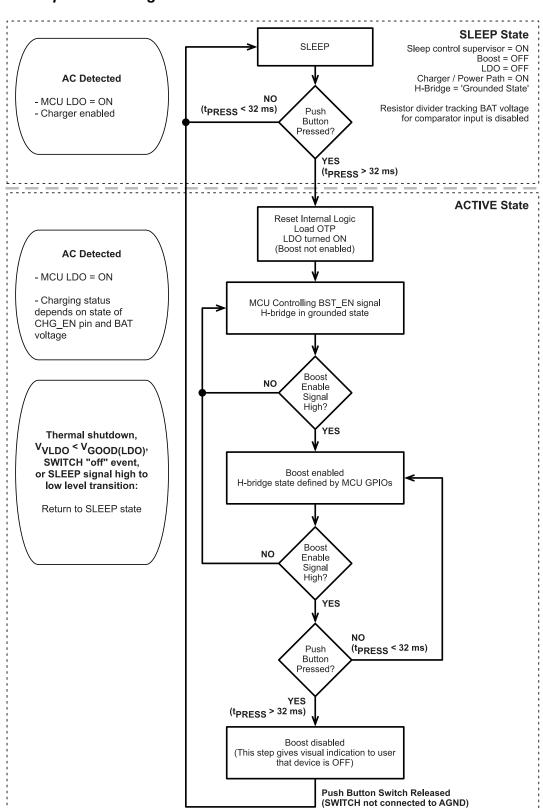

| 2-2  | Push Button State Diagram                                 | <u>15</u> |

| 2-3  | System Operation Using Slider Switch                      | <u>15</u> |

| 2-4  | Thermistor Detection and Circuit                          | <u>16</u> |

| 2-5  | Battery Charge Phases                                     |           |

| 2-10 | Boost Load Disconnect                                     | <u>20</u> |

| 2-11 | H-Bridge States                                           | <u>21</u> |

| 2-12 | H-Bridge States from Oscilloscope                         | 22        |

| 2-13 | SLEEP Signal to Force System Power Off                    | 22        |

| 2-14 | COMP Pin Internal Connection                              | 22        |

| 2-15 | SWITCH, Slider Power On-Off Behavior                      | <u>24</u> |

| 2-16 | SWITCH, Push-button Power On Behavior                     | <u>25</u> |

| 2-17 | SWITCH, Push-button Power Off Behavior                    | <u>25</u> |

| 3-1  | TPS65735 Applications Schematic                           | <u>26</u> |

| 3-2  | Reducing System I <sub>Q</sub> with Addition of a FET     | <u>27</u> |

| 3-3  | Boost Feedback Network Schematic                          | 27        |

| 3-4  | Bypassing Default TPS65735 Push Button SWITCH Timing      | 29        |

| 3-5  | SWITCH Press and SLEEP Signal to Control System Power Off |           |

|      |                                                           |           |

ZHCS357-JUNE 2011

# 图表表

| 1-1 | 引脚说明                                                                                     | 6  |

|-----|------------------------------------------------------------------------------------------|----|

| 1-2 | 引脚的最大绝对额定值                                                                               | 7  |

| 2-1 | nCHG_STAT Functionality                                                                  | 18 |

| 2-2 | VLDO_SET Functionality                                                                   | 18 |

| 2-3 | H-Bridge States from Inputs                                                              | 21 |

| 2-4 | Scaling Resistors for COMP Pin Function (V <sub>VLDO</sub> = 2.2 V)                      | 23 |

| 2-5 | Scaling Resistors for COMP Pin Function (V <sub>VLDO</sub> = 3.0 V)                      | 23 |

| 2-6 | SW_SEL Settings                                                                          | 23 |

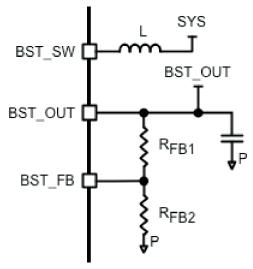

| 3-1 | Recommended R <sub>FB1</sub> and R <sub>FB2</sub> Values (for I <sub>Q(FB)</sub> = 5 µA) | 28 |

# PMU 用于有源快门3D 眼镜

查询样品: TPS65735

# 1 介绍

# 1.1 特性

- 线性充电器

- 三个充电阶段: 预充电、快速充电和充电终止

- 从外部设定的充电电流可支持高达 100mA

- 用于电源状态良好和充电器状态指示的 LED 电流吸收器

- 用于外部模块(微控制器、RF 模块、IR 模块)的 LDO 电源

- LDO 连续输出电流高达 30 mA

- 升压转换器

- 可调输出电压: 8 V 至 16 V

- 升压输出在内部连接至 H 桥模拟开关

- · 全 H 桥模拟开关

- 受控于一个外部微控制器以实现系统操作

- 输出引脚可提供经过分压的电池电压,适用于 ADC 或 MCU 的比较器输入

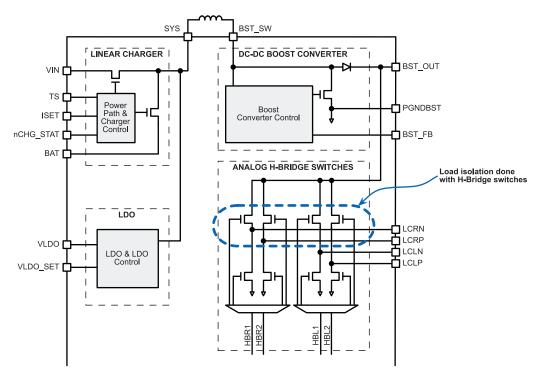

## 1.2 说明

TPS65735 是一款用于有源快门 3D 眼镜的电源管理单元 (PMU),它包括集成型电源通路、线性充电器、LDO、升压转换器以及用于在一副有源快门 3D 眼镜中实现左右快门操作的全 H 桥模拟开关。除了功率器件之外,典型的 3D 眼镜系统还包括一个微控制器和一个通信前端(IR、RF 或其他),以处理通信和同步操作以及一部 3D 电视。

图 1-1. TPS65735 的简化原理框图

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# **1.3** 引脚说明

表 1-1. 引脚说明

| 引脚名称          | I/O | 引脚序号   | 说明                                                                                                                              |

|---------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------|

| 电源管理内核 (PMIC) |     |        |                                                                                                                                 |

| VIN           | I   | 20     | AC 或 USB 适配器输入                                                                                                                  |

| ISET          | I/O | 15     | 快速充电电流设定电阻器                                                                                                                     |

| TS            | I   | 16     | Pin for 10 k $\Omega$ NTC Thermistor Connection FLOAT IF THERMISTOR / TS FUNCTION IS NOT USED                                   |

| nCHG_STAT     | 0   | 29     | Open-drain Output, Charge Status Indication CONNECT TO GROUND IF FUNCTION IS NOT USED                                           |

| BAT           | I/O | 18     | 充电器功率级输出和电池电压感测输入                                                                                                               |

| SYS           | 0   | 19     | 至系统的输出端                                                                                                                         |

| VLDO          | 0   | 21     | LDO 输出                                                                                                                          |

| VLDO_SET      | 1   | 22     | Sets LDO Output Voltage (see 表 2-2)                                                                                             |

| 开关            | ı   | 25     | 用于器件接通/关断的开关输入                                                                                                                  |

| SW_SEL        | 1   | 26     | Selects Type of Switch Connected to SWITCH Pin (see 表 2-6)                                                                      |

| BST_SW        | 0   | 11     | 升压开关节点                                                                                                                          |

| BST_FB        | 1   | 13     | 升压反馈节点                                                                                                                          |

| BST_OUT       | 0   | 10     | 升压输出                                                                                                                            |

| HBR1          | ı   | 8      | 用于右 LC 快门的 H 桥输入 1                                                                                                              |

| HBR2          | I   | 9      | 用于右 LC 快门的 H 桥输入 2                                                                                                              |

| HBL1          | ı   | 32     | 用于左 LC 快门的 H 桥输入 1                                                                                                              |

| HBL2          | I   | 7      | 用于左 LC 快门的 H 桥输入 2                                                                                                              |

| LCRN          | 0   | 6      | 用于右 LC 快门的 H 桥输出,"负(一)"端子                                                                                                       |

| LCRP          | 0   | 5      | 用于右 LC 快门的 H 桥输出,"正(+)"端子                                                                                                       |

| LCLN          | 0   | 4      | 用于左 LC 快门的 H 桥输出,"负(一)"端子                                                                                                       |

| LCLP          | 0   | 3      | 用于左 LC 快门的 H 桥输出,"正(+)"端子                                                                                                       |

| COMP          | 0   | 23     | Scaled Battery Voltage for MCU Comparator or ADC Input (Battery Voltage Monitoring) DO NOT CONNECT IF COMP FUNCTION IS NOT USED |

| 睡眠            | I/O | 31     | 来自一个 MCU 的睡眠启用输入(边缘触发,仅用于系统关断)                                                                                                  |

| BST_EN        | I   | 1      | 来自一个 MCU 的升压启用输入,高电平 = 升压被启用                                                                                                    |

| CHG_EN        | ı   | 30     | 来自一个 MCU 的充电器启用输入,高电平 = 升压被启用                                                                                                   |

| PSCL          | I/O | 28     | I <sup>2</sup> C Clock Pin (only used for TI debug and test) GROUND PIN IN APPLICATION                                          |

| PSDA          | I/O | 27     | I <sup>2</sup> C Data Pin (only used for TI debug and test) GROUND PIN IN APPLICATION                                           |

| PGNDBST       | -   | 12     | 升压电源地                                                                                                                           |

| AGND          | -   | 24     | 模拟地                                                                                                                             |

| DGND          | -   | 2      | 数字地                                                                                                                             |

| MISC. 及封装     | 1   |        | •                                                                                                                               |

| Thermal PAD   | -   | 33     | 在裸露散热焊盘与器件的 AGND 接地引脚之间布设了一根内部电气连接线。 散热焊盘必须连接至与印刷电路板上的 AGND 引脚相同的电位。 不要将散热焊盘用作器件的主要接地输入。 AGND 引脚必须始终连接至地。                       |

| 悬空            | -   | 14, 17 | 应把所有的悬空 (N/C) 引脚连接至主系统地。                                                                                                        |

## 表 1-2. 引脚的最大绝对额定值

| 引脚                                                                                                 | 数值/单位           |

|----------------------------------------------------------------------------------------------------|-----------------|

| 所有引脚(VIN、BST_OUT、BST_SW、BST_FB、VLDO、LCLP、LCLN、LCRP、LCRN、AGND、DGND 及PGNDBST 引脚除外)的输入电压范围均以 AGND 为基准 | -0.3 V 至 7.0 V  |

| VIN (相对于 AGND)                                                                                     | -0.3 V 至 28.0 V |

| BST_OUT、BST_SW、LCLP、LCLN、LCRP 和 LCRN(相对于 PGNDBST)                                                  | -0.3 V 至 18.0 V |

| BST_FB(相对于 PGNDBST), VLDO(相对于 DGND)                                                                | -0.3 V 至 3.6 V  |

# 1.4 封装引脚分布

Pins 14 & 17 = N/C. No internal connection, connect to main system ground.

图 1-2. TPS65735 封装引脚分布

ZHCS357 – JUNE 2011 www.ti.com.cn

# 2 POWER MANAGEMENT CORE

# 2.1 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| SUBSYSTEM AND PA                   | ARAMETER                                                                                             | MIN | NOM | MAX               | UNIT |

|------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-------------------|------|

| CHARGER / POWER                    | PATH                                                                                                 |     |     |                   |      |

| V <sub>VIN</sub>                   | Voltage range at charger input pin                                                                   | 3.7 |     | 28 <sup>(1)</sup> | V    |

| I <sub>VIN</sub>                   | Input current at VIN pin                                                                             |     |     | 200               | mA   |

| C <sub>VIN</sub>                   | Capacitor on VIN pin                                                                                 | 0.1 | 2.2 | 10                | μF   |

| L <sub>VIN</sub>                   | Inductance at VIN pin                                                                                | 0   |     | 2                 | μH   |

| V <sub>SYS</sub>                   | Voltage range at SYS pin                                                                             | 2.5 |     | 6.4               | V    |

| I <sub>SYS(OUT)</sub>              | Output current at SYS pin                                                                            |     |     | 100               | mA   |

| C <sub>SYS</sub>                   | Capacitor on SYS pin                                                                                 | 0.1 | 4.7 | 10                | μF   |

| V <sub>BAT</sub>                   | Voltage range at BAT pin                                                                             | 2.5 |     | 6.4               | V    |

| C <sub>BAT</sub>                   | Capacitor on BAT pin                                                                                 | 4.7 |     | 10                | μF   |

| R <sub>EXT(nCHG_STAT)</sub>        | Resistor connected to nCHG_STAT pin to limit current into pin                                        | 320 |     |                   | Ω    |

| BOOST CONVERTER                    | / H-BRIDGE SWITCHES                                                                                  |     |     |                   |      |

| V <sub>IN(BST_SW)</sub>            | Input voltage range for boost converter                                                              | 2.5 |     | 6.5               | V    |

| V <sub>BST_OUT</sub>               | Output voltage range for boost converter                                                             | 8   |     | 16                | V    |

| C <sub>BST_OUT</sub>               | Boost output capacitor                                                                               | 3.3 | 4.7 | 10                | μF   |

| L <sub>BST_SW</sub> <sup>(2)</sup> | Inductor connected between SYS and BST_SW pins                                                       | 4.7 |     | 10 <sup>(3)</sup> | μH   |

| LDO                                |                                                                                                      |     |     |                   |      |

| C <sub>VLDO</sub>                  | External decoupling cap on pin VLDO                                                                  | 1   |     | 10                | μF   |

| POWER MANAGEME                     | NT CORE CONTROL (LOGIC LEVELS FOR GPIOs)                                                             |     |     |                   |      |

| V <sub>IL(PMIC)</sub>              | GPIO low level (BST_EN, CHG_EN, SW_SEL, VLDO_SET and to switch H-Bridge inputs to a low, 0, level)   |     |     | 0.4               | V    |

| V <sub>IH(PMIC)</sub>              | GPIO high level (BST_EN, CHG_EN, SW_SEL, VLDO_SET and to switch H-Bridge inputs to a high, 1, level) | 1.2 |     |                   | V    |

<sup>(1)</sup> VIN pin has 28 V ESD protection

## 2.2 Absolute Maximum Ratings

| PARAMETER                                                                          | MINIMUM | MAXIMUM | UNITS |

|------------------------------------------------------------------------------------|---------|---------|-------|

| Operating free-air temperature, T <sub>A</sub>                                     | 0       | 60      | °C    |

| Max Junction Temperature, T <sub>J</sub> , Electrical Characteristics Guaranteed   | 0       | 85      | °C    |

| Max Junction temperature, T <sub>J</sub> , Functionality Guaranteed <sup>(1)</sup> | 0       | 105     | °C    |

<sup>(1)</sup> Device has a thermal shutdown feature implemented that shuts down at 105 °C

<sup>(2)</sup> See † 2.9 for information on boost converter inductor selection.

<sup>(3)</sup> Design optimized for boost operation with 10 µH inductor

#### 2.3 Thermal Information

|                         |                                                                                                                                                                                                                                                                                          | TPS65735 |       |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|

|                         | Junction-to-ambient thermal resistance <sup>(1)</sup> Junction-to-case (top) thermal resistance <sup>(2)</sup> Junction-to-board thermal resistance <sup>(3)</sup> Junction-to-top characterization parameter <sup>(4)</sup> Junction-to-board characterization parameter <sup>(5)</sup> | RSN      | UNITS |

|                         |                                                                                                                                                                                                                                                                                          | 32 PINS  |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(1)</sup>                                                                                                                                                                                                                                    | 38.9     |       |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance (2)                                                                                                                                                                                                                                            | 26.5     |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance (3)                                                                                                                                                                                                                                                 | 9.8      | 8000  |

| Ψлт                     | Junction-to-top characterization parameter <sup>(4)</sup>                                                                                                                                                                                                                                | 0.3      | °C/W  |

| ΨЈВ                     | Junction-to-board characterization parameter <sup>(5)</sup>                                                                                                                                                                                                                              | 9.8      | 1     |

| $\theta_{JCbot}$        | Junction-to-case (bottom) thermal resistance (6)                                                                                                                                                                                                                                         | 3.5      |       |

- (1) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (2) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (3) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (4) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (5) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### 2.4 Quiescent Current

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                              | TEST CONDITIONS                                                                                                                                                             | MIN | TYP | MAX  | UNIT |

|------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>Q(SLEEP)</sub>  | Power management core quiescent current in sleep mode  | @ 25° C  V <sub>BAT</sub> = 3.6 V  V <sub>VIN</sub> = 0 V  No load on LDO  CHG_EN, BST_EN grounded  BST_FB = 300 mV  Power management core in sleep mode / device 'off'     |     | 8.6 | 10.5 | μА   |

| I <sub>Q(ACTIVE)</sub> | Power management core quiescent current in active mode | @ 25° C  V <sub>BAT</sub> = 3.6 V  V <sub>VIN</sub> = 0 V  Boost enabled but not switching, H-bridge in grounded state No load on LDO  Power management core in active mode |     | 39  | 53.5 | μА   |

## 2.5 Electrical Characteristics

|                                 | PARAMETER                                         | TEST CONDITIONS                                                                                                                                   | MIN | TYP | MAX  | UNIT |

|---------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| BATTERY                         | CHARGER POWER PATH                                |                                                                                                                                                   |     |     |      |      |

| V <sub>UVLO(VIN)</sub>          | Undervoltage lockout at power path input, VIN pin | $V_{VIN}$ : 0 V $\rightarrow$ 4 V                                                                                                                 | 3.2 | 3.3 | 3.45 | V    |

| V <sub>HYS</sub> -<br>UVLO(VIN) | Hysteresis on UVLO at power path input, VIN pin   | $V_{VIN}$ : 4 V $\rightarrow$ 0 V                                                                                                                 | 200 |     | 300  | mV   |

| V <sub>IN-DT</sub>              | Input power detection threshold                   | Input power detected if: ( $V_{VIN} > V_{BAT} + V_{IN-DT}$ );<br>$V_{BAT} = 3.6 \text{ V}$<br>$V_{VIN}$ : $3.5 \text{ V} \rightarrow 4 \text{ V}$ | 40  |     | 140  | mV   |

| V <sub>HYS-INDT</sub>           | Hysteresis on V <sub>IN-DT</sub>                  | $V_{BAT} = 3.6 \text{ V}$<br>$V_{VIN}$ : 4 V $\rightarrow$ 3.5 V                                                                                  | 20  |     |      | mV   |

ZHCS357-JUNE 2011 www.ti.com.cn

# **Electrical Characteristics (continued)**

|                               | PARAMETER                                                                                  | TEST CONDITIONS                                                                                                                                                 | MIN                        | TYP                                           | MAX                        | UNIT |

|-------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------|----------------------------|------|

| $V_{OVP}$                     | Input over-voltage protection threshold                                                    | $V_{VIN}$ : 5 V $\rightarrow$ 7 V                                                                                                                               | 6.4                        | 6.6                                           | 6.8                        | V    |

| V <sub>HYS-OVP</sub>          | Hysteresis on OVP                                                                          | $V_{VIN}$ : 11 V $\rightarrow$ 5 V                                                                                                                              |                            | 105                                           |                            | mV   |

| V <sub>DO(VIN-</sub><br>SYS)  | VIN pin to SYS pin dropout voltage V <sub>VIN</sub> – V <sub>SYS</sub>                     | $I_{SYS}$ = 150 mA (including $I_{BAT}$ )<br>$V_{VIN}$ = 4.35 V<br>$V_{BAT}$ = 3.6 V                                                                            |                            |                                               | 350                        | mV   |

| V <sub>DO(BAT</sub> -<br>SYS) | BAT pin to SYS pin dropout voltage V <sub>BAT</sub> – V <sub>SYS</sub>                     | I <sub>SYS</sub> = 100 mA<br>V <sub>VIN</sub> = 0 V<br>V <sub>BAT</sub> > 3 V                                                                                   |                            |                                               | 150                        | mV   |

| I <sub>VIN(MAX)</sub>         | Maximum power path input current at pin VIN                                                | V <sub>VIN</sub> = 5 V                                                                                                                                          |                            | 200                                           |                            | mA   |

| V <sub>SUP(ENT)</sub>         | Enter battery supplement mode                                                              |                                                                                                                                                                 |                            | $V_{SYS} \le (V_{BAT} - 40 $ mV)              |                            | V    |

| V <sub>SUP(EXIT)</sub>        | Exit battery supplement mode                                                               |                                                                                                                                                                 |                            | V <sub>SYS</sub> ≥ (V <sub>BAT</sub> - 20 mV) |                            | V    |

| V <sub>SUP(SC)</sub>          | Output short-circuit limit in supplement mode                                              |                                                                                                                                                                 |                            | 250                                           |                            | mV   |

| V <sub>O(SC)</sub>            | Output short-circuit detection threshold, power-on                                         |                                                                                                                                                                 |                            | 0.9                                           |                            | V    |

| BATTERY                       | CHARGER                                                                                    | 1                                                                                                                                                               |                            |                                               |                            |      |

| I <sub>CC</sub>               | Active supply current into VIN pin                                                         | $V_{VIN} = 5 V$ No load on SYS pin $V_{BAT} > V_{BAT(REG)}$                                                                                                     |                            |                                               | 2                          | mA   |

| I <sub>BAT(SC)</sub>          | Source current for BAT pin short-circuit detection                                         |                                                                                                                                                                 |                            | 1                                             |                            | mA   |

| V <sub>BAT(SC)</sub>          | BAT pin short-circuit detection threshold                                                  |                                                                                                                                                                 | 1.6                        | 1.8                                           | 2.0                        | V    |

| V <sub>BAT(REG)</sub>         | Battery charger output voltage                                                             |                                                                                                                                                                 | -1%                        | 4.20                                          | 1%                         | V    |

| $V_{LOWV}$                    | Pre-charge to fast-charge transition threshold                                             |                                                                                                                                                                 | 2.9                        | 3.0                                           | 3.1                        | V    |

| I <sub>CHG</sub>              | Charger fast charge current range I <sub>CHG</sub> = K <sub>ISET</sub> / R <sub>ISET</sub> | $V_{VIN} = 5 V$<br>$V_{BAT(REG)} > V_{BAT} > V_{LOWV}$                                                                                                          | 5                          |                                               | 100                        | mA   |

| K <sub>ISET</sub>             | Battery fast charge current set factor $I_{CHG} = K_{ISET} / R_{ISET}$                     | $\begin{array}{l} V_{VIN} = 5 \ V \\ I_{VIN(MAX)} > I_{CHG} \\ I_{CHG} = 100 \ mA \\ No \ load \ on \ SYS \ pin, \ thermal \ loop \\ not \ active. \end{array}$ | -20%                       | 450                                           | 20%                        | ΑΩ   |

| I <sub>PRECHG</sub>           | Pre-charge current                                                                         |                                                                                                                                                                 | 0.07 ×<br>I <sub>CHG</sub> | 0.10 ×<br>I <sub>CHG</sub>                    | 0.15 ×<br>I <sub>CHG</sub> | mA   |

| I <sub>TERM</sub>             | Charge current value for termination detection threshold                                   | I <sub>CHG</sub> = 100 mA                                                                                                                                       | 7                          | 10                                            | 15                         | mA   |

| V <sub>RCH</sub>              | Recharge detection threshold                                                               | $\begin{array}{c} V_{BAT} \text{ below nominal charger voltage,} \\ V_{BAT(REG)} \end{array}$                                                                   | 55                         | 100                                           | 170                        | mV   |

| I <sub>BAT(DET)</sub>         | Sink current for battery detection                                                         |                                                                                                                                                                 |                            | 1                                             |                            | mA   |

| t <sub>CHG</sub>              | Charge safety timer<br>(18000 seconds = 5 hours)                                           |                                                                                                                                                                 |                            | 18000                                         |                            | S    |

| t <sub>PRECHG</sub>           | Pre-charge timer<br>(1800 seconds = 30 minutes)                                            |                                                                                                                                                                 |                            | 1800                                          |                            | S    |

| $V_{DPPM}$                    | DPPM threshold                                                                             |                                                                                                                                                                 |                            | V <sub>BAT</sub> +<br>100 mV                  |                            | V    |

| I <sub>LEAK(nCHG)</sub>       | Leakage current for nCHG_STAT pin                                                          | V <sub>nCHG_STAT</sub> = 4.2 V<br>CHG_EN = LOW (Charger disabled)                                                                                               |                            |                                               | 100                        | nA   |

| R <sub>DSON(nCH</sub>         | On resistance for nCHG_STAT MOSFET switch                                                  |                                                                                                                                                                 |                            | 20                                            | 60                         | Ω    |

# **Electrical Characteristics (continued)**

|                               | PARAMETER                                                                      | TEST CONDITIONS                                                                                                                                                                                                                               | MIN  | TYP  | MAX  | UNIT |

|-------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>MAX(nCHG)</sub>        | Maximum input current to nCHG_STAT pin                                         |                                                                                                                                                                                                                                               |      |      | 50   | mA   |

| BATTERY (                     | CHARGER NTC MONITOR                                                            |                                                                                                                                                                                                                                               |      |      |      |      |

| I <sub>TSBIAS</sub>           | TS pin bias current                                                            |                                                                                                                                                                                                                                               |      | 75   |      | μΑ   |

| V <sub>COLD</sub>             | $0^{\circ}\text{C}$ charge threshold for $10\text{k}\Omega$ NTC $(\beta=3490)$ |                                                                                                                                                                                                                                               |      | 2100 |      | mV   |

| V <sub>HYS(COLD)</sub>        | Low temperature threshold hysteresis                                           | Battery charging and battery / NTC temperature increasing                                                                                                                                                                                     |      | 300  |      | mV   |

| V <sub>HOT</sub>              | 50°C charge threshold for 10kΩ NTC ( $β = 3490$ )                              |                                                                                                                                                                                                                                               |      | 300  |      | mV   |

| V <sub>HYS(HOT)</sub>         | High temperature threshold hysteresis                                          | Battery charging and battery / NTC temperature decreasing                                                                                                                                                                                     |      | 30   |      | mV   |

| BATTERY (                     | CHARGER THERMAL REGULATION                                                     |                                                                                                                                                                                                                                               |      |      |      |      |

| T <sub>J(REG_LO</sub><br>WER) | Charger lower thermal regulation limit                                         |                                                                                                                                                                                                                                               |      | 75   |      | °C   |

| T <sub>J(REG_UPP</sub><br>ER) | Charger upper thermal regulation limit                                         |                                                                                                                                                                                                                                               |      | 95   |      | °C   |

| $T_{J(OFF)}$                  | Charger thermal shutdown temperature                                           |                                                                                                                                                                                                                                               |      | 105  |      | °C   |

| T <sub>J(OFF-HYS)</sub>       | Charger thermal shutdown hysteresis                                            |                                                                                                                                                                                                                                               |      | 20   |      | °C   |

| LDO                           |                                                                                |                                                                                                                                                                                                                                               |      |      |      |      |

| I <sub>MAX(LDO)</sub>         | Maximum LDO output current, $V_{VLDO} = 2.2 \text{ V}$                         | $V_{SYS} = 4.2 \text{ V}$<br>$V_{VIN} = 0 \text{ V}$<br>$VLDO\_SET = 0 \text{ V}$                                                                                                                                                             | 30   |      |      | mA   |

|                               |                                                                                | $V_{SYS} = 4.2 \text{ V}$ $V_{VIN} = 0 \text{ V}$ $VLDO\_SET = V_{SYS}$                                                                                                                                                                       | 30   |      |      | mA   |

| I <sub>SC(LDO)</sub>          | Short circuit current limit                                                    |                                                                                                                                                                                                                                               | 30   |      | 100  | mA   |

| $V_{VLDO}$                    | LDO output voltage                                                             | VLDO_SET = LOW (VLDO_SET pin connected to DGND) 3.7 $V \le V_{VIN} \le 6.5 V$ $I_{LOAD(LDO)} = -10 \text{ mA}$                                                                                                                                | 2.13 | 2.2  | 2.27 | V    |

| $V_{VLDO}$                    | LDO output voltage                                                             | $\begin{aligned} & \text{VLDO\_SET} = \text{HIGH} \\ & (\text{V}_{\text{VLDO\_SET}} = \text{V}_{\text{SYS}}) \\ & 3.7 \text{ V} \leq \text{V}_{\text{VIN}} \leq 6.5 \text{ V} \\ & \text{I}_{\text{LOAD(LDO)}} = \text{-10 mA} \end{aligned}$ | 2.91 | 3.0  | 3.09 | V    |

| V <sub>DO(LDO)</sub>          | LDO Dropout voltage                                                            | $V_{VIN}$ - $V_{LDO}$ when in dropout $I_{LOAD(LDO)}$ = -10 mA                                                                                                                                                                                |      |      | 200  | mV   |

|                               | Line regulation                                                                | $3.7 \text{ V} \le \text{V}_{\text{VIN}} \le 6.5 \text{ V}$<br>$\text{I}_{\text{LOAD(LDO)}} = -10 \text{ mA}$                                                                                                                                 | -1   |      | 1    | %    |

|                               | Load regulation                                                                | $V_{VIN} = 3.5 \text{ V}$<br>0.1 mA $\leq I_{LOAD(LDO)} \leq$ -10 mA                                                                                                                                                                          | -2   |      | 2    | %    |

| PSRR                          | Power supply rejection ratio                                                   | @20 KHz, $I_{LOAD(LDO)}$ = 10 mA<br>$V_{DO(LDO)}$ = 0.5 V<br>$C_{VLDO}$ = 10 $\mu$ F                                                                                                                                                          |      | 45   |      | dB   |

| BOOST CO                      | NVERTER                                                                        |                                                                                                                                                                                                                                               |      |      | · ·  |      |

| I <sub>Q(BST)</sub>           | Boost operating quiescent current                                              | Boost Enabled, BST_EN = High $I_{OUT(BST)} = 0$ mA (boost is not switching) $V_{BAT} = 3.6$ V                                                                                                                                                 |      | 2    | 4.5  | μА   |

| R <sub>DSON(BST)</sub>        | Boost MOSFET switch on-resistance                                              | $V_{IN(BST)} = 2.5 \text{ V}$<br>$I_{SW(MAIN)} = 200 \text{ mA}$                                                                                                                                                                              |      | 0.8  | 1.2  | Ω    |

ZHCS357-JUNE 2011 www.ti.com.cn

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                               | PARAMETER                                                                                                           | TEST CONDITIONS                                                                                                                                                | MIN  | TYP  | MAX  | UNIT |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>LKG(BST_S</sub><br>W)  | Leakage into BST_SW pin (includes leakage into analog h-bridge switches)                                            | BST_EN signal = LOW (Boost disabled) V <sub>BST_SW</sub> = 4.2 V No load on BST_OUT pin                                                                        |      |      | 90   | nA   |

| I <sub>SWLIM(BST)</sub>       | Boost MOSFET switch current limit                                                                                   |                                                                                                                                                                | 100  | 150  | 200  | mA   |

| V <sub>DIODE(BST</sub> )      | Voltage across integrated boost diode during normal operation                                                       | $\begin{array}{l} \text{BST\_EN signal} = \text{HIGH} \\ \text{V}_{\text{BST\_SW}} = 16.0 \text{ V} \\ \text{I}_{\text{BST\_OUT}} = \text{- 2 mA} \end{array}$ |      |      | 1.0  | V    |

| V <sub>REF(BST)</sub>         | Boost reference voltage on BST_FB pin                                                                               |                                                                                                                                                                | 1.17 | 1.2  | 1.23 | V    |

| V <sub>REFHYS(BS</sub>        | Boost reference voltage hysteresis on BST_FB pin                                                                    |                                                                                                                                                                | 2    | 2.5  | 3.2  | %    |

| T <sub>ON(BST)</sub>          | Maximum on time detection threshold                                                                                 |                                                                                                                                                                | 5    | 6.5  | 8    | μs   |

| T <sub>OFF(BST)</sub>         | Minimum off time detection threshold                                                                                |                                                                                                                                                                | 1.4  | 1.75 | 2.1  | μs   |

| T <sub>SHUT(BST)</sub>        | Boost thermal shutdown threshold                                                                                    |                                                                                                                                                                |      | 105  |      | °C   |

| T <sub>SHUT</sub> -           | Boost thermal shutdown threshold hysteresis                                                                         |                                                                                                                                                                |      | 20   |      | °C   |

| FULL H-BR                     | IDGE ANALOG SWITCHES                                                                                                |                                                                                                                                                                | 1    |      |      |      |

| I <sub>Q(HSW)</sub>           | Operating quiescent current for h-bridge switches                                                                   |                                                                                                                                                                |      |      | 5    | μA   |

| R <sub>DSON(HSW</sub>         | H-bridge switches on resistance                                                                                     |                                                                                                                                                                |      | 20   | 40   | Ω    |

| T <sub>DELAY(HS</sub> W-H)    | H-bridge switch propagation delay, input switched from low to high state.                                           | $V_{HBxy} = 0 \ V \rightarrow V_{VLDO}$                                                                                                                        |      | 100  |      | ns   |

| T <sub>DELAY(HS</sub><br>W-L) | H-bridge switch propagation delay, input switched from high to low state.                                           | $V_{HBxy} = V_{VLDO} \rightarrow 0 V$                                                                                                                          |      | 100  |      | ns   |

| POWER MA                      | NAGEMENT CORE CONTROLLER                                                                                            |                                                                                                                                                                |      |      |      |      |

| V <sub>IL(PMIC)</sub>         | Low logic level for logic signals on<br>power management core<br>(BST_EN, CHG_EN, SLEEP, HBR1,<br>HBR2, HBL1, HBL2) | IO logic level decreasing: $V_{SYS} \rightarrow 0 \text{ V}$<br>$I_{IN} = 1 \text{ mA}$                                                                        |      |      | 0.4  | V    |

| V <sub>IH(PMIC)</sub>         | High logic level for signals on power<br>management core<br>(BST_EN, CHG_EN, SLEEP, HBR1,<br>HBR2, HBL1, HBL2)      | IO logic level increasing: 0 V $\rightarrow$ V <sub>SYS</sub> I <sub>IN</sub> = 1 mA                                                                           | 1.2  |      |      | V    |

| V <sub>GOOD(LDO</sub>         | Power fault detection threshold                                                                                     | V <sub>VLDO</sub> decreasing                                                                                                                                   |      |      | 1.96 | V    |

| V <sub>GOOD_HYS</sub>         | Power fault detection hysteresis                                                                                    | V <sub>VLDO</sub> increasing                                                                                                                                   |      | 50   |      | mV   |

| V <sub>BATCOMP</sub>          | COMP pin voltage (scaled down battery voltage)                                                                      | $V_{BAT} = 4.2 \text{ V}$<br>$V_{VLDO} = 2.2 \text{ V}$                                                                                                        |      | 1.85 |      | V    |

|                               |                                                                                                                     | $V_{BAT} = 2.5 \text{ V}$<br>$V_{VLDO} = 2.2 \text{ V}$                                                                                                        |      | 1.10 |      | V    |

|                               |                                                                                                                     | $V_{BAT} = 4.2 \text{ V}$<br>$V_{VLDO} = 3.0 \text{ V}$                                                                                                        |      | 1.90 |      | V    |

|                               |                                                                                                                     | $V_{BAT} = 3.3 \text{ V}$<br>$V_{VLDO} = 3.0 \text{ V}$                                                                                                        |      | 1.50 |      | ٧    |

## 2.6 System Operation

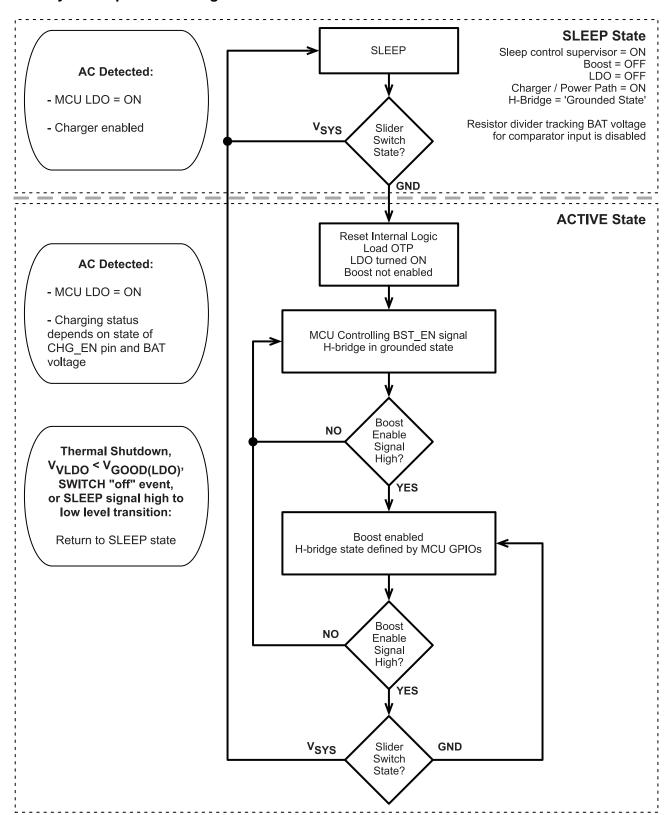

The system must complete the power up routine before it enters normal operating mode. The specific system operation depends on the setting defined by the state of the SW\_SEL pin. The details of the system operation for each configuration of the SW\_SEL pin are contained in this section.

#### 2.6.1 System Power Up

图 2-1. System Power Up State Diagram

ZHCS357 – JUNE 2011 www.ti.com.cn

# 2.6.2 System Operation Using Push Button Switch

2-2. Push Button State Diagram

NSTRUMENTS

## 2.6.3 System Operation Using Slider Switch

2-3. System Operation Using Slider Switch

ZHCS357-JUNE 2011 www.ti.com.cn

#### 2.7 **Linear Charger Operation**

This device has an integrated Li-lon battery charger and system power path management feature targeted at space-limited portable applications. The architecture powers the system while simultaneously and independently charging the battery. This feature reduces the number of charge and discharge cycles on the battery, allows for proper charge termination, and enables the system to run with a defective or absent battery pack. It also allows instant system turn-on even with a totally discharged battery.

The input power source for charging the battery and running the system can be an AC adapter or USB port connected to the VIN pin as long as the input meets the device operating conditions outlined in this datasheet. The power-path management feature automatically reduces the charging current if the system load increases. Note that the charger input, VIN, has voltage protection up to 28 V.

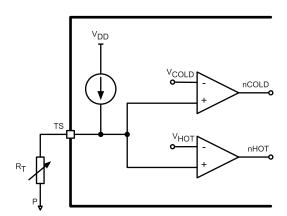

#### 2.7.1 Battery and TS Detection

To detect and determine between a good or damaged battery, the device checks for a short circuit on the BAT pin by sourcing I<sub>BAT(SC)</sub> to the battery and monitoring the voltage on the BAT pin. While sourcing this current if the BAT pin voltage exceeds V<sub>BAT(SC)</sub>, a battery has been detected. If the voltage stays below the V<sub>BAT(SC)</sub> level, the battery is presumed to be damaged and not safe to charge.

The device will also check for the presence of a 10 kΩ NTC thermistor attached to the TS pin of the device. The check for the NTC thermistor on the TS pin is done much like the battery detection feature described previously. The voltage on the TS pin is compared against a defined level and if it is found to be above the threshold, the NTC thermistor is assumed to be disconnected or not used in the system. To reduce the system guiescent current, the NTC thermistor temperature sensing function is only enabled when the device is charging and when the thermistor has been detected.

§ 2-4. Thermistor Detection and Circuit

#### 2.7.2 Battery Charging

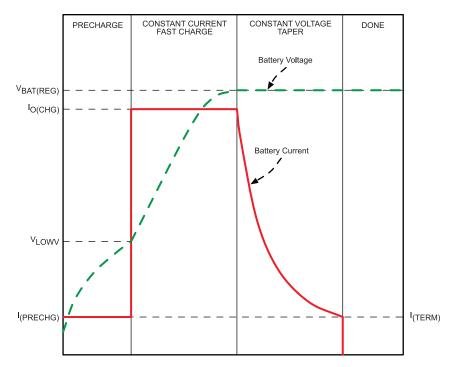

The battery is charged in three phases: conditioning pre-charge, constant-current fast charge (current regulation), and a constant-voltage tapering (voltage regulation). In all charge phases, an internal control loop monitors the IC junction temperature and reduces the charge current if an internal temperature threshold is exceeded.

2-5 shows what happens in each of the three charge phases:

图 2-5. Battery Charge Phases

In the pre-charge phase, the battery is charged with the pre-charge current that is scaled to be 10% of the fast-charge current set by the resistor connected to the ISET pin. Once the battery voltage crosses the  $V_{LOWV}$  threshold, the battery is charged with the fast-charge current ( $I_{CHG}$ ). As the battery voltage reaches  $V_{BAT(REG)}$ , the battery is held at a constant voltage of  $V_{BAT(REG)}$  and the charge current tapers off as the battery approaches full charge. When the battery current reaches  $I_{TERM}$ , the charger indicates charging is done by making the nCHG\_STAT pin high impedance. Note that termination detection is disabled whenever the charge rate is reduced from the set point because of the actions of the thermal loop, the DPM loop, or the  $V_{IN(LOWV)}$  loop.

## 2.7.2.1 Pre-charge

The value for the pre-charge current is set to be 10% of the charge current that is set by the external resistor,  $R_{ISET}$ . Pre-charge current is scaled to lower currents when the charger is in thermal regulation.

#### 2.7.2.2 Charge Termination

In the fast charge state, once  $V_{BAT} \ge V_{BAT(REG)}$ , the charger enters constant voltage mode. In constant voltage mode, the charge current will taper until termination when the charge current falls below the  $I_{(TERM)}$  threshold (typically 10% of the programmed fast charge current). Termination current is not scaled when the charger is in thermal regulation. When the charging is terminated, the nCHG\_STAT pin will be high impedance (effectively turning off any LED that is connected to this pin).

#### 2.7.2.3 Recharge

Once a charge cycle is complete and termination is reached, the battery voltage is monitored. If  $V_{BAT} < V_{BAT(REG)} - V_{RCH}$ , the device determines if the battery has been removed. If the battery is still present, then the recharge cycle begins and will end when  $V_{BAT} \ge V_{BAT(REG)}$ .

# 2.7.2.4 Charge Timers

The charger in this device has internal safety timers for the pre-charge and fast charge phases to prevent potential damage to either the battery or the system. The default values for these timers are found as follows: Pre-charge timer = 0.5 hours (30 minutes) and Fast charge timer = 5 hours (300 minutes).

ZHCS357-JUNE 2011 www.ti.com.cn

During the fast charge phase, the following events may increase the timer durations:

- 1. The system load current activates the DPM loop which reduces the available charging current

- 2. The input current is reduced because the input voltage has fallen to  $V_{\text{IN(LOW)}}$

- 3. The device has entered thermal regulation because the IC junction temperature has exceeded T<sub>J(REG)</sub>

During each of these events, the internal timers are slowed down proportionately to the reduction in charging current.

If the pre-charge timer expires before the battery voltage reaches  $V_{LOWV}$ , the charger indicates a fault condition.

# 2.7.3 Charger Status (nCHG\_STAT Pin)

The nCHG\_STAT pin is used to indicate the charger status by an externally connected resistor and LED circuit. The pin is an open drain input and the internal switch is controlled by the logic inside of the charger. This pin may also be connected to a GPIO of the system MCU to indicate charging status. The table below details the status of the nCHG\_STAT pin for various operating states of the charger.

| Charging Status                               | nCHG_STAT FET / LED |

|-----------------------------------------------|---------------------|

| Pre-charge / Fast Charge / Charge Termination | ON                  |

| Recharge                                      | OFF                 |

| OVP                                           | OFF                 |

| SLEED                                         | OFF                 |

表 2-1. nCHG\_STAT Functionality

# 2.8 LDO Operation

The power management core has a low dropout linear regulator (LDO) with variable output voltage capability. This LDO is used for supplying the microcontroller and may be used to supply either an external IR or RF module, depending on system requirements. The LDO can supply a continuous current of up to 30 mA.

The output voltage ( $V_{VLDO}$ ) of the LDO is set by the state of the VLDO\_SET pin. See  $\frac{1}{8}$  2-2 for details on setting the LDO output voltage.

| 丰  | 2-2  | <b>VLDO</b> | SET | Fun | ction | ality |

|----|------|-------------|-----|-----|-------|-------|

| 1X | Z-Z. | VLDU        | SEI | run | GUUI  | alitv |

| VLDO_SET State                          | VLDO Output Voltage (V <sub>VLDO</sub> ) |

|-----------------------------------------|------------------------------------------|

| Low (VLDO_SET < V <sub>IL(PMIC)</sub> ) | 2.2 V                                    |

| High (VLDO_SET > $V_{IH(PMIC)}$ )       | 3.0 V                                    |

#### 2.8.1 LDO Internal Current Limit

The internal current limit feature helps to protect the LDO regulator during fault conditions. During current limit, the output sources a fixed amount of current that is defined in the electrical specification table. The voltage on the output in this stage can not be regulated and will be  $V_{OUT} = I_{LIMIT} \times R_{LOAD}$ . The pass transistor integrated into the LDO will dissipate power,  $(V_{IN} - V_{OUT}) \times I_{LIMIT}$ , until the device enters thermal shutdown. In thermal shutdown the device will enter the "SLEEP / POWER OFF" state which means that the LDO will then be disabled and shut off.

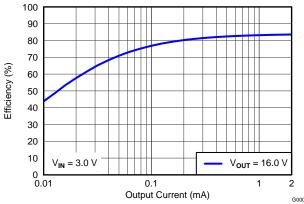

## 2.9 Boost Converter Operation

The boost converter in this device is designed for the load of active shutter 3D glasses. This load is typically a light load where the average current is 2 mA or lower and the peak current out of a battery is limited in operation. This asynchronous boost converter operates with a minimum off time / maximum on time for the integrated low side switch, these values are specified in the electrical characteristics table of this datasheet.

The peak output voltage from the boost converter is adjustable and set by using an external resistor divider connected between BST\_OUT, the BST\_FB pin, and ground. The peak output voltage is set by choosing resistors for the feedback network such that the voltage on the BST\_FB pin is  $V_{REF(BST)} = 1.2 \text{ V}$ . See  $\ddagger$  3.3 for more information on calculating resistance values for this feedback network.

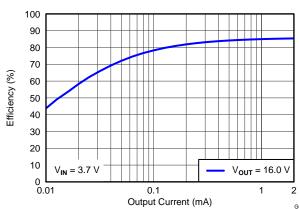

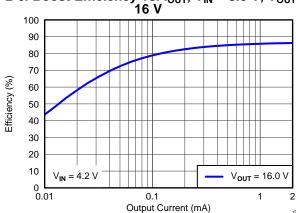

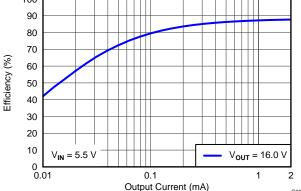

The efficiency curves for various input voltages over the typical 3D glasses load range (2 mA and lower) are shown below. All curves are for a target V<sub>OUT</sub> of 16 V. For output voltages less than 16 V, a higher efficiency at each operating input voltage should be expected. Note that efficiency is dependent upon the external boost feedback network resistances, the inductor used, and the type of load connected.

$\boxtimes$  2-6. Boost Efficiency vs.  $I_{OUT}$ ,  $V_{IN}$  = 3.0 V,  $V_{OUT}$  =

2-7. Boost Efficiency vs. I<sub>OUT</sub>, V<sub>IN</sub> = 3.7 V, V<sub>OUT</sub> = 16 V

$\boxtimes$  2-8. Boost Efficiency vs.  $I_{OUT}$ ,  $V_{IN}$  = 4.2 V,  $V_{OUT}$  =

$\boxtimes$  2-9. Boost Efficiency vs.  $I_{OUT}$ ,  $V_{IN}$  = 5.5 V,  $V_{OUT}$  = 16 V

#### 2.9.1 Boost Thermal Shutdown

An internal thermal shutdown mode is implemented in the boost converter that shuts down the device if the typical junction temperature of 105°C is exceeded. If the device is in thermal shutdown mode, the main switch of the boost is open and the device enters the "SLEEP / POWER OFF" state.

ZHCS357-JUNE 2011 www.ti.com.cn

#### 2.9.2 Boost Load Disconnect

When the boost is disabled (BST\_EN = LOW), the H-bridge is automatically placed into the OFF state. In the OFF state the high side H-bridge switches are open and the low side switches of the H-bridge are closed. The OFF state grounds and discharges the load, potentially prolonging the life of the LC shutters by eliminating any DC content (see † 2.10.1 for more information regarding the H-bridge states). The disconnection of the load is done with the H-Bridge and can be seen in the next figure (§ 2-10).

图 2-10. Boost Load Disconnect

An advantage to this topology for disconnecting the load is that the boost output capacitor is charged to approximately the SYS voltage level, specifically  $V_{SYS}$  -  $V_{DIODE(BST)}$ , when the boost is disabled. This design ensures that there is not a large in-rush current into the boost output capacitor when the boost is enabled. The boost operation efficiency is also increased because there is no load disconnect switch in the boost output path, such a switch would decrease efficiency because of the resistance that it would introduce.

#### 2.10 Full H-Bridge Analog Switches

The TPS65735 has two integrated full H-bridge analog switches that can be connected to GPIOs of a host microcontroller. There is an internal level shifter that takes care of the input signals to the H-Bridge switches.

#### 2.10.1 H-Bridge Switch Control

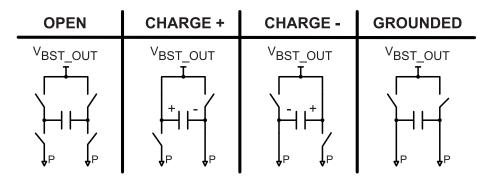

The H-Bridge switches are controlled by an external microcontroller for system operation - specifically to control charge polarity on the LCD shutters. Depending on the state of the signals from the microcontroller, the H-Bridge will be put into 4 different states. These states are:

- · OPEN: All Switches Opened

- CHARGE+: Boost Output Voltage Present on Pins LCLP or LCRP

- CHARGE-: Boost Output Voltage Present on Pins LCLN or LCRN

- GROUNDED: High Side Switches are Opened and Low Side Switches are Closed

If CHARGE+ state is followed by the CHARGE- state, the voltage across the capacitor connected to the H-Bridge output terminals will be reversed. The system is automatically put into the GROUNDED state when the boost is disabled by the BST\_EN pin - for more details see † 2.6.

| HBx2 [HBL2 & HBR2] | HBx1 [HBL1 & HBR1] | H-Bridge State |

|--------------------|--------------------|----------------|

| 0                  | 0                  | OPEN           |

| 0                  | 1                  | CHARGE +       |

| 1                  | 0                  | CHARGE -       |

| 1                  | 1                  | GROUNDED       |

图 2-11. H-Bridge States

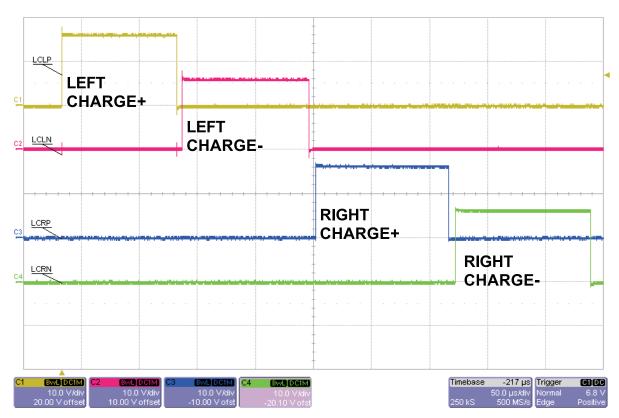

图 2-12. H-Bridge States from Oscilloscope

ZHCS357-JUNE 2011 www.ti.com.cn

#### 2.11 Power Management Core Control

Various functions of the power management core can be controlled by GPIOs of an external MCU or by setting the default state by connecting these function pins to a logic high or low level on the PCB.

#### 2.11.1 SLEEP / Power Control Pin Function

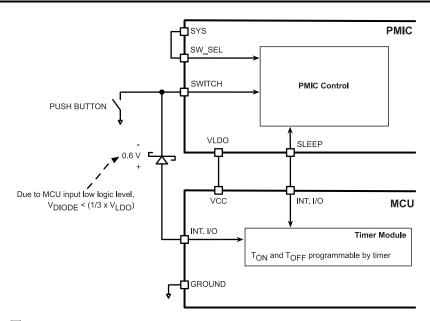

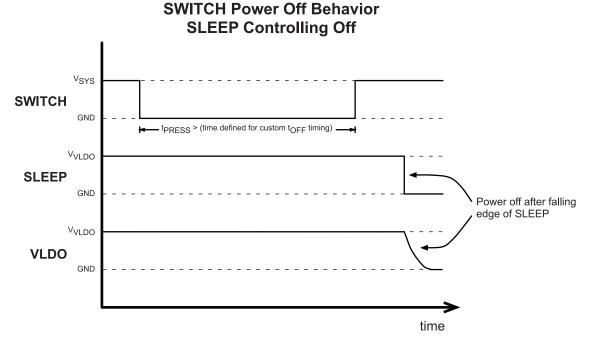

The internal SLEEP signal between the power management device and the MSP430 can be used to control the power down behavior of the device. This has multiple practical applications such as a watchdog implementation for the communication between the sender (TV) and the 3D glasses (receiver) or different required system on and off times; typically when the push-button press timing for an off event is a few seconds in length, programmable by software in the system MCU.

If there is a requirement that the push-button press for system on and off events are different, the SLEEP signal must be set to a logic high value ( $V_{SIFEP} > V_{IH(PMIC)}$ ) upon system startup. This implementation allows the device to power down the system on the falling edge of the SLEEP signal (when:  $V_{SLEEP} < V_{IL(PMIC)}$ ).

图 2-13. SLEEP Signal to Force System Power Off

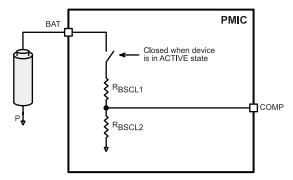

#### 2.11.2 COMP Pin Functionality

The COMP pin is used to output a scaled down voltage level related to the battery voltage for input to a comparator of a microcontroller. Applications for this COMP feature could be to generate an interrupt on the microcontroller when battery voltage drops under a threshold and the device can then be shut down or indicate to the end user with an LED that the battery requires charging.

图 2-14. COMP Pin Internal Connection

# 表 2-4. Scaling Resistors for COMP Pin Function (V<sub>VLDO</sub> = 2.2 V)

| Scaling Resistors for COMP Pin Function | Value   |

|-----------------------------------------|---------|

| R <sub>BSCL1</sub>                      | 3.0 ΜΩ  |

| R <sub>BSCL2</sub>                      | 2.36 ΜΩ |

# 表 2-5. Scaling Resistors for COMP Pin Function (V<sub>VLDO</sub> = 3.0 V)

| Scaling Resistors for COMP Pin Function | Value   |

|-----------------------------------------|---------|

| R <sub>BSCL1</sub>                      | 3.0 ΜΩ  |

| R <sub>BSCL2</sub>                      | 2.48 ΜΩ |

Using the designed values in  $\frac{1}{8}$  2-4 or  $\frac{1}{8}$  2-5, the voltage on the COMP pin will be:  $V_{COMP} = 0.5 \times V_{VLDO} + 300$  mV. This assures that the COMP pin voltage will be close to half of the LDO output voltage plus the LDO dropout voltage of the device. The COMP pin can also be used as the input to an ADC channel of an external microcontroller if greater accuracy or more functionality is desired than a simple comparison.

# 2.11.3 SW\_SEL Pin Functionality

The SW\_SEL pin is used to select what type of switch is connected to the SWITCH pin of the device. Selection between a push-button and a slider switch can be made based on the state of this pin.

表 2-6. SW\_SEL Settings

| SW_SEL State                                                                      | Type of Switch Selected |

|-----------------------------------------------------------------------------------|-------------------------|

|                                                                                   | Slider Switch           |

| $\begin{array}{c} \text{High} \\ (V_{SW\_SEL} > V_{\text{IH(PMIC)}}) \end{array}$ | Push-button             |

When the push button switch type is selected, the device will debounce the SWITCH input with a 32 ms timer for both the ON and OFF events and either power on or off the device. Using the push-button switch function, the ON and OFF timings are equal;  $t_{ON} = t_{OFF}$ . If the system requirements are such that the on and off timings should be different,  $t_{ON} \neq t_{OFF}$ , then refer to the following section for the correct system setup: †3.4. When the slider switch operation is selected, the SWITCH pin must be externally pulled up to the SYS voltage with a resistor and the output connected to the slider switch. When the SWITCH pin is pulled to ground, the device will turn on and enter the power up sequence.

#### 2.11.4 SWITCH Pin

The SWITCH pin behavior is defined by the SW\_SEL pin († 2.11.3) which defines the type of switch that is connected to the system; either a slider switch or push-button.

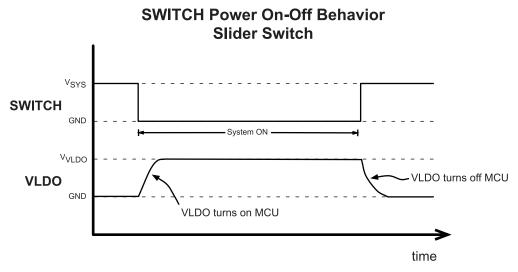

#### 2.11.5 Slider Switch Behavior

If a slider switch is connected in the system then the system power state and VLDO output (which can power an external MCU) is defined by the state of the slider switch. If the slider is in the "off" position than the SWITCH pin should be connected to the SYS pin. If the slider is in the "on" position than the SWITCH pin should be connected to ground. 2-15 details the system operation using the slider switch configuration.

ZHCS357-JUNE 2011 www.ti.com.cn

图 2-15. SWITCH, Slider Power On-Off Behavior

#### 2.11.6 Push-Button Switch Behavior

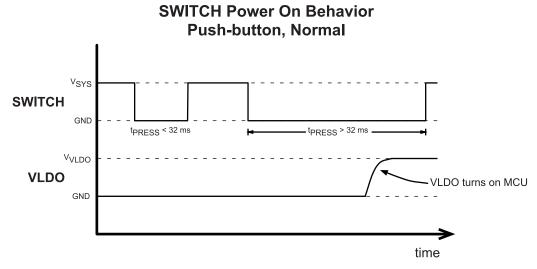

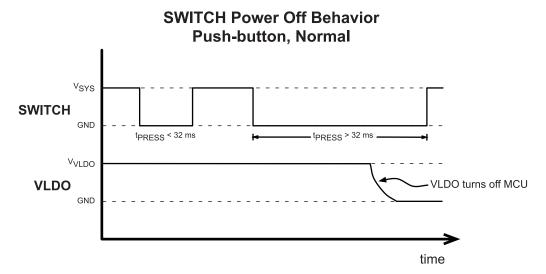

The system is powered on or off by a push-button press after a press that is greater than 32 ms. The following figures (图 2-16 and 图 2-17) show the system behavior and the expected VLDO output during the normal push-button operation where the ON and OFF press timings are the same value,  $t_{ON} = t_{OFF}$ .

图 2-16. SWITCH, Push-button Power On Behavior

图 2-17. SWITCH, Push-button Power Off Behavior

ZHCS357-JUNE 2011 www.ti.com.cn

# TEXAS INSTRUMENTS

#### 3 APPLICATION INFORMATION

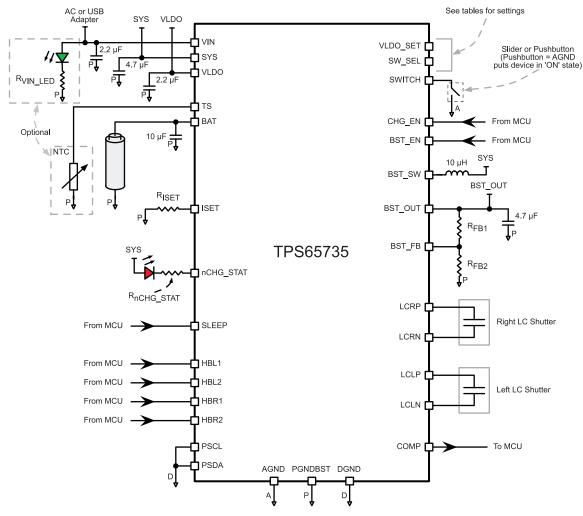

## 3.1 Applications Schematic

图 3-1. TPS65735 Applications Schematic

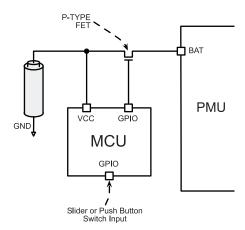

# 3.2 Reducing System Quiescent Current (I<sub>o</sub>)