**TPS657095**

ZHCSE51 - SEPTEMBER 2015

## TPS657095 用于嵌入式摄像头模块的电源管理单元 (PMU)

## 特性

- 2 个 100mA 低压降稳压器 (LDO)

- 输出电压精度为 ±1.5%

- V<sub>IN</sub> 范围为 3.7V 至 6V

- 具有 PWM 调光功能的 LED 驱动器

- 1 GPO

- 1个GPIO

- I<sup>2</sup>C™ 接口

- 4KB 用户一次性可编程 (OTP) 存储器

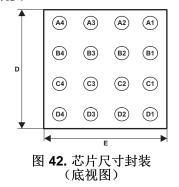

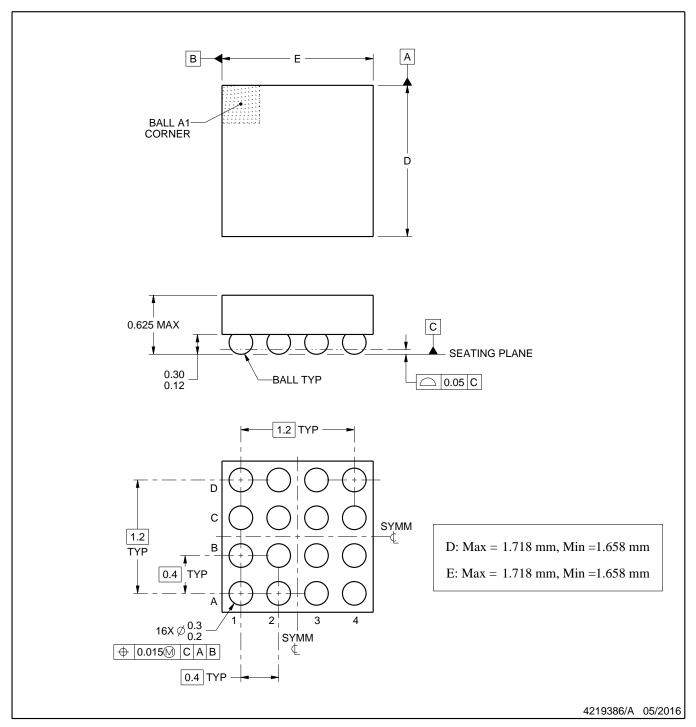

- 采用 16 焊球 0.4mm 间距芯片尺寸球栅阵列封装 (DSBGA)

## 2 应用

- 笔记本电脑

- 可拆卸平板电脑

- 平板电脑

- 监视器

- 智能手机

## 3 说明

TPS657095 是面向嵌入式摄像头模块或其他便携式低 功耗消费类终端设备的电源管理单元。 其包含两个由 I<sup>2</sup>C™ 接口使能的 LDO、一个用于驱动单个发光二极 管 (LED) 的脉宽调制 (PWM) 可调光电流阱、一个通用 输出 (GPO)、一个可编程时钟发生器和 4KB 的用户 OTP 存储器。 如果输入电压电源低于内部欠压锁定 值,则该器件将被禁止运行。

此器件采用 16 焊球芯片尺寸球栅阵列封装 (DSBGA), 焊球间距为 0.4mm。

#### 器件信息(1)

|           | BB 11 1B 10. |                 |

|-----------|--------------|-----------------|

| 器件型号      | 封装           | 封装尺寸 (标称值)      |

| TPS657095 | DSBGA (16)   | 1.70mm x 1.70mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

## 目录

| 1 | 特性 1                                 |    | 7.5 Programming                | 18 |

|---|--------------------------------------|----|--------------------------------|----|

| 2 | 应用 1                                 |    | 7.6 Register Map               | 22 |

| 3 | 说明 1                                 | 8  | Application and Implementation | 32 |

| 4 | 修订历史记录 2                             |    | 8.1 Application Information    | 32 |

| 5 | Pin Configuration and Functions      |    | 8.2 Typical Application        | 32 |

| 6 | Specifications                       | 9  | Power Supply Recommendations   | 35 |

| Ū | 6.1 Absolute Maximum Ratings         | 10 | Layout                         | 35 |

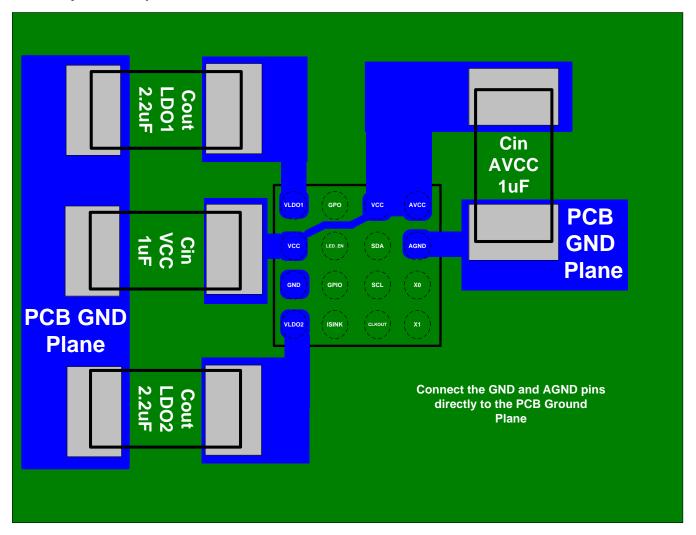

|   | 6.2 ESD Ratings                      |    | 10.1 Layout Guidelines         | 35 |

|   | 6.3 Recommended Operating Conditions |    | 10.2 Layout Example            | 35 |

|   | 6.4 Thermal Information              | 11 | 器件和文档支持                        | 36 |

|   | 6.5 Electrical Characteristics 5     |    | 11.1 器件支持                      | 36 |

|   | 6.6 Timing Requirements8             |    | 11.2 社区资源                      | 36 |

|   | 6.7 Typical Characteristics9         |    | 11.3 商标                        | 36 |

| 7 | Detailed Description 10              |    | 11.4 静电放电警告                    | 36 |

| - | 7.1 Overview                         |    | 11.5 Glossary                  | 36 |

|   | 7.2 Functional Block Diagram         | 12 | 机械、封装和可订购信息                    | 36 |

|   | 7.3 Feature Description              |    | 12.1 封装概要                      | 36 |

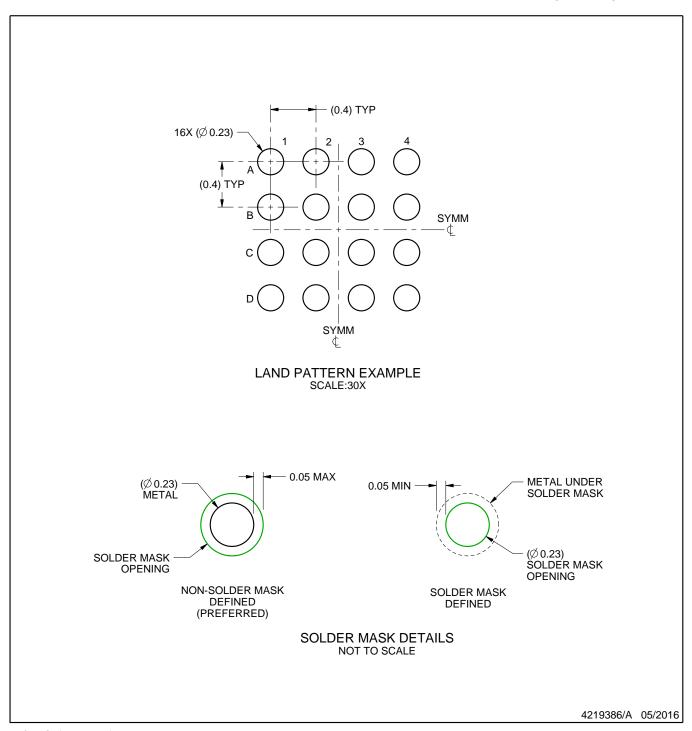

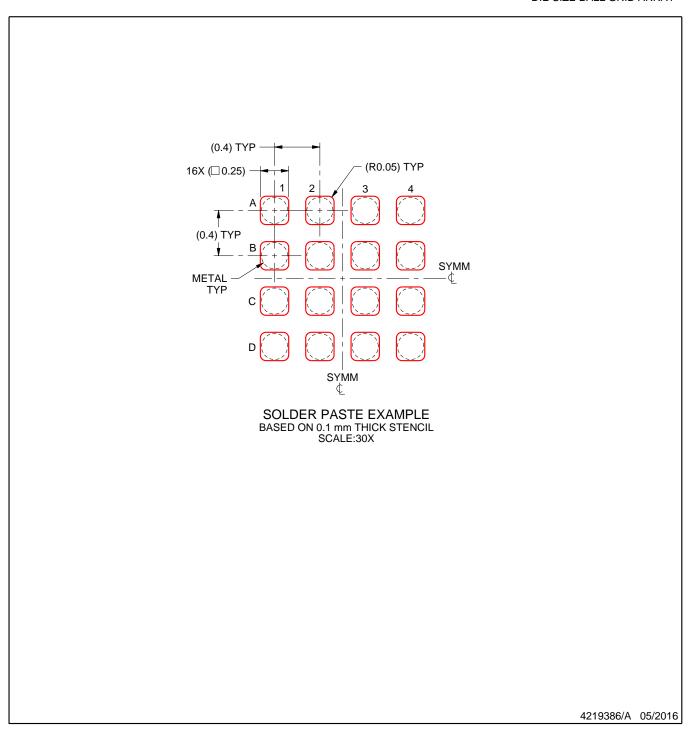

|   | 7.4 Device Functional Modes          |    | 12.2 芯片尺寸封装尺寸                  | 37 |

|   |                                      |    |                                |    |

## 4 修订历史记录

| 日期         | 修订版本 | 注释    |

|------------|------|-------|

| 2015 年 9 月 | *    | 首次发布。 |

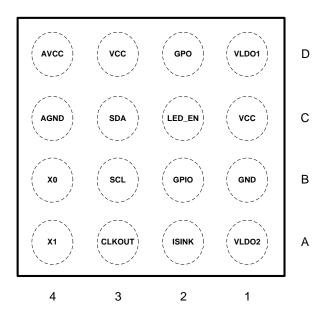

## **5 Pin Configuration and Functions**

## YFF Package 16-Pin DSBGA Top View

#### **Pin Functions**

| P           | IN                                                                                      |     |                                                                                                                     |  |  |

|-------------|-----------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NUMBER |                                                                                         | 1/0 | DESCRIPTION                                                                                                         |  |  |

| VCC         | C1, D3                                                                                  | I   | Supply Input. Connect a 1uF cap close to the C1 pin. Connect pins C1 and D3 together externally.                    |  |  |

| GND         | B1                                                                                      | ı   | Ground connection (main device ground - connect to ground plane on PCB)                                             |  |  |

| AVCC        | D4                                                                                      | I   | Analog Supply Input. Connect a 1uF cap close to pin. The D4 pin must be connected externally to the D3 and C1 pins. |  |  |

| AGND        | ND C4 I Analog Ground connection (device quiet ground - connect to ground plane on PCB) |     |                                                                                                                     |  |  |

| VLDO1       | D1                                                                                      | 0   | Output voltage from LDO1                                                                                            |  |  |

| VLDO2       | A1                                                                                      | 0   | Output voltage from LDO2                                                                                            |  |  |

| ISINK       | A2                                                                                      | 0   | Open drain current sink; connect to the cathode of LED                                                              |  |  |

| GPO         | D2                                                                                      | 0   | general purpose output                                                                                              |  |  |

| LED_EN      | C2                                                                                      | ı   | LED enable pin ( 0 = disabled, 1 = enabled)                                                                         |  |  |

| GPIO        | B2                                                                                      | I   | General Purpose Input/Output (see GPIO_CTRL Register for details) As an input, it is used to enable LDO2            |  |  |

| SCL         | В3                                                                                      | ı   | clock input for the I2C compatible interface                                                                        |  |  |

| SDA         | C3                                                                                      | I/O | data input for the I2C compatible interface                                                                         |  |  |

| XO          | B4                                                                                      | ı   | connection for external crystal to clock generator (input of amplifier)                                             |  |  |

| XI          | A4                                                                                      | 1   | connection for external crystal to clock generator (output of amplifier)                                            |  |  |

| CLKOUT      | А3                                                                                      | 0   | clock output                                                                                                        |  |  |

# TEXAS INSTRUMENTS

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|             |                                                                 | MIN  | MAX            | UNIT |

|-------------|-----------------------------------------------------------------|------|----------------|------|

| Maximum ju  | All pins except GND pin with respect to AGND                    | -0.3 | 7              | V    |

| Voltage     | GPIO and GPO pull-up voltage if configured as open drain output | -0.3 | $V_{CC} + 0.3$ | V    |

|             | Pin VLDO1 and VLDO2 with respect to AGND                        | -0.3 | 3.6            | V    |

|             | VLDO1, VLDO2, VCC                                               |      | 200            | mA   |

| Current     | GND, ISINK, GPIO, GPO                                           |      | 50             | mA   |

|             | All other pins                                                  |      | 3              | mA   |

| Operating f | ree-air temperature, T <sub>A</sub>                             | -40  | 85             | °C   |

| Maximum j   | unction temperature, T <sub>J</sub>                             |      | 125            | °C   |

| Storage ter | nperature range, T <sub>stg</sub>                               | -65  | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                                  |                         |                                                                     | VALUE | UNIT |

|----------------------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| M                                | Clastractatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | 2000  | V    |

| V <sub>(ESD)</sub> Electrostatic | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 (2) | 500   | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                        |                                                             | MIN | NOM MAX | UNIT |

|------------------------|-------------------------------------------------------------|-----|---------|------|

| VCC /AVCC              | Input voltage range                                         | 3.7 | 6       | V    |

| C <sub>VCC</sub>       | Input capacitor at VCC                                      | 1   |         | μF   |

| C <sub>AVCC</sub>      | Input capacitor at AVCC                                     | 1   |         | μF   |

| $V_{LDOx}$             | Output voltage range for LDO1 and LDO2                      | 0.8 | 3.3     | V    |

| I <sub>LDO</sub>       | Output current at LDO1 or LDO2                              |     | 75      | mA   |

| C <sub>OUTLDO1/2</sub> | Output capacitance at V <sub>LDO1</sub> , V <sub>LDO2</sub> | 2.2 | 6.8     | μF   |

| LED_EN                 | Voltage range                                               | 1.3 | 6       | V    |

| GPIO                   | Voltage range (configured as an input)                      | 1.3 | 3.3     | V    |

| T <sub>A</sub>         | Operating ambient temperature                               | -40 | 85      | °C   |

| TJ                     | Operating junction temperature                              | -40 | 125     | °C   |

#### 6.4 Thermal Information

|                      |                                              | TPS657095   |       |

|----------------------|----------------------------------------------|-------------|-------|

|                      | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | UNIT  |

|                      |                                              | 16 PINS     |       |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 78.2        |       |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.6         |       |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 13.2        | °C/W  |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 2.5         | *C/VV |

| ΨЈВ                  | Junction-to-board characterization parameter | 13          |       |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | n/a         |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.5 Electrical Characteristics

Unless otherwise noted: VCC = AVCC = 5V,  $C_{VCC}$  = 1 $\mu$ F;  $C_{OUTLDOx}$ = 2.2 $\mu$ F,  $T_A$  = -40°C to 85°C

|                      | PARAMETER                                         | TEST CONDITIONS                                                                                                                                                                                                                       | MIN  | TYP                         | MAX             | UNIT |

|----------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------|-----------------|------|

| SUPPL                | Y CURRENT                                         |                                                                                                                                                                                                                                       |      |                             | •               |      |

| V <sub>CC</sub> ,    | Complement                                        | During normal operation                                                                                                                                                                                                               | 3.7  |                             | 6               | V    |

| AV <sub>CC</sub>     | Supply voltage                                    | During programming (writing) of OTP memory                                                                                                                                                                                            | -5%  | 5                           | +5%             | V    |

|                      |                                                   | LDO1 disabled LDO2 disabled No I <sup>2</sup> C communications LED_EN = 0 CLKout_EN = 0 24MHz crystal disabled                                                                                                                        |      | 25                          | 30              | μА   |

|                      |                                                   | LDO1 disabled LDO2 enabled, I <sub>OUT(LDO2)</sub> = 0 mA No I <sup>2</sup> C communications LED_EN = 0 CLKout_EN = 0 24MHz crystal disabled                                                                                          |      | 40                          | 55              | uA   |

|                      |                                                   | LDO1 enabled, I <sub>OUT(LDO1)</sub> = 0 mA<br>LDO2 disabled<br>No I <sup>2</sup> C communications<br>LED_EN = 0<br>CLKout_EN = 0<br>24MHz crystal disabled                                                                           |      | 40                          | 55              | μА   |

| I <sub>Q</sub>       | Operating quiescent current                       | LDO1 enabled, I <sub>OUT(LDO1)</sub> = 0 mA<br>LDO2 enabled, I <sub>OUT(LDO2)</sub> = 0 mA<br>No I <sup>2</sup> C communications<br>LED_EN = 0<br>CLKout_EN = 0<br>24MHz crystal disabled                                             |      | 60                          | 80              | μΑ   |

|                      |                                                   | LDO1 enabled, $I_{OUT(LDO1)} = 0$ mA<br>LDO2 enabled, $I_{OUT(LDO2)} = 0$ mA<br>No $I^2C$ communications<br>LED_EN = 0<br>CLKout_EN = 1<br>24MHz crystal enabled                                                                      |      | 2900                        | 3550            | μА   |

|                      |                                                   | LDO1 enabled, I <sub>OUT(LDO1)</sub> = 0 mA<br>LDO2 enabled, I <sub>OUT(LDO2)</sub> = 0 mA<br>No I <sup>2</sup> C communications<br>LED_EN = 1, PWM Duty Cycle set to 99.9%, ISINK<br>= 2mA<br>CLKout_EN = 1<br>24MHz crystal enabled |      | 3000                        | 3600            | μΑ   |

| I <sub>SD</sub>      | Shutdown current                                  | Device disabled;                                                                                                                                                                                                                      |      | 45                          | 85              | μA   |

|                      |                                                   | V <sub>CC</sub> and AV <sub>CC</sub> < 1.8V                                                                                                                                                                                           |      |                             |                 | r    |

| LED_EI               |                                                   |                                                                                                                                                                                                                                       | 4 4  |                             | V               | V    |

| V <sub>IH</sub>      | High level input voltage  Low level input voltage |                                                                                                                                                                                                                                       | 1.1  |                             | V <sub>CC</sub> | V    |

| V <sub>IL</sub>      | Input Leakage Current                             |                                                                                                                                                                                                                                       |      |                             | 0.4             | μA   |

| I <sub>(in)Ikg</sub> | Input Deglitch                                    | With a minimum pulse period of 500ns before another glitch is received                                                                                                                                                                |      |                             | 100             | ns   |

| GENER                | AL PURPOSE INPUT/OUTPUT (GPIO                     | )                                                                                                                                                                                                                                     |      |                             | l               |      |

| V <sub>IH</sub>      | High level input voltage                          | For VLDO1 = 1.8V                                                                                                                                                                                                                      | 1.1  |                             | VLDO1           | V    |

| V <sub>IH</sub>      | High level input voltage                          | For VLDO1 = 3.3V                                                                                                                                                                                                                      | 1.37 |                             | VLDO1           | V    |

| $V_{IL}$             | Low level input voltage                           | For VLDO1 = 1.8V                                                                                                                                                                                                                      | 0    |                             | 0.4             | V    |

| V <sub>IL</sub>      | Low level input voltage                           | For VLDO1 = 3.3V                                                                                                                                                                                                                      | 0    |                             | 0.6             | V    |

| I <sub>(in)Ikg</sub> | Input leakage current                             | GPIO programmed as input and tied to GND or V <sub>CC</sub>                                                                                                                                                                           |      | 0.01                        | 0.1             | μΑ   |

| V <sub>OH</sub>      | High level output voltage                         | Configured as a push-pull output, $I_{OH} = 1mA$ , VLDO1 $\geq 1.8V$                                                                                                                                                                  | 1.2  | V <sub>LDO1</sub> -<br>0.2V | $V_{LDO1}$      | V    |

## **Electrical Characteristics (continued)**

Unless otherwise noted: VCC = AVCC = 5V,  $C_{VCC}$  = 1 $\mu$ F;  $C_{OUTLDOx}$ = 2.2 $\mu$ F,  $T_A$  = -40 $^{\circ}$ C to 85 $^{\circ}$ C

|                       | PARAMETER                                                                            | TEST CONDITIONS                                                                   | MIN | TYP                         | MAX        | UNIT |

|-----------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-----------------------------|------------|------|

| V <sub>OH</sub>       | High level output voltage                                                            | Configured as a push-pull output, I <sub>OH</sub> = 1mA, 1.3V ≤ VLDO1 ≤1.8V       | 1.0 |                             | $V_{LDO1}$ | V    |

| $V_{OL}$              | Low level output voltage                                                             | Configured as a push-pull output, I <sub>OL</sub> = 2mA, VLDO1 ≥ 1.8V             |     |                             | 0.25       | V    |

| $V_{OL}$              | Low level output voltage                                                             | Configured as a push-pull output, I <sub>OL</sub> = 2mA, 1.3V ≤ VLDO1 ≤1.8V       |     |                             | 0.3        | V    |

| V <sub>OL</sub>       | Low level output voltage                                                             | Configured as an open-drain output, I <sub>OL</sub> = 4mA, VLDO1 ≥ 1.8V           |     |                             | 0.6        | V    |

| V <sub>OL</sub>       | Low level output voltage                                                             | Configured as an open-drain output, I <sub>OL</sub> = 2mA, 1.3V ≤ VLDO1 ≤1.8V     |     |                             | 0.6        | V    |

| I <sub>(out)lkg</sub> | Output leakage current                                                               | Configured as an open-drain output, GPIO connected to VLDO1                       |     | 0.01                        | 0.1        | μΑ   |

| GENER                 | AL PURPOSE OUTPUT (GPO)                                                              |                                                                                   |     |                             |            |      |

| V <sub>OH</sub>       | High level output voltage                                                            | Configured as a push-pull output, I <sub>OH</sub> = 1mA, VLDO1 ≥ 1.8V             | 1.2 | V <sub>LDO1</sub> -<br>0.2V | $V_{LDO1}$ | V    |

| $V_{OH}$              | High level output voltage                                                            | Configured as a push-pull output, I <sub>OH</sub> = 1mA, 1.3V ≤ VLDO1 ≤ 1.8V      | 1.0 |                             | $V_{LDO1}$ | V    |

| V <sub>OL</sub>       | Low level output voltage                                                             | Configured as a push-pull output, I <sub>OL</sub> = 2mA, VLDO1 ≥ 1.8V             |     |                             | 0.25       | V    |

| $V_{OL}$              | Low level output voltage                                                             | Configured as a push-pull output, I <sub>OL</sub> = 2mA, 1.3V ≤ VLDO1 ≤ 1.8V      |     |                             | 0.3        | V    |

| V <sub>OL</sub>       | Low level output voltage                                                             | Configured as an open-drain output, I <sub>OL</sub> = 4mA, VLDO1 ≥ 1.8V           |     |                             | 0.6        | V    |

| $V_{OL}$              | Low level output voltage                                                             | Configured as an open-drain output, I <sub>OL</sub> = 2mA, 1.3V ≤ VLDO1 ≤1.8V     |     |                             | 0.6        | V    |

| I <sub>(out)lkg</sub> | Output leakage current                                                               | Configured as an open-drain output, GPO connected to VLDO1                        |     | 0.01                        | 0.1        | μΑ   |

| SCL, SE               | DA .                                                                                 |                                                                                   |     |                             |            |      |

| $V_{IH}$              | High level input voltage on SCL, SDA                                                 |                                                                                   | 1.2 |                             | Vcc        | V    |

| $V_{IL}$              | Low level input voltage on SCL, SDA                                                  |                                                                                   | 0   |                             | 0.4        | V    |

| I <sub>lkg</sub>      | Pin leakage current on SCL, SDA (includes leakage current for the open-drain output) | Input at V <sub>IL</sub> or V <sub>IH</sub>                                       |     |                             | 100        | nA   |

| V <sub>OL</sub>       | Low level output voltage on SDA                                                      | For I <sub>OL</sub> = 1mA                                                         |     |                             | 0.25       | V    |

| UNDER                 | VOLTAGE LOCKOUT (UVLO), SENSED                                                       | AT PIN AVCC                                                                       |     |                             |            |      |

|                       | Internal undervoltage lockout threshold                                              | AV <sub>CC</sub> rising                                                           | 3.4 | 3.6                         | 3.7        | V    |

| UVLO                  | Internal undervoltage lockout threshold hysteresis                                   | AV <sub>CC</sub> falling                                                          |     | 130                         |            | mV   |

| CLOCK                 | GENERATOR                                                                            | ,                                                                                 |     |                             |            |      |

| f <sub>osc</sub>      | Frequency of external crystal                                                        |                                                                                   |     | 24                          |            | MHz  |

|                       |                                                                                      | For OSC_FREQ[1,0] = 00                                                            |     | 24                          |            |      |

| f <sub>CLKOUT</sub>   | Frequency on pin CLKOUT                                                              | For OSC_FREQ[1,0] = 01                                                            |     | 12                          |            | MHz  |

| JENOUT                | · · · · · · · · · · · · · · · · · · ·                                                | For OSC_FREQ[1,0] = 10                                                            |     | 6                           |            |      |

|                       |                                                                                      | For OSC_FREQ[1,0] = 11                                                            |     | 3                           |            |      |

|                       | Period jitter; rms                                                                   | Measured period compared to the Average Period of 10,000 randomly selected cylces |     |                             | 600        | ps   |

|                       | Peak period to period jitter                                                         | Measured period compared to the Average Period of 10,000 randomly selected cylces |     |                             | 600        | ps   |

|                       | Duty cycle of CLKout                                                                 |                                                                                   | 40% | 50%                         | 60%        |      |

|                       | Rise time / fall time for clock output                                               | 10% to 90% of output voltage, 1.3V ≤ VLDO1 ≤ 3.3V                                 |     |                             | 10         | ns   |

|                       |                                                                                      |                                                                                   |     |                             |            |      |

## **Electrical Characteristics (continued)**

Unless otherwise noted: VCC = AVCC = 5V,  $C_{VCC}$  = 1 $\mu$ F;  $C_{OUTLDOx}$ = 2.2 $\mu$ F,  $T_A$  = -40 $^{\circ}$ C to 85 $^{\circ}$ C

|                                                                                                                                              | PARAMETER                                                           | TEST CONDITIONS                                                                                                         | MIN   | TYP                         | MAX        | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------|------------|------|

|                                                                                                                                              | Load capacitance                                                    | Defines the maximum capacitance that can be driven by the CLKOUT buffer and still meet the specified rise/fall times    |       |                             | 15         | pF   |

|                                                                                                                                              | Output impedance                                                    |                                                                                                                         |       | 50                          |            | Ω    |

| $V_{OH}$                                                                                                                                     | High level output voltage                                           | Internally connected to V <sub>LDO1</sub> ≥ 1.8V: for C <sub>OUT</sub> = 15pF, I <sub>OH</sub> = 1mA                    | 1.6   | V <sub>LDO1</sub><br>- 0.2V | $V_{LDO1}$ | ٧    |

| $V_{OL}$                                                                                                                                     | Low level output voltage                                            | For C <sub>OUT</sub> = 15pF, I <sub>OL</sub> = 1mA                                                                      |       | 0.2                         | 0.3        | V    |

| t <sub>start</sub>                                                                                                                           | Oscillator start-up time                                            | Time from CLKout_EN=1 to CLKout active for the NXTBD-24.000M crystal, not tested in production but based on simulations |       |                             | 10         | ms   |

| Load capacitance   Defines the maximum capacitance that can be driven by the CLROUT buffer and still meet the specified rise/fall times   50 |                                                                     |                                                                                                                         |       |                             |            |      |

| $T_{SD}$                                                                                                                                     | Thermal shutdown                                                    | Increasing junction temperature                                                                                         |       | 150                         |            | °C   |

|                                                                                                                                              | Thermal shutdown hysteresis                                         | Decreasing junction temperature                                                                                         |       | 30                          |            | °C   |

| VLDO1,                                                                                                                                       | , VLDO2 LOW DROPOUT REGULATORS                                      | 5                                                                                                                       |       |                             |            |      |

| V <sub>CC</sub>                                                                                                                              |                                                                     |                                                                                                                         | 3.7   |                             | 6          | V    |

| V <sub>LDO1</sub>                                                                                                                            | LDO1 output voltage                                                 | See LDO1_CTRL Register definition for all available voltage settings.                                                   | 0.8   | 1.8                         | 3.3        | V    |

| $V_{LDO2}$                                                                                                                                   | LDO2 output voltage                                                 | _                                                                                                                       | 0.8   | 1.2                         | 3.3        | >    |

| Io                                                                                                                                           | Output current for LDO1 and LDO2                                    |                                                                                                                         |       |                             | 100        | mA   |

| I <sub>SC</sub>                                                                                                                              |                                                                     | $V_{LDOx} = GND$                                                                                                        | 110   |                             | 220        | mA   |

|                                                                                                                                              | Dropout voltage at LDO1 and LDO2                                    | I <sub>O</sub> = 75mA; V <sub>CC</sub> ≥ 3.7V                                                                           |       |                             | 700        | mV   |

|                                                                                                                                              |                                                                     | I <sub>O</sub> = 2mA through 75mA                                                                                       | -1.5% |                             | 1.5%       |      |

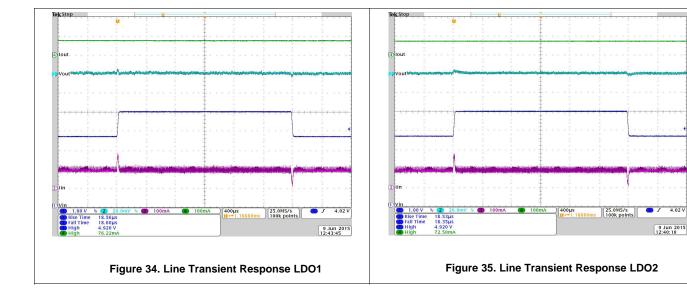

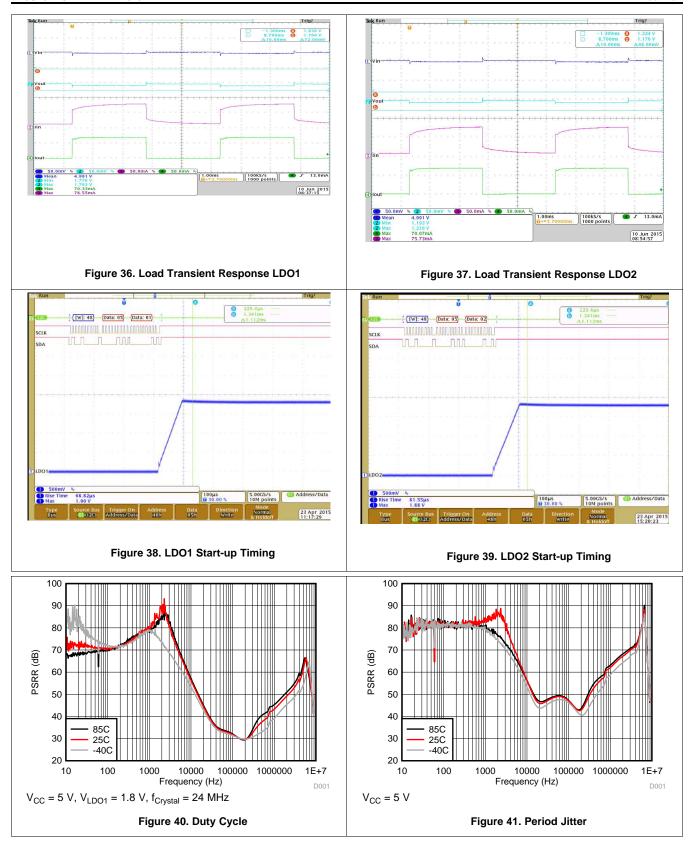

|                                                                                                                                              | Load Transient                                                      | VCC=AVCC=5V, I <sub>O(LDOx)</sub> = 0A to 75mA in 1us                                                                   |       |                             | 10%        |      |

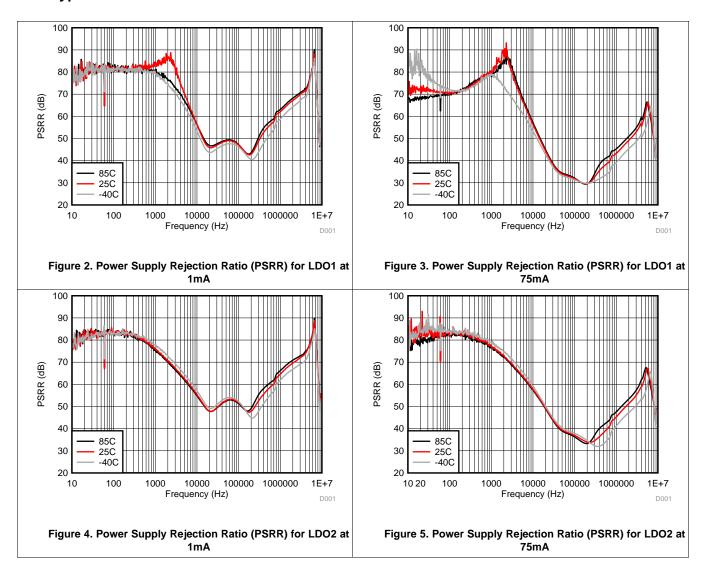

| PSRR                                                                                                                                         | Power supply rejection ratio                                        | $f = 10kHz, C_{OUT} \ge 2.2\mu F VINLDOx = 5V, V_{OUT} =$                                                               |       | 56                          |            | dB   |

|                                                                                                                                              | Output voltage rms noise                                            |                                                                                                                         |       |                             | 4          | mV   |

| t <sub>Ramp</sub>                                                                                                                            | V <sub>OUT</sub> ramp time                                          | Time to ramp from 5% to 95% of V <sub>OUT</sub>                                                                         | 24    | 50                          | 200        | μs   |

| R <sub>DIS</sub>                                                                                                                             |                                                                     | V <sub>IN</sub> < UVLO                                                                                                  | 200   | 400                         | 550        | Ω    |

| MINIMU                                                                                                                                       | JM ON TIME                                                          |                                                                                                                         |       |                             |            |      |

|                                                                                                                                              | Minimum on time range                                               |                                                                                                                         | 0     |                             | 11         | s    |

|                                                                                                                                              | Minimum on time accuracy                                            |                                                                                                                         | -1    |                             | 1          | LSB  |

| LED CU                                                                                                                                       | JRRENT SINK                                                         |                                                                                                                         |       |                             |            |      |

| I <sub>LED</sub>                                                                                                                             |                                                                     |                                                                                                                         |       | 10                          |            | mA   |

|                                                                                                                                              | Minimum voltage drop from ISINK to GND needed for proper regulation | At ISINK = 10mA                                                                                                         | 0.3   |                             |            | V    |

|                                                                                                                                              | ISINK accuracy                                                      | ISINK = 10mA, Duty Cycle set to 99.9%                                                                                   | -10%  |                             | 5%         | V    |

|                                                                                                                                              |                                                                     | For PWM_FREQ[1,0] = 00                                                                                                  |       | 23.5                        |            |      |

|                                                                                                                                              | DIMM fraguency as ations                                            | For PWM_FREQ[1,0] = 01                                                                                                  |       | 11.7                        |            |      |

|                                                                                                                                              | PWM frequency seetings                                              | For PWM_FREQ[1,0] = 10                                                                                                  |       | 5.8                         |            | kHz  |

|                                                                                                                                              |                                                                     | For PWM_FREQ[1,0] = 11                                                                                                  |       | 2.9                         |            |      |

|                                                                                                                                              | PWM duty cycle range                                                | Limited by ISINK rise / fall time for PWM_FREQ[1:0] other than 2'b11 setting                                            | 0%    |                             | 99.9%      |      |

|                                                                                                                                              | ISINK rise / fall time                                              | $V_{( SINK)} \ge 0.6V$ for 2 mA $\le ISINK \le 30$ mA                                                                   |       | 400                         |            | ns   |

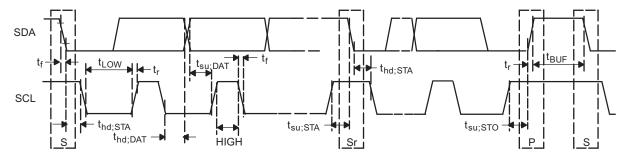

## 6.6 Timing Requirements

|                     |                                                                                                                    | MIN  | MAX | UNIT |

|---------------------|--------------------------------------------------------------------------------------------------------------------|------|-----|------|

| $f_{MAX}$           | Clock frequency                                                                                                    |      | 400 | kHz  |

| t <sub>(HIGH)</sub> | Clock high time                                                                                                    | 600  |     | ns   |

| t <sub>(LOW)</sub>  | Clock low time                                                                                                     | 1300 |     | ns   |

| t <sub>r</sub>      | DATA and CLK rise time                                                                                             |      | 300 | ns   |

| t <sub>f</sub>      | DATA and CLK fall time                                                                                             |      | 300 | ns   |

| t <sub>hd;STA</sub> | Hold time (repeated) START condition (after this period the first clock pulse is generated)                        | 600  |     | ns   |

| t <sub>su;STA</sub> | Setup time for repeated START condition                                                                            | 600  |     | ns   |

| t <sub>hd;DAT</sub> | Data input hold time                                                                                               | 10   |     | ns   |

| t <sub>su;DAT</sub> | Data input setup time                                                                                              | 100  |     | ns   |

| t <sub>su;STO</sub> | STOP condition setup time                                                                                          | 600  |     | ns   |

| t <sub>BUF</sub>    | Bus free time                                                                                                      | 1300 |     | ns   |

| CI                  | load capacitance on SDA and SCL (with a 730 $\Omega$ or smaller pull-up resistor on SDA and SCL pulled up to 1.8V) |      | 400 | pF   |

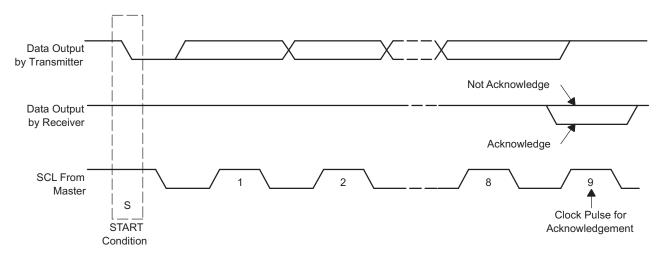

Figure 1. Serial I/f Timing Diagram

## 6.7 Typical Characteristics

## 7 Detailed Description

## 7.1 Overview

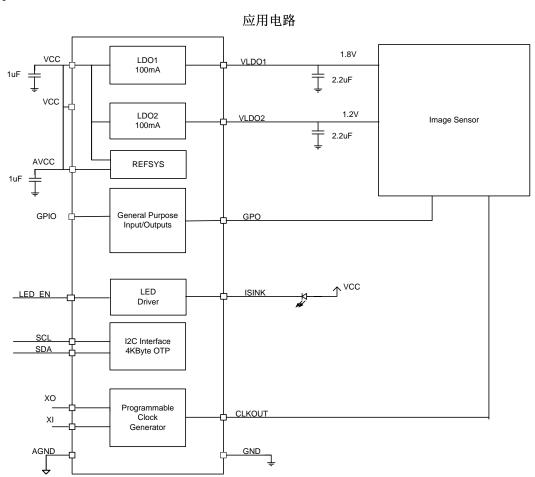

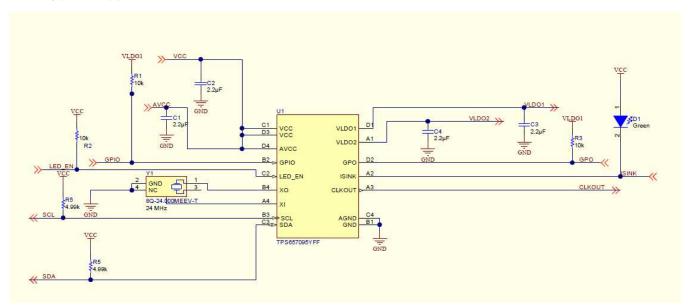

The TPS657095 integrates two LDOs, a PWM-dimmable current sink for driving an LED, one GPIO for controlling an external device and one GPO for controlling an embedded camera module.

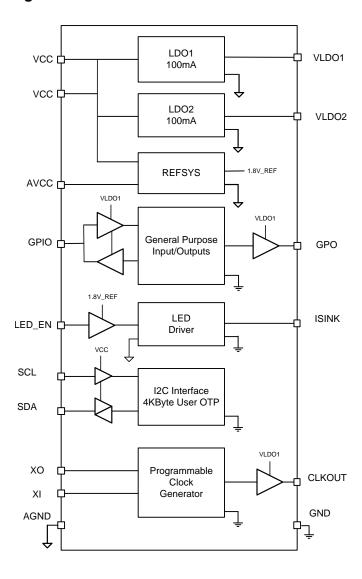

## 7.2 Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 State Diagram

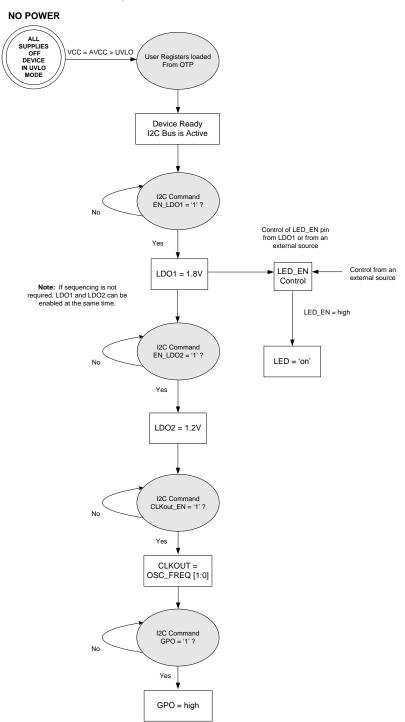

The state diagram below details the basic operation of this device.

Figure 6. State Diagram

www.ti.com.cn

## **Feature Description (continued)**

## 7.3.2 Power-up Timing

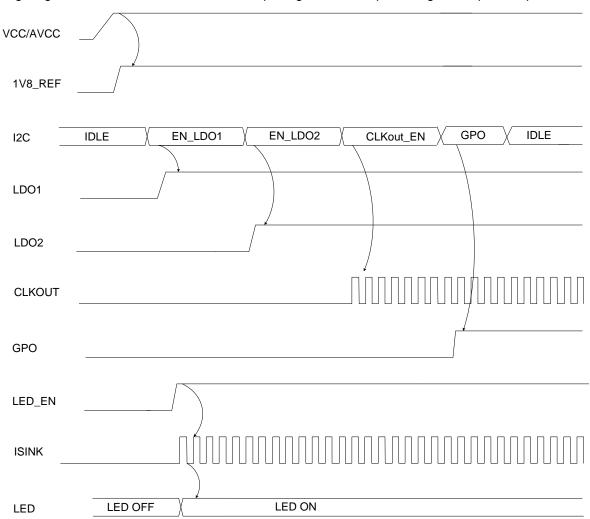

The timing diagram below details the state of the input signals and output voltages in a power-up event.

Figure 7. Power-up Timing

#### **Feature Description (continued)**

#### 7.3.3 GPO

The TPS657095 has one general purpose output (GP0) that can be used to control a camera image sensor. Bit 0 of the GPIO\_CTRL Register can be used to set the output level and bit 1 of the GPIO\_CTRL Register can be used to define whether the output is an open-drain or push-pull output. Internally, the GPO output buffer is connected to LDO1. Therefore, LDO1 has to be enabled in order for the GPO output to operate. In the open-drain configuration, the external pull-up resistor should be pulled up to a voltage that is equal to or less than VCC at all times. Connecting the pull-up resistor to a voltage source that is greater than VCC or present whenever VCC is not present may cause an unwanted leakage path.

#### 7.3.4 GPIO

The TPS657095 has one general purpose input/output (GPIO) that can be used to control an external device when configured as an output. When configured as an input, the GPIO pin serves as a dedicated LDO2 enable. This discrete pin is 'ORed' with the software LDO2 enable. The functionality is shown in the following table.

GPIO (configured as an input)

EN\_LDO2 (bit 1 of the LDO\_CTRL REGISTER

LDO2 OUTPUT

0

0

Off

0

1

On

1

0

On

1

0

On

1

0

On

**Table 1. LDO2 Output Control**

The GPIO\_CTRL register contains the bits used to configure this GPIO. Bit 3 of the GPIO\_CTRL Register can be used to set the output level, bit 4 can be used to configure the GPIO as an input or an output, and bit 5 of the GPIO\_CTRL Register can be used to define whether the output is an open-drain or push-pull output. Internally, the GPIO output buffer is connected to LDO1. Therefore, LDO1 has to be enabled in order for the GPIO to operate. In the open-drain configuration, the external pull-up resistor should be pulled up to a voltage that is equal to or less than VCC at all times. Connecting the pull-up resistor to a voltage source that is greater than VCC or present whenever VCC is not present may cause an unwanted leakage path.

#### 7.3.5 LED EN

The TPS657095 has a pin, LED\_EN, which is used to control a privacy LED. The privacy LED can only be turned on or off using the LED\_EN pin. No other means to control the privacy LED exists in this device. Operation of the LED\_EN pin as it relates to minimum on time is shown in the Minimum-On-Time feature section of this document. The LED driver circuit of this device is internally biased by an internal 1.8V reference which is automatically powered once a valid voltage is present on the VCC/AVCC pins of this device. The input leakage current specified in the Electrical Characteristics section of this datasheet will not be exceeded even if a logic high voltage is applied to this pin while VCC/AVCC are not present.

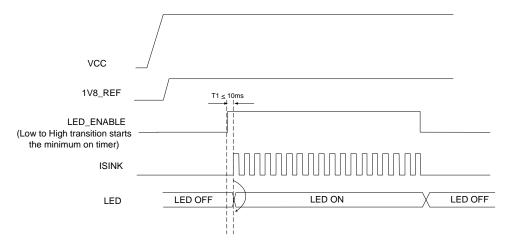

#### 7.3.6 Minimum-On-Time Feature

In order to ensure proper operation of a privacy LED, the TPS657095 device incorporates a Minimum-On-Time feature. The Minimum-On-Time for this device is programmed at the factory to a specified value which is shown in the MIN\_ON\_TIME\_THR Register. The user programmable Minimum-On-Time Register can be used to set a minimum on time for the LED. .

Once the Minimum-On-Time Register is loaded with a value and the internal PWM is enabled, the Minimum-On-Time timer will count to the value loaded. Writing a new value to the Minimum-On-Time Register prior to the timer expire will only take effect after the timer expires and the internal PWM is re-enabled.

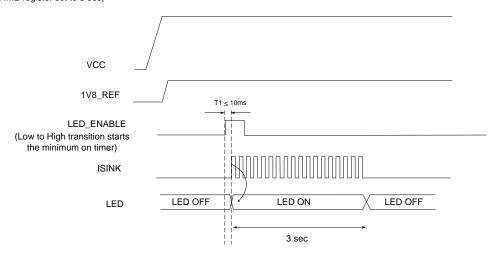

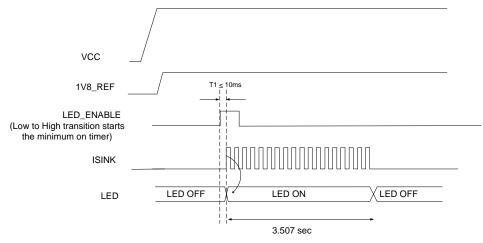

Case #1: LED\_ENABLE is in the active state for a time much greater than the 'MIN\_ON\_TIME' register settings

Case #2:

LED\_ENABLE is in the active state for a time less than the 'MIN\_ON\_TIME' register setting. (MIN\_ON\_TIME register set to 3 sec)

Case #3: LED\_ENABLE is in the active state for a time less than the 'MIN\_ON\_TIME' register setting (MIN\_ON\_TIME register set to 3.507 sec)

Figure 8. Minimum-On-Time Timing Diagrams

#### 7.3.7 PWM Dimming

LED EN serves as the enable for the internal PWM.

- LED EN = 0: LED is OFF

- LED EN = 1: LED is ON / internal PWM is enabled

Since the crystal oscillator is needed for the internal PWM dimming, it is automatically enabled based on the status of the LED EN pin and on the CLKout EN register bit.

| CLKout_EN | LED_EN | ISINK             | CRYSTAL OSCILLATOR<br>ENABLED | CLKout |

|-----------|--------|-------------------|-------------------------------|--------|

| 0         | 0      | OFF               | OFF                           | OFF    |

| 0         | 1      | ON - internal PWM | ON                            | OFF    |

| 1         | 0      | OFF               | ON                            | ON     |

| 1         | 1      | ON - internal PWM | ON                            | ON     |

#### 7.3.8 Crystal Oscillator and CLKOUT

The crystal oscilator is used to provide a clock signal to the camera image sensor via the CLKOUT pin. It is also used to control the internal PWM for dimming the LED and as the clock for the Minimum-On-Time counter. The crystal oscillator is enabled by either the CLKout\_EN bit in the PWM\_OSC\_CNTRL register or by driving the LED\_EN pin to a high state. Since the Minimum-On-Time counter is started when the LED\_EN input is driven to a high state, the crystal oscillator will remain on if the LED\_EN pin is driven to a low state and the Minimum-On-Time counter has yet to time out.

The CLKOUT buffer is internally supplied by LDO1, hence LDO1 needs to be enabled for proper functionality of the clock output. the CLKOUT buffer is enabled only when bit 2 of the PWM\_OSC\_CNTRL Register is set to a logic one. If bit 2 of the PWM\_OSC\_CNTRL register is set to a logic one while LDO1 is disabled, the crystal oscillator will run but the clock output will not be present on the CLKOUT pin. The OSC\_FREQ[1:0] bits in the PWM\_OSC\_CNTRL Register should be set prior to enabling the CLKOUT buffer.

In addition, the crystal oscillator is driving the internal charge pump that generates the programming voltage for the 4kByte OTP memory. For programming the OTP, the oscillator has to be enabled by setting CLKout\_EN to a logic '1' at least 10ms before the OTP is written to allow the crystal to stabilize.

The oscillator circuit used does not require external components other than the crystal itself on pins XI and XO. Internally, the oscillator circuit contains two 16pF capacitors connected from XI to GND and from XO to GND. It is designed for an equivalent series resistance of the crystal to be less than  $100\Omega$ . Therefore, a crystal must be used with a series resistance of less than this value and no other resistors in series or in parallel to the crystal must be added.

The signal on CLKOUT is delayed from the CLKout\_EN bit enabling the output buffer until the oscillator is stable. Once it has stabilized, an additional internal wait time of 131072 clk cycles x 1/24MHz has been added internally to the design before the output is set active. Given the typical start-up time of the crystal oscillator, it is safe to assume the total start-up time which depends on the crystal used including the 131072 cycles of clk delay is less than 10ms.

**Table 2. Tested Crystals**

| TYPE            | NOMINAL<br>FREQUENCY | LOAD CAPACITANCE       | EQUIVALENT SERIES<br>RESISTANCE | SUPPLIER |

|-----------------|----------------------|------------------------|---------------------------------|----------|

| 8Q-24.000MEEV-T | 24MHz                | 8pF (16pF on each pin) | 100Ω maximum                    | TXC      |

#### 7.3.9 LDOs

The low dropout voltage regulators are designed to operate with low value ceramic input and output capacitors. Both LDOs contain a current limit feature which is used at start up to control the voltage ramp time.

LDO1 is enabled by bit 0 of the LDO\_CTRL register. LDO2 can be enabled by either bit 1 of the LDO\_CTRL register or by the GPIO if configured as an input. Since the input buffer for the GPIO is powered by LDO1, LDO1 must be enabled before the GPIO pin can be used to enable LDO1. In the case of a thermal event, the register enable bits will be cleared with no auto-re-start feature so as to allow the application software to control the power sequencing of the LDOs.

## TEXAS INSTRUMENTS

#### 7.3.10 Undervoltage Lockout

The undervoltage lockout circuit prevents the device from malfunctioning at low input voltages and from excessive discharge of the battery. It disables the complete device at low input voltages.

The supply voltage to the TPS657095 is internally sensed at pin AVCC. When the voltage at AVCC exceeds the UVLO limit, the internal enable signals turns HIGH and allows the device to operate. When the supply voltage drops below the UVLO limit, TPS657095 is forced OFF, all functions are disabled and the LDO output voltage discharge circuitry is forced ON to ramp down the output voltage. However, if the input voltage drops below 2V, the discharge circuit becomes inactive.

#### 7.3.11 Power Up/Power Down Default States

The GPO, GPIO and CLKOUT pins contain internal buffers powered by LDO1. The following table shows their state during a power up (UVLO Rising) and power down (UVLO Falling) event.

|               |                              | •                                            |                             |                                               |  |  |  |  |  |  |

|---------------|------------------------------|----------------------------------------------|-----------------------------|-----------------------------------------------|--|--|--|--|--|--|

|               | EVENT                        |                                              |                             |                                               |  |  |  |  |  |  |

| CIRCUIT       | VCC > UVLO, LDO1<br>turn-off | VCC rising > UVLO,<br>LDO1 in an 'off' state | VCC > UVLO, LDO1<br>turn-on | VCC falling < UVLO,<br>LDO1 in an 'off' state |  |  |  |  |  |  |

| GPO           | Off <sup>1</sup>             | Off <sup>1</sup>                             | Push-Pull, Low Level        | Off <sup>1</sup>                              |  |  |  |  |  |  |

| GPIO          | Off <sup>1,2</sup>           | Off <sup>1,2</sup>                           | Input <sup>3</sup>          | Off <sup>1</sup>                              |  |  |  |  |  |  |

| Register Bits | no change                    | OTP Load State                               | no change                   | Reset State                                   |  |  |  |  |  |  |

| CLKOUT        | Off <sup>1</sup>             | Off <sup>1</sup>                             | Low (CLKOUT_EN = low)       | Off <sup>1</sup>                              |  |  |  |  |  |  |

Table 3. Power Up/Power Down Events

#### Notes:

- 1. Output is 'off' as a result of no power supply. The output follows LDO1 to within a diode drop.

- 2. The GPIO STATE bit (bit 3 in the GPIO CTRL register) is forced to a logic low.

- 3. The default setting is configured as an input. This can be modified by using the GPIO CTRL register.

#### 7.3.12 Output Voltage Discharge for LDO1 and LDO2

The LDOs contain an output capacitor discharge feature which makes sure that the capacitor is discharged to GND when the supply voltage drops below the undervoltage lockout threshold. The discharge function is enabled when voltage is applied at AVCC starting at about 2.1V until the LDOs are enabled.

#### 7.3.13 Power-Good Status Bits for LDO1 and LDO2

Bits PGOOD\_LDO1 and PGOOD\_LDO2 in register LDO\_CTRL are driven by an comparator inside the LDOs to indicate when the output voltage is in regulation. The Bits are set 'high' when the LDO is in regulation. When the LDO is enabled but the voltage is not above the power-good threshold, the bit is set to a 'low' state. The bit is also set to a 'low' state if the LDO is disabled.

#### 7.3.14 Short-Circuit Protection

All outputs are short circuit protected with a maximum output current as defined in the electrical specifications.

#### 7.3.15 Thermal Shutdown

As soon as the junction temperature,  $T_J$ , exceeds 150°C (typically) for any of the LDOs, the LDO will go into thermal shutdown. In this case, the LDOs are turned-off. After the temperature has fallen below the threshold, the LDO remains off until it is enabled again by the I2C interface. There is no automatic power-on feature once the thermal event is past.

#### 7.3.16 LED Driver

The TPS657095 contains a LED driver for a current of up to 30mA. ISINK is an open drain current sink that regulates a current in a LED. The anode of the LED needs to be tied to a positive supply voltage e.g., V<sub>CC</sub> or any other voltage within the limits of the electrical spec of TPS657095, depending on the forward voltage of the LED. The cathode of the LED is connected to ISINK which sets a constant current to GND. ISINK is regulated internally based on the default current set internally. If the LED\_EN pin is pulled LOW, the LED driver is disabled and its output ISINK is high resistive. If LED\_EN is HIGH, the current sink regulates to the current defined by the setting in the ISINK CURRENT Register.

The internal PWM generator allows for internal dimming with a frequency of 3kHz, 6kHz, 12kHz or 24kHz. A 10Bit duty cycle register allows to set the duty cycle in a range from 0% to 99.9% using 8Bits PWM resolution and another 2Bits of dithering.

A signal applied at the LED\_EN pin is used to synchronously enable and disable the internal PWM signal.

#### 7.3.17 4kByte OTP Memory

The TPS657095 contains 4kBytes of one-time-programmable (OTP) memory to store user data. The memory has a linear address range from 0x0000 to 0x0FFF and uses two Byte addressing as described in the serial interface description. Reading beyond the specified linear address range will result in reading all zeros. Writes to an address space beyond the specified linear address range are inhibited.

The 4kByte OTP memory requires a programming voltage higher than 5V. The program voltage is generated internally by a charge pump which uses the VCC voltage as its input. During programming, Vcc has to be kept at 5V +/-5% (a voltage of 5.25V is recommended) and the internal oscillator has to be enabled 10ms before programming to allow the 24MHz crystal to stabilize. The 24MHz clock is needed for the internal charge pump to generate the programming voltage from Vcc.

As an added security measure, programming the 4kByte OTP memory requires a two byte sequential password to be written to in the PMU register space at address 0x0F. The two bytes must be written back to back with no restriction on the delay between the writes. Any data written at address 0x0F that does not match the password and sequence will disable the ability to program the 4kByte OTP memory.

#### 7.3.17.1 Programming the 4KByte OTP Memory

- 1. Apply 5V +/-5% to the VCC and AVCC pins.

- 2. Enable the internal oscillator by driving the LED\_EN pin to a high state or setting the CLKout\_EN bit to a '1'.

- 3. Wait at least 10ms for the crystal to stabilize.

- 3. Using the PMU register I2C address, write the password to the 4K OTP PASSWORD register.

- 4. Using the 4kByte OTP memory I2C address, write the desired value to a specific address using the protocol shown in Figure 6.

- 5. Exit the programming of the 4KByte OTP memory by over writing the 4K\_OTP\_PASSWORD register with an incorrect password or by removing power to the device.

#### 7.4 Device Functional Modes

#### 7.4.1 Shutdown Mode

The TPS657095 is in a 'Shutdown' mode if the voltage on the AVCC pin is below 1.8V. In this mode, the device will not respond to I2C commands nor will the LED\_EN pin be operational.

#### 7.4.2 Operational Mode

The TPS657095 enters an 'Operational' mode mode once a voltage greater than the UVLO limit is present on both the VCC and AVCC pins. In this mode, the I2C is active, the operation of the LED is controllable via the LED\_EN pin and the LDOs can be enabled.

# TEXAS INSTRUMENTS

#### **Device Functional Modes (continued)**

#### NOTE

The voltage on the AVCC and VCC pins should not be left in a state between the Shutdown Mode voltage and the Operational Mode voltage. Keeping the input voltage to the device in this indeterminate state will result in unwanted quiescent current consumption.

#### 7.5 Programming

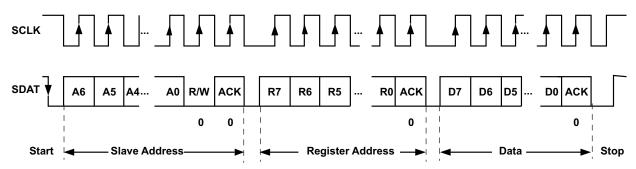

#### 7.5.1 Serial Interface

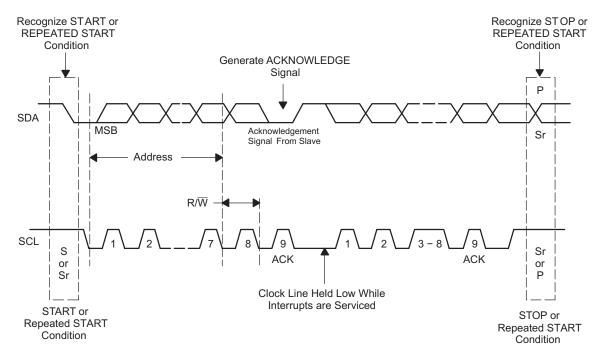

The serial interface is compatible with the standard and fast mode I<sup>2</sup>C specifications, allowing transfers at up to 400kHz. The interface adds flexibility to the power supply solution, enabling most functions to be programmed to new values depending on the instantaneous application requirements and charger status to be monitored. Register contents remain intact as long as VCC remains above the UVLO threshold. The I<sup>2</sup>C interface is running from an internal oscillator that is automatically enabled when there is an access to the interface. Additional features supported by the I<sup>2</sup>C compatible interface are:

- multi-byte read/write capability

- clock stretching; specifically needed during OTP write

The 7bit device address for TPS657095 is:

- "100 1000" for the PMU user registers

- "101 1000" for the 4kByte OTP memory

For the PMU, at address "100 1000", the device address is followed by the 1Byte register address and 1Byte data (for a write instruction)

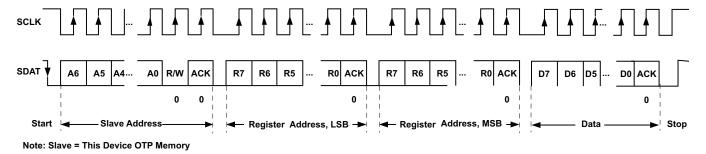

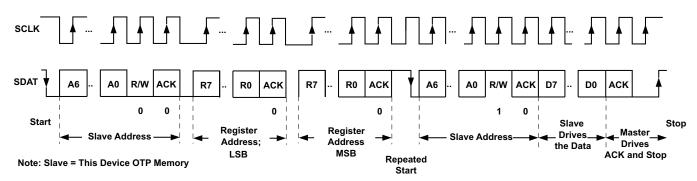

For the 4kByte OTP memory, at address "101 1000", the device address is followed by the 1Byte register address [7:0] followed by the second address Byte [15:8] and 1Byte data (for a write instruction) giving a 4kByte linear address range for the memory. Please note that the supply voltage range at pins VCC and AVCC during programming (writing) of the OTP memory is limited to 5V ±5%.

Attempting to read data from register addresses not listed in this section will result in 00h being read out.

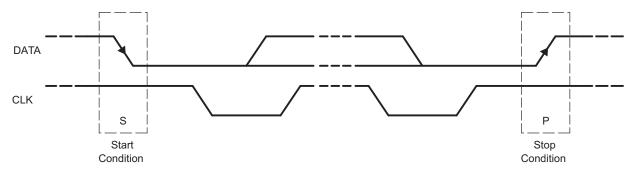

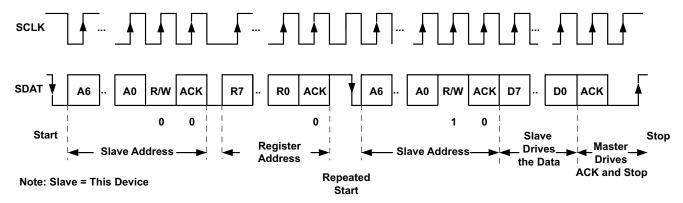

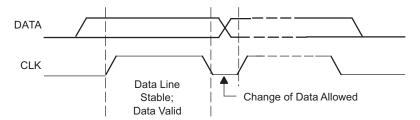

For normal data transfer, DATA is allowed to change only when CLK is low. Changes when CLK is high are reserved for indicating the start and stop conditions. During data transfer, the data line must remain stable whenever the clock line is high. There is one clock pulse per bit of data. Each data transfer is initiated with a start condition and terminated with a stop condition. When addressed, the TPS657095 generates an acknowledge bit after the reception of each byte. The master device (microprocessor) must generate an extra clock pulse that is associated with the acknowledge bit. The TPS657095 must pull down the DATA line during the acknowledge clock pulse so that the DATA line is a stable low during the high period of the acknowledge—related clock pulse. Setup and hold times must be taken into account. During read operations, a master must signal the end of data to the slave by not generating an acknowledge bit on the last byte that was clocked out of the slave. In this case, the slave device TPS657095 must leave the data line high to enable the master to generate the stop condition.

The interface is reset by the internal UVLO signal of TPS657095 or by a STOP condition. If the SCL and SDA signal is not stable at the time the UVLO threshold on pin Vcc is exceeded, the first communication may not be acknowledged and will have to be re-transmitted after a STOP condition.

Upon the application of power on the VCC/AVCC pins, the internal I2C buffers may sequence up in a manner that produces a false START. If a false START is detected, an internal synchronization clock will be enabled until a STOP condition is received. During the time that the internal synchronization clock is active, the device will consume an additional 120uA of current.

## **Programming (continued)**

Figure 9. START and STOP Conditions

Note: Slave = This Device

Figure 10. Serial Interface WRITE to TPS657095 User Registers

Figure 11. Serial Interface READ from TPS657095 User Registers

Figure 12. Serial Interface WRITE to TPS657095 OTP Memory

www.ti.com.cn

## **Programming (continued)**

Figure 13. Serial Interface READ from TPS657095 OTP Memory

Figure 14. Bit Transfer on the Serial Interface

Figure 15. Acknowledge on the I<sup>2</sup>C Bus

## **Programming (continued)**

Figure 16. Bus Protocol

## 7.6 Register Map

## 7.6.1 DEV\_AND\_REV\_ID Register Address: 00h

## Figure 17. DEV\_AND\_REV\_ID Register

| DEV_AND_REV_ID           | B7        | В6        | B5        | B4        | В3        | B2        | B1        | ВО        |

|--------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Bit name and function    | DEV_ID[3] | DEV_ID[2] | DEV_ID[1] | DEV_ID[0] | REV_ID[3] | REV_ID[2] | REV_ID[1] | REV_ID[0] |

| Default                  | 0         | 1         | 0         | 1         | 0         | 1         | 0         | 0         |

| Default set by:          | OTP       |

| Default value loaded by: | UVLO      |

| Read/write               | R         | R         | R         | R         | R         | R         | R         | R         |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 4. DEV\_AND\_REV\_ID Field Descriptions

| Bit     | Field       | Туре | Reset | Description                   |

|---------|-------------|------|-------|-------------------------------|

| Bit 7:4 | DEV_ID[3:0] | R    | 0101  | Device ID: TPS657095 = 0101   |

| Bit 3:0 | REV_ID[3:0] | R    | 0100  | Die Revision ID: PG1.0 = 0100 |

## 7.6.2 OTP\_REV Register Address: 01h

## Figure 18. OTP\_REV Register Address: 01h Register

| OTP_REV                  | B7   | В6             | B5             | B4             | В3             | B2         | B1         | во             |

|--------------------------|------|----------------|----------------|----------------|----------------|------------|------------|----------------|

| Bit name and function    | RSVD | OTP_REV<br>[6] | OTP_REV[<br>5] | OTP_REV[<br>4] | OTP_REV[<br>3] | OTP_REV[2] | OTP_REV[1] | OTP_REV[<br>0] |

| Default                  | 0    | 1              | 0              | 0              | 0              | 0          | 0          | 0              |

| Default set by:          | OTP  | OTP            | OTP            | OTP            | OTP            | OTP        | OTP        | OTP            |

| Default value loaded by: | UVLO | UVLO           | UVLO           | UVLO           | UVLO           | UVLO       | UVLO       | UVLO           |

| Read/write               | R    | R              | R              | R              | R              | R          | R          | R              |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 5. OTP\_REV Register Address: 01h Register Field Descriptions

| Bit     | Field        | Туре | Reset   | Description                                      |

|---------|--------------|------|---------|--------------------------------------------------|

| Bit 7   | RSVD         | R    | 0       |                                                  |

| Bit 6:0 | OTP_REV[6:0] | R    | 1000000 | Reserved: 100_0000: Production PG1.0 programming |

## 7.6.3 GPIO\_CTRL Register Address: 02h

## Figure 19. GPIO\_CTRL Register

| GPIO_CTRL                | B7    | В6    | B5           | B4       | В3             | B2    | B1         | ВО   |

|--------------------------|-------|-------|--------------|----------|----------------|-------|------------|------|

| Bit name and function    | SPARE | SPARE | GPIO_drive r | GPIO_DIR | GPIO_STA<br>TE | SPARE | GPO_driver | GPO  |

| Default                  | 0     | 0     | 1            | 1        | 1              | 0     | 0          | 0    |

| Defualt set by:          | OTP   | OTP   | OTP          | OTP      | OTP            | OTP   | OTP        | OTP  |

| Default value loaded by: | UVLO  | UVLO  | UVLO         | UVLO     | UVLO           | UVLO  | UVLO       | UVLO |

| Read/write               | R     | R     | R/W          | R/W      | R/W            | R     | R/W        | R/W  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 6. GPIO\_CTRL Register Field Descriptions

| Bit     | Field       | Туре | Reset | Description                                                                                                                                                                                                                              |

|---------|-------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7:6 | SPARE       | R    | 00    |                                                                                                                                                                                                                                          |

| Bit 5   | GPIO_driver | R/W  | 1     | 0 = GPIO is configured as push pull output; internally connected to LDO1<br>1 = GPIO is configured as open drain output                                                                                                                  |

| Bit 4   | GPIO_DIR    | R/W  | 1     | 0 = GPIO is configured as an input and used to enable LDO2<br>1 = GPIO is configured as an output                                                                                                                                        |

| Bit 3   | GPIO_STATE  | R/W  | 1     | 0 = actively pulled low<br>1 = high impedance output if the GPIO_driver bit is configured<br>as an open-drain output / internally pulled up to the LDO1<br>voltage setting if the GPIO_driver bit is configured as a push-pull<br>output |

| Bit 2   | SPARE       | R    | 0     |                                                                                                                                                                                                                                          |

| Bit 1   | GPO_driver  | R/W  | 0     | 0 = GPO is configured as push pull output; internally connected to LDO1 1 = GPO is configured as open drain output                                                                                                                       |

| Bit 0   | GPO         | R/W  | 0     | 0 = actively pulled low 1 = high impedance output if the GPO_driver bit is configured as an open-drain output / internally pulled up to the LDO1 voltage setting if the GPO_driver bit is configured as a push-pull output               |

# TEXAS INSTRUMENTS

## 7.6.4 PWM\_OSC\_CNTRL Register Address: 03h

## Figure 20. PWM\_OSC\_CNTRL Register

| OSCILLATOR_CONTROL       | B7    | В6    | B5    | B4              | В3              | B2        | B1          | ВО              |

|--------------------------|-------|-------|-------|-----------------|-----------------|-----------|-------------|-----------------|

| Bit name and function    | SPARE | SPARE | SPARE | PWM_<br>FREQ[1] | PWM_<br>FREQ[0] | CLKout_EN | OSC_FREQ[1] | OSC_FREQ[<br>0] |

| Default                  | 0     | 0     | 0     | 1               | 1               | 0         | 0           | 0               |

| Default set by:          | OTP   | OTP   | OTP   | OTP             | OTP             | OTP       | OTP         | OTP             |

| Default value loaded by: | UVLO  | UVLO  | UVLO  | UVLO            | UVLO            | UVLO      | UVLO        | UVLO            |

| Read/write               | R     | R     | R     | R/W             | R/W             | R/W       | R/W         | R/W             |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 7. PWM\_OSC\_CNTRL Register Field Descriptions

| Bit     | Field         | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7:5 | SPARE         | R    | 000   |                                                                                                                                                                                                                                                                                                                                                    |

| Bit 4:3 | PWM_FREQ[1:0] | R/W  | 11    | Frequency divider for internally generated PWM signal: 00 : f(PWM) = 23.5KHz 01 : f(PWM) = 11.7KHz 10 : f(PWM) = 5.8KHz 11 : f(PWM) = 2.9KHz                                                                                                                                                                                                       |

| Bit 2   | CLKout_EN     | R/W  | 0     | 0 = CLKOUT is disabled and the output is held LOW 1 = the crystal oscillator is forced ON; CLKOUT is enabled and is switching with the frequency defined by OSC_FREQ[10]; LDO1 needs to be enabled for CLKout being active Please note that the crystal oscillator itself is active once the Bit is set high, independently of the status of LDO1. |