TPS65631W

ZHCSCV3A - JULY 2013-REVISED SEPTEMBER 2014

#### TPS65631W 双输出有源矩阵有机发光二极管 (AMOLED) 显示屏电源

### 特性

- 2.9V 至 4.5V 输入电压范围

- 4.6V 固定正输出电压

- 25℃ 至 85℃ 温度范围内, V<sub>POS</sub> 精度 0.5%

- 单独的 V<sub>POS</sub> 输出感测引脚

- -1.4V 至 -4.4V 的数字可编程负输出电压(缺省值-4V)

- 支持高达 200mA 的输出电流

- 出色的线路瞬态稳压

- 短路保护功能

- 热关断

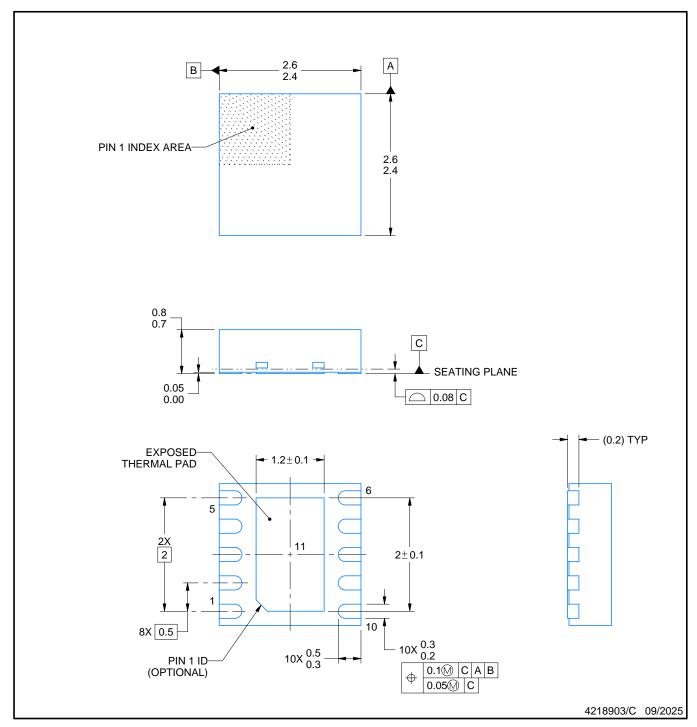

- 采用 2.5mm x 2.5mm 10 引脚四方扁平无引线 (QFN) 封装

- 2 应用范围 AMOLED 显示屏

### 3 说明

TPS65631W 被设计用于驱动需要正负电源轨的 AMOLED 显示屏。 此器件集成了一个针对 V<sub>POS</sub> 的升 压转换器和一个针对 V<sub>NEG</sub> 的反相降压升压转换器,非 常适合于电池供电类产品。 数字控制引脚 (CTRL) 允 许用数字步长设定负输出电压。 TPS65631W 采用创 新技术, 能够实现出色线路瞬态性能。

#### 器件信息の

| 部件号       | 封装       | 封装尺寸 (标称值)      |  |

|-----------|----------|-----------------|--|

| TPS65631W | QFN (10) | 2.50mm x 2.50mm |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

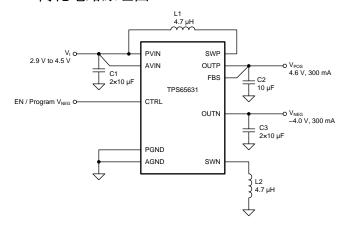

## 简化电路原理图

#### 100 90 80 70 Efficiency (%) 60 50 40 30 20 $V_{POS} = 4.6 \text{ V}$ 10 $V_{NEG} = -4.0 \text{ V}$ $V_1 = 3.7 \text{ V}$

100

Output Current (mA)

125

175

200

150

效率与输出电流间的关系

0

25

50

| 1 | 特性1                                  |    | 8.3 Feature Description         | 8  |

|---|--------------------------------------|----|---------------------------------|----|

| 2 | 应用范围 1                               |    | 8.4 Device Functional Modes     |    |

| 3 |                                      |    | 8.5 Programming                 | 11 |

| 4 | 简化电路原理图1                             | 9  | Applications and Implementation | 12 |

| 5 | 修订历史记录                               |    | 9.1 Application Information     | 12 |

| 6 | Pin Configuration and Functions      |    | 9.2 Typical Application         | 12 |

| 7 | Specifications4                      | 10 | Power Supply Recommendations    | 16 |

| • | 7.1 Absolute Maximum Ratings         | 11 | Layout                          | 17 |

|   | 7.2 Handling Ratings                 |    | 11.1 Layout Guidelines          | 17 |

|   | 7.3 Recommended Operating Conditions |    | 11.2 Layout Example             | 17 |

|   | 7.4 Thermal Information              | 12 | 器件和文档支持                         | 18 |

|   | 7.5 Electrical Characteristics5      |    | 12.1 第三方产品免责声明                  | 18 |

|   | 7.6 Timing Requirements6             |    | 12.2 相关链接                       | 18 |

|   | 7.7 Typical Characteristics          |    | 12.3 商标                         | 18 |

| 8 | Detailed Description 8               |    | 12.4 静电放电警告                     | 18 |

|   | 8.1 Overview 8                       |    | 12.5 术语表                        |    |

|   | 8.2 Functional Block Diagram 8       | 13 | 机械封装和可订购信息                      | 18 |

## 5 修订历史记录

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Original (July 2013) to Revision A

**Page**

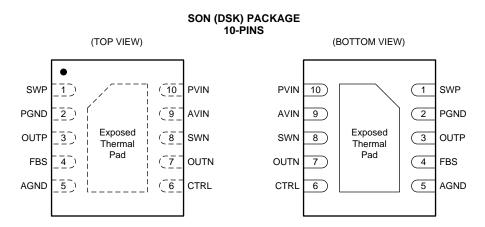

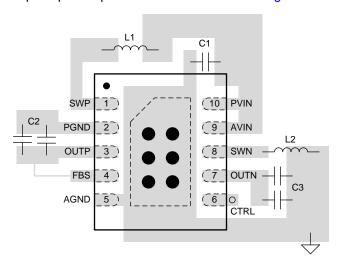

# 6 Pin Configuration and Functions

#### **Pin Functions**

| NAME                   | NO. | I/O | DESCRIPTION                                                                                            |

|------------------------|-----|-----|--------------------------------------------------------------------------------------------------------|

| AGND                   | 5   | _   | Analog ground.                                                                                         |

| AVIN                   | 9   | _   | Input supply voltage for internal analog circuits (both converters).                                   |

| CTRL                   | 6   | I   | Control pin. Combined device enable and inverting buck-boost converter output voltage programming pin. |

| FBS                    | 4   | 1   | Feedback sense pin of the boost converter output voltage.                                              |

| PGND                   | 2   | _   | Power ground of the boost converter.                                                                   |

| PVIN                   | 12  | _   | Input supply voltage pin for the inverting buck-boost converter.                                       |

| SWN                    | 8   | 0   | Switch pin of the inverting buck-boost converter.                                                      |

| SWP                    | 1   | 0   | Switch pin of the boost converter.                                                                     |

| OUTN                   | 7   | 0   | Rectifier pin of the inverting buck-boost converter.                                                   |

| OUTP                   | 3   | 0   | Rectifier pin of the boost converter.                                                                  |

| Exposed Thermal<br>Pad | 13  | _   | Connect this pad to AGND and PGND.                                                                     |

## 7 Specifications

## 7.1 Absolute Maximum Ratings (1)

over operating free-air temperature range (unless otherwise noted) (1)

|                        |                            | MIN  | MAX | UNIT |

|------------------------|----------------------------|------|-----|------|

|                        | SWP, OUTP, FBS, PVIN, AVIN | -0.3 | 6   | V    |

| Input voltage (2)      | OUTN                       | -0.3 | -6  | V    |

|                        | SWN                        | -6   | 6   | V    |

|                        | CTRL                       | -0.3 | 5.5 | V    |

| Operating junction tem | -40                        | 150  | °C  |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) With respect to AGND pin.

## 7.2 Handling Ratings

|                  |                         |                                                                               | MIN  | MAX | UNIT |

|------------------|-------------------------|-------------------------------------------------------------------------------|------|-----|------|

| T <sub>STG</sub> | Storage temperature ran | nge                                                                           | -65  | 150 | Ô    |

|                  |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | -2   | 2   | kV   |

| V <sub>ESD</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -500 | 500 | V    |

|                  |                         | Machine model (MM) ESD stress voltage                                         | -200 | 200 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                            | MIN              | NOM  | MAX | UNIT |    |  |

|-----------------------|------------------------------------------------------|------------------|------|-----|------|----|--|

| $V_{I}$               | Input supply voltage range                           |                  | 2.9  | 3.7 | 4.5  | V  |  |

| V O dand and language |                                                      | V <sub>POS</sub> |      | 4.6 |      | ., |  |

| VO                    | V <sub>O</sub> Output voltage range V <sub>NEG</sub> |                  | -4.4 | -4  | -1.4 | V  |  |

|                       | Output ourrent range                                 | I <sub>POS</sub> | 0    |     | 200  |    |  |

| IO                    | Output current range                                 | I <sub>NEG</sub> | 0    |     | 200  | mA |  |

| $T_A$                 | Operating ambient temperature                        |                  | -40  | 25  | 85   | °C |  |

| $T_{J}$               | Operating junction temperature                       |                  | -40  | 85  | 125  | C  |  |

#### 7.4 Thermal Information

|                      | TUEDMAL METRIC(1)                            | DSK     |        |

|----------------------|----------------------------------------------|---------|--------|

|                      | THERMAL METRIC <sup>(1)</sup>                | 10 PINS | UNIT   |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 47.1    |        |

| R <sub>0</sub> JCtop | Junction-to-case (top) thermal resistance    | 57.8    |        |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 21.1    | °C /\/ |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.8     | °C/W   |

| ΨЈВ                  | Junction-to-board characterization parameter | 21.4    |        |

| R <sub>0JCbot</sub>  | Junction-to-case (bottom) thermal resistance | 4.3     |        |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process...

## 7.5 Electrical Characteristics

$V_I = 3.7$  V,  $V_{(CTRL)} = 3.7$  V,  $V_{POS} = 4.6$  V,  $V_{NEG} = -4.0$  V,  $T_J = -40^{\circ}C$  to 125°C, typical values are at  $T_J = 25^{\circ}C$  (unless otherwise noted)

|                     | PARAMETER                                        | TEST CONDITIONS                                     | MIN   | TYP   | MAX  | UNIT         |

|---------------------|--------------------------------------------------|-----------------------------------------------------|-------|-------|------|--------------|

| SUPPLY              |                                                  |                                                     |       |       |      |              |

| l <sub>l</sub>      | Shutdown current into AVIN and PVIN              | CTRL pin connected to ground.                       |       | 0.1   |      | μΑ           |

| V <sub>UVLO</sub>   | Undervoltage lockout threshold                   |                                                     |       |       | 2.4  | V            |

| BOOST C             | CONVERTER                                        | ·   ·g.                                             |       |       |      |              |

|                     | Output voltage                                   |                                                     |       | 4.6   |      | V            |

| Vo                  | - Carpar renage                                  | 25°C ≤ T <sub>J</sub> ≤ 85°C, no load               | -0.5% | 0     | 0.5% | <del>`</del> |

| -0                  | Output voltage tolerance                         | -40°C ≤ T <sub>J</sub> < 85°C, no load              | -0.8% |       | 0.8% |              |

|                     | Switch (low-side) on-resistance                  | I <sub>(SWP)</sub> = 200 mA                         |       | 200   |      |              |

| r <sub>DS(ON)</sub> | Rectifier (high-side) on-resistance              | I <sub>(SWP)</sub> = 200 mA                         |       | 350   |      | mΩ           |

|                     | Switching frequency                              | $I_{O} = 200 \text{ mA}$                            |       | 1.7   |      | MHz          |

|                     | Switch current limit                             | Inductor valley current                             | 0.8   | 1     |      | Α            |

|                     | Short-circuit threshold voltage in operation     | V <sub>O</sub> falling                              |       | 4.1   |      | V            |

|                     | Short-circuit detection time during operation    |                                                     |       | 3     |      | ms           |

|                     | Output sense threshold voltage using OUTP        | V <sub>(OUTP)</sub> - V <sub>(FBS)</sub> increasing |       | 300   |      | mV           |

|                     | Output sense threshold voltage using FBS         | V <sub>(OUTP)</sub> - V <sub>(FBS)</sub> decreasing |       | 200   |      | mV           |

|                     | Input resistance of FBS                          | Between FBS pin and ground                          |       | 4     |      | ΜΩ           |

|                     | Discharge resistance                             | CTRL pin connected to ground, $I_O = 1 \text{ mA}$  |       | 30    |      | Ω            |

|                     | Line regulation                                  | I <sub>O</sub> = 200 mA                             |       | 0.002 |      | %/V          |

|                     | Load regulation                                  |                                                     |       | 0.01  |      | %/A          |

| INVERTIN            | NG BUCK-BOOST CONVERTER                          |                                                     |       |       |      |              |

|                     | Output voltage default                           |                                                     |       | -4.0  |      |              |

| Vo                  | Output voltage range                             |                                                     | -4.4  |       | -1.4 | V            |

|                     | Output voltage tolerance                         |                                                     | -0.05 |       | 0.05 |              |

| r                   | Switch (high-side) on-resistance                 | I <sub>(SWN)</sub> = 200 mA                         |       | 200   |      | mΩ           |

| r <sub>DS(ON)</sub> | Rectifier (low-side) on-resistance               | I <sub>(SWN)</sub> = 200 mA                         |       | 300   |      | 11132        |

|                     | Switching frequency                              | I <sub>O</sub> = 10 mA                              |       | 1.7   |      | MHz          |

|                     | Switch current limit                             | V <sub>I</sub> = 2.9 V                              | 1.5   | 2.2   |      | Α            |

|                     | Short-circuit threshold voltage during operation | Voltage drop from nominal V <sub>O</sub>            |       | 500   |      | mV           |

|                     | Short-circuit threshold voltage during start-up  |                                                     | 180   | 200   | 230  | 111.V        |

| t <sub>SCP</sub>    | Short-circuit detection time during start-up     |                                                     |       | 10    |      | ms           |

|                     | Short-circuit detection time during operation    |                                                     |       | 3     |      | ms           |

|                     | Discharge resistance                             | CTRL pin connected to ground, $I_O = 1 \text{ mA}$  |       | 150   |      | Ω            |

|                     | Line regulation                                  | I <sub>O</sub> = 200 mA                             |       | 0.006 |      | %/V          |

|                     | Load regulation                                  |                                                     |       | 0.31  |      | %/A          |

# **Electrical Characteristics (continued)**

$V_I = 3.7 \text{ V}, \ V_{(CTRL)} = 3.7 \text{ V}, \ V_{POS} = 4.6 \text{ V}, \ V_{NEG} = -4.0 \text{ V}, \ T_J = -40 ^{\circ}\text{C}$  to 125  $^{\circ}\text{C}$ , typical values are at  $T_J = 25 ^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER          |                              | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |

|--------------------|------------------------------|-----------------|-----|-----|-----|------|--|

| CTRL               | CTRL                         |                 |     |     |     |      |  |

|                    | High-level threshold voltage |                 |     |     | 1.2 | V    |  |

|                    | Low-level threshold voltage  |                 | 0.4 |     |     | V    |  |

|                    | Pull-down resistance         |                 | 150 | 400 | 860 | kΩ   |  |

| OTHER              |                              |                 |     |     | ·   |      |  |

| t <sub>INIT</sub>  | Initialization time          |                 |     | 300 | 400 | μs   |  |

| t <sub>OFF</sub>   | Shut-down time               |                 | 30  |     | 80  | μs   |  |

| t <sub>STORE</sub> | Data storage time            |                 | 30  |     | 80  | μs   |  |

| T <sub>SD</sub>    | Thermal shutdown temperature |                 |     | 145 |     | °C   |  |

# 7.6 Timing Requirements

|                   |                           | MIN | TYP | MAX | UNIT |

|-------------------|---------------------------|-----|-----|-----|------|

| CTRL In           | nterface                  |     |     |     |      |

| t <sub>HIGH</sub> | High-level pulse duration | 2   | 10  | 25  | μs   |

| $t_{LOW}$         | Low-level pulse duration  | 2   | 10  | 25  | μs   |

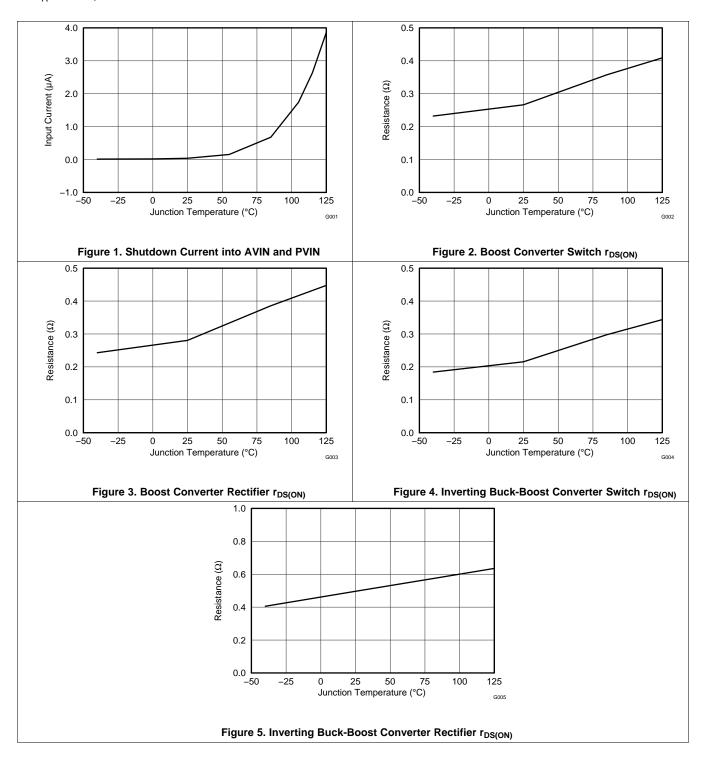

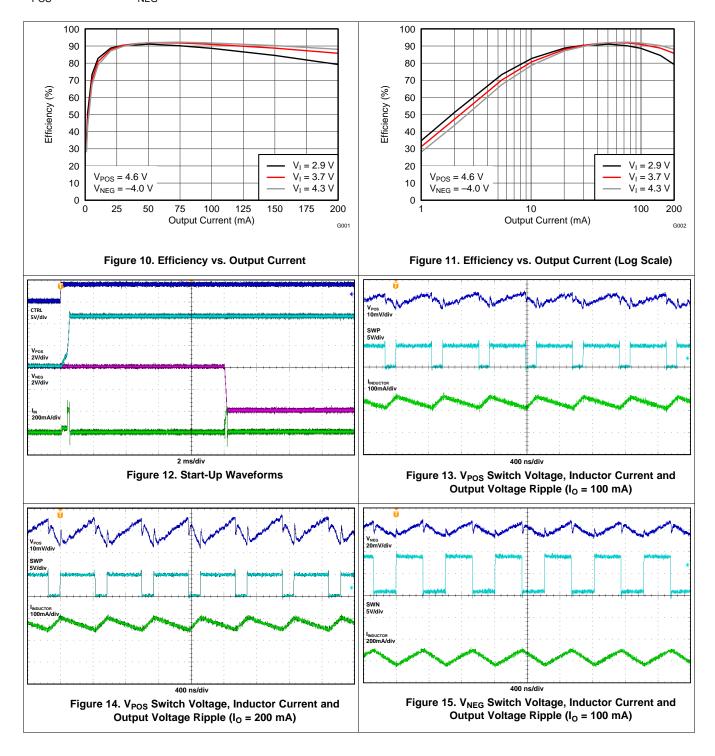

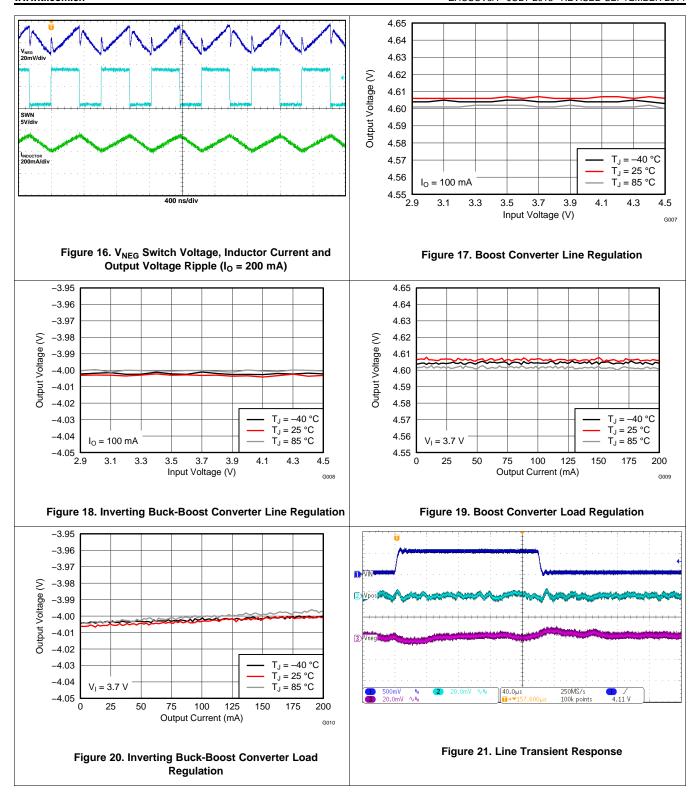

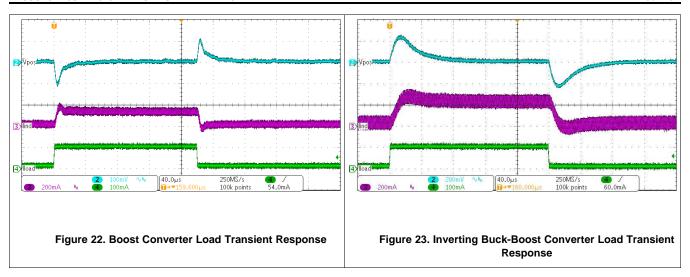

## 7.7 Typical Characteristics

At  $T_A = 25$ °C, unless otherwise noted.

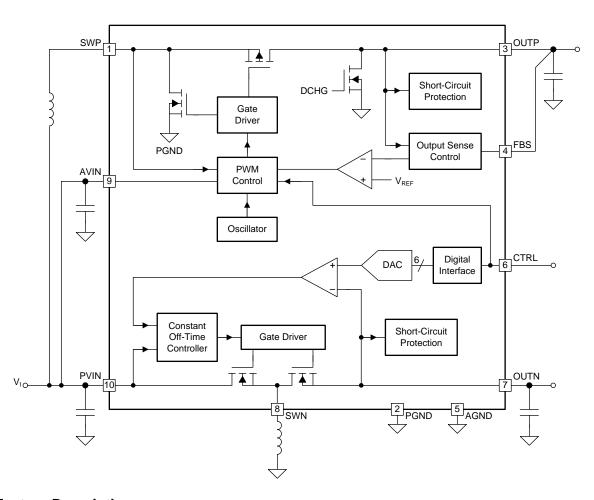

## 8 Detailed Description

#### 8.1 Overview

The TPS65631W consists of a boost converter and an inverting buck boost converter. The  $V_{POS}$  output is fixed at 4.6 V and  $V_{NEG}$  output is programmable via a digital interface in the range of -1.4 V  $\sim$  -4.4 V, the default is -4 V. The transition time of  $V_{NEG}$  output is adjustable by the CT pin capacitor.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Boost Converter

The boost converter uses a fixed-frequency current-mode topology, and its output voltage (V<sub>POS</sub>) is fixed at 4.6 V

For the highest output voltage accuracy, connect the output sense pin (FBS) directly to the positive pin of the output capacitor. If not used, the FBS pin can be left floating or connected to ground. If the FBS pin is not used, the boost converter senses its output voltage using the OUTP pin.

#### 8.3.2 Inverting Buck-Boost Converter

The inverting buck-boost converter uses a constant-off-time peak-current mode topology. The converter's default output voltage ( $V_{NEG}$ ) is -4 V, but it can be programmed to any voltage in the range -1.4 V to -4.4 V (see *Programming V\_{NEG}*).

### **Feature Description (continued)**

#### 8.3.3 Soft-Start and Start-Up Sequence

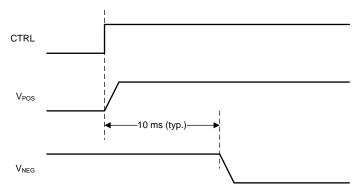

The TPS65631W features a soft-start function to limit inrush current. When the device is enabled by a high-level signal applied to the CTRL pin, the boost converter starts switching with a reduced switch current limit. Ten milliseconds after the CTRL pin goes high, the inverting buck-boost converter starts with a default value of –4 V. A typical start-up sequence is shown in Figure 6.

Figure 6. Typical Start-Up Sequence

### 8.3.4 Enable (CTRL)

The CTRL pin serves two functions. One is to enable and disable the device, and the other is to program the output voltage ( $V_{NEG}$ ) of the inverting buck-boost converter (see *Programming V\_{NEG}*). If the digital interface is not required, the CTRL pin can be used as a standard enable pin for the device, which will come up with its default value on  $V_{NEG}$  of -4 V. When CTRL is pulled high, the device is enabled. The device is shut down with CTRL low.

#### 8.3.5 Undervoltage Lockout

The TPS65631W features an undervoltage lockout function that disables the device when the input supply voltage is too low for normal operation.

#### 8.3.6 Short Circuit Protection

The TPS65631W is protected against short-circuits of V<sub>POS</sub> and V<sub>NEG</sub> to ground and to each other.

#### 8.3.6.1 Short-Circuits During Normal Operation

During normal operation an error condition is detected if  $V_{POS}$  falls below 4.1 V for more than 3 ms or  $V_{NEG}$  is pulled above the programmed nominal output by 500 mV for longer than 3 ms. In either case the device enters shutdown mode: the converters are disabled and their outputs are disconnected from the input. To resume normal operation either cycle the input supply voltage or toggle the CTRL pin low and then high again.

#### 8.3.6.2 Short-Circuits During Start-Up

During start up an error condition is detected if:

- V<sub>POS</sub> is not in regulation 10 ms after a high-level is applied to the CTRL pin.

- V<sub>NEG</sub> is higher than threshold level 10 ms after a high-level is applied to the CTRL pin.

- V<sub>NEG</sub> is not in regulation 20 ms after a high-level is applied to the CTRL pin.

To resume normal operation either cycle the input supply voltage or toggle the CTRL pin low and then high again.

#### 8.3.7 Output Discharge During Shutdown

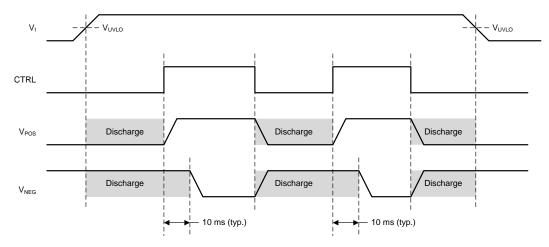

The TPS65631W actively discharges its outputs during shutdown. Figure 7 shows the output discharge control.

### **Feature Description (continued)**

Figure 7. Active Discharge of V<sub>POS</sub> and V<sub>NEG</sub> During Shutdown

#### 8.3.8 Thermal Shutdown

The TPS65631W enters thermal shutdown mode if its junction temperature exceeds 145°C (typical). During thermal shutdown mode none of the device functions are available. To resume normal operation, either cycle the input supply voltage or toggle the CTRL pin low and then high again.

#### 8.4 Device Functional Modes

#### 8.4.1 Operation with $V_1 < 2.9 \text{ V}$

The recommended minimum input supply voltage for full performance is 2.9 V. The device continues to operate with input supply voltages below 2.9 V; however, full performance is not guaranteed. The device does not operate with input supply voltages below the UVLO threshold.

#### 8.4.2 Operation with $V_I \approx V_{POS}$ (Diode Mode)

The TPS65631W features a "diode" mode that enables it to regulate its output voltage even when the input supply voltage is close to  $V_{POS}$  (that is, too high for normal boost operation). When operating in diode mode the converter's high-side switch stops switching and its body diode is used as the rectifier. Boost converter efficiency is reduced when operating in diode mode. At low output currents ( $\approx$ 2 mA and below), the boost converter automatically transitions from pulse-width modulation to pulse-skip mode. This ensures that  $V_{POS}$  stays in regulation but increases the output voltage ripple on  $V_{POS}$ .

#### 8.4.3 Operation with CTRL

When a low-level signal is applied to the CTRL pin the device is disabled and switching is inhibited. When the input supply voltage is above the UVLO threshold and a high-level signal is applied to the CTRL pin the device is enabled and its start-up sequence begins.

### 8.5 Programming

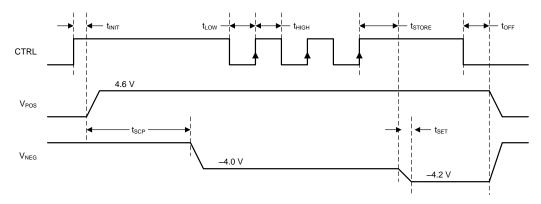

## 8.5.1 Programming V<sub>NEG</sub>

The output voltage of the inverting buck-boost converter ( $V_{NEG}$ ) can be programmed using the CTRL pin. If output voltage programming is not required, the CTRL pin can be used as a standard enable pin (see *Enable (CTRL)*).

Figure 8. Programming V<sub>NEG</sub> Using the CTRL Pin

When the CTRL pin is pulled high, the inverting buck-boost converter starts up with its default voltage of -4V. The device now counts the rising edges applied to the CTRL pin and sets the output voltage ( $V_{NEG}$ ) according to Table 1. For the timing diagram shown in Figure 8,  $V_{NEG}$  is programmed to -4.2 V, since three rising edges are detected.

The CTRL interface is designed to work with pulses whose duration is between 2  $\mu$ s and 25  $\mu$ s. Pulses shorter than 2  $\mu$ s or longer than 25  $\mu$ s are not ensured to be recognized.

| Number of Rising Edges | V <sub>NEG</sub> | Number of Rising Edges | V <sub>NEG</sub> |

|------------------------|------------------|------------------------|------------------|

| 0 / no pulses          | -4 V             | 16                     | -2.9 V           |

| 1                      | -4.4 V           | 17                     | -2.8 V           |

| 2                      | -4.3 V           | 18                     | −2.7 V           |

| 3                      | -4.2 V           | 19                     | -2.6 V           |

| 4                      | -4.1 V           | 20                     | –2.5 V           |

| 5                      | -4.0 V           | 21                     | -2.4 V           |

| 6                      | −3.9 V           | 22                     | -2.3 V           |

| 7                      | –3.8 V           | 23                     | -2.2 V           |

| 8                      | −3.7 V           | 24                     | –2.1 V           |

| 9                      | −3.6 V           | 25                     | -2.0 V           |

| 10                     | –3.5 V           | 26                     | –1.9 V           |

| 11                     | -3.4 V           | 27                     | -1.8 V           |

| 12                     | −3.3 V           | 28                     | -1.7 V           |

| 13                     | −3.2 V           | 29                     | -1.6 V           |

| 14                     | –3.1 V           | 30                     | −1.5 V           |

| 15                     | -3.0 V           | 31                     | -1.4 V           |

Table 1. Programming Table for V<sub>NEG</sub>

## 9 Applications and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

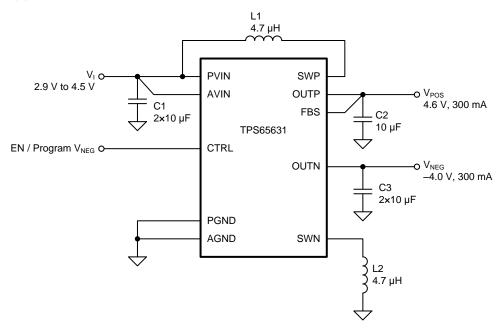

### 9.1 Application Information

Figure 9 shows a typical application circuit suitable for supplying AMOLED displays in smartphone applications. The circuit is designed to operate from a single-cell Li-lon battery and generates a positive output voltage  $V_{POS}$  of 4.6 V and a negative output voltage of -4 V. Both outputs are capable of supplying up to 300 mA of output current.

## 9.2 Typical Application

Figure 9. Typical Application Schematic

### 9.2.1 Design Requirements

For this design example, use the following input parameters.

**Table 2. Design Parameters**

| DESIGN PARAMETER    | EXAMPLE                             |

|---------------------|-------------------------------------|

| Input voltage range | 2.9 V to 4.5 V                      |

| Output voltage      | $V_{POS} = 4.6V$ , $V_{NEG} = -4 V$ |

#### 9.2.2 Detailed Design Procedure

In order to maximize performance, the TPS65631W has been optimized for use with a relatively narrow range of component values, and customers are strongly recommended to use the application circuit shown in Figure 9 with the components listed in Table 3 and Table 4.

#### 9.2.2.1 Inductor Selection

The boost converter and inverting buck-boost converter have been optimized for use with 10  $\mu$ H inductors, and it is recommended that this value be used in all applications. Customers using other values of inductor are strongly recommended to characterize circuit performance on a case-by-case basis.

Table 3. Inductor Selection (1)

| PARAMETER | VALUE | MANUFACTURER | PART NUMBER     |  |

|-----------|-------|--------------|-----------------|--|

|           |       | Toko         | DFE252012C-100M |  |

| L1, L2    | 10 µH | ABCO         | LPP252012-100M  |  |

|           |       | Taiyo Yuden  | MDKK2020T-100M  |  |

<sup>(1)</sup> See Third-Party Products Disclaimer

#### 9.2.2.2 Capacitor Selection

The recommended capacitor values are shown in Table 4. Applications using less than the recommended capacitance (e.g. to save PCB area) may experience increased voltage ripple. In general, the lower the output power, the lower the necessary capacitance.

Table 4. Capacitor Selection<sup>(1)</sup>

| PARAMETER | VALUE     | MANUFACTURER | PART NUMBER       |

|-----------|-----------|--------------|-------------------|

| C1        | 2 × 10 µF | Murata       | GRM21BR71A106KE51 |

| C2        | 10 μF     | Murata       | GRM21BR71A106KE51 |

| C3        | 2 × 10 µF | Murata       | GRM21BR71A106KE51 |

| C4        | 100 nF    | Murata       | GRM21BR71E104KA01 |

<sup>(1)</sup> See Third-Party Products Disclaimer

### 9.2.2.3 Stability

Applications using component values that differ significantly from those recommended in Table 3 and Table 4 should be checked for stability over the full range of operating conditions.

#### 9.2.3 Application Curves

The performance shown in the following graphs was obtained using the circuit shown in Figure 9 and the external components shown in Table 3 and Table 4. The output voltage settings for these measurements were  $V_{POS} = 4.6 \text{ V}$  and  $V_{NFG} = -4 \text{ V}$ .

# 10 Power Supply Recommendations

The TPS65631W is designed to operate from an input voltage supply range between 2.9 V and 4.5 V. If the input supply is located more than a few centimeters from the TPS65631W additional bulk capacitance may be required. The  $2\times10~\mu\text{F}$  shown in the schematics in this data sheet are a typical choice for this function.

## 11 Layout

### 11.1 Layout Guidelines

No PCB layout is perfect and compromises are always necessary. However, following the basic principles listed below (in order of importance) should go a long way to achieving good performance:

- Route switching currents on the top layer using short, wide traces. Do not route these signals through vias, which have relatively high parasitic inductance and resistance.

- Use a copper pour on layer 2 as a ground plane and thermal spreader, and connect the thermal pad to it using a number of thermal vias.

- Place C1 as close as possible to pin 10.

- Place C2 as close as possible to pins 2 and 3.

- Place C3 as close as possible to pin 7.

- Place L1 as close as possible to pin 1.

- Place L2 as close as possible to pin 10.

- Use the thermal pad to join AGND and PGND.

- Connect the FBS pin directly to the positive pin of C2, that is, keep this connection separate from the connection between OUTP and C2.

Figure 24 illustrates how a PCB layout following the above principles may be realized in practice.

## 11.2 Layout Example

Figure 24 shows the above principles implemented for the circuit of Figure 9.

- Via to signal layer on internal or bottom layer.

- Thermal via to copper pour on internal or bottom layer.

Figure 24. PCB Layout Example

### 12 器件和文档支持

### 12.1 第三方产品免责声明

TI 发布的与第三方产品或服务有关的信息,不能构成与此类产品或服务或保修的适用性有关的认可,不能构成此类产品或服务单独或与任何 TI 产品或服务一起的表示或认可。

### 12.2 相关链接

以下表格列出了快速访问链接。 范围包括技术文档、支持与社区资源、工具和软件,并且可以快速访问样片或购买链接。

#### 表 5. 相关链接

| 部件        | 产品文件夹 | 样片与购买 | 技术文档  | 工具与软件 | 支持与社区 |

|-----------|-------|-------|-------|-------|-------|

| TPS65631W | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

### 12.3 商标

All trademarks are the property of their respective owners.

#### 12.4 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 12.5 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、首字母缩略词和定义。

### 13 机械封装和可订购信息

以下页中包括机械封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com 10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |                 | (4)                           | (5)                        |              |                  |

| TPS65631WDSKR         | Active | Production    | SON (DSK)   10 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | SJN              |

| TPS65631WDSKR.A       | Active | Production    | SON (DSK)   10 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | SJN              |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

PACKAGE MATERIALS INFORMATION

www.ti.com 8-Jun-2019

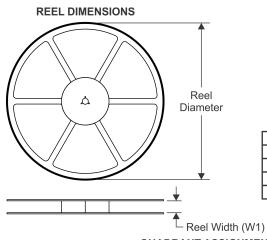

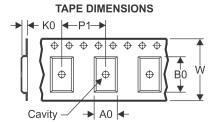

## TAPE AND REEL INFORMATION

| A0 |                                                           |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

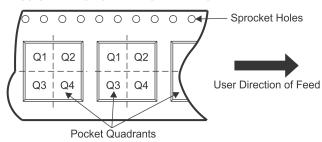

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS65631WDSKR | SON             | DSK                | 10 | 3000 | 180.0                    | 8.4                      | 2.8        | 2.8        | 1.0        | 4.0        | 8.0       | Q2               |

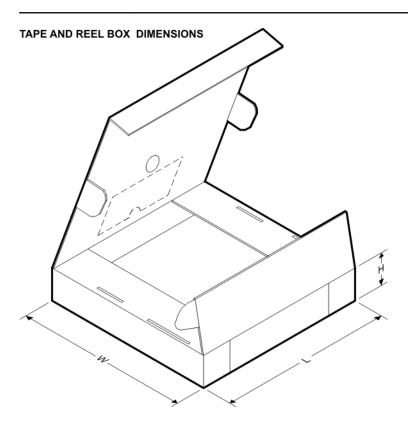

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 8-Jun-2019

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS65631WDSKR | SON          | DSK             | 10   | 3000 | 182.0       | 182.0      | 20.0        |

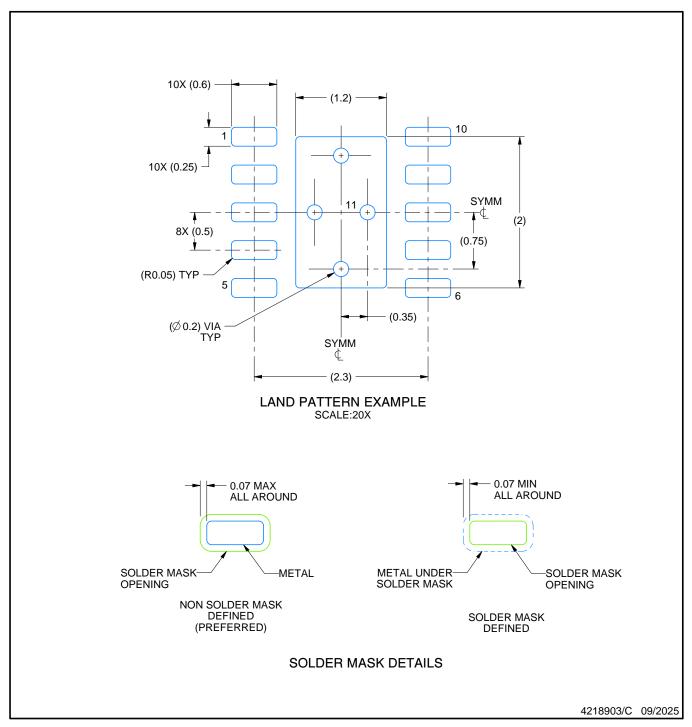

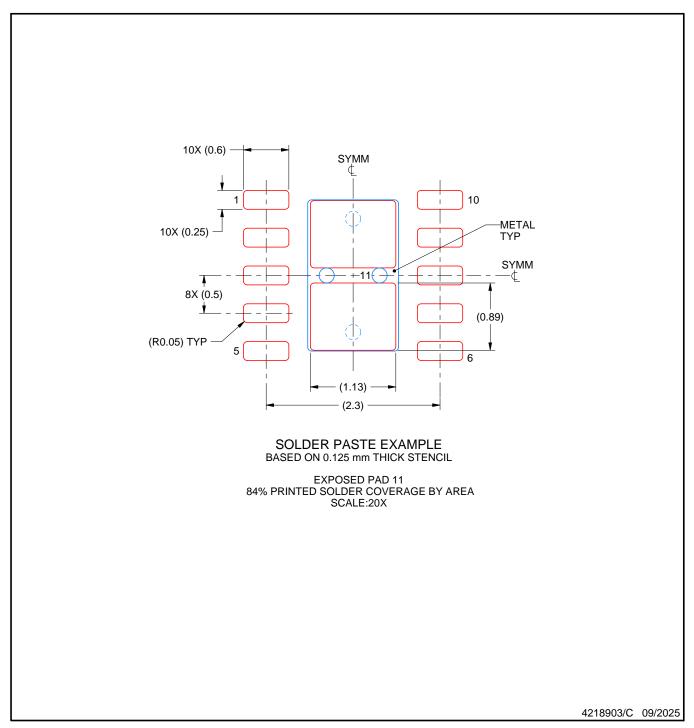

2.5 x 2.5 mm, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4225304/A

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月