TPS65219-Q1

ZHCSNP4A - DECEMBER 2022 **REVISED MAY 2023**

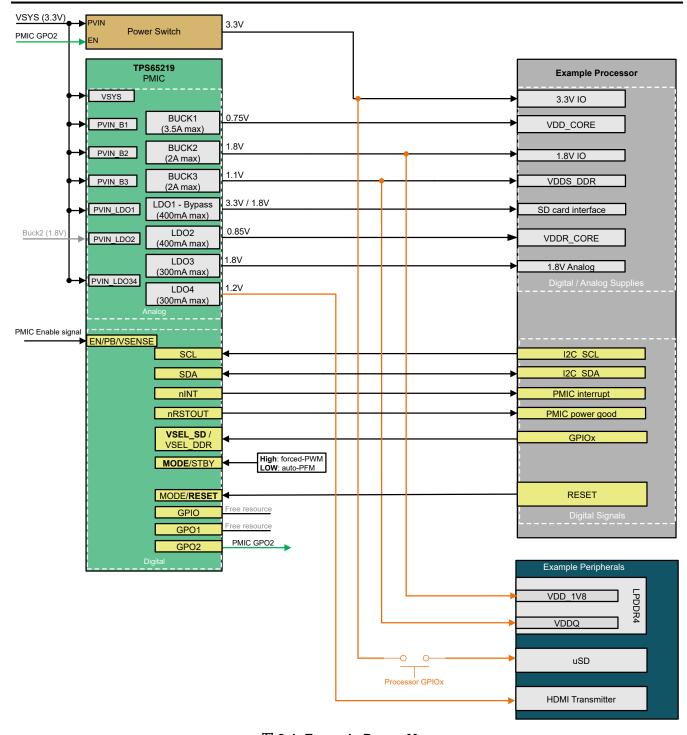

## TPS65219-Q1 适用于 ARM Cortex®—A53 处理器

#### 1 特性

- 3 个高达 2.3MHz 非固定开关频率或固定频率模式 的降压转换器:

- 1  $\uparrow$  VIN : 2.5V 5.5V ; I<sub>OUT</sub> : 3.5A ; V<sub>OUT</sub> 0.6V - 3.4V

- 2 个 VIN: 2.5V 5.5V; I<sub>OUT</sub>: 2A; V<sub>OUT</sub> 0.6V - 3.4V

- 4 个线性稳压器:

- 2  $\uparrow$  VIN : 1.5V 5.5V ; I<sub>OUT</sub> : 400mA ; V<sub>OUT</sub>: 0.6V - 3.4V (可配置为负载开关和旁路 模式,支持SD卡)

- 2x VIN: 2.2V 5.5V;  $I_{OUT}: 300\text{mA}$ ;  $V_{OUT}:$ 1.2V - 3.3V (可配置为负载开关)

- 所有三个降压转换器上的动态电压调节

- 低 IQ/PFM 的 PWM 模式(准固定频率)或固定频 率模式

- 可编程电源时序和默认电压

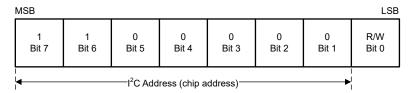

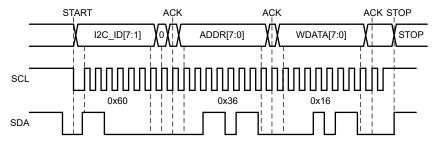

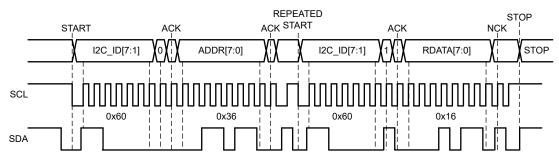

- I<sup>2</sup>C 接口,支持标准模式、快速模式和快速模式增

- 设计为支持具有多达 14 个以上电源轨的系统 (2 个 TPS65219-Q1,每个7个电源轨+GPO控制的外 部电源轨)

- 2 个 GPO、1 个 GPIO 和 3 个多功能引脚

- EEPROM 可编程性

- 提供功能安全

#### 2 应用

- AM62x-Q1 和 AM64x-Q1 等低功耗汽车 MPU

- 音响主机、数字仪表组、远程信息处理控制单元、 激光雷达处理器

- DMS/OMS、eMirror 和 CMS

- ISP 和深度学习

#### 3 说明

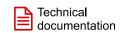

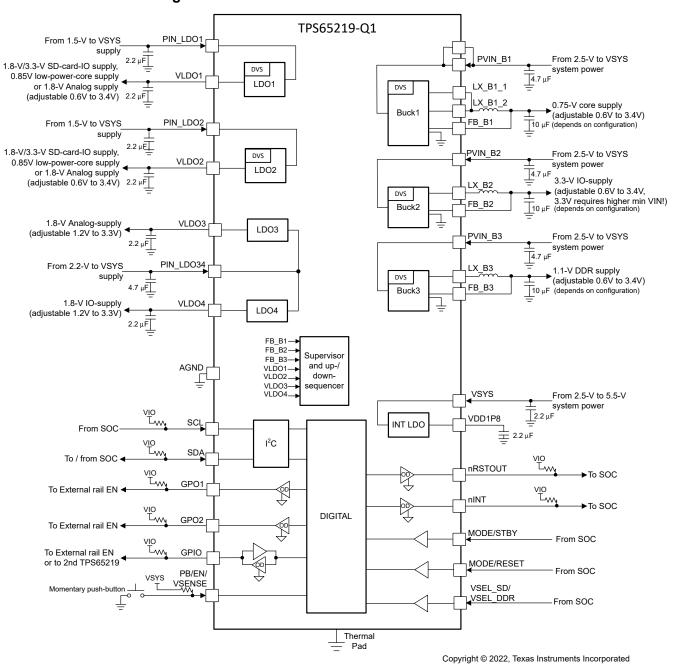

TPS65219-Q1 是一款电源管理 IC (PMIC), 旨在为汽 车应用中的各种 SoC 供电。该 PMIC 的额定环境温度 范围为  $-40^{\circ}$ C 至  $+125^{\circ}$ C,因此适用于汽车应用。该器 件包括三个同步直流/直流降压转换器和四个线性稳压

直流/直流转换器能够提供 1 个 3.5A 电流和 2 个 2A 电 流。这些转换器需要一个 470nH 的小型电感器、一个 4.7μF 的输入电容,以及每个电源轨一个最小 10μF 的输出电容。

其中两个 LDO 在 0.6V 至 3.4V 的输出电压范围内支持 400mA 的输出电流。这些 LDO 支持旁路模式,充当 负载开关,并允许在工作期间改变电压。其他两个 LDO 在 1.2V 至 3.3V 的输出电压范围内支持 300mA 的输出电流。这些 LDO 也支持负载开关模式。

I2C接口、IO、GPIO和多功能引脚 (MFP)可实现与各 种 SoC 的无缝连接。

#### 封装信息(1)

| 器件型号        | 封装             | 封装尺寸(标称值)       |  |  |

|-------------|----------------|-----------------|--|--|

| TPS65219-Q1 | 32 引脚 QFN - 可湿 | 5.00mm × 5.00mm |  |  |

|             | 性侧面            |                 |  |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

## **Table of Contents**

| 1 特性 1                                     | 7 Detailed Description                  | 29  |

|--------------------------------------------|-----------------------------------------|-----|

|                                            | 7.1 Overview                            |     |

| 3 说明                                       | 7.2 Functional Block Diagram            | 30  |

| 4 Revision History2                        | 7.3 Feature Description                 |     |

| 5 Pin Configuration and Functions3         | 7.4 Device Functional Modes             | 55  |

| 6 Specifications7                          | 7.5 User Registers                      | 61  |

| 6.1 Absolute Maximum Ratings7              | 7.6 Device Registers                    | 62  |

| 6.2 ESD Ratings7                           | 8 Application and Implementation        | 138 |

| 6.3 Recommended Operating Conditions7      | 8.1 Application Information             | 138 |

| 6.4 Thermal Information9                   | 8.2 Typical Application                 | 138 |

| 6.5 System Control Thresholds9             | 8.3 Application Curves                  | 143 |

| 6.6 BUCK1 Converter                        | 8.4 Power Supply Recommendations        | 145 |

| 6.7 BUCK2, BUCK3 Converter                 | 8.5 Layout                              |     |

| 6.8 General Purpose LDOs (LDO1, LDO2)      | 9 Device and Documentation Support      | 147 |

| 6.9 General Purpose LDOs (LDO3, LDO4)      | 9.1 Documentation Support               | 147 |

| 6.10 GPIOs and multi-function pins (EN/PB/ | 9.2 接收文档更新通知                            | 147 |

| VSENSE, nRSTOUT, nINT, GPO1, GPO2, GPIO,   | 9.3 支持资源                                | 147 |

| MODE/RESET, MODE/STBY, VSEL SD/            | 9.4 Trademarks                          | 147 |

| VSEL DDR)21                                | 9.5 静电放电警告                              | 147 |

| 6.11 Voltage and Temperature Monitors23    | 9.6 术语表                                 |     |

| 6.12 I <sup>2</sup> C Interface24          | 10 Mechanical, Packaging, and Orderable |     |

| 6.13 Typical Characteristics27             | Information                             | 148 |

## **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| CI | hanges from R | Revision * (D | ecembe | r 2022) to R | Revision A (May 2023) | Page |

|----|---------------|---------------|--------|--------------|-----------------------|------|

| •  | 将器件状态从        | "预告信息"        | 更改为'   | "量产数据"       |                       | 1    |

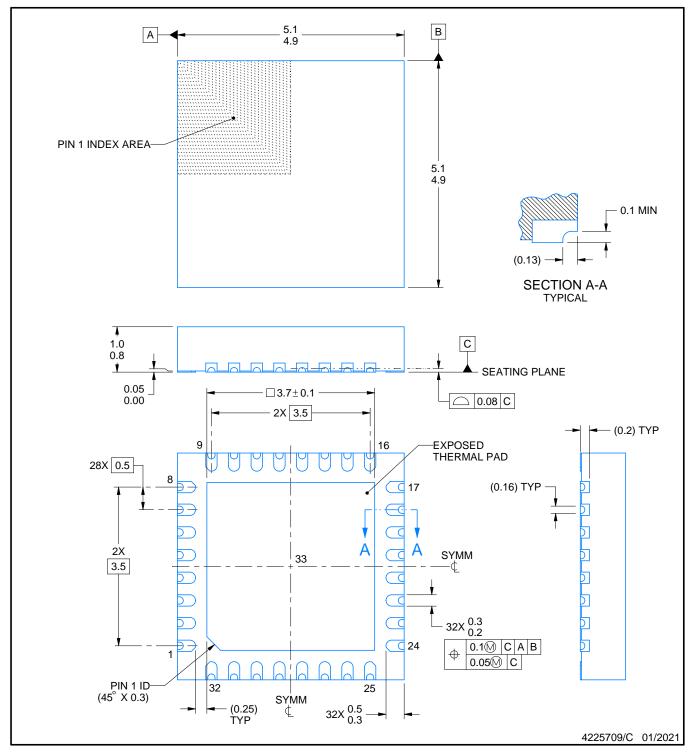

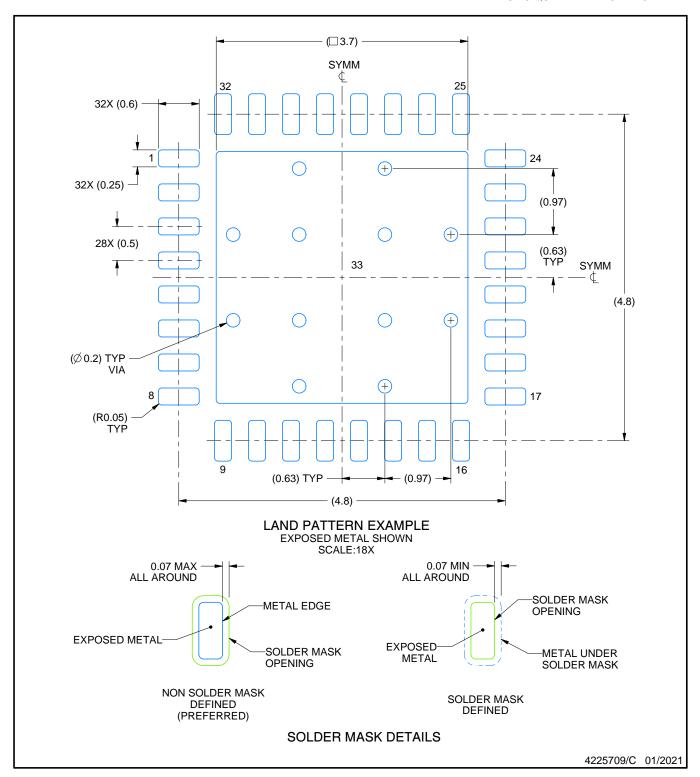

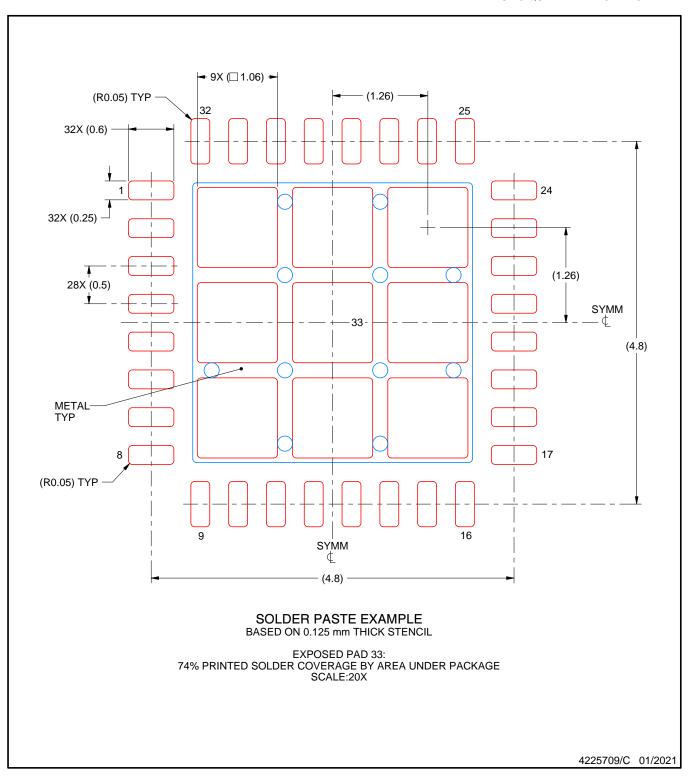

## **5 Pin Configuration and Functions**

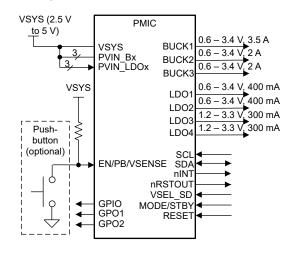

图 5-1. RHB Package, 32-pin QFN (Top View)

表 5-1. Pin Functions

| PIN NAME  | PIN NO. | TYPE | DESCRIPTION                                                                                                                                                     | CONNECTION if not used<br>(output rails must be<br>permanently disabled) |

|-----------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| FB_B1     | 1       | I    | Feedback Input for Buck1. Connect to Buck1 output filter. Nominal output voltage is configured in EEPROM.                                                       | Connect to GND                                                           |

| LX_B1_1   | 2       | PWR  | Switch Pin for Buck1. Connect one side of the Buck1-inductor to this pin.                                                                                       | Leave floating                                                           |

| LX_B1_2   | 3       | PWR  | 2nd Switch Pin for Buck1. Connect one side of the Buck1-inductor to this pin. Connect to LX_B1_1.                                                               | Leave floating                                                           |

| PVIN_B1_1 | 4       | PWR  | Power Input for BUCK1. Bypass this pin to ground with a 4.7 $\mu$ F or greater ceramic capacitor. Voltage on PVIN_B1_1 pin must not exceed voltage on VSYS pin. | Connect to VSYS                                                          |

| PVIN_B1_2 | 5       | PWR  | 2nd Power Input for BUCK1. This pin shares the bypass capacitor from pin 4. Voltage on PVIN_B1_2 pin must not exceed voltage on VSYS pin.                       | Connect to VSYS                                                          |

| PVIN_LDO1 | 6       | PWR  | Power Input for LDO1. Voltage on PVIN_LDO1 pin must not exceed voltage on VSYS pin.                                                                             | Connect to VSYS                                                          |

| VLDO1     | 7       | PWR  | Output Voltage of LDO1. Nominal output voltage is configured in EEPROM. Bypass this pin to ground with a 2.2 µF or greater ceramic capacitor.                   | Leave floating                                                           |

| GPO1      | 8       | 0    | General Purpose Open-Drain Output. Configurable in the power-up and power-down-sequence to enable an external rail.                                             | Leave floating                                                           |

| SDA       | 9       | I/O  | Data Pin for the I2C Serial Port. The I2C logic levels depend on the external pull-up voltage.                                                                  | Connect to VIO                                                           |

## 表 5-1. Pin Functions (continued)

| PIN NAME             | PIN NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                       | CONNECTION if not used<br>(output rails must be<br>permanently disabled) |

|----------------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| SCL                  | 10      | I    | Clock Pin for the I2C Serial Port. The I2C logic levels depend on the external pull-up voltage.                                                                                                                                                                                                                                   | Connect to VIO                                                           |

| nINT                 | 11      | 0    | Interrupt Request Output. Open-drain driver is pulled low for fault conditions. Released if bit is cleared                                                                                                                                                                                                                        | Leave floating                                                           |

| VSEL_SD/<br>VSEL_DDR | 12      | I    | Multi-Function-Pin: Configured as VSEL_SD: SD-card-IO-voltage select. Connected to SoC. Trigger a voltage change between 1.8 V and register-based VOUT on LDO1 or LDO2. Polarity is configurable. Configured as VSEL_DDR: DDR-voltage selection. Hard-wired pull-up (1.35 V), pull-down (register based VOUT) or floating (1.2 V) | n/a (connect to GND)                                                     |

| VSYS                 | 13      | PWR  | Input supply pin for reference system. Bypass this pin to ground with a 2.2 µF or greater ceramic capacitor (can be shared with PVIN-capacitors).                                                                                                                                                                                 | n/a                                                                      |

| VDD1P8               | 14      | PWR  | Internal Reference Voltage: For Internal Use Only. Bypass this pin to ground with a 2.2 µF or greater ceramic capacitor.                                                                                                                                                                                                          | n/a                                                                      |

| AGND                 | 15      | GND  | Ground pin for Analog GND                                                                                                                                                                                                                                                                                                         | n/a                                                                      |

| GPIO                 | 16      | I/O  | GPO-configuration: General Purpose Open-Drain Output. Configurable in the power-up and power-down-sequence to enable an external rail. GPIO-configuration: Synchronizing I/O. Used to synchronize two or more TPS65219-Q1. The pin is level-sensitive.                                                                            | Leave floating                                                           |

| GPO2                 | 17      | 0    | General Purpose Open-Drain Output. Configurable in the power-up and power-down-sequence to enable an external rail.                                                                                                                                                                                                               | Leave floating                                                           |

| nRSTOUT              | 18      | 0    | Reset-output to SoC. Controlled by sequencer.<br>High in ACTIVE and STBY state.                                                                                                                                                                                                                                                   | Leave floating                                                           |

| VLDO2                | 19      | PWR  | Output Voltage of LDO2. Nominal output voltage is configured in EEPROM. Bypass this pin to ground with a 2.2 µF or greater ceramic capacitor.                                                                                                                                                                                     | Leave floating                                                           |

| PVIN_LDO2            | 20      | PWR  | Power Input for LDO2. Bypass this pin to ground with a 2.2 $\mu$ F or greater ceramic capacitor. Voltage on PVIN_LDO2 pin must not exceed voltage on VSYS pin.                                                                                                                                                                    | Connect to VSYS                                                          |

| VLDO3                | 21      | PWR  | Output Voltage of LDO3. Nominal output voltage is configured in EEPROM. Bypass this pin to ground with a 2.2 µF or greater ceramic capacitor.                                                                                                                                                                                     | Leave floating                                                           |

| PVIN_LDO34           | 22      | PWR  | Power Input for LDO3 and LDO4. Bypass this pin to ground with a 4.7 $\mu$ F or greater ceramic capacitor. Voltage on PVIN_LDO34 pin must not exceed voltage on VSYS pin.                                                                                                                                                          | Connect to VSYS                                                          |

| VLDO4                | 23      | PWR  | Output Voltage of LDO4. Nominal output voltage is configured in EEPROM.Bypass this pin to ground with a 2.2 µF or greater ceramic capacitor.                                                                                                                                                                                      | Leave floating                                                           |

| FB_B3                | 24      | I    | Feedback Input for Buck3. Connect to Buck3 output filter. Nominal output voltage is configured in EEPROM.                                                                                                                                                                                                                         | Connect to GND                                                           |

## 表 5-1. Pin Functions (continued)

| PIN NAME         | PIN NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CONNECTION if not used<br>(output rails must be<br>permanently disabled)                                  |

|------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| EN/PB/<br>VSENSE | 25      | I    | ON-request input. Configured as EN: Device enable pin, high level is ON-request, low-level is OFF-request. Configured as PB: Push-button monitor input. 600 ms low-level is an ON-request, 8 s low-level is an OFF-request. Configured as VSENSE: Power-fail comparator input. Set sense voltage using a resistor divider connected from the input to the pre-regulator to this pin to ground. Detects rising/falling voltage on pre-regulator and triggers ON- / OFF-request. The pin is edge-sensitive with a wait-time in PB-configuration and deglitch time for EN- and VSENSE-configuration. | n/a (configure as EN and connect<br>to VSYS)                                                              |

| PVIN_B3          | 26      | PWR  | Power Input for BUCK3. Bypass this pin to ground with a 4.7 $\mu$ F or greater ceramic capacitor. Voltage on PVIN_B3 pin must not exceed voltage on VSYS pin.                                                                                                                                                                                                                                                                                                                                                                                                                                     | Connect to VSYS                                                                                           |

| LX_B3            | 27      | PWR  | Switch Pin for Buck3. Connect one side of the Buck3-inductor to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Leave floating                                                                                            |

| MODE/RESET       | 28      | I    | Multi-Function-Pin: Configured as MODE: Connected to SoC or hard-wired pull-up/-down. Forces the Buck-converters into PWM or permits auto-entry in PFM-mode. Configured as RESET: Connected to SoC. Forces a WARM or COLD reset (configurable), WARM reset resetting output voltages to defaults, COLD reset sequencing down all enabled rails and power up again. Polarity is configurable. The pin is level-sensitive for MODE-configuration, edge-sensitive for RESET-configuration.                                                                                                           | n/a (tie high or low, dependent on configuration, see 'PWM/PFM and Reset (MODE/RESET)'                    |

| LX_B2            | 29      | PWR  | Switch Pin for Buck2. Connect one side of the Buck2-inductor to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Leave floating                                                                                            |

| PVIN_B2          | 30      | PWR  | Power Input for BUCK2. Bypass this pin to ground with a 4.7 $\mu$ F or greater ceramic capacitor. Voltage on PVIN_B2 pin must not exceed voltage on VSYS pin.                                                                                                                                                                                                                                                                                                                                                                                                                                     | Connect to VSYS                                                                                           |

| MODE/STBY        | 31      | I    | Multi-Function-Pin: Configured as MODE: Connected to SoC or hard-wired pull-up/-down. Forces the Buck-converters into PWM or permits auto-entry in PFM-mode. Configured as STBY: Low-power-mode command, disables selected rails. Both functions, MODE and STBY, can be combined. The pin is level-sensitive.                                                                                                                                                                                                                                                                                     | n/a (tie high or low, dependent on<br>configuration, see 'PWM/PFM<br>and Low Power Modes (MODE/<br>STBY)' |

| FB_B2            | 32      | I    | Feedback Input for Buck2. Connect to Buck2 output filter. Nominal output voltage is configured in EEPROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Connect to GND                                                                                            |

## 表 5-1. Pin Functions (continued)

| PIN NAME | PIN NO.  | TYPE | DESCRIPTION                                                                                                                                                                                                           | CONNECTION if not used<br>(output rails must be<br>permanently disabled) |

|----------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| PGND     | PowerPad | GND  | Power-Ground. The exposed pad must be connected to a continuous ground plane of the printed circuit board by multiple interconnect vias directly under the TPS65219-Q1 to maximize electrical and thermal conduction. | n/a                                                                      |

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

| POS   |                                       |                                                                 | MIN   | MAX                                | UNIT |

|-------|---------------------------------------|-----------------------------------------------------------------|-------|------------------------------------|------|

| 1.1.1 | Input voltage                         | VSYS                                                            | - 0.3 | 6                                  | V    |

| 1.1.2 | Input voltage                         | PVIN_B1, PVIN_B2, PVIN_B3, PVIN_LDO1, PVIN_LDO2, PVIN_LDO34     | - 0.3 | 6                                  | V    |

| 1.1.3 | Input voltage vs. VSYS for Bucks      | PVIN_B1, PVIN_B2, PVIN_B3 maximum voltage exceeding VSYS        |       | 200                                | mV   |

| 1.1.4 | Input voltage vs. VSYS for LDOs       | PVIN_LDO1, PVIN_LDO2, PVIN_LDO34 maximum voltage exceeding VSYS |       | 20                                 | mV   |

| 1.1.5 | Input voltage                         | FB_B1, FB_B2, FB_B3                                             | - 0.3 | 6                                  | V    |

| 1.1.6 | Input voltage                         | EN/PB/VSENSE, MODE/STBY, MODE/RESET, VSEL_SD/VSEL_DDR           | - 0.3 | 6                                  | V    |

| 1.2.1 | Output voltage                        | LX_B1, LX_B2, LX_B3                                             | - 0.3 | PVIN_Bx + 0.3 V, up to 6 V         | V    |

| 1.2.2 | Output voltage                        | LX_B1, LX_B2, LX_B3 spikes for maximum 10ns                     | - 2   | 10                                 | V    |

| 1.2.3 | Output voltage                        | GPO1, GPO2, GPIO                                                | - 0.3 | 6                                  | V    |

| 1.2.4 | Output voltage                        | VLDO1, VLDO2, VLDO4, VLDO4                                      | - 0.3 | PVIN_LDOx<br>+ 0.3 V, up<br>to 6 V | V    |

| 1.2.5 | Output voltage                        | VDD1P8                                                          | - 0.3 | 2                                  | V    |

| 1.2.6 | Output voltage                        | SDA, SCL                                                        | - 0.3 | 6                                  | V    |

| 1.2.7 | Output voltage                        | nINT, nRSTOUT                                                   | - 0.3 | 6                                  | V    |

| 1.4.1 | Operating junction temperatu          | re, T <sub>J</sub>                                              | -40   | 150                                | °C   |

| 1.4.2 | Storage temperature, T <sub>stg</sub> |                                                                 | -40   | 150                                | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 6.2 ESD Ratings

| POS |                    |                                                  |                                                                                          | VALUE | UNIT |

|-----|--------------------|--------------------------------------------------|------------------------------------------------------------------------------------------|-------|------|

| 2.1 | V <sub>(ESD)</sub> | Electrostatic discharge, Human Body<br>Model     | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, all pins <sup>(1)</sup>          | ±2000 | V    |

| 2.2 | V <sub>(ESD)</sub> | Electrostatic discharge, Charged Device<br>Model | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

| POS   |                                                                                                                                          |                                                                    | MIN                | NOM MA            | UNIT     |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------|-------------------|----------|

| 3.1.1 | V <sub>VSYS</sub>                                                                                                                        | Input voltage                                                      | 2.5 <sup>(1)</sup> | 5.                | 5 V      |

| 3.1.2 | V <sub>PVIN_B1</sub> , V <sub>PVIN_B2</sub> ,<br>V <sub>PVIN_B3</sub><br>V <sub>LX_B1</sub> , V <sub>LX_B2</sub> ,<br>V <sub>LX_B3</sub> | BUCKx Pins                                                         | 2.5                | 5.5 <sup>(;</sup> | <u>V</u> |

| 3.1.3 | Δ V <sub>VSYS_PVIN_Bx</sub>                                                                                                              | Voltage by which V <sub>PVIN_Bx</sub> may exceed V <sub>VSYS</sub> |                    |                   | ) mV     |

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

## **6.3 Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)

| POS     |                                                                       |                                                                                                                                                            | MIN  | NOM | MAX                | UNIT |

|---------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------|

| 3.1.4   | Δ V <sub>VSYS_PVIN_LDO1,LDO2</sub>                                    | Voltage by which V <sub>PVIN_LDO1</sub> or V <sub>PVIN_LDO2</sub> may exceed V <sub>VSYS</sub>                                                             |      |     | 0                  | mV   |

| 3.1.5   | Δ V <sub>VSYS_VLDO34</sub>                                            | Voltage by which $V_{VSYS}$ must exceed LDO output voltage (VLDO3, VLDO4); $V_{VSYS}$ = 2.5V to 3.45V; LDO mode                                            | 150  |     |                    | mV   |

| 3.1.6   | Δ V <sub>VSYS_VLDO34</sub>                                            | Voltage by which $V_{VSYS}$ must exceed LDO output voltage (VLDO3, VLDO4); $V_{VSYS}$ = 3.45V to 5.5V in LDO-mode or $V_{VSYS}$ = 2.5V to 5.5V in LSW-mode | n/a  |     |                    | mV   |

| 3.1.7   | C <sub>PVIN_B1</sub> , C <sub>PVIN_B2</sub> ,<br>C <sub>PVIN_B3</sub> | BUCKx Input Capacitance                                                                                                                                    | 3.9  | 4.7 |                    | μF   |

| 3.1.8   | L <sub>B1</sub> , L <sub>B2</sub> , L <sub>B3</sub>                   | BUCKx Output Inductance                                                                                                                                    | 330  | 470 | 611                | nΗ   |

| 3.1.9a  | C <sub>OUT_B1</sub> , C <sub>OUT_B2</sub> ,<br>C <sub>OUT_B3</sub>    | BUCKx Output Capacitance, forced PWM or auto-PFM, low bandwidth case                                                                                       | 10   |     | 75                 | μF   |

| 3.1.9b  | C <sub>OUT_B1</sub> , C <sub>OUT_B2</sub> ,<br>C <sub>OUT_B3</sub>    | BUCKx Output Capacitance, fixed frequency, low BW case                                                                                                     | 12   |     | 36                 | μF   |

| 3.1.10a | C <sub>OUT_B1</sub> , C <sub>OUT_B2</sub> ,<br>C <sub>OUT_B3</sub>    | BUCKx Output Capacitance, forced PWM or auto-PFM, high bandwidth case                                                                                      | 30   |     | 220                | μF   |

| 3.1.10b | C <sub>OUT_B1</sub> , C <sub>OUT_B2</sub> ,<br>C <sub>OUT_B3</sub>    | BUCKx Output Capacitance, fixed frequency, high BW case                                                                                                    | 48   |     | 144                | μF   |

| 3.1.11  | V <sub>FB_B1</sub> , V <sub>FB_B2</sub> ,<br>V <sub>FB_B3</sub>       | BUCKx FB Pins                                                                                                                                              | 0    |     | 5.5 <sup>(2)</sup> | V    |

| 3.1.12  | V <sub>PVIN_LDO1</sub> , V <sub>PVIN_LDO2</sub>                       | LDO Input Voltage                                                                                                                                          | 1.5  |     | 5.5 <sup>(2)</sup> | V    |

| 3.1.13  | V <sub>PVIN_LDO1</sub> , V <sub>PVIN_LDO2</sub>                       | LDO Input Voltage in bypass mode                                                                                                                           | 1.5  |     | 3.6                | V    |

| 3.1.14  | V <sub>PVIN_LDO1</sub> , V <sub>PVIN_LDO2</sub>                       | Allowable delta between V <sub>PVIN_LDOx</sub> and configured V <sub>VLDOx</sub> in bypass mode                                                            | -200 |     | 200                | mV   |

| 3.1.15  | V <sub>VLDO1</sub> , V <sub>VLDO2</sub>                               | LDO Output Voltage Range                                                                                                                                   | 0.6  |     | 3.4                | V    |

| 3.1.16  | C <sub>PVIN_LDO1</sub> , C <sub>PVIN_LDO2</sub>                       | LDO Input Capacitance                                                                                                                                      | 1.6  | 2.2 |                    | μF   |

| 3.1.17  | C <sub>VLDO1</sub> , C <sub>VLDO2</sub>                               | LDO Output Capacitance                                                                                                                                     | 1.6  | 2.2 | 20                 | μF   |

| 3.1.18  | V <sub>PVIN_LDO3</sub> , V <sub>PVIN_LDO4</sub>                       | LDO Input Voltage                                                                                                                                          | 2.2  |     | 5.5 <sup>(2)</sup> | V    |

| 3.1.19  | V <sub>VLDO3</sub> , V <sub>VLDO4</sub>                               | LDO Output Voltage Range                                                                                                                                   | 1.2  |     | 3.3                | V    |

| 3.1.20  | C <sub>PVIN_LDO34</sub>                                               | LDO Input Capacitance                                                                                                                                      | 2.2  | 4.7 |                    | μF   |

| 3.1.21  | C <sub>VLDO3</sub> , C <sub>VLDO4</sub>                               | LDO Output Capacitance                                                                                                                                     | 1.6  | 2.2 | 30 (3)             | μF   |

| 3.1.22  | V <sub>VDD1P8</sub>                                                   | VDD1P8 pin                                                                                                                                                 | 0    |     | 1.8                | V    |

| 3.1.23  | C <sub>VDD1P8</sub>                                                   | Internal Regulator Decoupling Capacitance                                                                                                                  | 1    | 2.2 | 4                  | μF   |

| 3.1.24  | C <sub>VSYS</sub>                                                     | VSYS Input Decoupling Capacitance                                                                                                                          | 1    | 2.2 |                    | μF   |

| 3.1.25  | V <sub>nINT</sub> , V <sub>nRSTOUT</sub>                              | Digital Outputs                                                                                                                                            | 0    |     | 3.4                | V    |

| 3.1.26  | V <sub>GPO1</sub> , V <sub>GPO2</sub> , V <sub>GPIO</sub>             | Digital Outputs                                                                                                                                            | 0    |     | 5.5 <sup>(2)</sup> | V    |

| 3.1.27  | V <sub>SCL</sub> , V <sub>SDA</sub>                                   | I2C Interface                                                                                                                                              | 0    |     | 3.4                | V    |

| 3.1.28  | VEN/PB/VSENSE, VMODE/STBY, VMODE/RESET, VVSEL_SD/VSEL/DDR             | Digital Inputs                                                                                                                                             | 0    |     | 5.5 (2)            | V    |

| 3.2.1   | t <sub>VSYS_RAMP_RISE</sub>                                           | Input voltage rising ramp Time, Input voltage controlled by a pre-regulator. $V_{VSYS} = V_{PVIN\_Bx} = V_{PVIN\_LDOx} = 0V$ to 5V                         | 0.1  |     | 600000             | ms   |

| 3.2.2   | tvsys_ramp_fall                                                       | Input voltage falling Ramp Time, $V_{VSYS} = V_{PVIN\_Bx} = V_{PVIN\_LDOx} = 5V$ to 2.5V                                                                   | 0.4  |     | 600000             | ms   |

| 3.3.1   | T <sub>A</sub> _                                                      | Operating free-air temperature                                                                                                                             | - 40 |     | 125                | °C   |

## 6.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

| POS   |                 |                                | MIN  | NOM MAX | UNIT |

|-------|-----------------|--------------------------------|------|---------|------|

| 3.3.2 | T <sub>J_</sub> | Operating junction temperature | - 40 | 150     | °C   |

- (1) For EEPROM programming, VSYS(min)=3.3V

- (2) Must not exceed VSYS

- (3) In slow-ramp-mode. Fast-ramp supports 15µF maximum

#### **6.4 Thermal Information**

|                        |                                              | TPS65219-Q1 |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RHB (QFN)   | UNIT |

|                        |                                              | 32 PINS     |      |

| R <sub>⊕JA</sub>       | Junction-to-ambient thermal resistance       | 31.3        | °C/W |

| R <sub>⊕ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 20.4        | °C/W |

| R <sub>⊕JB</sub>       | Junction-to-board thermal resistance         | 10.9        | °C/W |

| Ψ <sub>JT</sub>        | Junction-to-top characterization parameter   | 0.3         | °C/W |

| Ψ ЈВ                   | Junction-to-board characterization parameter | 10.8        | °C/W |

| R <sub>⊙JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 2.8         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 6.5 System Control Thresholds

Over operating free-air temperature range (unless otherwise noted). Voltage level refers to the AGND ground of the device.

| POS      |                              | PARAMETER                                               | TEST CONDITIONS                                                                                                                    | MIN   | TYP | MAX  | UNIT |

|----------|------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| Electric | al Characteristics           |                                                         |                                                                                                                                    |       |     |      |      |

| 4.1.1    | VSYS                         | Operating Input Voltage                                 |                                                                                                                                    | 2.5   |     | 5.5  | V    |

| 4.1.2    | VSYS <sub>POR_Rising</sub>   | VSYS POR rising threshold                               | Measured on VSYS pin, untrimmed                                                                                                    | 2.2   |     | 2.5  | V    |

| 4.1.3    | VSYS <sub>UVLO_Falling</sub> | VSYS UVLO falling threshold                             | Measured on VSYS pin, trimmed                                                                                                      | 2.175 |     | 2.25 | V    |

| 4.1.4    | VSYS <sub>POR_Hyst</sub>     | VSYS UVLO/POR hysteresis                                | VSYS <sub>POR_Rising_untrimmed</sub> -<br>VSYS <sub>UVLO_Falling_trimmed</sub>                                                     |       | 130 |      | mV   |

| 4.1.5    | V <sub>VSYS_OVP_Rise</sub>   | VSYS OVP rising threshold, trimmed                      | Measured on VSYS pin, trimmed                                                                                                      | 5.9   |     | 6.1  | V    |

| 4.1.6    | V <sub>VSYS_OVP_Fall</sub>   | VSYS OVP falling threshold, trimmed                     | Measured on VSYS pin, trimmed                                                                                                      | 5.7   |     | 5.95 | V    |

| 4.1.7    | V <sub>VSYS_OVP_Hyst</sub>   | VSYS OVP hysteresis                                     | VSYS <sub>OVP_Rising_trimmed</sub> -<br>VSYS <sub>OVP_falling_trimmed</sub>                                                        | 100   | 140 | 180  | mV   |

| 4.1.8    | V <sub>VDD1P8</sub>          | VDD1P8 voltage                                          |                                                                                                                                    | 1.7   | 1.8 | 1.9  | V    |

| 4.2.1a   | I <sub>INITIALIZE</sub>      | Current Consumption in INITIALIZE state, at 25°C        | Combined Current from VSYS and PVIN_x pins. VSYS = PVIN_Bx = PVIN_LDOx = 5V. All Monitors are off. T <sub>J</sub> = 25°C           |       | 15  | 22   | μΑ   |

| 4.2.1b   | Initialize                   | Current Consumption in INITIALIZE state, -40°C to 150°C | Combined Current from VSYS and PVIN_x pins. VSYS = PVIN_Bx = PVIN_LDOx = 5V. All Monitors are off. T <sub>J</sub> = -40°C to 150°C |       | 15  | 37   | μА   |

## 6.5 System Control Thresholds (continued)

Over operating free-air temperature range (unless otherwise noted). Voltage level refers to the AGND ground of the device.

| POS    |                               | PARAMETER                                                                                                      | TEST CONDITIONS                                                                                                                                                                                                                                   | MIN | TYP | MAX                                                                 | UNIT |

|--------|-------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------------------------------------------------------|------|

| 4.2.2a | I <sub>ACTIVE</sub>           | ACTIVE State Current<br>Consumption, all rails on, at 25°C                                                     | Combined Current from VSYS and PVIN_x pins. VSYS = PVIN_Bx = PVIN_LDOx = 5V. All Outputs are on, all LDOs in LDO-mode, Bucks in PFM mode. No Load. T <sub>J</sub> = 25°C                                                                          |     | 250 | 290                                                                 | μА   |

| 4.2.2b | I <sub>ACTIVE</sub>           | ACTIVE State Current<br>Consumption, all rails on,<br>-40°C to 150°C                                           | Combined Current from VSYS and PVIN_x pins. VSYS = PVIN_Bx = PVIN_LDOx = 5V. All Outputs are on, all LDOs in LDO-mode, Bucks in PFM mode. No Load. T <sub>J</sub> = -40°C to 150°C                                                                |     | 250 | 500                                                                 | μА   |

| 4.2.3a | I <sub>STBY</sub>             | STBY State Current Consumption, only LDO1 on, at 25°C                                                          | Combined Current from VSYS and PVIN_x pins. VSYS = PVIN_Bx = PVIN_LDOx = 5V. Only LDO1 on in LDO-mode. No Load. T <sub>J</sub> = 25°C                                                                                                             |     | 105 | 125                                                                 | μА   |

| 4.2.3b | I <sub>STBY</sub>             | STBY State Current Consumption, only LDO1 on, -40°C to 150°C                                                   | Combined Current from VSYS and PVIN_x pins. VSYS = PVIN_Bx = PVIN_LDOx = 5V. Only LDO1 on in LDO-mode. No Load. T <sub>J</sub> = -40°C to 150°C                                                                                                   |     | 105 | 150                                                                 | μА   |

| 4.2.4a | I <sub>STBY</sub>             | STBY State Current Consumption, all rails on, VMON on at 25°C                                                  | Combined Current from VSYS and PVIN_x pins. VSYS = PVIN_Bx = PVIN_LDOx = 5V. All Outputs are on, all LDOs in LDO-mode, Bucks in PFM mode. No Load. Output-voltage Monitors are on, VSYS-monitor (UV/OVP) are on. T <sub>J</sub> = 25°C            |     | 250 | 290                                                                 | μА   |

| 4.2.4b | I <sub>STBY</sub>             | STBY State Current Consumption, all rails on, VMON on, -40°C to 150°C                                          | Combined Current from VSYS and PVIN_x pins. VSYS = PVIN_Bx = PVIN_LDOx = 5V. All Outputs are on, all LDOs in LDO-mode,, Bucks in PFM mode. No Load. Output-voltage Monitors are on, VSYS-monitor (UV/OVP) are on. T <sub>J</sub> = -40°C to 150°C |     | 250 | 500                                                                 | μА   |

| Timing | Requirements                  |                                                                                                                |                                                                                                                                                                                                                                                   |     |     |                                                                     |      |

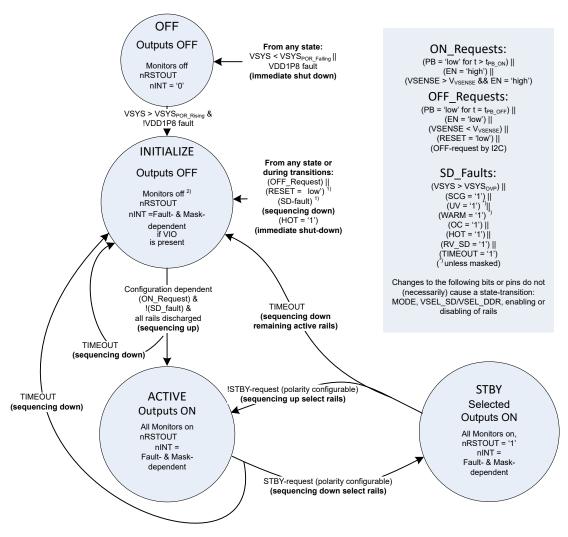

| 4.3.1  | t <sub>OFF_TO_INIT</sub>      | Time from VSYS passing VSYS_POR until entering INITIALIZE state, including EEPROM-read, ready for ON- request  | Time from VSYS passing VSYS_POR until entering INITIALIZE state. On request execution gated by HOT and RV                                                                                                                                         |     |     | 3.2                                                                 | ms   |

| 4.3.2a | t <sub>TIMEOUT_UV</sub>       | UV-detection in case a rail does not reach UV-threshold during ramp-up                                         |                                                                                                                                                                                                                                                   |     |     | end of<br>t <sub>RAMP</sub> +<br>sample-<br>and<br>deglitch<br>time |      |

| 4.3.2b | t <sub>TIMEOUT_UV_</sub> SLOT | Timeout in case a rail does not reach UV-threshold during ramp-up, applicable in Multi-PMIC-configuration only |                                                                                                                                                                                                                                                   |     |     | end of<br>slot-<br>extensi<br>on time<br>(3ms,<br>4ms or<br>13ms)   |      |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLVSGA1

10

## 6.5 System Control Thresholds (continued)

Over operating free-air temperature range (unless otherwise noted). Voltage level refers to the AGND ground of the device.

| POS   |                                | PARAMETER                                                                                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------|--------------------------------|------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| 4.3.3 | t <sub>TIMEOUT_Discharge</sub> | Timeout in case a rail cannot be discharged when transitioning from STBY to ACTIVE state |                 | 72  | 80  | 88  | ms   |

#### 6.6 BUCK1 Converter

over operating free-air temperature range (unless otherwise noted)

| POS      |                            | PARAMETER                                                                          | TEST CONDITIONS                                                                                                                                                                              | MIN    | TYP | MAX  | UNIT |

|----------|----------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|------|------|

| Electric | al Characteristics         |                                                                                    |                                                                                                                                                                                              |        |     |      |      |

| 5.1.1a   | V <sub>IN_BUCK1</sub>      | Input voltage <sup>(1)</sup>                                                       | Buck supply voltage, maximum VSYS                                                                                                                                                            | 2.5    |     | 5.5  | V    |

| 5.1.1b   | V <sub>OUT_BUCK1</sub>     | Buck Output Voltage configurable<br>Range                                          | Output voltage configurable in 25mV-steps for $0.6V \leqslant V_{OUT} \leqslant 1.4V$ , in 100mV steps for $1.4V < V_{OUT} \leqslant 3.4V$                                                   | 0.6    |     | 3.4  | V    |

| 5.1.2a   | I <sub>Q_BUCK1</sub>       | Quiescent Current at 25°C, PFM, low BW case                                        | PFM, BUCK1 enabled, no load,<br>V <sub>IN</sub> = 5.0V, V <sub>OUT</sub> = 1.2V, T <sub>J</sub> =25°C                                                                                        |        | 10  | 13   | μА   |

| 5.1.2b   | I <sub>Q_BUCK1</sub>       | Quiescent Current -40°C to 125°C, PFM, low BW case                                 | PFM, BUCK1 enabled, no load,<br>V <sub>IN</sub> = 5.0V, V <sub>OUT</sub> = 1.2V, T <sub>J</sub> =-40°C<br>to 125°C                                                                           |        | 15  | 44   | μА   |

| 5.1.2c   | I <sub>Q_BUCK1</sub>       | Quiescent Current -40°C to 150°C, PFM, low BW case                                 | PFM, BUCK1 enabled, no load,<br>V <sub>IN</sub> = 5.0V, V <sub>OUT</sub> = 1.2V, T <sub>J</sub> =-40°C<br>to 150°C                                                                           |        | 20  | 63   | μА   |

| 5.1.3a   | V <sub>HEADROOM_PWM</sub>  | Input to Output Voltage<br>Headroom <sup>(2)</sup>                                 | Corner cases at maximum load I <sub>OUT</sub> = 2.5A                                                                                                                                         | 500    |     |      | mV   |

| 5.1.3b   | V <sub>HEADROOM_PWM</sub>  | Input to Output Voltage<br>Headroom at I <sub>OUT</sub> = I <sub>OUT_MAX</sub> (2) | Corner cases at I <sub>OUT</sub> = I <sub>OUT_MAX</sub>                                                                                                                                      | 700    |     |      | mV   |

| 5.1.3c   | V <sub>HEADROOM_FF</sub>   | Input to Output Voltage<br>Headroom <sup>(2)</sup>                                 | Corner cases at maximum load I <sub>OUT</sub> = 0.7A                                                                                                                                         | 500    |     |      | mV   |

| 5.1.3d   | V <sub>HEADROOM_FF</sub>   | Input to Output Voltage<br>Headroom at I <sub>OUT</sub> = I <sub>OUT_MAX</sub> (2) | Corner cases at I <sub>OUT</sub> = I <sub>OUT_MAX</sub>                                                                                                                                      | 1000   |     |      | mV   |

| 5.1.4    | V <sub>OUT_STEP_LOW</sub>  | Output voltage Steps                                                               | $0.6V \leqslant V_{OUT} \leqslant 1.4V$                                                                                                                                                      |        | 25  |      | mV   |

| 5.1.5    | V <sub>OUT_STEP_HIGH</sub> | Output voltage Steps                                                               | $1.5V \leqslant V_{OUT} \leqslant 3.4V$                                                                                                                                                      |        | 100 |      | mV   |

| 5.1.6a   | V <sub>OUT_ACC_DC_PW</sub> | DC Output Voltage Accuracy in forced PWM mode, low and high BW case                | $I_{OUT} = I_{OUT\_MAX},$<br>$V_{OUT} \ge 0.7V$ to 3.4V,<br>$V_{IN} - V_{OUT} > 700$ mV<br>forced PWM, low BW case                                                                           | - 1.5% |     | 1.5% |      |

| 5.1.6b   | VOUT_ACC_DC_PW             | DC Output Voltage Accuracy in forced PWM mode, low and high BW case                | $\begin{split} I_{OUT} &= I_{OUT\_MAX}, \\ V_{OUT} &= 0.6 \overline{V} \text{ to } 0.7 \text{V}, \\ V_{\text{IN}} &- V_{OUT} > 700 \text{ mV} \\ \text{forced PWM, low BW case} \end{split}$ | - 10   |     | 10   | mV   |

| 5.1.6c   | Vout_acc_dc_pfm            | DC Output Voltage Accuracy in auto-PFM mode, low and high BW case                  | $I_{OUT}$ = 1mA,<br>$V_{OUT}$ = 0.6V to 3.4V,<br>$V_{IN}$ - $V_{OUT}$ > 500 mV<br>auto-PFM, low BW case                                                                                      | - 3.0% |     | 3.5% |      |

| 5.1.6d   | V <sub>OUT_ACC_DC_FF</sub> | DC Output Voltage Accuracy in Fixed Frequency mode, low and high BW case           | $I_{OUT} = I_{OUT\_MAX}$ ,<br>$V_{OUT} \geqslant 0.7V$ to 3.4V,<br>$V_{IN} - V_{OUT} > 1000$ mV<br>fixed frequency, low BW case                                                              | - 1.5% |     | 1.5% |      |

| 5.1.6e   | V <sub>OUT_ACC_DC_FF</sub> | DC Output Voltage Accuracy in<br>Fixed Frequency mode, low and<br>high BW case     | $\begin{split} I_{OUT} &= I_{OUT\_MAX}, \\ V_{OUT} &= 0.6 \text{V to } 0.7 \text{V}, \\ V_{\text{IN}} &- V_{OUT} > 1000 \text{ mV} \\ \text{fixed frequency, low BW case} \end{split}$       | - 10   |     | 10   | mV   |

## 6.6 BUCK1 Converter (continued)

over operating free-air temperature range (unless otherwise noted)

| POS    |                          | PARAMETER                                                              | TEST CONDITIONS                                                                                                                                                                                                                                                                              | MIN    | TYP  | MAX  | UNIT |

|--------|--------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|------|

| 5.1.7  | R <sub>FB_INPUT</sub>    | Feedback input impedance                                               | Converter enabled                                                                                                                                                                                                                                                                            | 2.3    | 3.75 | 5.0  | ΜΩ   |

| 5.2.1a | VLOAD_REG_PWM            | DC Load Regulation, forced PWM, low BW case                            | $V_{\text{IN}}$ = 5.0V, $V_{\text{OUT}}$ = 1.2V, $I_{\text{OUT}}$ = 0 to $I_{\text{OUT\_MAX}}$ , forced PWM, low BW case, $C_{\text{OUT}}$ = 40 $\mu$ F                                                                                                                                      |        | 0.1  | 0.16 | %/A  |

| 5.2.1b | V <sub>LOAD_REG_FF</sub> | DC Load Regulation, fixed frequency, low BW case                       | $\begin{aligned} &V_{\text{IN}} = 5.0\text{V, } V_{\text{OUT}} = 1.2\text{V,} \\ &I_{\text{OUT}} = 0 \text{ to } I_{\text{OUT\_MAX,}} \\ &\text{fixed frequency, low BW case, } C_{\text{OUT}} \\ &= 40 \ \mu \text{ F} \end{aligned}$                                                       |        | 0.1  | 0.16 | %/A  |

| 5.2.2a | V <sub>LINE_REG</sub>    | DC Line Regulation, forced PWM, low BW case                            | $V_{IN}$ = 3.3V to 5.5V,<br>$V_{OUT}$ = 1.2V,<br>$I_{OUT}$ = 1mA and $I_{OUT\_MAX}$<br>forced PWM, low BW case, $C_{OUT}$ =<br>40 $\mu$ F                                                                                                                                                    |        | 0.1  | 0.16 | %/V  |

| 5.2.2b | V <sub>LINE_REG</sub>    | DC Line Regulation, fixed frequency, low BW case                       | $V_{IN}$ = 3.3V to 5.5V,<br>$V_{OUT}$ = 1.2V,<br>$I_{OUT}$ = 1mA and $I_{OUT\_MAX}$<br>fixed frequency, low $\overline{B}W$ case, $C_{OUT}$<br>= 12 $\mu$ F                                                                                                                                  |        | 0.1  | 0.16 | %/V  |

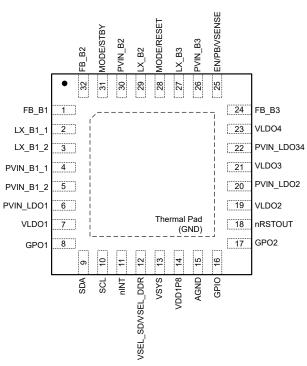

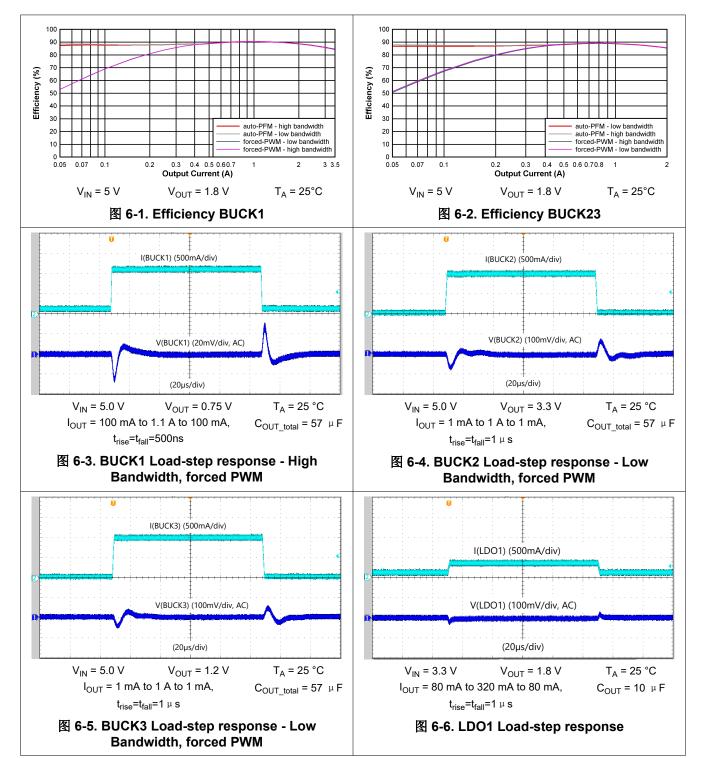

| 5.2.3a | VLOAD_TRANSIENT          | Load Transient, V <sub>OUT</sub> =0.75V, auto-PFM, high BW case        | $\begin{aligned} &V_{\text{IN}} = 5.0\text{V, } V_{\text{OUT}} = 0.75\text{V,} \\ &I_{\text{OUT}} = 100\text{mA to } 1100\text{mA to } 100\text{mA,} \\ &t_{\text{R}} = t_{\text{F}} = 500\text{ns,} \\ &\text{auto-PFM, high BW case, } C_{\text{OUT}} = \\ &80~\mu\text{ F} \end{aligned}$ | - 27.5 |      | 27.5 | mV   |

| 5.2.3b | VLOAD_TRANSIENT          | Load Transient, V <sub>OUT</sub> =0.75V, forced PWM, high BW case      | $V_{\text{IN}}$ = 5.0V, $V_{\text{OUT}}$ = 0.75V, $I_{\text{OUT}}$ = 100mA to 1100mA to 100mA, $t_{\text{R}}$ = $t_{\text{F}}$ = 500ns, forced PWM, high BW case, $C_{\text{OUT}}$ = 80 μ F                                                                                                  | - 27.5 |      | 27.5 | mV   |

| 5.2.3c | VLOAD_TRANSIENT          | Load Transient, V <sub>OUT</sub> =0.75V, fixed frequency, high BW case | $\begin{array}{l} V_{IN}=5.0\text{V, } V_{OUT}=0.75\text{V,} \\ I_{OUT}=I_{OUT}=100\text{mA to }1100\text{mA to} \\ 100\text{mA,} \\ t_R=t_F=500\text{ns,} \\ \text{fixed frequency, high BW case,} \\ C_{OUT}=60~~\mu\text{ F} \end{array}$                                                 | - 27.5 |      | 27.5 | mV   |

| 5.2.4a | VLOAD_TRANSIENT          | Load Transient, V <sub>OUT</sub> =1.8V, auto-<br>PFM, low BW case      | $\begin{split} &V_{\text{IN}} = 5.0\text{V, } V_{\text{OUT}} = 1.8\text{V,} \\ &I_{\text{OUT}} = 1\text{mA to 1A to 1mA,} \\ &t_{\text{R}} = t_{\text{F}} = 1~\mu~\text{s,} \\ &\text{auto-PFM, } C_{\text{OUT}} = 40~\mu~\text{F} \end{split}$                                              | -90    |      | 90   | mV   |

| 5.2.4b | VLOAD_TRANSIENT          | Load Transient, V <sub>OUT</sub> =1.8V, forced PWM, low BW case        | $\begin{split} &V_{\text{IN}} = 5.0\text{V, } V_{\text{OUT}} = 1.8\text{V,} \\ &I_{\text{OUT}} = 1\text{mA to 1A to 1mA,} \\ &I_{\text{R}} = I_{\text{F}} = 1~\mu~\text{s,} \\ &\text{forced PWM, } C_{\text{OUT}} = 40~\mu~\text{F} \end{split}$                                            | -60    |      | 60   | mV   |

| 5.2.4c | VLOAD_TRANSIENT          | Load Transient, V <sub>OUT</sub> =1.8V, fixed frequency, low BW case   | $\begin{split} &V_{IN}=5.0\text{V, }V_{OUT}=1.8\text{V,}\\ &I_{OUT}=1\text{mA to 1A to 1mA,}\\ &t_R=t_F=1~\mu~\text{s,}\\ &\text{fixed frequency, low BW case, }C_{OUT}\\ &=12~\mu~\text{F} \end{split}$                                                                                     | -180   |      | 180  | mV   |

| 5.2.5a | VLINE_TRANSIENT          | Line Transient, V <sub>OUT</sub> =1.2V, forced PWM, low BW case        | $V_{IN}$ = 3.3V to 5.5V in 50 $\mu$ s, $V_{OUT}$ = 1.2V, $I_{OUT}$ = 1mA and $I_{OUT\_MAX},$ forced PWM, low BW case, $C_{OUT}$ = 40 $\mu$ F                                                                                                                                                 | - 50   |      | 50   | mV   |

English Data Sheet: SLVSGA1

## 6.6 BUCK1 Converter (continued)

over operating free-air temperature range (unless otherwise noted)

| POS    |                              | PARAMETER                                                            | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                  | MIN   | TYP   | MAX   | UNIT             |

|--------|------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------------------|

| 5.2.5b | V <sub>LINE_</sub> TRANSIENT | Line Transient, V <sub>OUT</sub> =1.2V, fixed frequency, low BW case | $V_{IN}$ = 3.3V to 5.5V in 50 $\mu$ s, $V_{OUT}$ = 1.2V, $I_{OUT}$ = 1mA and $I_{OUT\_MAX}$ , fixed frequency, low BW case, $C_{OUT}$ = 12 $\mu$ F                                                                                                                                                                               | - 50  |       | 50    | mV               |

| 5.2.6a | V <sub>RIPPLE_PP_PWM</sub>   | Forced PWM Mode, low BW case                                         | $\begin{aligned} &V_{\text{IN}} = 5.0\text{V},  V_{\text{OUT}} = 2.5\text{V}, \\ &\text{forced PWM, low BW case, } C_{\text{OUT}} = \\ &40\text{uF, X5R, ESR} = 10\text{mOhm,} \\ &L = 470\text{nH, DCR} = 50\text{m}\Omega \\ &I_{\text{OUT}} = 1\text{A} \end{aligned}$                                                        |       | 10    | 20    | mV <sub>PP</sub> |

| 5.2.6b | V <sub>RIPPLE_PP_PFM</sub>   | Auto PFM Mode, low BW case                                           | $\begin{aligned} &V_{\text{IN}} = 5.0\text{V},  V_{\text{OUT}} = 2.5\text{V}, \\ &\text{auto PFM, low BW case, } C_{\text{OUT}} = \\ &40\text{uF, X5R, ESR} = 10\text{mOhm,} \\ &\text{L} = 470\text{nH, DCR} = 50\text{m}\Omega \\ &\text{I}_{\text{OUT}} = 20\text{mA} \end{aligned}$                                          |       | 20    | 40    | mV <sub>PP</sub> |

| 5.2.6c | V <sub>RIPPLE_PP_FF</sub>    | Fixed Frequency Mode, low BW case, spread spectrum disabled          | $\begin{aligned} & V_{\text{IN}} = 5.0\text{V},  V_{\text{OUT}} = 2.5\text{V}, \\ & \text{fixed frequency, low BW case, C}_{\text{OUT}} \\ & = 12\text{uF, X5R, ESR} = 10\text{mOhm,} \\ & \text{L} = 470\text{nH, DCR} = 50\text{m}\Omega, \\ & I_{\text{OUT}} = 1\text{A,} \\ & \text{Spread-Spectrum disabled} \end{aligned}$ |       | 10    | 20    | mV <sub>PP</sub> |

| 5.2.6d | V <sub>RIPPLE_PP_FF_SS</sub> | Fixed Frequency Mode, low BW case                                    | $\begin{split} &V_{\text{IN}} = 5.0\text{V},  V_{\text{OUT}} = 2.5\text{V}, \\ &\text{fixed frequency, low BW case, } C_{\text{OUT}} \\ &= 12\text{uF, X5R, ESR} = 10\text{mOhm,} \\ &\text{L} = 470\text{nH, DCR} = 50\text{m}\Omega, \\ &\text{I}_{\text{OUT}} = 1\text{A}, \\ &\text{Spread-Spectrum enabled} \end{split}$    |       | 20    | 40    | mV <sub>PP</sub> |

| 5.3.1  | I <sub>OUT_MAX</sub>         | Maximum Operating Current                                            |                                                                                                                                                                                                                                                                                                                                  |       | ,     | 3.5   | Α                |

| 5.3.2  | I <sub>CURRENT_LIMIT</sub>   | Peak Current Limit                                                   | V <sub>IN</sub> = 2.5V to 5.5V                                                                                                                                                                                                                                                                                                   | 4.6   | 5.7   | 6.9   | Α                |

| 5.3.3  | I <sub>REV_CUR_LIMIT</sub>   | Reverse Peak Current Limit                                           | V <sub>IN</sub> = 2.5V to 5.5V                                                                                                                                                                                                                                                                                                   | - 2.0 | - 1.5 | - 1.0 | Α                |

| 5.3.4a | R <sub>DSON_HS</sub>         | High Side MOSFET On Resistance, 5V-supply                            | Measured Pin to Pin, V <sub>IN</sub> = 5V                                                                                                                                                                                                                                                                                        |       |       | 70    | m Ω              |

| 5.3.4b | R <sub>DSON_HS</sub>         | High Side MOSFET On Resistance, 3.3V-supply                          | Measured Pin to Pin, V <sub>IN</sub> = 3.3V                                                                                                                                                                                                                                                                                      |       |       | 80    | m Ω              |

| 5.3.5a | R <sub>DSON_LS</sub>         | Low Side MOSFET On Resistance, 5V-supply                             | Measured Pin to Pin, V <sub>IN</sub> = 5V                                                                                                                                                                                                                                                                                        |       |       | 40    | m Ω              |

| 5.3.5b | R <sub>DSON_LS</sub>         | Low Side MOSFET On Resistance, 3.3V-supply                           | Measured Pin to Pin, V <sub>IN</sub> = 3.3V                                                                                                                                                                                                                                                                                      |       |       | 50    | m Ω              |

| 5.3.6  | R <sub>DISCHARGE</sub>       | Output Discharge Resistance                                          | Active only when converter is disabled                                                                                                                                                                                                                                                                                           | 60    | 125   | 200   | Ω                |

| 5.4.1  | L <sub>SW</sub>              | Output Inductance                                                    | DCR = 50mΩ max                                                                                                                                                                                                                                                                                                                   | 330   | 470   | 611   | nH               |

| 5.4.2a | C <sub>OUT</sub>             | Output Capacitance in auto-PFM or forced PWM for low BW case         | ESR = 10mΩ max                                                                                                                                                                                                                                                                                                                   | 10    |       | 75    | μF               |

| 5.4.2b | C <sub>OUT_FF</sub>          | Output Capacitance in fixed frequency for low BW case                | ESR = 10mΩ max                                                                                                                                                                                                                                                                                                                   | 12    |       | 36    | μF               |

| 5.4.3a | C <sub>OUT_HIGH_BW</sub>     | Output Capacitance in auto-PFM or forced PWM for high BW case        | ESR = 10mΩ max                                                                                                                                                                                                                                                                                                                   | 30    |       | 220   | μF               |

| 5.4.3b | C <sub>OUT_HIGH_BW_FF</sub>  | Output Capacitance in fixed frequency for high BW case               | ESR = 10mΩ max                                                                                                                                                                                                                                                                                                                   | 48    |       | 144   | μF               |

| Timing | Requirements                 |                                                                      |                                                                                                                                                                                                                                                                                                                                  |       |       |       |                  |

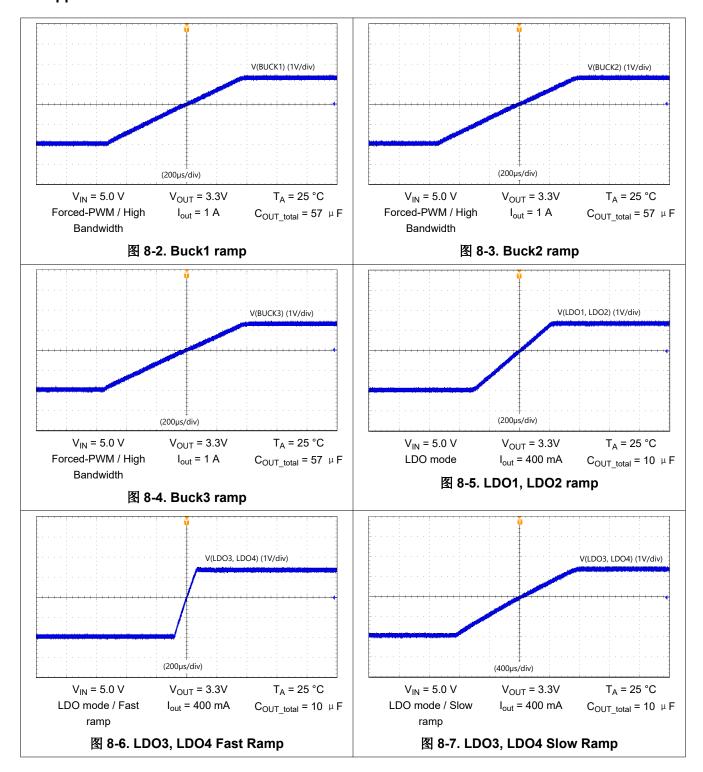

| 5.5.1  | t <sub>RAMP</sub>            | Ramp Time in forced PWM, low BW case                                 | Time from enable to 98% of target value, assuming no residual voltage                                                                                                                                                                                                                                                            | 0.3   |       | 1.65  | ms               |

| 5.5.2a | DVFS_RISE_<br>QFF            | DVFS timing requirements in forced PWM, rising slope                 | Step-duration during DVFS voltage adjustments from 0.6V to 1.4V                                                                                                                                                                                                                                                                  | 2.9   | 3.2   | 3.5   | mV/μs            |

#### 6.6 BUCK1 Converter (continued)

over operating free-air temperature range (unless otherwise noted)

| POS     |                       | PARAMETER                                                                               | TEST CONDITIONS                                                                                                           | MIN  | TYP  | MAX  | UNIT    |

|---------|-----------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|---------|

| 5.5.2b  | DVFS_RISE_<br>FF      | DVFS timing requirements in fixed-frequency mode, rising slope                          | Step-duration during DVFS voltage adjustments from 0.6V to 1.4V                                                           | 1.8  | 2.1  | 2.5  | mV/ μ s |

| 5.5.2c  | DVFS_FALL             | DVFS timing requirements in forced PWM or fixed-frequency mode, falling slope           | Step-duration during DVFS voltage adjustments from 1.4V to 0.6V                                                           | 0.45 | 0.53 | 0.61 | mV/ μ s |

| Switchi | ng Characteristics    | s                                                                                       |                                                                                                                           |      |      |      |         |

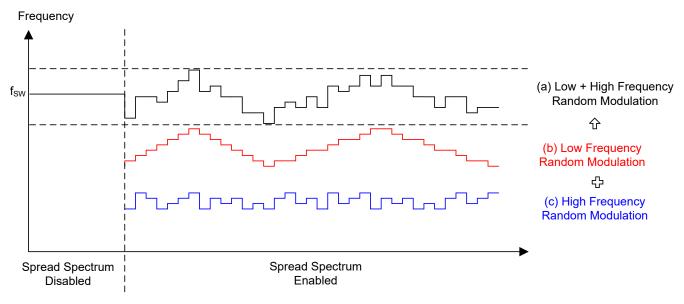

| 5.6.1a  | f <sub>SW</sub>       | Switching Frequency, forced PWM, high or low BW case                                    | Forced PWM, V <sub>IN</sub> = 3.3V to 5V,<br>V <sub>OUT</sub> = 0.8V to 1.8V,<br>I <sub>OUT</sub> = 1A to 3A              |      | 2.3  |      | MHz     |

| 5.6.1b  | f <sub>SW</sub>       | Switching Frequency, fixed frequency, high or low BW case, no Spread Spectrum           | Fixed - Frequency, $V_{IN}$ = 3.3V to 5V, $V_{OUT}$ = 0.8V to 1.8V, $I_{OUT}$ = 1A to 3A                                  | 2.18 | 2.3  | 2.42 | MHz     |

| 5.6.2   | f <sub>SW_SS_EN</sub> | Switching Frequency, fixed frequency, high or low BW case, with Spread Spectrum enabled | Fixed - Frequency, $V_{IN}$ = 3.3V to 5V,<br>$V_{OUT}$ = 0.8V to 1.8V,<br>$I_{OUT}$ = 1A to 3A<br>Spread spectrum enabled | 1.95 |      | 2.65 | MHz     |

<sup>(1)</sup> PVIN\_Bx must not exceed VSYS

#### 6.7 BUCK2, BUCK3 Converter

over operating free-air temperature range (unless otherwise noted)

| POS      |                            | PARAMETER                                                                          | TEST CONDITIONS                                                                                                                           | MIN  | TYP | MAX | UNIT       |

|----------|----------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------------|

| Electric | al Characteristics         |                                                                                    |                                                                                                                                           |      |     | '   |            |

| 6.1.1a   | V <sub>IN_BUCK23</sub>     | Input Voltage <sup>(1)</sup>                                                       | Buck supply voltage, maximum VSYS                                                                                                         | 2.5  |     | 5.5 | V          |

| 6.1.1b   | Vоит_виск23                | Buck Output Voltage configurable<br>Range                                          | Output voltage configurable in 25mV-steps for $0.6V \leqslant V_{OUT} \leqslant$ 1.4V, in 100mV steps for 1.4V < $V_{OUT} \leqslant$ 3.4V | 0.6  |     | 3.4 | V          |