**TPS53676**

ZHCSN24A - AUGUST 2019 - REVISED MAY 2021

# TPS53676 具有 AVSBus™ 和 PMBus™ 接口的双通道 D-CAP+™ (N+M ≤ 7 相) 压多相控制器

#### 1 特性

- 输入电压范围: 4.5V 至 17V

- 输出电压范围: 0.25V 至 5.5V

- 每相位开关频率范围: 300 kHz 至 2000 kHz

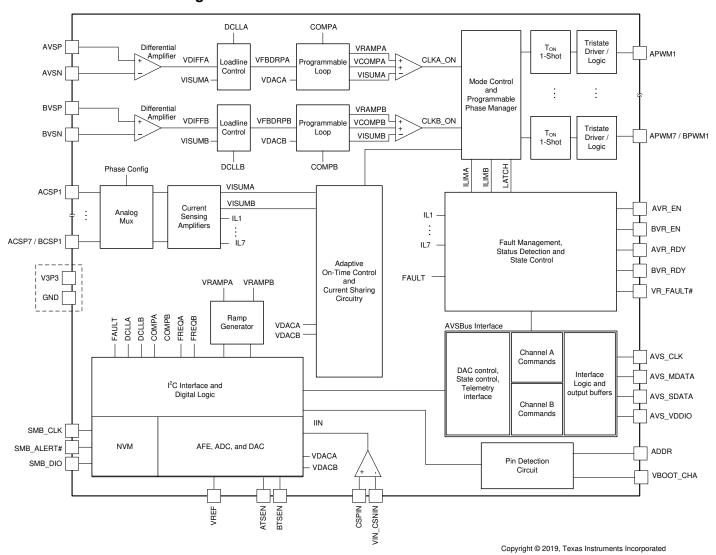

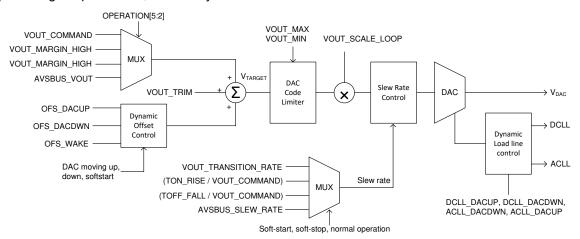

- 支持 N+M 相位配置(N+M≤7, M≤3)的双路

- 根据 PMBus 1.3.1 第 III 部分,符合 AVSBus 标准

- PMBus v1.3.1 系统接口,用于电压、电流、功率、 温度和故障状态的配置、控制和遥测

- 通过 VOUT COMMAND 进行自适应电压调节 (AVS)

- 增强型 D-CAP+ 控制可提供卓越的瞬态性能和出色 的动态电流共享

- 可编程环路补偿

- 灵活的相位触发顺序

- 用于通道 A 启动电压设置的外部引脚搭接

- 单独的相电流校准和报告

- 相位热平衡管理 (TBM)

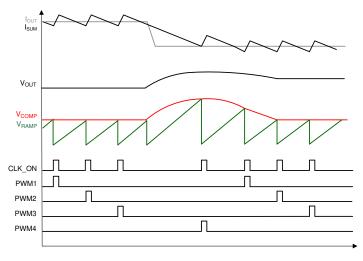

- 完全支持动态切相 (DPS)

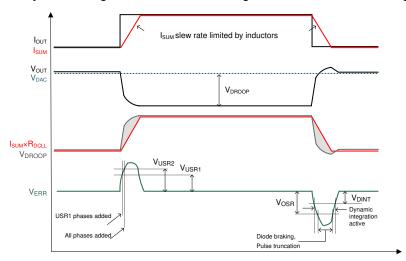

- 快速添相以减弱下冲 (USR)

- 针对过冲衰减 (OSR) 的体二极管制动

- 无驱动器配置,有助于实现高效的高频开关

- 与 TI NexFET™ 功率级完全兼容,可实现高密度解 决方案

- 精确的可编程自适应电压定位 (AVP)

- 获得专利的 AutoBalance™ 相位平衡

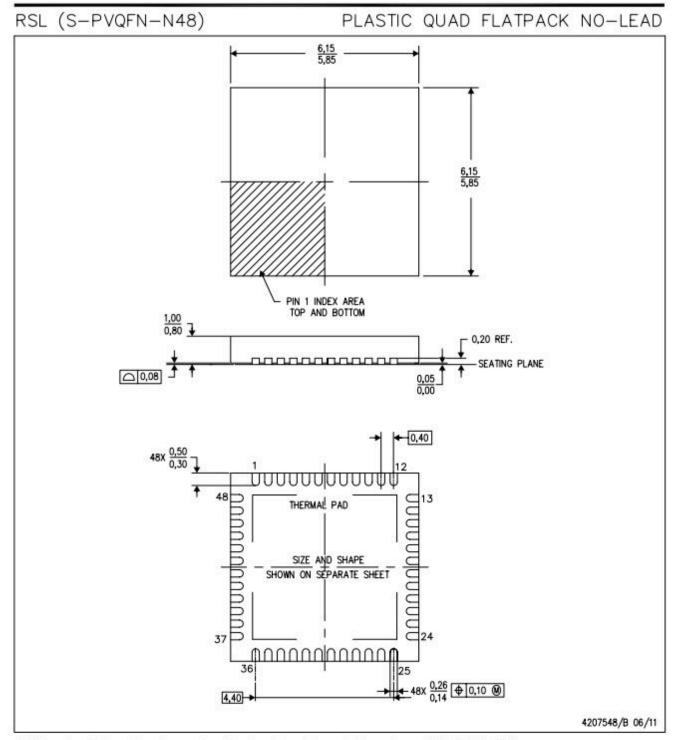

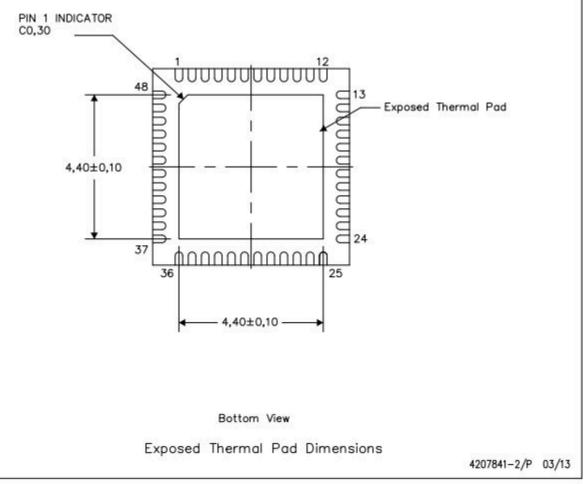

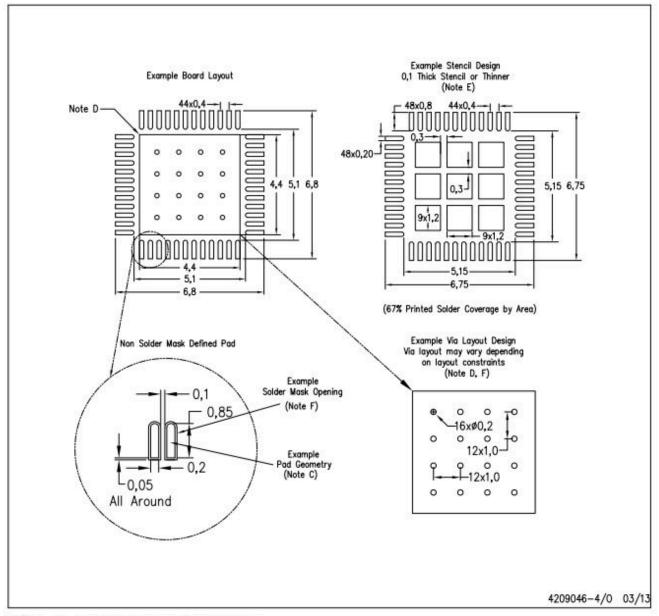

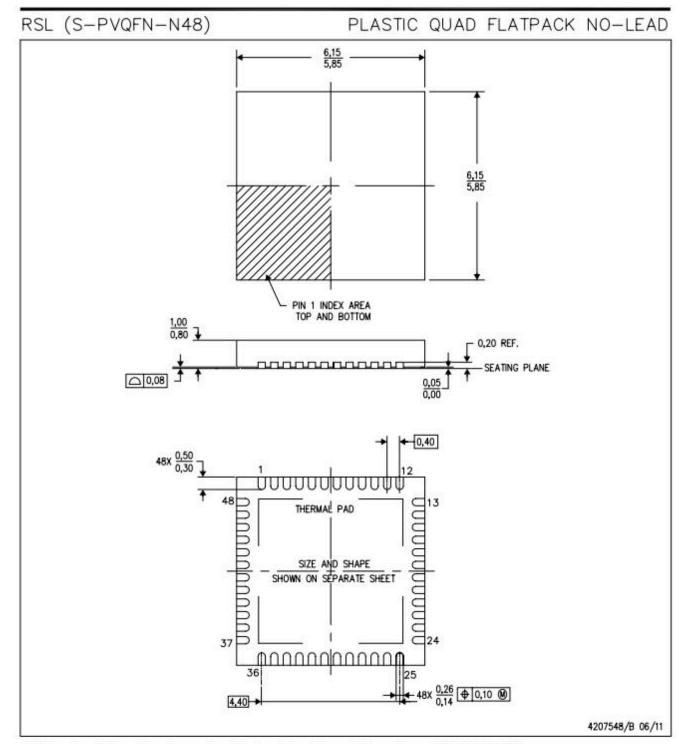

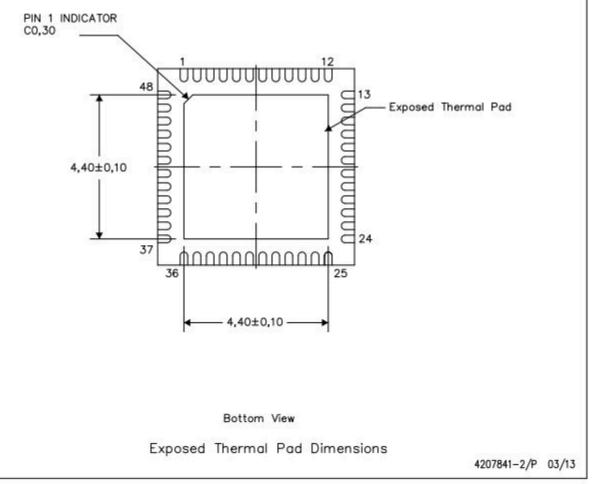

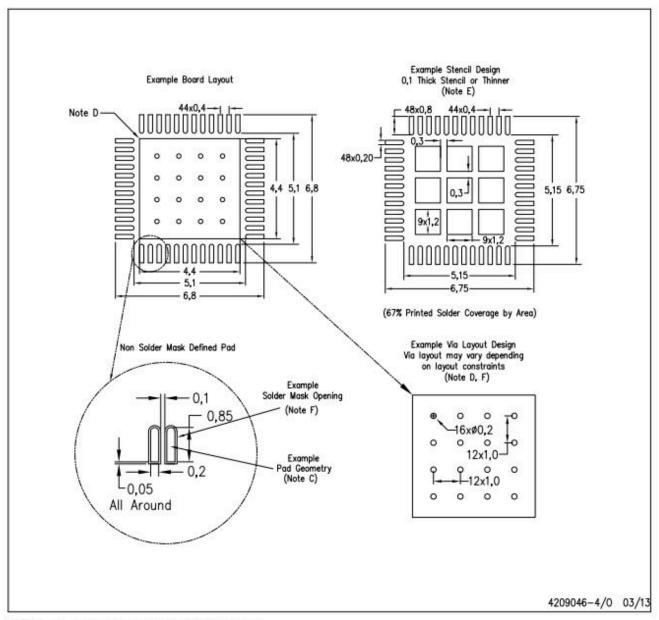

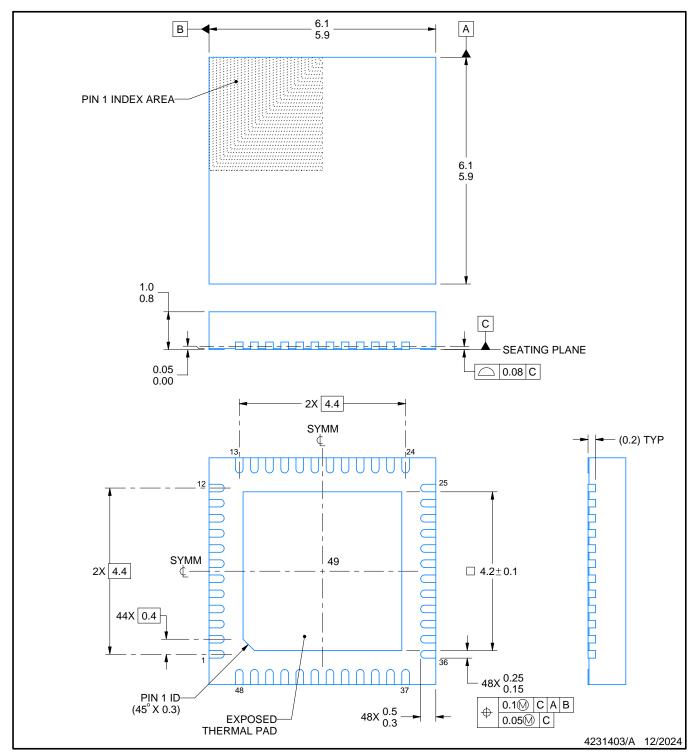

- 6 mm × 6 mm 48 引脚 QFN 封装

#### 2 应用

- 数据中心网络交换机

- 校园网交换机和分支交换机

- 核心和边缘路由器

- 硬件加速器卡

- 高性能 CPU/ASIC/FPGA 电源

#### 3 说明

TPS53676 是一款具有双通道、内置非易失性存储器 (NVM) 和 PMBus™ 兼容串行接口的降压控制器,与 TI NexFET™ 智能功率级完全兼容。D-CAP+™ 架构等高 级控制特性可提供快速瞬态响应、低输出电容和良好的 电流共享。该器件还提供新颖的相位交错策略和灵活的 触发序列,来提高热性能。还支持输出电压转换率和电 压定位的可调控制。此外,该器件还支持 PMBus 通信 接口,可向系统主机报告遥测的电压、电流、功率、温 度和故障状况。所有可编程参数均可通过串行接口进行 配置,而且可作为新的默认值存储在 NVM 中,来尽可 能减少外部组件数量。

TPS53676 器件采用热增强型 48 引脚 QFN 封装,额 定工作温度为 - 40°C 至 125°C。

#### 器件信息

| 器件型号     | 封装 <sup>(1)</sup> | 封装尺寸 ( 标称值 ) |  |

|----------|-------------------|--------------|--|

| TPS53676 | QFN (48)          | 6mm × 6mm    |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

简化版应用

## **Table of Contents**

| 1 特性                                     | 7.7 Power supply fault protection60         |

|------------------------------------------|---------------------------------------------|

| 2 应用                                     |                                             |

| - <i>—,-,-</i><br>3 说明                   |                                             |

| 4 Revision History                       |                                             |

| 5 Pin Configuration and Functions        |                                             |

| 6 Specifications                         | 0 D 0   - 0 D   - 4!   - 400                |

| 6.1 Absolute Maximum Ratings             | 6 10 Layout130                              |

| 6.2 Recommended Operating Conditions     | 44 Davilaa awal Daawwaaw4a4law Oww.aaw4 400 |

| 6.3 ESD Ratings                          | 4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.      |

| 6.4 Electrical Specifications            |                                             |

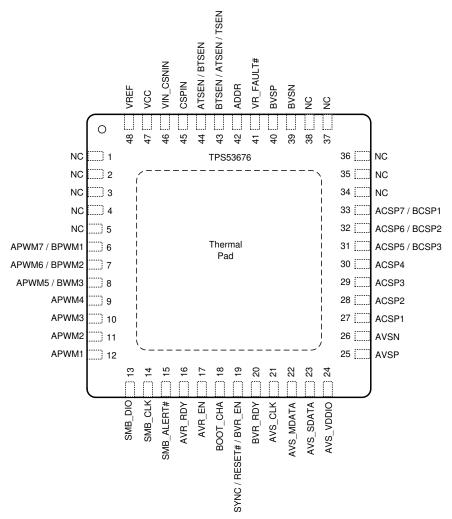

| 7 Detailed Description3                  |                                             |

| 7.1 Overview3                            | 0 11.4 静电放电警告132                            |

| 7.2 Functional Block Diagram3            |                                             |

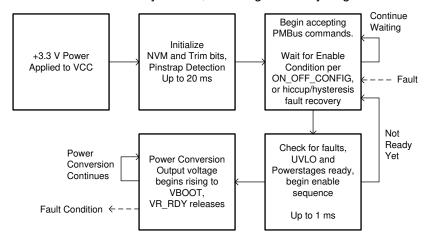

| 7.3 Power-up and initialization3         |                                             |

| 7.4 Pin connections and bevahior3        |                                             |

| 7.5 Advanced power management functions4 | 3 12.1 Package Option Addendum              |

| 7.6 Control Loop Theory of Operation5    |                                             |

|                                          |                                             |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| C | hanges from Revision * (December 2020) to Revision A (April 2021) | Page |

|---|-------------------------------------------------------------------|------|

| • | Updated R <sub>HA</sub> resistor values column 表 7-2              | 33   |

## 5 Pin Configuration and Functions

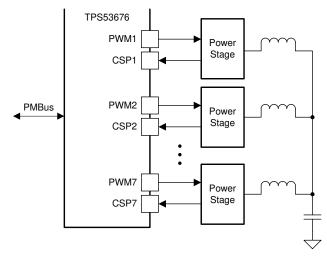

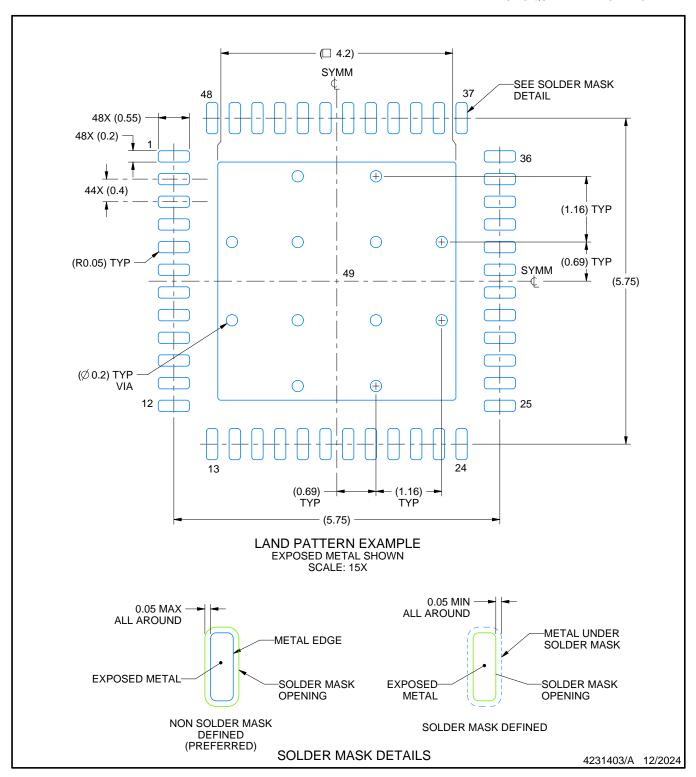

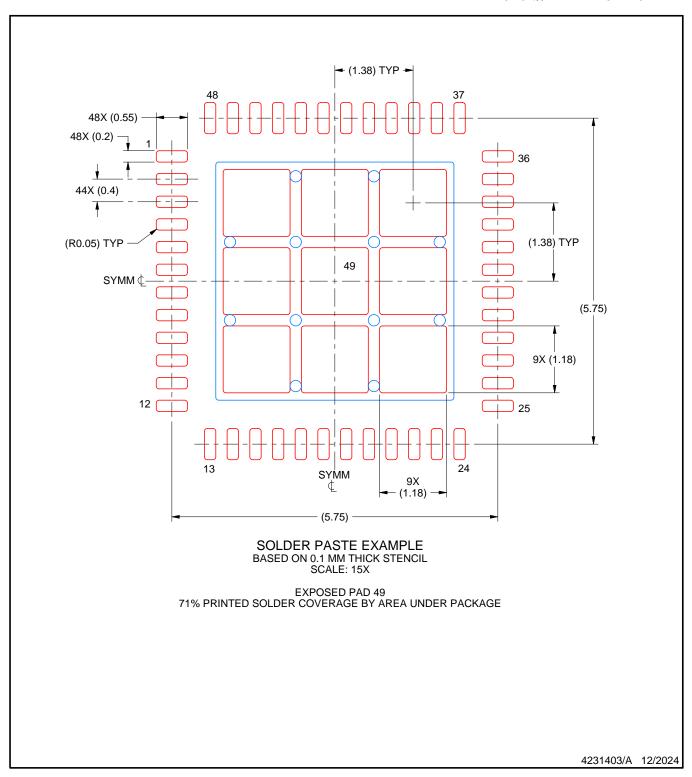

图 5-1. RSL Package 48-Pin QFN (Top View)

表 5-1. Default Functionality of Multifunction Pins

| PIN <sup>(1)</sup> | DEFAULT    |

|--------------------|------------|

| 7, 8, 31, 32       | APWM, ACSP |

| 6, 33              | BPWM, BCSP |

| 19                 | BVR_EN     |

| 43                 | BTSEN      |

| 44                 | ATSEN      |

(1) Default settings can be changed through NVM settings

## 表 5-2. Pin Functions

| PIN           |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|---------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME          | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| ACSP1         | 27  | ı   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| ACSP2         | 28  | I   | Current sense input for channel A. Connect to the IOUT pin of TI smart power stages. Float unused                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| ACSP3         | 29  | I   | CSP pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ACSP4         | 30  | ı   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| ACSP5 / BCSP3 | 31  | I   | Current sense input for phase 7 of channel A or phase 3 of channel B. Float unused CSP pins.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ACSP6 / BCSP2 | 32  | I   | Current sense input for phase 7 of channel A or phase 2 of channel B. Float unused CSP pins.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ACSP7 / BCSP1 | 33  | ı   | Current sense input for phase 7 of channel A or phase 1 of channel B. Float unused CSP pins.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| NC            | 34  | -   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NC            | 35  | -   | Oo not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NC            | 36  | -   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NC            | 37  | -   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NC            | 38  | -   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

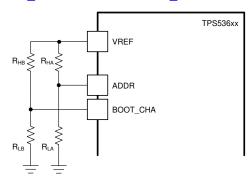

| ADDR          | 42  | I   | Voltage divider to VREF and GND. The value of a resistor connected between this pin and GND and the voltage level set the PMBus address. Latched at VCC power up. Use the PIN_DETECT_OVERRIDE command to select addresses which are not available through pinstrap.                                                                                                                                                                                                    |  |  |  |

| APWM1         | 12  | 0   | PWM signal for phase 1 of channel A. Float unused PWM pins.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| APWM2         | 11  | 0   | PWM signal for phase 2 of channel A. Float unused PWM pins.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| APWM3         | 10  | 0   | PWM signal for phase 3 of channel A. Float unused PWM pins.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| APWM4         | 9   | 0   | PWM signal for phase 4 of channel A. Float unused PWM pins.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| APWM5 / BPWM3 | 8   | 0   | PWM signal for phase 5 of channel A, or phase 3 of channel B. Float unused PWM pins.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| APWM6 / BPWM2 | 7   | 0   | PWM signal for phase 6 of channel A, or phase 2 of channel B. Float unused PWM pins.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| APWM7 / BPWM1 | 6   | 0   | PWM signal for phase 7 of channel A, or phase 1 of channel B. Float unused PWM pins.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| NC            | 5   | -   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NC            | 4   | -   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NC            | 3   | -   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NC            | 2   | -   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NC            | 1   | -   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| ATSEN / BTSEN | 44  | I   | Multi-function pin. Configure through PMBus.  ATSEN (default): Connect to the TAO pin of the TI smart power stages of channel A to sense the highest temperature of the power stages and to sense the built-in fault signal from the power stages.  BTSEN: Connect to the TAO pin of the TI smart power stages of channel B to sense the highest temperature of the power stages and to sense the built-in fault signal from the power stages. Float unused TSEN pins. |  |  |  |

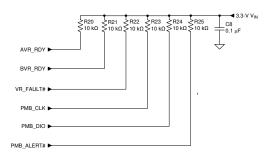

| AVR_EN        | 17  | ı   | Active high enable input for channel A. By default, asserting the AVR_EN pin activates channel A. Polarity and enable conditions are programmable through ON_OFF_CONFIG.                                                                                                                                                                                                                                                                                               |  |  |  |

| AVR_RDY       | 16  | 0   | VRD "Ready" output signal of channel A. This open drain output requires an external pull-up resistor. The AVR_RDY pin is pulled low when a shutdown fault occurs.                                                                                                                                                                                                                                                                                                      |  |  |  |

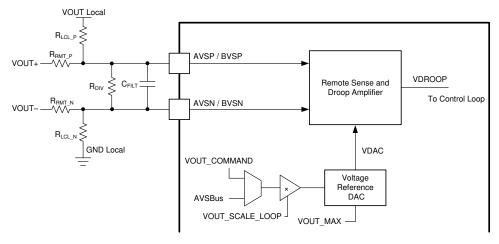

| AVSN          | 26  | I   | Negative input of the remote voltage sense of channel A.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| AVSP          | 25  | I   | Positive input of the remote voltage sense of channel A.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

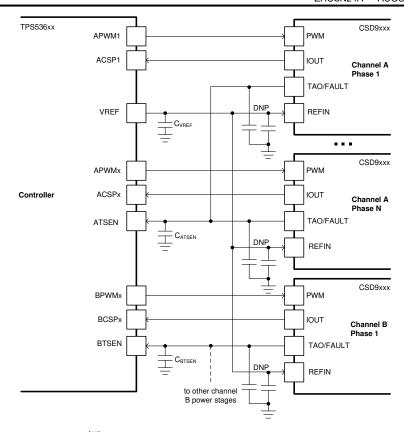

| AVS_CLK       | 21  | ı   | AVSBus clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| AVS_MDATA     | 22  | I   | AVSBus master data (MOSI)                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| AVS_SDATA     | 23  | 0   | AVSBus slave data (MISO)                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| AVS_VDDIO     | 24  | I   | AVSBus supply pin. Bypass to ground with minimum 1uF effective ceramic capacitance and connect to a well regulated supply voltage which supplies the logic levels for the AVS communication interface.                                                                                                                                                                                                                                                                 |  |  |  |

| BOOT_CHA      | 18  | I   | Pinstraps for Channel A boot voltage (8 bits). Use the PIN_DETECT_OVERRIDE command to select options which are not available through pinstrap.                                                                                                                                                                                                                                                                                                                         |  |  |  |

## 表 5-2. Pin Functions (continued)

| PIN                       |     |     | DECORPTION .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                      | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BTSEN / ATSEN /<br>TSEN   | 43  | I   | Multi-function pin. Configure through PMBus.  BTSEN (default): Connect to the TAO pin of the TI smart power stages of channel B to sense the highest temperature of the power stages and to sense the built-in fault signal from the power stages.  BTSEN: Connect to the TAO pin of the TI smart power stages of channel A to sense the highest temperature of the power stages and to sense the built-in fault signal from the power stages.  TSEN: Connect to the TAO pin of the TI smart power stages of channels A and B to sense the highest temperature of the power stages and to sense the built-in fault signal from the power stages.  Float unused TSEN pins.                                         |

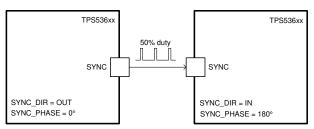

| BVR_EN /<br>RESET# / SYNC | 19  | I/O | Multi-function pin. Configure through PMBus.  BVR_EN (Default): Active high enable input for channel B. Asserting the BVR_EN pin activates channel B. Polarity and enable conditions are programmable through ON_OFF_CONFIG.  RESET#: Active low signal which causes both channels output voltage target to revert to their respective VBOOT values when asserted. Pull-up to 3.3 V.  SYNC: If assigned as an output, this pin provides a free-running clock for other TPS53676 devices to synchronize to. If assigned as an input, an internal phase locked-loop can synchronize switching of one or both channels to a clock supplied to this pin. Phase shift and data direction are programmable through NVM. |

| BVR_RDY                   | 20  | 0   | VRD "Ready" output signal of channel B. This open drain output requires an external pull-up resistor. The BVR_RDY pin is pulled low when a shutdown fault occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BVSN                      | 39  | ı   | Negative input of the remote voltage sense of channel B. If channel B is not used, connect BVSN to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BVSP                      | 40  | ı   | Positive input of the remote voltage sense of channel B. If channel B is not used, connect BVSP to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

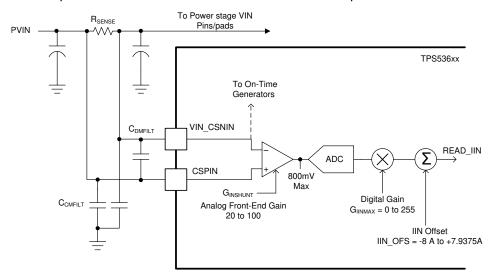

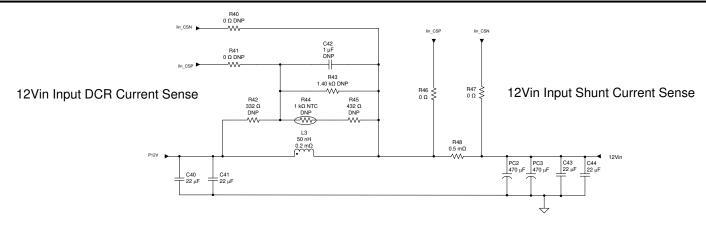

| CSPIN                     | 45  | I   | Positive terminal of the integrated high-side current sensing amplifier. Connect to the supply side of the input current sense element. Tie to VIN_CSNIN, and to the input voltage, if measured input current sensing is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SMB_ALERT#                | 15  | 0   | SMBus or I <sup>2</sup> C bi-directional alert pin interface. (Open drain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SMB_CLK                   | 14  | ı   | SMBus or I <sup>2</sup> C serial clock interface. (Open drain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SMB_DIO                   | 13  | I/O | SMBus or I <sup>2</sup> C bi-directional serial data interface. (Open drain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCC                       | 47  | Р   | 3.3-V power input. Bypass to GND with a ceramic capacitor with a value greater than or equal to 1 $\mu$ F. Used to power all digital logic circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VIN_CSNIN                 | 46  | I   | Negative terminal of the integrated high-side current sense amplifier. Connect to the power-stage side of the current sense element. The VIN_CSNIN voltage is also used to determine the correct on-time for the converter. Tie to CSPIN, and to the input voltage, if measured input current sensing is not used.                                                                                                                                                                                                                                                                                                                                                                                                |

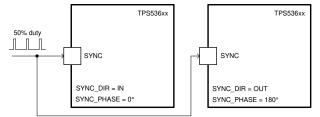

| VREF                      | 48  | 0   | 1.5-V LDO reference voltage. Bypass to GND with 1-µF effective ceramic capacitor. Connect the VREF pin to the REFIN pin of the TI smart power stages as the current sense common-mode voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VR_FAULT#                 | 41  | 0   | VR fault indicator. (Open-drain). The failures include the high-side FETs short, over-voltage, over-temperature, and the input over-current conditions. Use the fault signal on the platform to remove the power source by turning off the AC power supply. When the failure occurs, the VR_FAULT# pin is LOW, and put the controller into latch-off mode.                                                                                                                                                                                                                                                                                                                                                        |

| Thermal Pad               | 1   | G   | Analog ground pad. Connect to GND plan with vias.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)

|                        | and the second s | MIN   | MAX                   | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|------|

|                        | CSPIN, VIN_CSNIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - 0.3 | 19                    | V    |

|                        | Pin voltage, duration less than 100 ns ACSP1, ACSP2, ACSP3, ACSP4, ACSP5 / BCSP3, ACSP6 / BCSP2, ACSP7 / BCSP1, ADDR, ATSEN / BTSEN, AVR_EN, AVSP, AVS_VDDIO, BOOT_CHA, BTSEN / ATSEN / TSEN, BVSP, BVR_EN / RESET# / SYNC, SMB_CLK, SMB_DIO, VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - 0.3 | 5.0                   | V    |

| Input voltage (1) (2)  | Pin voltage, duration greater than or equal to 100 ns ACSP1, ACSP2, ACSP3, ACSP4, ACSP5 / BCSP3, ACSP6 / BCSP2, ACSP7 / BCSP1, ADDR, ATSEN / BTSEN, AVR_EN, AVSP, AVS_VDDIO, BOOT_CHA, BTSEN / ATSEN / TSEN, BVSP, BVR_EN / RESET# / SYNC, SMB_CLK, SMB_DIO, VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - 0.3 | 3.6                   | V    |

|                        | AVS_CLK, AVS_MDATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -0.3  | AVS<br>VDDIO +<br>0.5 | V    |

|                        | AVSN, BVSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 0.3 | 0.3                   | V    |

|                        | Pin voltage, duration less than 100 ns<br>APWM1, APWM2, APWM3, APWM4, APWM5 / BPWM3, APWM6 / BPWM2,<br>APWM7 / BPWM1, AVR_RDY, BVR_RDY, SMB_ALERT#, VR_FAULT#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 0.3 | 5.0                   | V    |

| Output voltage (1) (2) | Pin voltage, duration greater than or equal to 100 ns APWM1, APWM2, APWM3, APWM4, APWM5 / BPWM3, APWM6 / BPWM2, APWM7 / BPWM1, AVR_RDY, BVR_RDY, SMB_ALERT#, VR_FAULT#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 0.3 | 3.6                   | V    |

|                        | AVS_SDATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -0.3  | AVS<br>VDDIO +<br>0.5 | V    |

|                        | VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - 0.3 | 1.65                  | V    |

| Operating junction ten | nperature, T <sub>J</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - 40  | 150                   | °C   |

| Storage temperature,   | T <sub>STG</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - 55  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### (2) All voltage values are with respect to the network ground terminal GND unless otherwise noted.

## **6.2 Recommended Operating Conditions**

|               |                                                                                                                                                                                      | MIN   | NOM | MAX          | UNIT |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|--------------|------|

|               | CSPIN, VIN_CSNIN                                                                                                                                                                     | 4.5   | 12  | 17           |      |

|               | VCC                                                                                                                                                                                  | 2.97  | 3.3 | 3.6          |      |

| Input voltage | ACSP1, ACSP2, ACSP3, ACSP4, ACSP5 / BCSP3, ACSP6 / BCSP2, ACSP7 / BCSP1, ATSEN / BTSEN, AVR_EN, AVSP, BOOT_CHA, BTSEN / ATSEN / TSEN, BVSP, BVR_EN / RESET# / SYNC, SMB_CLK, SMB_DIO | - 0.1 | 3.6 |              | V    |

| mpat voltage  | AVS_VDDIO                                                                                                                                                                            | 1.14  |     | 3.6          | •    |

|               | AVS_CLK, AVS_MDATA                                                                                                                                                                   | -0.1  |     | AVS<br>VDDIO |      |

|               | ADDR                                                                                                                                                                                 |       |     | 1.52         |      |

|               | AVSN, BVSN                                                                                                                                                                           | - 0.1 |     | 0.1          |      |

|                      |                                                                                                                  | MIN   | NOM MAX      | UNIT |

|----------------------|------------------------------------------------------------------------------------------------------------------|-------|--------------|------|

|                      | VREF                                                                                                             | - 0.1 | 1.52         |      |

| Output voltage       | APWM1, APWM2, APWM3, APWM4, APWM5 / BPWM3, APWM6 / BPWM2, APWM7 / BPWM1, AVR_RDY, BVR_RDY, SMB_ALERT#, VR_FAULT# | - 0.1 | 3.6          | V    |

|                      | AVS_SDATA                                                                                                        | -0.1  | AVS<br>VDDIO |      |

| Ambient temperature, | T <sub>A</sub>                                                                                                   | - 40  | 125          | °C   |

## 6.3 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| \/                 | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.4 Electrical Specifications

#### **6.4.1 Thermal Information**

|                        |                                              | TPS53676   |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC(1)                            | RSL (VQFN) | UNIT |

|                        |                                              | 48 PINS    |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 25.2       | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 14.8       | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 7.9        | °C/W |

| $\Psi$ JT              | Junction-to-top characterization parameter   | 0.2        | °C/W |

| Y <sub>JB</sub>        | Junction-to-board characterization parameter | 7.8        | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### **6.4.2 Supply**

VCC = 3.3 V, CSPIN = VIN\_CSNIN = 12 V,  $T_J$  = -40 to 125  $^{\circ}{\rm C}$  unless otherwise specified

|                                            | PARAMETER                                 | TEST CONDITIONS  | MIN  | TYP MAX | UNIT |  |  |  |  |  |

|--------------------------------------------|-------------------------------------------|------------------|------|---------|------|--|--|--|--|--|

| Supply: Currents, UVLO, and Power-On Reset |                                           |                  |      |         |      |  |  |  |  |  |

| I <sub>VCC</sub>                           | VCC supply current with all phases active | Enable = 'HI '   |      | 100     | mA   |  |  |  |  |  |

| V <sub>CCNORMAL</sub>                      | VCC Normal Range                          | Normal operation | 2.97 | 3.6     | V    |  |  |  |  |  |

| V <sub>CCUVLOH</sub>                       | VCC UVLO 'OK ' Threshold                  | Ramp up          | 2.92 | 2.97    | V    |  |  |  |  |  |

| V <sub>CCUVLOL</sub>                       | VCC UVLO Fault Threshold                  | Ramp down        | 2.68 | 2.82    | V    |  |  |  |  |  |

| V <sub>CCUVLOH</sub>                       | VCC UVLO Hysteresis                       | Hyseteresis      | 138  | 600     | mV   |  |  |  |  |  |

#### 6.4.3 DAC and Voltage Feedback

VCC = 3.3 V, CSPIN = VIN\_CSNIN = 12 V,  $T_J$  = -40 to 125  $^{\circ}{\rm C}$  unless otherwise specified

|                     | PARAMETER           | TEST CONDITIONS                           | MIN               | TYP MA | X UN |

|---------------------|---------------------|-------------------------------------------|-------------------|--------|------|

| References: I       | DAC and VREF        |                                           |                   |        |      |

| $V_{MODE}$          | Supported VOUT_MODE | VOUT_MODE = 16h                           | ULINEAI<br>N = -1 | -      |      |

| V <sub>DACRNG</sub> | VDAC range          | No external divider.<br>VOUT_MAX ≤ 1.87 V | 0.25              | 1.     | 37 V |

VCC = 3.3 V, CSPIN = VIN\_CSNIN = 12 V,  $T_J$  = -40 to 125  $^{\circ}$ C unless otherwise specified

|                        | PARAMETER                                                       | TEST CONDITIONS                                                                 | MIN   | TYP    | MAX   | UNIT |

|------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------|-------|--------|-------|------|

|                        |                                                                 | No external divider<br>VOUT_MAX > 1.87 V                                        | 0.50  |        | 3.74  | V    |

| R <sub>DIV</sub>       | External resistor for output voltage scaling with Vout > 3.74 V | VOUT to VSP resistor                                                            |       | 500    |       | Ω    |

|                        |                                                                 | VSP to VSN resistor                                                             |       | 500    |       | Ω    |

| V <sub>DAC</sub>       | VSP accuracy                                                    | $0.25 \leqslant \text{VSP} \leqslant 1 \text{ V, I}_{\text{CORE}} = 0 \text{A}$ | -5    |        | 5     | mV   |

|                        |                                                                 | 1 V < VSP ≤ 1.87 V; I <sub>CORE</sub> = 0A                                      | -0.5  |        | 0.5   | %    |

|                        |                                                                 | 1.87 V < VSP ≤ 5 V; I <sub>CORE</sub> = 0A                                      | -1    | ,      | 1     | %    |

| V <sub>VREF</sub>      | VREF output accuracy                                            | VCC = 2.97 V to 3.6 V, I <sub>VREF</sub> = 0                                    | 1.493 | 1.5    | 1.507 | V    |

| V <sub>VREF(REG)</sub> | VREF load regulation (sourcing)                                 | I <sub>VREF</sub> = 0A to 10 mA                                                 | -8    |        |       | mV   |

|                        | VREF load regulaiton (sinking)                                  | I <sub>VREF</sub> = -10 mA to 0A                                                |       |        | 8     | mV   |

| V <sub>TRIM(RES)</sub> | Vout offset NVM resolution (1)                                  | MFR_SPECIFIC_ED[13:12] = 00b                                                    |       | 0.9765 |       | mV   |

|                        |                                                                 | MFR_SPECIFIC_ED[13:12] = 01b                                                    |       | 1.9531 |       | mV   |

|                        |                                                                 | MFR_SPECIFIC_ED[13:12] = 10b                                                    |       | 3.9063 |       | mV   |

|                        |                                                                 | MFR_SPECIFIC_ED[13:12] = 11b                                                    |       | 7.8125 |       | mV   |

| V <sub>TRIM(RNG)</sub> | Vout offset NVM range (1)                                       | VOUT_TRIM in SLINEAR16 format                                                   | -128  |        | 127   | LSB  |

| Voltage Sen            | se: AVSP/BVSP and AVSN/BVSN                                     |                                                                                 |       |        | 1     |      |

| I <sub>AVSP</sub>      | AVSP Input Bias Current                                         | Not in Fault, Disable or UVLO;<br>AVSP = VDAC = 1.8 V<br>AVSN = 0 V             |       |        | 50    | μΑ   |

| I <sub>AVSN</sub>      | AVSN Input Bias Current                                         | Not in Fault, Disable or UVLO;<br>AVSP = VDAC = 1.8 V,<br>AVSN = 0 V            | -55   |        |       | μΑ   |

| I <sub>BVSP</sub>      | BVSP Input Bias Current                                         | Not in Fault, Disable or UVLO;<br>BVSP = VDAC = 1.8 V,<br>BVSN = 0 V            |       |        | 50    | μΑ   |

| I <sub>BVSN</sub>      | BVSN Input Bias Current                                         | Not in Fault, Disable or UVLO;<br>BVSP = VDAC = 1.8 V,<br>BVSN = 0 V            | -55   |        |       | μΑ   |

<sup>(1)</sup> Specified by Design.

#### **6.4.4 Control Loop Parameters**

VCC = 3.3 V, CSPIN = VIN\_CSNIN = 12 V,  $T_J$  = -40 to 125  $^{\circ}$ C unless otherwise specified

|                        | PARAMETER                          | TEST CONDITIONS                                                       | MIN TYP | MAX | UNIT |

|------------------------|------------------------------------|-----------------------------------------------------------------------|---------|-----|------|

| Programma              | ble Loadline and Loop Compensation | n                                                                     |         | -   |      |

| R <sub>DCLL(RES)</sub> | DC load line resolution            | VOUT_DROOP = 0 to 1 m $\Omega$                                        | 7.8125  | 5   | μΩ   |

|                        |                                    | VOUT_DROOP = 1 to 2 m $\Omega$                                        | 15.625  | 5   | μΩ   |

|                        |                                    | VOUT_DROOP = 2 to 4 m $\Omega$                                        | 31.25   | 5   | μΩ   |

|                        |                                    | VOUT_DROOP = 4 to 8 m $\Omega$                                        | 62.5    | 5   | μΩ   |

| R <sub>DCLL(ACC)</sub> | DC load line accuracy              | VOUT_DROOP > 0.3 m Ω                                                  | -2.5    | 2.5 | %    |

| R <sub>ACLL(RES)</sub> | AC loadline resolution (1)         | USER_DATA_01[47:32] = 0 m $\Omega$ (program in SLINEAR11 format)      | 15.625  | 5   | μΩ   |

|                        |                                    | USER_DATA_01[47:32] = 1 to 2 m $\Omega$ (program in SLINEAR11 format) | 31.25   | 5   | μΩ   |

|                        |                                    | USER_DATA_01[47:32] = 2 to 4 m $\Omega$ (program in SLINEAR11 format) | 62.5    | 5   | μΩ   |

|                        |                                    | USER_DATA_01[47:32] = 4 to 8 m $\Omega$ (program in SLINEAR11 format) | 125     | 5   | μΩ   |

| R <sub>ACLL(RES)</sub> | AC loadline accuracy (1)           | AC loadline > 0.3 m $\Omega$                                          | -5      | 5   | %    |

|                    | PARAMETER                                                                        | TEST CONDITIONS             | MIN   | TYP | MAX   | UNIT |

|--------------------|----------------------------------------------------------------------------------|-----------------------------|-------|-----|-------|------|

| t <sub>INT</sub>   | Static integration-time constant (1)                                             | USER_DATA_01[23:20] = 0000b | 0.9   | 1   | 1.1   | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 0001b | 1.8   | 2   | 2.2   | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 0010b | 2.7   | 3   | 3.3   | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 0011b | 3.6   | 4   | 4.4   | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 0100b | 4.5   | 5   | 5.5   | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 0101b | 5.4   | 6   | 6.6   | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 0110b | 6.3   | 7   | 7.7   | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 0111b | 7.2   | 8   | 8.8   | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 1000b | 8.1   | 9   | 9.9   | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 1001b | 9     | 10  | 11    | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 1010b | 9.9   | 11  | 12.1  | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 1011b | 10.8  | 12  | 13.2  | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 1100b | 11.7  | 13  | 14.3  | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 1101b | 12.6  | 14  | 15.4  | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 1110b | 13.5  | 15  | 16.5  | μs   |

|                    |                                                                                  | USER_DATA_01[23:20] = 1111b | 14.4  | 16  | 17.6  | μs   |

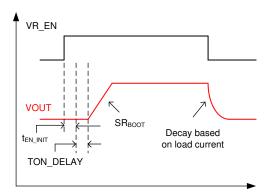

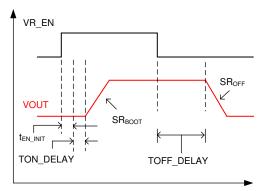

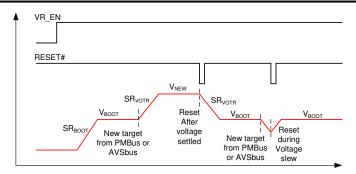

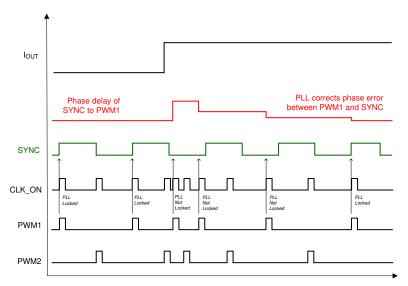

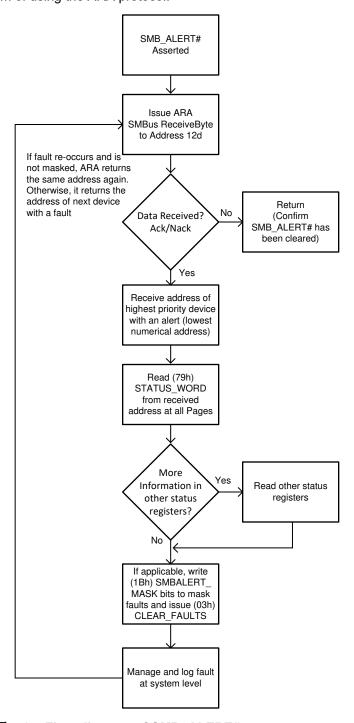

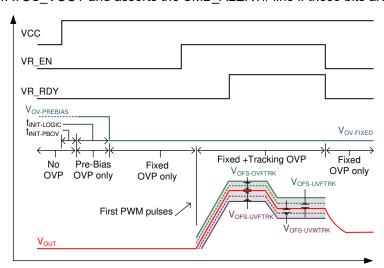

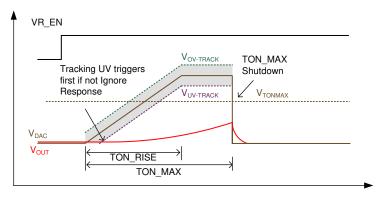

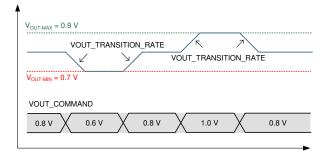

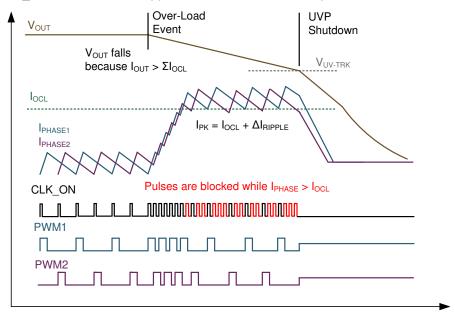

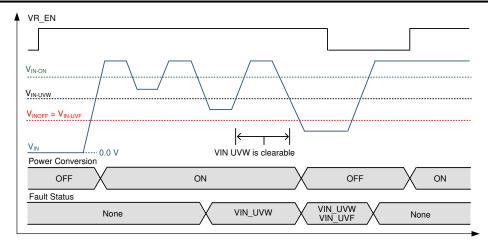

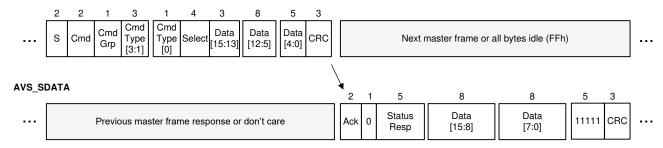

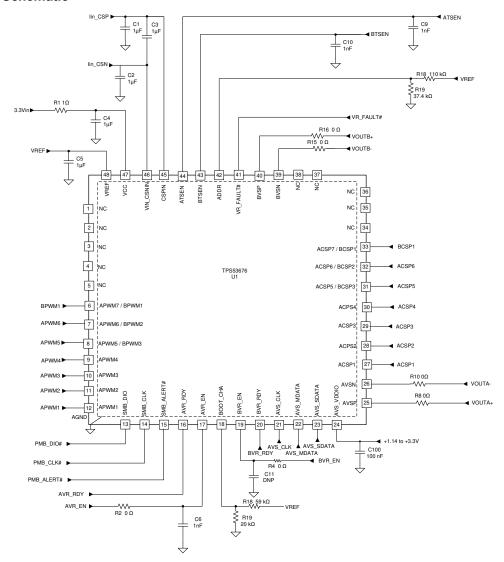

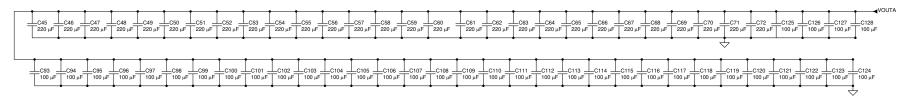

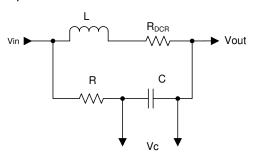

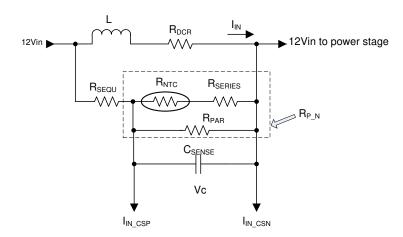

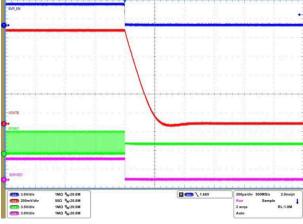

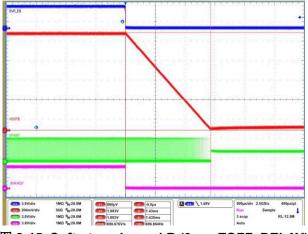

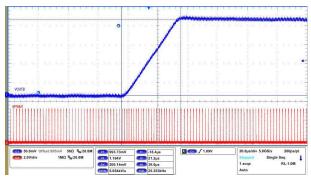

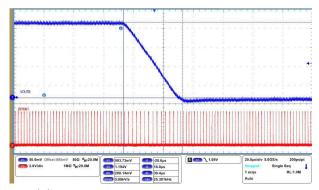

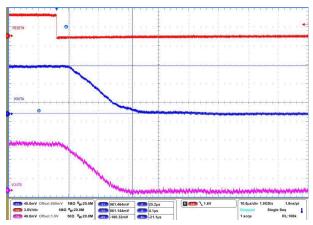

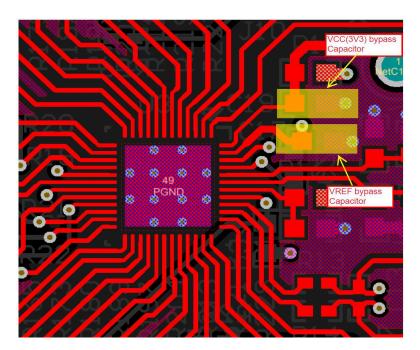

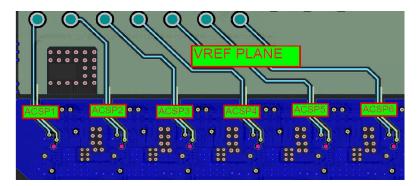

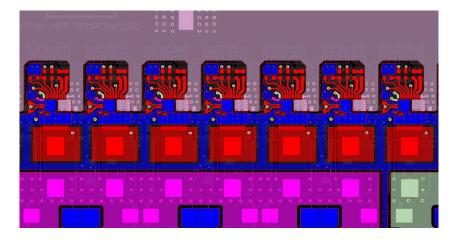

| t <sub>DINT</sub>  | Dynamic integration-time constant (1)                                            | USER_DATA_01[27:24] = 0000b | 0.8   | 1   | 1.2   | μs   |