TPS40210-Q1, TPS40211-Q1 AUGUST 2008 - REVISED JUNE 2020

# TPS4021x-Q1 4.5V 至 52V 输入、电流模式升压控制器

# 1 特性

- 符合汽车应用要求

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 1:-40°C 至 125°C 的环境工作温 度范围

- 器件 HBM ESD 分类等级 2

- 器件 CDM ESD 分类等级 C4B

- 功能安全型

- 可提供用于功能安全系统设计的文档

- 适用于升压、反激式、SEPIC 拓扑和 LED 驱动器

- 宽输入工作电压范围: 4.5V 至 52V

- 可调振荡器频率

- 固定频率电流模式控制

- 内部斜率补偿

- 集成式低侧驱动器

- 可编程闭环软启动

- 过流保护

- 支持外部同步

- 基准电压:700mV (TPS40210-Q1)、 260mV (TPS40211-Q1)

- 低电流禁用功能

# 2 应用

- 信息娱乐系统和仪表组应用

- 汽车车身电子装置(照明)

- HEV/EV 和动力总成

# 3 说明

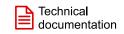

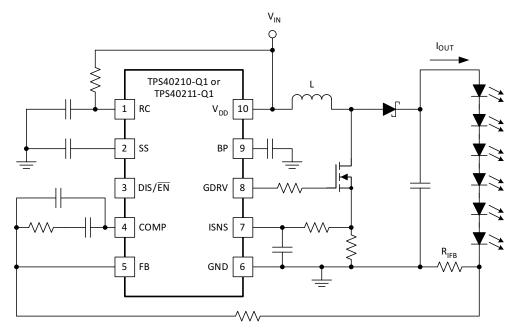

TPS40210-Q1 和 TPS40211-Q1 器件是宽输入电压 (4.5V至52V)异步升压控制器,适用于需要源极接 地 N 沟道 FET 的升压、反激式、SEPIC 拓扑以及各种 LED 驱动器应用。器件特性包括可编程软启动、具有 自动重试功能的过流保护以及可编程振荡器频率。电流 模式控制可改善瞬态响应并简化环路补偿。这两个器件 之间的主要差异是误差放大器调节的 FB 引脚基准电 压。

# 器件信息(1)

| 器件型号        | 封装         | 封装尺寸(标称值)       |

|-------------|------------|-----------------|

| TPS40210-Q1 | PDSO (10)  | 3.00mm × 3.00mm |

| TPS40211-Q1 | 1 000 (10) | 3.00mm × 3.00mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附

简化版原理图

# **Table of Contents**

| 1 特性                                             | 1 7.4 Device Functional Modes                     | <mark>2</mark> 3                       |

|--------------------------------------------------|---------------------------------------------------|----------------------------------------|

| 2 应用                                             |                                                   | 2                                      |

| 3 说明                                             |                                                   |                                        |

| 4 Revision History                               |                                                   |                                        |

| 5 Pin Configuration and Functions                |                                                   |                                        |

| Pin Functions                                    | 40.14                                             |                                        |

| 6 Specifications                                 |                                                   | 34                                     |

| 6.1 Absolute Maximum Ratings                     |                                                   |                                        |

| 6.2 ESD Ratings                                  | 44 Deviles and Description for the second         |                                        |

| 6.3 Recommended Operating Conditions             |                                                   |                                        |

| 6.4 Thermal Information                          |                                                   |                                        |

| 6.5 Electrical Characteristics.                  | 44.0 Delete di Colo                               |                                        |

| 6.6 Timing Requirements                          | 4.4.1 (A.1) A. D. T. A.C. T. L.                   |                                        |

| 6.7 Switching Characteristics                    |                                                   |                                        |

| 6.8 Typical Characteristics                      |                                                   |                                        |

| 7 Detailed Description                           |                                                   |                                        |

| 7.1 Overview                                     |                                                   |                                        |

| 7.2 Functional Block Diagram                     | 11 12 Mechanical, Packaging, and Orderable        |                                        |

| 7.3 Feature Description                          |                                                   | 38                                     |

| 4 Revision History                               | Povision E ( luna 2020)                           | Dog                                    |

| Changes from Revision E (December 2014) to R     |                                                   | Page                                   |

| • 向 <i>节1</i> 添加了功能安全要点                          |                                                   | ······································ |

| Changes from Revision D (April 2010) to Revision | on E (November 2014)                              | Page                                   |

| Added ESD Ratings table, Feature Description:    | section, Device Functional Modes, Application and | <del></del>                            |

Implementation section, Power Supply Recommendations section, Layout section, Device and

Documentation Support section, and Mechanical, Packaging, and Orderable Information section ......4

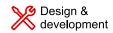

# **5 Pin Configuration and Functions**

图 5-1. DGQ Package 10-Pin PDSO PowerPAD™ Package (Top View)

# **Pin Functions**

| PIN I/O         |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BP              | 9   | 0   | Regulator output. Connect a 1- $\mu$ F bypass capacitor from this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| СОМР            | 4   | 0   | Error amplifier output. Connect a control-loop compensation network between the COMP pin and the FB pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DIS/ EN         | 3   | I   | Disable or enable. Pulling this pin high places the part into a shutdown mode. The prime characteristic of shutdown mode is a very low quiescent current. Shutdown mode disables the functionality of all blocks and shuts down the BP regulator. This pin has an internal $1-M\Omega$ pulldown resistor to GND. Leaving this pin unconnected enables the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FB              | 5   | I   | Error amplifier inverting input. Connect a voltage divider from the output to this pin to set the output voltage. Connect a compensation network between this pin and COMP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GDRV            | 8   | 0   | Connect the gate of the power N-channel MOSFET to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND             | 6   | _   | Device ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ISNS            | 7   | I   | Current sense. Connect an external current-sensing resistor between this pin and GND. The voltage on this pin provides current feedback in the control loop for detecting an overcurrent condition. Declaration of an overcurrent condition occurs when ISNS pin voltage exceeds the overcurrent threshold voltage, 150 mV typical.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

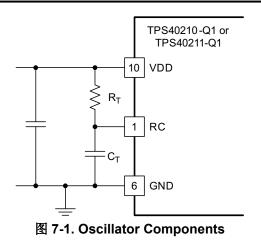

| RC              | 1   | I   | Switching-frequency setting. Connect a capacitor from the RC pin to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and $V_{DD}$ of the IC power supply and a capacitor from RC to $V_{DD}$ of the IC power supply and $V$ |

| SS              | 2   | I   | Soft-start time programming. Connect a capacitor from the SS pin to GND to program the converter soft-start time. This pin also functions as a time-out timer when the power supply is in an overcurrent condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>DD</sub> | 10  | I   | System input voltage. Connect a local bypass capacitor from this pin to GND. Depending on the amount of required slope compensation, connection of this pin to the converter output might be desirable. See the #8 section for additional details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                  |                                               |                     | MIN    | MAX | UNIT |

|------------------|-----------------------------------------------|---------------------|--------|-----|------|

|                  |                                               | $V_{DD}$            | - 0.3  | 52  | V    |

|                  | Input voltage range                           | RC, SS, FB, DIS/ EN | - 0.3  | 10  | V    |

|                  |                                               | ISNS                | - 0.3  | 8   | V    |

|                  | Output voltage range                          | COMP, BP, GDRV      | - 0.3  | 9   | V    |

| TJ               | T <sub>J</sub> Operating junction temperature |                     | - 40°C | 150 | °C   |

| T <sub>stg</sub> | Storage temperature                           |                     | - 55°C | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                                            |                                                         |                                     |                                                                             | VALUE | UNIT |

|--------------------------------------------|---------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                                     | ±2000                                                                       |       |      |

|                                            | Electrostatic discharge                                 | Charged-device model (CDM), per AEC | All pins - Classification<br>level C4B for both All pins<br>and Corner pins | ±750  | V    |

|                                            |                                                         | Corner pins (1, 5, 6, and 10)       | ±750                                                                        |       |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# **6.3 Recommended Operating Conditions**

|          |                                | MIN  | NOM | MAX | UNIT |

|----------|--------------------------------|------|-----|-----|------|

| $V_{DD}$ | Input voltage                  | 4.5  |     | 52  | V    |

| TJ       | Operating junction temperature | - 40 |     | 125 | °C   |

# 6.4 Thermal Information

|                        | (4)                                          | TPS40210-Q1,<br>TPS40211-Q1 |      |

|------------------------|----------------------------------------------|-----------------------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DGQ                         | UNIT |

|                        |                                              | 10 PINS                     |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 67.2                        | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 50.5                        | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 41                          | °C/W |

| ψJT                    | Junction-to-top characterization parameter   | 2.4                         | °C/W |

| ψ ЈВ                   | Junction-to-board characterization parameter | 40.7                        | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 15.6                        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# 6.5 Electrical Characteristics

$T_J = -40$ °C to 125°C,  $V_{DD} = 12 V_{dc}$ , all parameters at zero power dissipation (unless otherwise noted)

|                         | PARAMETER                                     |                     | TEST                                                       | CONDITIONS                                                                      | MIN   | TYP  | MAX  | UNIT       |

|-------------------------|-----------------------------------------------|---------------------|------------------------------------------------------------|---------------------------------------------------------------------------------|-------|------|------|------------|

| VOLTAGE                 | REFERENCE                                     |                     |                                                            |                                                                                 |       |      |      |            |

|                         |                                               | TPS40210-           | COMP = FB,                                                 | T <sub>J</sub> = 25°C                                                           | 693   | 700  | 707  |            |

| \/                      | Foodback voltage range                        | Q1                  | $4.5 \leqslant V_{DD} \leqslant 52 V$                      | - 40°C ≤ T <sub>J</sub> ≤ 125°C                                                 | 686   | 700  | 714  | m\/        |

| $V_{FB}$                | Feedback voltage range                        | TPS40211-           | COMP = FB,                                                 | T <sub>J</sub> = 25°C                                                           | 254   | 260  | 266  | mV         |

|                         |                                               | Q1                  | $4.5 \leqslant V_{DD} \leqslant 52 V$                      | - 40°C ≤ T <sub>J</sub> ≤ 125°C                                                 | 250   | 260  | 270  |            |

| INPUT SUP               | PPLY                                          |                     |                                                            | <u> </u>                                                                        |       |      |      |            |

|                         |                                               |                     | $4.5 \leqslant V_{DD} \leqslant 52 \text{ V, no}$          | switching, V <sub>DIS</sub> < 0.8                                               |       | 1.5  | 2.5  | mA         |

| $I_{DD}$                | Operating current                             |                     | $2.5 \leqslant V_{DIS} \leqslant 7 V$                      |                                                                                 |       | 10   | 20   |            |

|                         |                                               |                     | V <sub>DD</sub> < V <sub>UVLO(on)</sub> , V <sub>DIS</sub> | < 0.8                                                                           |       |      | 530  | μА         |

| UNDERVO                 | LTAGE LOCKOUT (UVLO)                          |                     |                                                            |                                                                                 |       |      |      |            |

| V <sub>UVLO(on)</sub>   | Turnon threshold voltage                      |                     |                                                            |                                                                                 | 4     | 4.25 | 4.5  | V          |

| V <sub>UVLO(hyst)</sub> | UVLO hysteresis                               |                     |                                                            |                                                                                 | 140   | 195  | 240  | mV         |

|                         | For more than a model of                      |                     | $4.5 \leqslant V_{DD} \leqslant 52 V$                      |                                                                                 | - 20% |      | 7%   |            |

|                         | Frequency line regulation                     |                     | $7 \leqslant V_{DD} \leqslant 52 V$                        |                                                                                 | - 10% |      | 7%   |            |

| V <sub>SLP</sub>        | Slope compensation ramp                       | )                   |                                                            |                                                                                 | 520   | 620  | 720  | mV         |

| PWM                     |                                               |                     |                                                            |                                                                                 |       | ,    |      |            |

| $V_{VLY}$               | Valley voltage                                |                     |                                                            |                                                                                 |       | 1.2  |      | V          |

| SOFT-STAF               | RT                                            |                     |                                                            |                                                                                 |       |      |      |            |

| V <sub>SS(ofst)</sub>   | Offset voltage from SS pir<br>amplifier input | n to error          |                                                            |                                                                                 |       | 1    |      | V          |

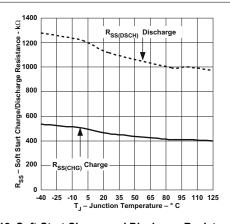

| R <sub>SS(chg)</sub>    | Soft-start charge resistan                    | се                  |                                                            |                                                                                 | 320   | 430  | 600  | L-O        |

| R <sub>SS(dchg)</sub>   | Soft-start discharge resist                   | ance                |                                                            |                                                                                 | 840   | 1200 | 1600 | kΩ         |

| ERROR AN                | /IPLIFIER                                     |                     |                                                            |                                                                                 |       |      |      |            |

| GBWP                    | Unity gain bandwidth prod                     | duct <sup>(1)</sup> |                                                            |                                                                                 | 1.5   | 3.0  |      | MHz        |

| A <sub>OL</sub>         | Open loop gain <sup>(1)</sup>                 |                     |                                                            |                                                                                 | 60    | 80   |      | dB         |

| I <sub>IB(FB)</sub>     | Input bias current (current pin)              | t out of FB         |                                                            |                                                                                 |       | 100  | 300  | nA         |

| I <sub>COMP(src)</sub>  | Output source current                         |                     | V <sub>FB</sub> = 0.6 V, V <sub>COMP</sub> = 1             | 1 V                                                                             | 100   | 250  |      | μ <b>А</b> |

| I <sub>COMP(snk)</sub>  | Output sink current                           |                     | V <sub>FB</sub> = 1.2 V, V <sub>COMP</sub> = 1             | 1 V                                                                             | 1.2   | 2.5  |      | mA         |

| OVERCUR                 | RENT PROTECTION                               |                     |                                                            |                                                                                 |       |      |      |            |

| V <sub>ISNS(oc)</sub>   | Overcurrent detection thre ISNS pin)          | eshold (at          | 4.5 ≤ V <sub>DD</sub> < 52 V, - 4                          | $0^{\circ}\text{C} \leqslant \text{T}_{\text{J}} \leqslant 125^{\circ}\text{C}$ | 120   | 150  | 180  | mV         |

| D <sub>OC</sub>         | Overcurrent duty cycle <sup>(1)</sup>         |                     |                                                            |                                                                                 |       |      | 2%   |            |

| V <sub>SS(rst)</sub>    | Overcurrent reset thresho                     | ld voltage          |                                                            |                                                                                 | 100   | 150  | 350  | mV         |

# **6.5 Electrical Characteristics (continued)**

$T_J = -40$ °C to 125°C,  $V_{DD} = 12 V_{dc}$ , all parameters at zero power dissipation (unless otherwise noted)

|                         | PARAMETER                    | TEST CONDITIONS                                | MIN | TYP | MAX | UNIT |  |  |  |

|-------------------------|------------------------------|------------------------------------------------|-----|-----|-----|------|--|--|--|

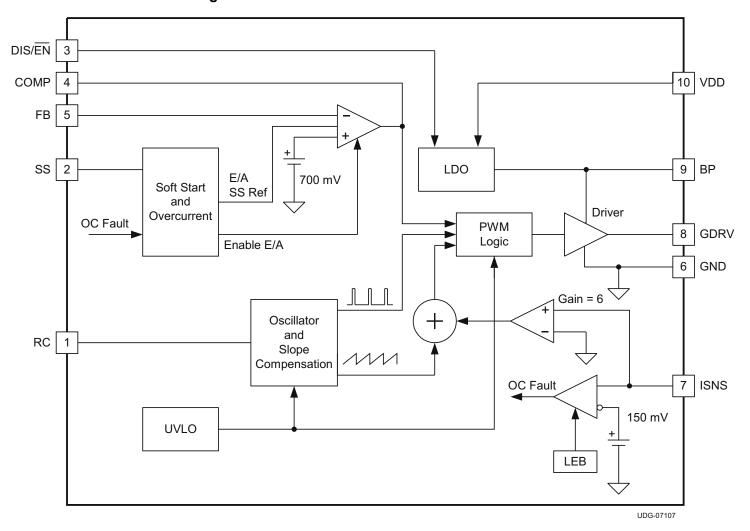

| CURRENT-SENSE AMPLIFIER |                              |                                                |     |     |     |      |  |  |  |

| A <sub>CS</sub>         | Current sense amplifier gain |                                                | 4.2 | 5.6 | 7.2 | V/V  |  |  |  |

| I <sub>B(ISNS)</sub>    | Input bias current           |                                                |     | 1   | 3   | μА   |  |  |  |

| DRIVER                  |                              |                                                |     |     | ,   |      |  |  |  |

| I <sub>GDRV(src)</sub>  | Gate driver source current   | V <sub>GDRV</sub> = 4 V, T <sub>J</sub> = 25°C | 375 | 400 |     | mA   |  |  |  |

| I <sub>GDRV(snk)</sub>  | Gate driver sink current     | V <sub>GDRV</sub> = 4 V, T <sub>J</sub> = 25°C | 330 | 400 |     | ША   |  |  |  |

| LINEAR RE               | EGULATOR                     |                                                |     |     |     |      |  |  |  |

| V <sub>BP</sub>         | Bypass voltage output        | 0 mA < I <sub>BP</sub> < 15 mA                 | 7   | 8   | 9   | V    |  |  |  |

| DISABLE A               | AND ENABLE                   |                                                |     |     |     |      |  |  |  |

| V <sub>DIS(en)</sub>    | Turn-on voltage              |                                                | 0.7 |     | 1.3 | V    |  |  |  |

| V <sub>DIS(hys)</sub>   | Hysteresis voltage           |                                                | 25  | 130 | 220 | mV   |  |  |  |

| R <sub>DIS</sub>        | DIS pin pulldown resistance  |                                                | 0.7 | 1.1 | 1.5 | ΜΩ   |  |  |  |

<sup>(1)</sup> Specified by design

# 6.6 Timing Requirements

|                       |                        |                                       |  | MIN | TYP | MAX | UNIT |  |

|-----------------------|------------------------|---------------------------------------|--|-----|-----|-----|------|--|

| PWM                   |                        |                                       |  |     |     |     |      |  |

| tau                   | Minimum pulse duration | V <sub>DD</sub> = 12 V <sup>(1)</sup> |  |     | 275 | 400 |      |  |

| <sup>t</sup> ON(min)  |                        | V <sub>DD</sub> = 30 V                |  |     | 90  | 200 | ns   |  |

| t <sub>OFF(min)</sub> | Minimum off-time       |                                       |  |     | 170 | 200 |      |  |

| OVERCU                | OVERCURRENT PROTECTION |                                       |  |     |     |     |      |  |

| t <sub>BLNK</sub>     | Leading edge blanking  |                                       |  |     | 75  |     | ns   |  |

# **6.7 Switching Characteristics**

over operating free-air temperature range (unless otherwise noted)

|         | PARAMETER                                 | TEST CONDITIONS                               | MIN | TYP | MAX  | UNIT |  |  |  |  |

|---------|-------------------------------------------|-----------------------------------------------|-----|-----|------|------|--|--|--|--|

| OSCILLA | OSCILLATOR                                |                                               |     |     |      |      |  |  |  |  |

| fosc    | Oscillator frequency range <sup>(1)</sup> |                                               | 35  |     | 1000 | KHz  |  |  |  |  |

|         | Oscillator frequency                      | $R_{RC}$ = 182 k $\Omega$ , $C_{RC}$ = 330 pF | 260 | 300 | 340  |      |  |  |  |  |

(1) Specified by design

# **6.8 Typical Characteristics**

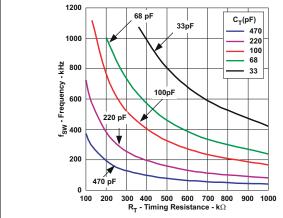

图 6-1. Frequency vs Timing Resistance

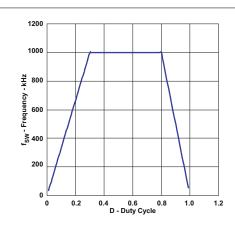

图 6-2. Switching Frequency vs Duty Cycle

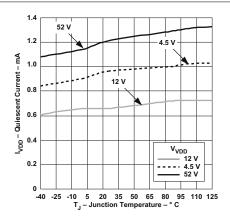

图 6-3. Quiescent Current vs Junction Temperature

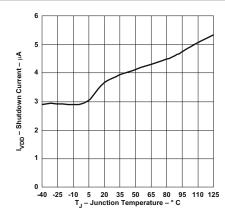

图 6-4. Shutdown Current vs Junction Temperature

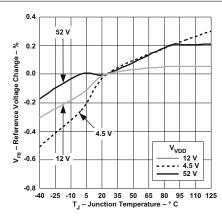

图 6-5. Reference Voltage Change vs Junction Temperature

图 6-6. Reference Voltage Change vs Input Voltage

# 6.8 Typical Characteristics (continued)

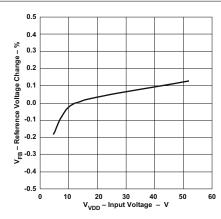

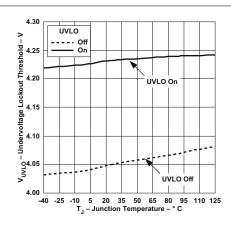

图 6-7. Undervoltage Lockout Threshold vs Junction Temperature

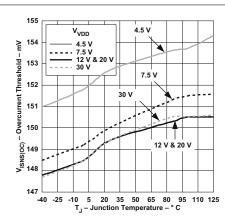

图 6-8. Overcurrent Threshold vs Junction Temperature

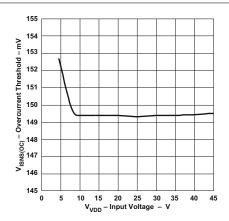

图 6-9. Overcurrent Threshold vs Input Voltage

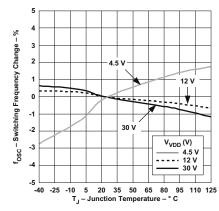

图 6-10. Switching Frequency Change vs Junction Temperature

图 6-11. Oscillator Amplitude vs Junction Temperature

图 6-12. Soft-Start Charge and Discharge Resistance vs Junction Temperature

# **6.8 Typical Characteristics (continued)**

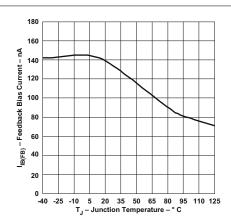

图 6-13. FB Bias Current vs Junction Temperature

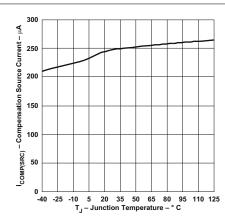

图 6-14. Compensation Source Current vs Junction Temperature

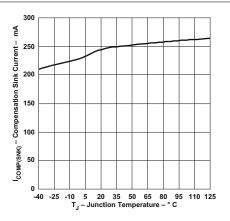

图 6-15. Compensation Sink Current vs Junction Temperature

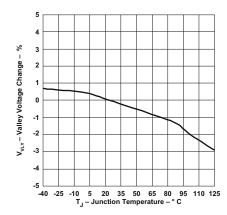

图 6-16. Valley Voltage Change vs Junction Temperature

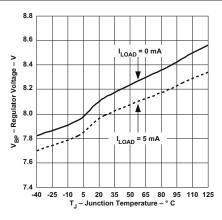

图 6-17. Regulator Voltage vs Junction Temperature

图 6-18. DIS/ EN Turn-On Threshold vs Junction Temperature

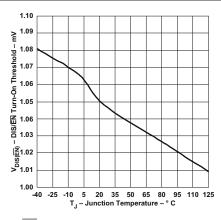

# **6.8 Typical Characteristics (continued)**

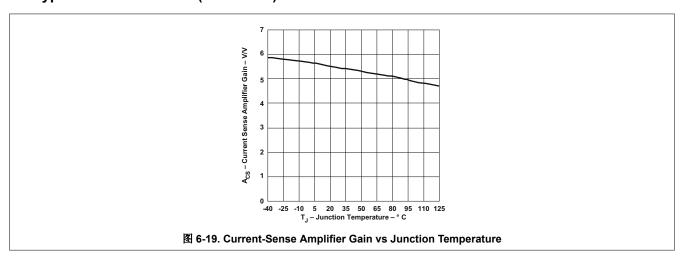

# 7 Detailed Description

# 7.1 Overview

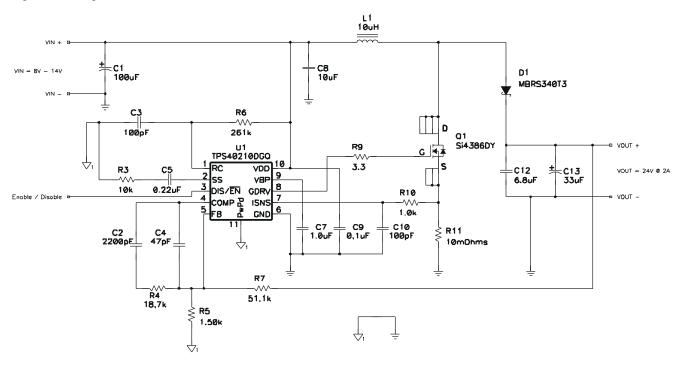

The TPS40210-Q1 and TPS40211-Q1 devices are wide-input voltage non-sync boost controllers. These devices can be used in various topologies such as boost, flyback, SEPIC, and various LED driver applications because of its grounded source N-channel FET. The device also features programmable soft start, overcurrent protection, and programmable oscillator frequency. Current mode control provides improved transient response and simplified loop compensation. The TPS40210-Q1 and TPS40211-Q1 devices differ in the reference voltage to which the error amplifier regulates the FB pin.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

### 7.3.1 Minimum On-Time and Off-Time Considerations

The TPS40210-Q1 device has a minimum off-time of approximately 200 ns and a minimum on-time of 300 ns. These two constraints place limitations on the operating frequency that can be used for a given input-to-output conversion ratio. See 8 6-2 for the maximum frequency that can be used for a given duty cycle.

The duty cycle at which the converter operates is dependent on the mode in which the converter is running. If the converter is running in discontinuous-conduction mode, the duty cycle varies with changes to the load much more than it does when running in continuous-conduction mode.

In continuous-conduction mode, the duty cycle is related primarily to the input and output voltages.

$$\frac{V_{OUT} + V_D}{V_{IN}} = \frac{1}{1 - D} \tag{1}$$

$$D = \left(1 - \left(\frac{V_{IN}}{V_{OUT} + V_{D}}\right)\right)$$

(2)

In discontinuous-conduction mode, the duty cycle is a function of the load, input and output voltages, inductance, and switching frequency.

$$D = \frac{2 \times \left(V_{OUT} + V_{D}\right) \times I_{OUT} \times L \times f_{SW}}{\left(V_{IN}\right)^{2}}$$

(3)

All converters using a diode as the freewheeling or catch component have a load current level at which they transition from discontinuous conduction to continuous conduction. This is the point at which the inductor current falls to zero. At higher load currents, the inductor current does not fall to zero but remains flowing in a positive direction and assumes a trapezoidal wave shape as opposed to a triangular wave shape. This load boundary between discontinuous conduction and continuous conduction can be found for a set of converter parameters as shown in 方程式 4.

$$I_{OUT(crit)} = \frac{\left(V_{OUT} + V_D - V_{IN}\right) \times \left(V_{IN}\right)^2}{2 \times \left(V_{OUT} + V_D\right)^2 \times f_{SW} \times L}$$

(4)

For loads higher than the result of 方程式 4, the duty cycle is given by 方程式 2, and for loads less than the results of 方程式 4, the duty cycle is given 方程式 3. For 方程式 1 through 方程式 4, the variable definitions are as follows:

- V<sub>OUT</sub> is the output voltage of the converter in V.

- V<sub>D</sub> is the forward conduction voltage drop across the rectifier or catch diode in V.

- V<sub>IN</sub> is the input voltage to the converter in V.

- I<sub>OUT</sub> is the output current of the converter in A.

- L is the inductor value in H.

- f<sub>SW</sub> is the switching frequency in Hz.

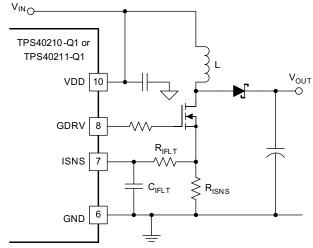

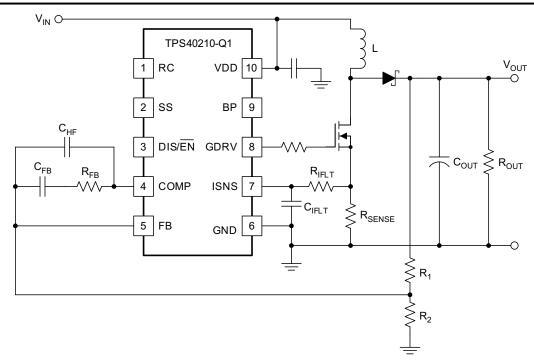

# 7.3.2 Current Sense and Overcurrent

The TPS40210-Q1 and TPS40211-Q1 devices are current-mode controllers and use a resistor in series with the source terminal power FET to sense current for both the current-mode control and overcurrent protection. The device enters a current-limit state if the voltage on the ISNS pin exceeds the current-limit threshold voltage  $V_{\rm ISNS(oc)}$  from the # 6.5. When this happens, the controller discharges the SS capacitor through a relatively high impedance and then attempts to restart. The amount of output current that causes this to happen is dependent on several variables in the converter.

图 7-2. Current Sense Components

The load current overcurrent threshold is set by proper choice of  $R_{ISNS}$ . If the converter is operating in discontinuous mode, the current sense resistor is found in 54 $\pm$ 5.

$$R_{ISNS} = \frac{f_{SW} \times L \times V_{ISNS(oc)}}{\sqrt{2 \times L \times f_{SW} \times I_{OUT(oc)} \times \left(V_{OUT} + V_{D} - V_{IN}\right)}}$$

(5)

If the converter is operating in continuous conduction mode,  $R_{ISNS}$  can be found in 方程式 6.

$$R_{ISNS} = \frac{V_{ISNS}}{\left(\frac{I_{OUT}}{1 - D}\right) + \left(\frac{I_{RIPPLE}}{2}\right)} = \frac{V_{ISNS}}{\left(\frac{I_{OUT}}{(1 - D)}\right) + \left(\frac{D \times V_{IN}}{2 \times f_{SW} \times L}\right)}$$

(6)

#### where

- $R_{ISNS}$  is the value of the current sense resistor in  $\Omega$ .

- $V_{ISNS(oc)}$  is the overcurrent threshold voltage at the ISNS pin (from the #6.5)

- D is the duty cycle (from 方程式 2)

- f<sub>SW</sub> is the switching frequency in Hz

- $V_{\text{IN}}$  is the input voltage to the power stage in V (see text)

- · L is the value of the inductor in H

- I<sub>OUT</sub>(oc) is the desired overcurrent trip point in A

- V<sub>D</sub> is the drop across the diode in

▼ 7-2

The TPS40210-Q1 and TPS40211-Q1 devices have a fixed undervoltage lockout (UVLO) that allows the controller to start at a typical input voltage of 4.25 V. If the input voltage is slowly rising, the converter might have less than its designed nominal input voltage available when it has reached regulation. As a result, this can decrease the apparent current-limit load current value and must be taken into consideration when selecting  $R_{ISNS}$ . The value of  $V_{IN}$  used to calculate  $R_{ISNS}$  must be the value at which the converter finishes start-up. The total converter output current at start-up is the sum of the external load current and the current required to charge the output capacitor(s). See the # 7.3.5 section of this data sheet for information on calculating the required output capacitor charging current.

The topology of the standard boost converter has no method to limit current from the input to the output in the event of a short circuit fault on the output of the converter. If protection from this type of event is desired, it is

necessary to use some secondary protection scheme such as a fuse or rely on the current limit of the upstream power source.

# 7.3.3 Current Sense and Subharmonic Instability

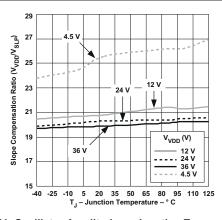

A characteristic of peak current-mode control results in a condition where the current control loop can exhibit instability. This results in alternating long and short pulses from the pulse-width modulator. The voltage loop maintains regulation and does not oscillate, but the output ripple voltage increases. The condition occurs only when the converter is operating in continuous conduction mode, and the duty cycle is 50% or greater. The cause of this condition is described in the *Modeling, Analysis and Compensation of the Current-Mode Converter Application Report*. The remedy for this condition is to apply a compensating ramp from the oscillator to the signal going to the pulse-width modulator. In the TPS40210-Q1 and TPS40211-Q1 devices, the oscillator ramp is applied in a fixed amount to the pulse-width modulator. The slope of the ramp is given in 方程式 7.

$$s_{e} = f_{SW} \times \left(\frac{V_{VDD}}{20}\right) \tag{7}$$

To ensure that the converter does not enter into sub-harmonic instability, the slope of the compensating ramp signal must be at least half of the down slope of the current ramp signal. Because the compensating ramp is fixed in the TPS40210-Q1 and TPS40211-Q1 devices, this places a constraint on the selection of the current sense resistor.

The down slope of the current sense wave form at the pulse-width modulator is described in 方程式 8.

$$m2 = \frac{A_{CS} \times R_{ISNS} \times (V_{OUT} + V_D - V_{IN})}{L}$$

(8)

$$R_{ISNS(max)} = \frac{V_{VDD} \times L \times f_{SW}}{60 \times \left(V_{OUT} + V_D - V_{IN}\right)}$$

(9)

### where

- Se is the slope of the voltage compensating ramp applied to the pulse-width modulator in V/s

- f<sub>SW</sub> is the switching frequency in Hz

- V<sub>DD</sub> is the voltage at the V<sub>DD</sub> pin in V

- · m2 is the down slope of the current sense waveform seen at the pulse-width modulator in V/s

- $R_{ISNS}$  is the value of the current sense resistor in  $\Omega$

- V<sub>OUT</sub> is the converter output voltage V<sub>IN</sub> is the converter power stage input voltage

- V<sub>D</sub> is the drop across the diode in

▼ 7-2

It is possible to increase the voltage compensation ramp slope by connecting the  $V_{DD}$  pin to the output voltage of the converter instead of the input voltage as shown in  $\boxed{8}$  7-2. This can help in situations where the converter design calls for a large ripple current value in relation to the desired output current limit setting.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

### 备注

Connecting the  $V_{DD}$  pin to the output voltage of the converter affects the start-up voltage of the converter since the controller undervoltage lockout (UVLO) circuit monitors the  $V_{DD}$  pin and senses the input voltage less the diode drop before start-up. The effect is to increase the start-up voltage by the value of the diode voltage drop.

If an acceptable R<sub>ISNS</sub> value is not available, the next higher value can be used and the signal from the resistor divided down to an acceptable level by placing another resistor in parallel with C<sub>ISNS</sub>.

### 7.3.4 Current Sense Filtering

In most cases, a small filter placed on the ISNS pin improves performance of the converter. These are the components  $R_{\text{IFLT}}$  and  $C_{\text{IFLT}}$  in 图 7-2. The time constant of this filter should be approximately 10% of the nominal pulse width of the converter. The pulse width can be found using 方程式 10.

$$t_{ON} = \frac{D}{f_{SW}} \tag{10}$$

The suggested time constant is then

$$R_{IFLT} \times C_{IFLT} = 0.1 \times t_{ON}$$

(11)

The range of  $R_{IFLT}$  should be from about 1 k $\Omega$  to 5 k $\Omega$  for best results. Higher values can be used, but this raises the impedance of the ISNS pin connection more than necessary and can lead to noise-pickup issues in some layouts.  $C_{ISNS}$  should be located as close as possible to the ISNS pin as well to provide noise immunity.

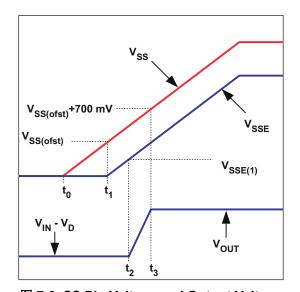

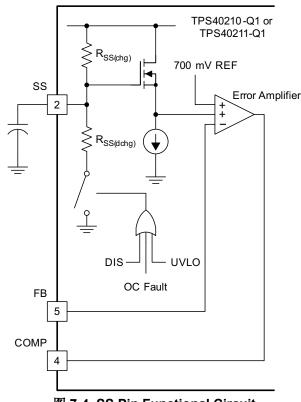

### 7.3.5 Soft Start

The soft-start feature of the TPS40210-Q1 and TPS40211-Q1 devices is a closed-loop soft start, meaning that the output voltage follows a linear ramp that is proportional to the ramp generated at the SS pin. This ramp is generated by an internal resistor connected from the BP pin to the SS pin and an external capacitor connected from the SS pin to GND. The SS pin voltage ( $V_{SS}$ ) is level shifted down by approximately  $V_{SS(ofst)}$  (approximately 1 V) and sent to one of the + inputs (the + input with the lowest voltage dominates) of the error amplifier. When this level-shifted voltage ( $V_{SSE}$ ) starts to rise at time  $t_1$  (see  $\mbox{\ensuremath{\mathbb{K}}}$  7-3), the output voltage that the controller expects rises as well. Since  $V_{SSE}$  starts at near 0 V, the controller attempts to regulate the output voltage from a starting point of zero volts. It cannot do this, due to the converter architecture. The output voltage starts from the input voltage less the drop across the diode ( $V_{IN} - V_D$ ) and rises from there. The point at which the output voltage starts to rise ( $t_2$ ) is when the  $V_{SSE}$  ramp passes the point where it is commanding more output voltage than ( $V_{IN} - V_D$ ). This voltage level is labeled  $V_{SSE(1)}$ . The time required for the output voltage to ramp from a theoretical zero to the final regulated value (from  $t_1$  to  $t_3$ ) is determined by the time it takes for the capacitor connected to the SS pin ( $C_{SS}$ ) to rise through a 700-mV range, beginning at  $V_{SS(ofst)}$  above GND.

图 7-3. SS Pin Voltage and Output Voltage

图 7-4. SS Pin Functional Circuit

The required capacitance for a given soft-start time,  $t_3 - t_1$  in 图 7-3, is calculated in 方程式 12.

$$C_{SS} = \frac{t_{SS}}{R_{SS} \times In \left( \frac{V_{BP} - V_{SS(ofst)}}{V_{BP} - \left(V_{SS(ofst)} + V_{FB}\right)} \right)}$$

(12)

### where

- t<sub>SS</sub> is the soft-start time

- $R_{SS(chq)}$  is the SS charging resistance in  $\Omega$ , typically 500 k $\Omega$

- C<sub>SS</sub> is the value of the capacitor on the SS pin, in F

- V<sub>BP</sub> is the value of the voltage on the BP pin in V

- V<sub>SS(ofst)</sub> is the approximate level shift from the SS pin to the error amplifier (~1 V)

- V<sub>FB</sub> is the error amplifier reference voltage, 700 mV typical

Note that  $t_{SS}$  is the time it takes for the output voltage to rise from 0 V to the final output voltage. Also note the tolerance on  $R_{SS(chg)}$  given in the # 6.5. This contributes to some variability in the output voltage rise time, and margin must be applied to account for it in design.

Also take note of  $V_{BP}$ . Its value varies depending on input conditions. For example, a converter operating from a slowly rising input initializes  $V_{BP}$  at a fairly low value and increases during the entire start-up sequence. If the controller has a voltage above 8 V at the input and the DIS pin is used to stop and then restart the converter,  $V_{BP}$  is approximately 8 V for the entire start-up sequence. The higher the voltage on BP, the shorter the start-up time is and conversely, the lower the voltage on BP, the longer the start-up time is.

www.ti.com.cn

The soft-start time (t<sub>SS</sub>) must be chosen long enough so that the converter can start up without going into an overcurrent state. Since the overcurrent state is triggered by sensing the peak voltage on the ISNS pin, that voltage must be kept below the overcurrent threshold voltage, V<sub>ISNS(oc)</sub>. The voltage on the ISNS pin is a function of the load current of the converter, the rate of rise of the output voltage and the output capacitance, and the current sensing resistor. The total output current that must be supported by the converter is the sum of the charging current required by the output capacitor and any external load that must be supplied during start-up. This current must be less than the I<sub>OUT(oc)</sub> value used in 方程式 5 or 方程式 6 (depending on the operating mode of the converter) to determine the current sense resistor value.

In these equations, the actual input voltage at the time that the controller reaches the final output voltage is the important input voltage to use in the calculations. If the input voltage is slowly rising and is at less than the nominal input voltage when the startup time ends, the output current limit is less than IOUT(oc) at the nominal input voltage. The output capacitor charging current must be reduced (decrease COUT or increase the tSS) or I<sub>OUT(oc)</sub> must be increased and a new value for R<sub>ISNS</sub> calculated.

$$I_{C(chg)} = \left(\frac{C_{OUT} \times V_{OUT}}{t_{SS}}\right)$$

(13)

$$t_{SS} > \left(\frac{C_{OUT} \times V_{OUT}}{(I_{OUT(oc)} - I_{EXT})}\right)$$

(14)

#### where

- $I_{C(chq)}$  is the output capacitor charging current in A

- C<sub>OUT</sub> is the total output capacitance in F

- V<sub>OUT</sub> is the output voltage in V

- t<sub>SS</sub> is the soft-start time from 方程式 12

- I<sub>OUT(oc)</sub> is the desired over current trip point in A

- I<sub>EXT</sub> is any external load current in A

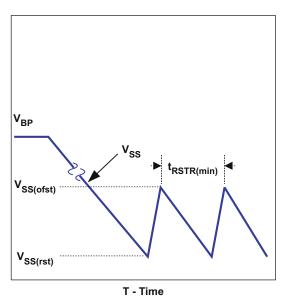

The capacitor on the SS pin ( $C_{SS}$ ) also plays a role in overcurrent functionality. It is used as the timer between restart attempts. The SS pin is connected to GND through a resistor,  $R_{SS(dchg)}$ , when the controller senses an overcurrent condition. Switching stops and nothing else happens until the SS pin discharges to the soft-start reset threshold,  $V_{SS(rst)}$ . At this point, the SS pin capacitor is allowed to charge again through the charging resistor  $R_{SS(chg)}$ , and the controller restarts from that point. The shortest time between restart attempts occurs when the SS pin discharges from  $V_{SS(ofst)}$  (approximately 1 V) to  $V_{SS(rst)}$  (150 mV) and then back to  $V_{SS(ofst)}$  and switching resumes. In actuality, this is a conservative estimate since switching does not resume until the  $V_{SSE}$  ramp rises to a point where it is commanding more output voltage than exists at the output of the controller. This occurs at some SS pin voltage greater than  $V_{SS(ofst)}$  and depends on the voltage that remains on the output overvoltage the converter while switching has been halted. The fastest restart time can be calculated by using  $\hat{\mathcal{T}}$   $\mathcal{T}$  15,  $\hat{\mathcal{T}}$   $\mathcal{T}$  16, and  $\hat{\mathcal{T}}$   $\mathcal{T}$  17.

$$t_{DCHG} = R_{SS(dchg)} \times C_{SS} \times In \left( \frac{V_{SS(ofst)}}{V_{SS(rst)}} \right)$$

(15)

$$t_{CHG} = R_{SS(chg)} \times C_{SS} \times In \left( \frac{\left( V_{BP} - V_{SS(rst)} \right)}{\left( V_{BP} - V_{SS(ofst)} \right)} \right)$$

(16)

$$t_{RSTRT(min)} = t_{CHG} + t_{DCHG}$$

(17)

图 7-5. Soft Start During Overcurrent

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

### 7.3.6 BP Regulator

The TPS40210-Q1 and TPS40211-Q1 devices have an on-board linear regulator that supplies power for the internal circuitry of the controller, including the gate driver. This regulator has a nominal output voltage of 8 V and must be bypassed with a 1-  $\mu$  F capacitor. If the voltage at the V<sub>DD</sub> pin is less than 8 V, the voltage on the BP pin is also less, and the gate drive voltage to the external FET is reduced from the nominal 8 V. This should be considered when choosing a FET for the converter.

Connecting external loads to this regulator can be done, but care must be taken to ensure that the thermal rating of the device is observed, because there is no thermal shutdown feature in this controller. Exceeding the thermal ratings causes out-of-specification behavior and can lead to reduced reliability. The controller dissipates more power when there is an external load on the BP pin and is tested for dropout voltage for up to 5-mA load. When the controller is in the disabled state, the BP pin regulator also shuts off so loads connected there power down as well. When the controller is disabled with the DIS/  $\overline{\text{EN}}$  pin, this regulator is turned off.

The total power dissipation in the controller can be calculated as follows. The total power is the sum of  $P_Q$ ,  $P_G$ , and  $P_F$ .

$$P_{Q} = V_{VDD} \times I_{VDD(en)}$$

(18)

$$P_{G} = V_{VDD} \times Q_{g} \times f_{SW}$$

(19)

$$P_{E} = V_{VDD} \times I_{EXT}$$

(20)

#### where

- P<sub>O</sub> is the quiescent power of the device in W

- V<sub>DD</sub> is the V<sub>DD</sub> pin voltage in V

- I<sub>DD(en)</sub> is the quiescent current of the controller when enabled but not switching in A

- P<sub>G</sub> is the power dissipated by driving the gate of the FET in W

- $Q_g$  is the total gate charge of the FET at the voltage on the BP pin in C

- f<sub>SW</sub> is the switching frequency in Hz

- P<sub>E</sub> is the dissipation caused be external loading of the BP pin in W

- I<sub>FXT</sub> is the external load current in A

#### 7.3.7 Shutdown (DIS/ EN Pin)

The DIS/ $\overline{\text{EN}}$  pin is an active-high shutdown command for the controller. Pulling this pin above 1.2 V causes the controller to completely shut down and enter a low current consumption state. In this state, the regulator connected to the BP pin is turned off. There is an internal 1.1-M $\Omega$  pulldown resistor connected to this pin that keeps the pin at GND level when left floating. If this function is not used in an application, it is best to connect this pin to GND

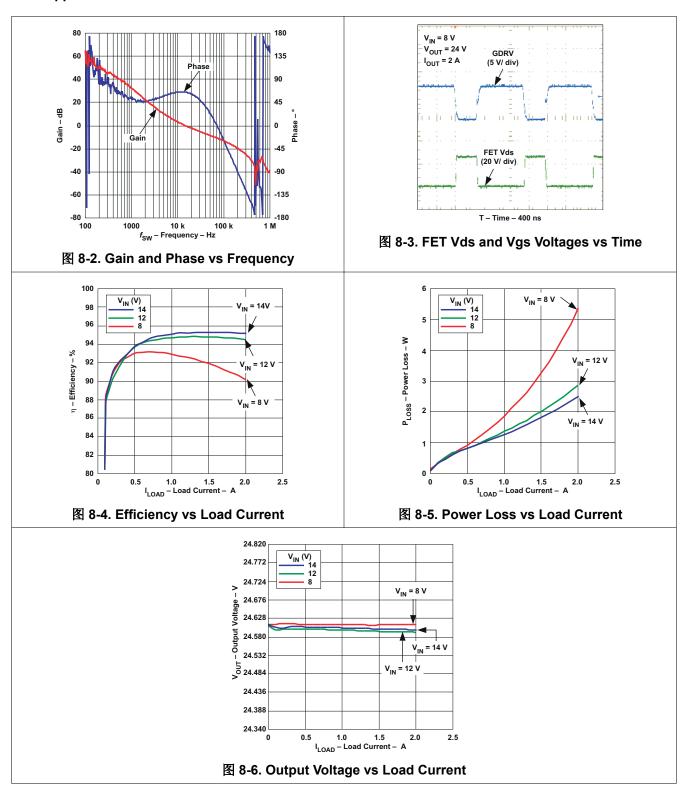

# 7.3.8 Control Loop Considerations

There are two methods to design a suitable control loop for the TPS4021x device. The first (and preferred, if equipment is available) is to use a frequency-response analyzer to measure the open-loop modulator and power stage gain and to then design compensation to fit that. The usage of these tools for this purpose is well-documented with the literature that accompanies the tool and is not discussed here.

The second option is to make an initial guess at compensation, and then evaluate the transient response of the system to see if the compensation is acceptable to the application or not. For most systems, an adequate response can be obtained by simply placing a series resistor and capacitor ( $R_{FB}$  and  $C_{FB}$ ) from the COMP pin to the FB pin as shown in  $\boxed{8}$  7-6.

图 7-6. Basic Compensation Network

The natural phase characteristics of most capacitors used for boost outputs combined with the current mode control provide adequate phase margin when using this type of compensation. To determine an initial starting point for the compensation, the desired crossover frequency must be considered when estimating the control to output gain. The model used is a current source into the output capacitor and load.

When using these equations, the loop bandwidth should be no more than 20% of the switching frequency, f<sub>SW</sub>. A more reasonable loop bandwidth would be 10% of the switching frequency. Be sure to evaluate the transient response of the converter over the expected load range to ensure acceptable operation.

$$|K_{CO}| = g_m \times |Z_{OUT}(f_{CO})| = 19.1 \text{ S} \times 0.146 \Omega = 2.80$$

(21)

$$g_{m} = \frac{0.13 \times \sqrt{L \times \frac{f_{SW}}{R_{OUT}}}}{\left(R_{ISNS}\right)^{2} \times \left(120 \times R_{ISNS} + L \times f_{SW}\right)} = \frac{0.13 \times \sqrt{10 \,\mu\text{H} \times \frac{600 \,k\text{Hz}}{240 \,\Omega}}}{\left(12 \,m\Omega\right)^{2} \times \left(120 \times 12 \,m\Omega + 10 \,\mu\text{H} \times 600 \,k\text{Hz}\right)} = 19.1 \,S \tag{22}$$

$$\left|Z_{OUT}\right| = R_{OUT} \times \sqrt{\frac{\left(1 + \left(2\pi \times f_{L} \times R_{ESR} \times C_{OUT}\right)^{2}\right)}{1 + \left(\left(R_{OUT}\right)^{2} + 2 \times R_{OUT} \times R_{ESR} + \left(R_{ESR}\right)^{2}\right) \times \left(2\pi \times f_{L} \times C_{OUT}\right)^{2}}}$$

(23)

# where

- K<sub>CO</sub> is the control to output gain of the converter, in V/V

- g<sub>M</sub> is the transconductance of the power stage and modulator, in S

- R<sub>OUT</sub> is the output load equivalent resistance, in Ω

- $Z_{OUT}$  is the output impedance, including the output capacitor, in  $\Omega$

- $\mbox{R}_{\mbox{\footnotesize{ISNS}}}$  is the value of the current sense resistor, in  $\Omega$

- L is the value of the inductor, in H

#### www.ti.com.cn

- C<sub>OUT</sub> is the value of the output capacitance, in μF

- $\mbox{R}_{\mbox{\footnotesize ESR}}$  is the equivalent series resistance of  $\mbox{C}_{\mbox{\footnotesize OUT}},$  in  $\Omega$

- f SW is the switching frequency, in Hz

- $f_{\perp}$  is the desired crossover frequency for the control loop, in Hz

These equations assume that the operation is discontinuous and that the load is purely resistive. The gain in continuous conduction can be found by evaluating 方程式 22 at the resistance that gives the critical conduction current for the converter. Loads that are more like current sources give slightly higher gains than predicted here. To find the gain of the compensation network required for a control loop of bandwidth  $f_L$ , take the reciprocal of 方程式 21.

$$K_{COMP} = \frac{1}{|K_{CO}|} = \frac{1}{2.80} = 0.356$$

(24)

The GBWP of the error amplifier is only specified to be at least 1.5 MHz. If  $K_{COMP}$  multiplied by the  $f_L$  is greater than 750 kHz, reduce the desired loop crossover frequency until this condition is satisfied. This ensures that the high-frequency pole from the error amplifier response with the compensation network in place does not cause excessive phase lag at the  $f_L$  and decrease phase margin in the loop.

The R-C network connected from COMP to FB places a zero in the compensation response. That zero should be approximately  $1/10^{th}$  of the desired crossover frequency,  $f_L$ . With that being the case,  $R_{FB}$  and  $C_{FB}$  can be found from 方程式 25 and 方程式 26.

$$R_{FB} = \frac{R1}{|K_{CO}|} = R1 \times K_{COMP}$$

(25)

$$C_{FB} = \frac{10}{2\pi \times f_L \times R_{FB}} \tag{26}$$

#### where

- R1 is in f<sub>1</sub> is the loop crossover frequency desired, in Hz

- $R_{FB}$  is the feedback resistor in  $C_{FB}$  is the feedback capacitance in  $\mu$  F

Though not strictly necessary, it is recommended that a capacitor be added between COMP and FB to provide high-frequency noise attenuation in the control loop circuit. This capacitor introduces another pole in the compensation response. The allowable location of that pole frequency determines the capacitor value. As a starting point, the pole frequency should be  $10 \times f_L$ . The value of  $C_{HF}$  can be found from  $5 \times f_L$ ?

$$C_{HF} = \frac{1}{20\pi \times f_L \times R_{FB}} \tag{27}$$

$$C_{HF} = \frac{1}{2\pi \times 1.5 \times (10)^6 \times R_{FB}}$$

(28)

#### where

- $C_{HF}$  is the high-frequency roll-off capacitor value in  $\mu$  F

- $R_{FB}$  is the mid-band gain-setting resistor value in  $\Omega$

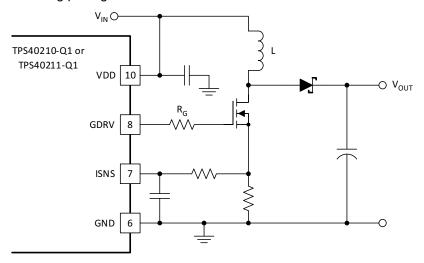

#### 7.3.9 Gate Drive Circuit

Some applications benefit from the addition of a resistor connected between the GDRV pin and the gate of the switching MOSFET. In applications that have particularly stringent load regulation (under 0.75%) requirements and operate from input voltages above 5 V, or are sensitive to pulse jitter in the discontinuous conduction region, this resistor is recommended. The recommended starting point for the value of this resistor can be calculated from 方程式 29.

$$R_{G} = \frac{105}{Q_{G}} \tag{29}$$

#### where

- Q<sub>G</sub> is the MOSFET total gate charge at 8-V V<sub>GS</sub> in nC

- $R_G$  is the suggested starting point gate resistance in  $\Omega$

图 7-7. Gate Drive Resistor

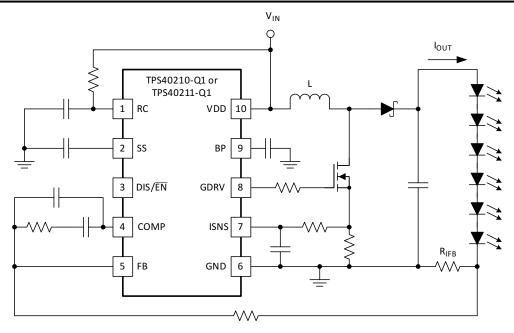

### 7.3.10 TPS40211-Q1

The only difference between the TPS40210-Q1 and the TPS40211-Q1 devices is the reference voltage that the error amplifier uses to regulate the output voltage. The TPS40211-Q1 device uses a 260-mV reference and is intended for applications where the output is actually a current instead of a regulated voltage. A typical example of an application of this type is an LED driver. 8 7-8 shows an example schematic.

An example of an LED driver design using the TPS40211-Q1 device with detailed analysis is available in the TPS40211 - SEPIC Design for MR-16 LED Application Report.

图 7-8. Typical LED Drive Schematic

The current in the LED string is set by the choice of the resistor R<sub>ISNS</sub> as shown in 方程式 30.

$$R_{IFB} = \frac{V_{FB}}{I_{OUT}} \tag{30}$$

#### where

- R<sub>IFB</sub> is the value of the current sense resistor for the LED string in  $\,\Omega$

- V<sub>FB</sub> is the reference voltage for the TPS40211-Q1 device in volts (0.26 V typ)

- · I<sub>OUT</sub> is the desired dc current in the LED string in amperes

### 7.4 Device Functional Modes

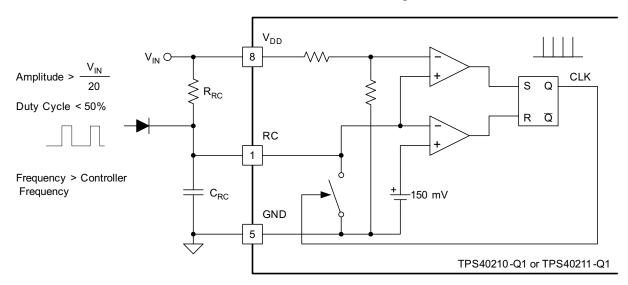

### 7.4.1 Setting the Oscillator Frequency

The oscillator frequency is determined by a resistor and capacitor connected to the RC pin of the TPS40210-Q1 device. The capacitor is charged to a level of approximately  $V_{DD}$  / 20 by current flowing through the resistor and is then discharged by a transistor internal to the TPS40210-Q1 device. The required resistor for a given oscillator frequency is found from either  $\boxtimes$  6-1 or 31.

$$R_{T} = \frac{1}{5.8 \times 10^{-8} \times f_{SW} \times C_{T} + 8 \times 10^{-10} \times f_{SW}^{2} + 1.4 \times 10^{-7} \times f_{SW} - 1.5 \times 10^{-4} + 1.7 \times 10^{-6} \times C_{T} - 4 \times 10^{-9} \times C_{T}^{2}}$$

(31)

#### where

- $R_T$  is the timing resistance in  $k\Omega$

- f<sub>SW</sub> is the switching frequency in kHz

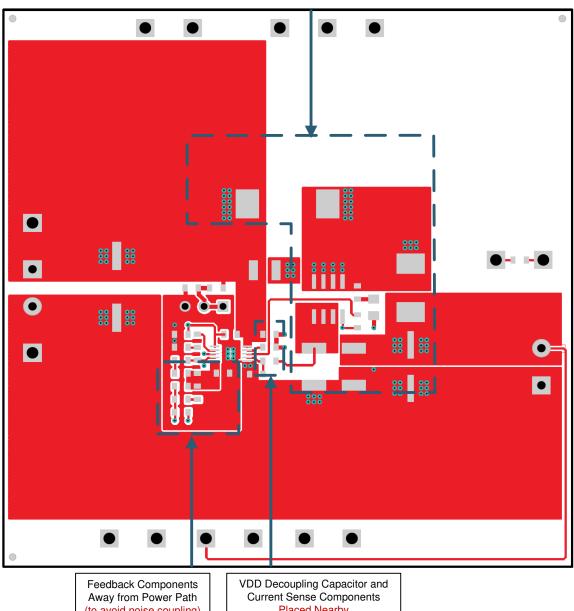

- C<sub>T</sub> is the timing capacitance in pF