# 3-W 单声道D类音频放大器，此放大器具有智能增益 SmartGain™ 自动增益控制(AGC)/动态范围压缩(DRC)

查询样品: [TPA2029D1](#)

## 特性

- 无滤波器D类架构

- **5 V** 和 **4 Ω** 时, 输出功率 **3 W** (**10%** 总谐波失真+D)

- **3.6 V** 和 **8 Ω** 时, 输出功率 **880 mW** (**10%** 总谐波失真+D)

- 电源范围: **2.5 V** 至 **5.5 V**

- 3 个可选 **AGC** 功能

- 低电源电流: **1.8 mA**

- 低关断电流 **0.2 μA**

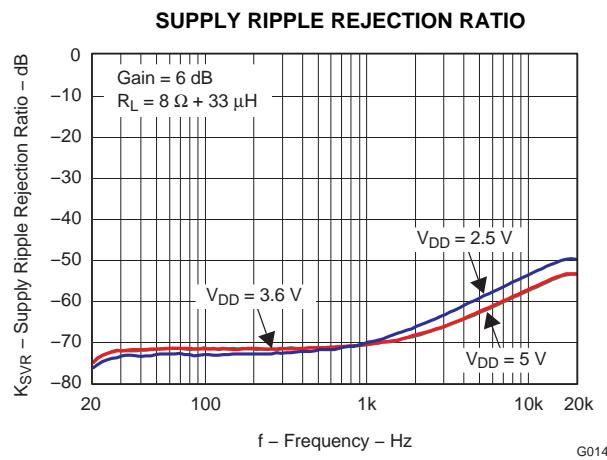

- 高电源抑制比 (PSRR): **80 dB**

- 快速启动时间: **5 ms**

- **AGC**启用/禁用功能

- 限制器启用/禁用功能

- 短路和热保护

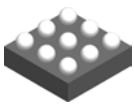

- 节省空间的

- **1.63 mm × 1.63 mm** 晶圆级芯片封装 (WCSP) (YZF)

## 应用范围

- 无线或蜂窝手机及 **PDA**

- 便携式导航设备

- 便携式 **DVD** 播放器

- 笔记本电脑

- 便携式收音机

- 便携式游戏机

- 教育玩具

- **USB** 扬声器

## 说明

TPA2029D1 是一款单声道, 无滤波器D类音频功率放大器, 此放大器具有动态范围压缩 (DRC) 和自动增益控制 (AGC)。它采用 1.63 mm x 1.63 mm WCSP 封装。

TPA2029D1 的 DRC/AGC 功能可被打开和关闭。

DRC/AGC 功能被配置为自动防止音频信号失真并且提高在正常情况下无法听见的静默信息的传输能力。

DRC/AGC 功能还可被配置为保护扬声器在高功率水平下不受损害并且压缩音乐的动态范围以适合扬声器的动态范围。TPA2029D1 能够在 5 V 时驱动 3 W 4Ω 负载或者在 3.6 V 时驱动 880 mW 8Ω 负载。此器件特有一个使能引脚并提供过热和短路保护。

除了这些特性之外, 一个快速启动时间和小封装尺寸使得 TPA2029D1 成为笔记本个人电脑, PDA 和其它便携式应用的理想选择。

TPA2029D1 采用不同的默认 AGC/DRC 设置以满足多样的系统需求。要获得更多细节, 请参见 [Table 2](#)。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

智能增益 SmartGain 是 trademark of Texas Instruments.

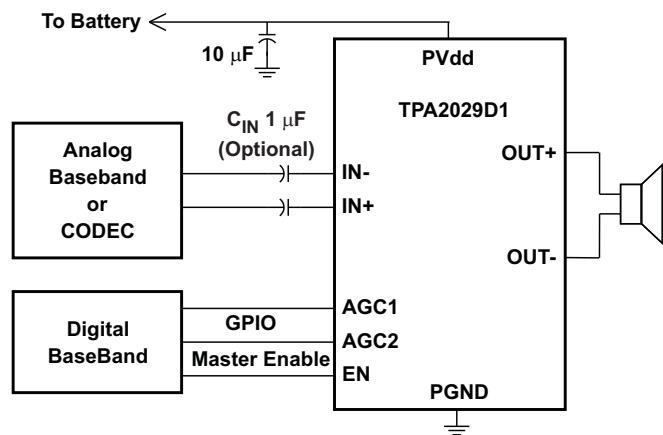

## 简化的应用图

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

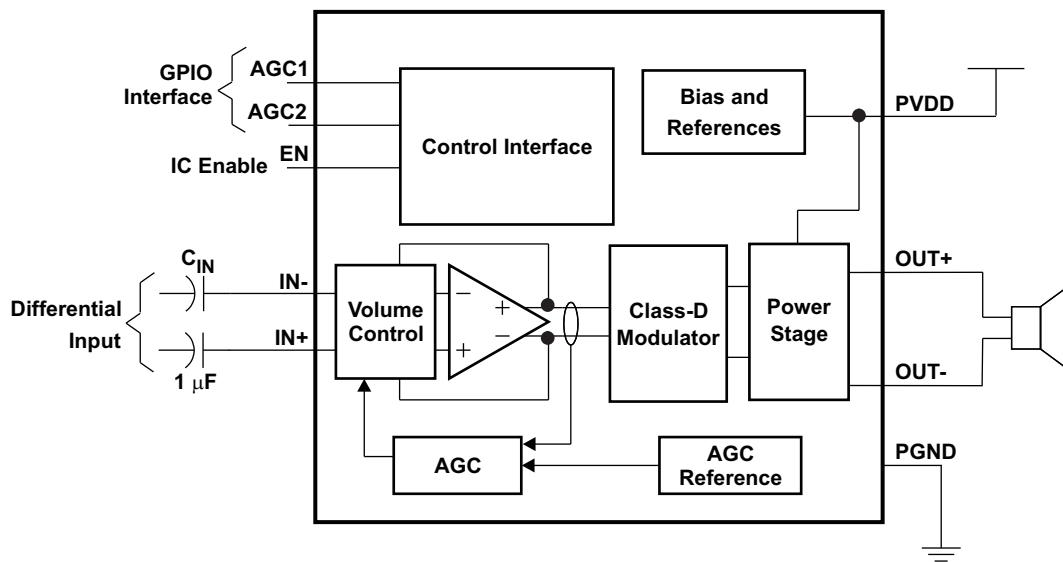

### FUNCTIONAL BLOCK DIAGRAM

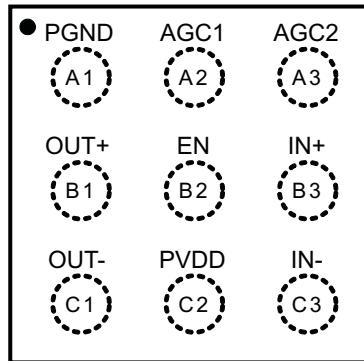

**DEVICE PINOUT**

**WCSP (YZF) PACKAGE**

**(TOP VIEW)**

## PIN FUNCTIONS

| PIN  |      | I/O/P | DESCRIPTION                   |

|------|------|-------|-------------------------------|

| NAME | WCSP |       |                               |

| IN+  | B3   | I     | Positive audio input          |

| IN–  | C3   | I     | Negative audio input          |

| EN   | B2   | I     | Enable terminal (active high) |

| AGC2 | A3   | I     | AGC select function pin 2     |

| AGC1 | A2   | I     | AGC select function pin 1     |

| OUT+ | B1   | O     | Positive differential output  |

| OUT– | C1   | O     | Negative differential output  |

| PVDD | C2   | P     | Power supply                  |

| PGND | A1   | P     | Power ground                  |

ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted).

|                                    |                                                 |                            | VALUE / UNIT                  |

|------------------------------------|-------------------------------------------------|----------------------------|-------------------------------|

| $V_{DD}$                           | Supply voltage                                  | PVDD                       | –0.3 V to 6 V                 |

|                                    | Input voltage                                   | EN, INR+, INR–, INL+, INL– | –0.3 V to $V_{DD}+0.3$ V      |

|                                    |                                                 | AGC1, AGC2                 | –0.3 V to 6 V                 |

| Continuous total power dissipation |                                                 |                            | See Dissipation Ratings Table |

| $T_A$                              | Operating free-air temperature range            |                            | –40°C to 85°C                 |

| $T_J$                              | Operating junction temperature range            |                            | –40°C to 150°C                |

| $T_{stg}$                          | Storage temperature range                       |                            | –65°C to 150°C                |

| ESD                                | Electro-Static Discharge<br>Tolerance, all pins | Human Body Model (HBM)     | 2 KV                          |

|                                    |                                                 | Charged Device Model (CDM) | 500 V                         |

| $R_{LOAD}$                         | Minimum load resistance                         |                            | 3.6 Ω                         |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

DISSIPATION RATINGS TABLE<sup>(1)</sup>

| PACKAGE     | $T_A \leq 25^\circ\text{C}$ | DERATING FACTOR | $T_A = 70^\circ\text{C}$ | $T_A = 85^\circ\text{C}$ |

|-------------|-----------------------------|-----------------|--------------------------|--------------------------|

| 9-ball WCSP | 1.19 W                      | 9.52 mW/°C      | 0.76 W                   | 0.62 W                   |

(1) Dissipation ratings are for a 2-side, 2-plane PCB.

**AVAILABLE OPTIONS<sup>(1)</sup>**

| <b>T<sub>A</sub></b> | <b>PACKAGED DEVICES<sup>(2)</sup></b> | <b>PART NUMBER</b> | <b>SYMBOL</b> |

|----------------------|---------------------------------------|--------------------|---------------|

| –40°C to 85°C        | 9-pin, 1.63 mm × 1.63 mm WCSP         | TPA2029D1YZFR      | QWI           |

|                      |                                       | TPA2029D1YZFT      | QWI           |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at [www.ti.com](http://www.ti.com)

(2) The YZF packages are only available taped and reeled. The suffix R indicates a reel of 3000; the suffix T indicates a reel of 250.

**RECOMMENDED OPERATING CONDITIONS**

|                 |                                | <b>MIN</b>     | <b>MAX</b> | <b>UNIT</b> |

|-----------------|--------------------------------|----------------|------------|-------------|

| V <sub>DD</sub> | Supply voltage                 | PVDD           | 2.5        | 5.5         |

| V <sub>IH</sub> | High-level input voltage       | EN, AGC1, AGC2 | 1.3        | V           |

| V <sub>IL</sub> | Low-level input voltage        | EN, AGC1, AGC2 | 0.6        | V           |

| T <sub>A</sub>  | Operating free-air temperature | –40            | 85         | °C          |

**ELECTRICAL CHARACTERISTICS**

at T<sub>A</sub> = 25°C, V<sub>DD</sub> = 3.6 V, EN = 1.3 V, and R<sub>L</sub> = 8 Ω + 33 μH (unless otherwise noted).

| <b>PARAMETER</b>                     |                                   | <b>TEST CONDITIONS</b>                                                                                                     | <b>MIN</b> | <b>TYP</b> | <b>MAX</b> | <b>UNIT</b> |

|--------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|-------------|

| V <sub>DD</sub> Supply voltage range |                                   |                                                                                                                            | 2.5        | 3.6        | 5.5        | V           |

| I <sub>SDZ</sub>                     | Shutdown quiescent current        | EN = 0.35 V, V <sub>DD</sub> = 2.5 V                                                                                       | 0.1        | 1          |            | μA          |

|                                      |                                   | EN = 0.35 V, V <sub>DD</sub> = 3.6 V                                                                                       | 0.2        | 1          |            |             |

|                                      |                                   | EN = 0.35 V, V <sub>DD</sub> = 5.5 V                                                                                       | 0.3        | 1          |            |             |

| I <sub>DD</sub>                      | Supply current                    | V <sub>DD</sub> = 2.5 V                                                                                                    | 1.6        | 4.5        |            | mA          |

|                                      |                                   | V <sub>DD</sub> = 3.6 V                                                                                                    | 1.8        | 4.7        |            |             |

|                                      |                                   | V <sub>DD</sub> = 5.5 V                                                                                                    | 2.1        | 5.5        |            |             |

| f <sub>SW</sub>                      | Class D Switching Frequency       |                                                                                                                            | 275        | 300        | 325        | kHz         |

| I <sub>IH</sub>                      | High-level input current          | V <sub>DD</sub> = 5.5 V, EN = 5.8 V                                                                                        |            |            | 1          | μA          |

| I <sub>IL</sub>                      | Low-level input current           | V <sub>DD</sub> = 5.5 V, EN = –0.3 V                                                                                       | –1         |            |            | μA          |

| t <sub>START</sub>                   | Start-up time                     | 2.5 V ≤ V <sub>DD</sub> ≤ 5.5 V no pop, C <sub>IN</sub> ≤ 1 μF                                                             |            | 5          |            | ms          |

| POR                                  | Power on reset ON threshold       |                                                                                                                            | 2          | 2.3        |            | V           |

|                                      | Power on reset hysteresis         |                                                                                                                            | 0.2        |            |            | V           |

| CMRR                                 | Input common mode rejection       | R <sub>L</sub> = 8 Ω, V <sub>icm</sub> = 0.5 V and V <sub>icm</sub> = V <sub>DD</sub> – 0.8 V, differential inputs shorted | –75        |            |            | dB          |

| V <sub>oo</sub>                      | Output offset voltage             | V <sub>DD</sub> = 3.6 V, A <sub>V</sub> = 6 dB, R <sub>L</sub> = 8 Ω, inputs ac grounded                                   | 1.5        | 10         |            | mV          |

| Z <sub>O</sub>                       | Output Impedance in shutdown mode | EN = 0.35 V                                                                                                                |            | 2          |            | kΩ          |

| Gain accuracy                        |                                   | Compression and limiter disabled, Gain = 0 to 30 dB                                                                        | –0.5       | 0.5        |            | dB          |

| PSRR                                 | Power supply rejection ratio      | V <sub>DD</sub> = 2.5 V to 4.7 V                                                                                           | –80        |            |            | dB          |

## OPERATING CHARACTERISTICS

at  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 3.6\text{V}$ ,  $EN = 1.3\text{V}$ ,  $R_L = 8\Omega$ ,  $+33\mu\text{H}$ , and  $A_V = 6\text{dB}$  (unless otherwise noted).

| PARAMETER                                     | TEST CONDITIONS                                                                        | MIN | TYP   | MAX | UNIT          |

|-----------------------------------------------|----------------------------------------------------------------------------------------|-----|-------|-----|---------------|

| $k_{SVR}$ power-supply ripple rejection ratio | $V_{DD} = 3.6\text{Vdc}$ with ac of $200\text{mV}_{PP}$ at $217\text{Hz}$              |     | -70   |     | dB            |

| THD+N Total harmonic distortion + noise       | $f_{aud\_in} = 1\text{kHz}$ ; $P_O = 550\text{mW}$ ; $V_{DD} = 3.6\text{V}$            |     | 0.1%  |     |               |

|                                               | $f_{aud\_in} = 1\text{kHz}$ ; $P_O = 1.25\text{W}$ ; $V_{DD} = 5\text{V}$              |     | 0.1%  |     |               |

|                                               | $f_{aud\_in} = 1\text{kHz}$ ; $P_O = 710\text{mW}$ ; $V_{DD} = 3.6\text{V}$            |     | 1%    |     |               |

|                                               | $f_{aud\_in} = 1\text{kHz}$ ; $P_O = 1.4\text{W}$ ; $V_{DD} = 5\text{V}$               |     | 1%    |     |               |

| $N_r$ Output integrated noise                 | $Av = 6\text{dB}$                                                                      |     | 42    |     | $\mu\text{V}$ |

|                                               | $Av = 6\text{dB}$ floor, A-weighted                                                    |     | 30    |     | $\mu\text{V}$ |

| $f$ Frequency response                        | $Av = 6\text{dB}$                                                                      | 20  | 20000 |     | Hz            |

| $P_{O(max)}$ Maximum output power             | $\text{THD+N} = 10\%$ , $V_{DD} = 5\text{V}$ , $R_L = 8\Omega$                         |     | 1.72  |     | W             |

|                                               | $\text{THD+N} = 10\%$ , $V_{DD} = 3.6\text{V}$ , $R_L = 8\Omega$                       |     | 880   |     | mW            |

|                                               | $\text{THD+N} = 1\%$ , $V_{DD} = 5\text{V}$ , $R_L = 8\Omega$                          |     | 1.4   |     | W             |

|                                               | $\text{THD+N} = 1\%$ , $V_{DD} = 3.6\text{V}$ , $R_L = 8\Omega$                        |     | 710   |     | mW            |

|                                               | $\text{THD+N} = 10\%$ , $V_{DD} = 5\text{V}$ , $R_L = 4\Omega$                         |     | 3     |     | W             |

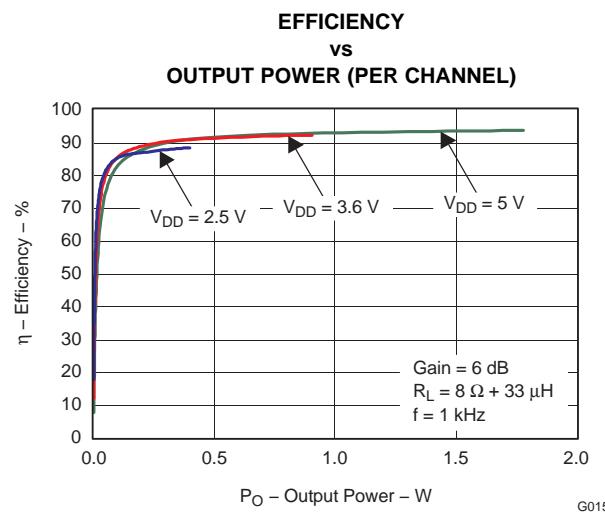

| $\eta$ Efficiency                             | $\text{THD+N} = 1\%$ , $V_{DD} = 3.6\text{V}$ , $R_L = 8\Omega$ , $P_O = 0.71\text{W}$ |     | 91%   |     |               |

|                                               | $\text{THD+N} = 1\%$ , $V_{DD} = 5\text{V}$ , $R_L = 8\Omega$ , $P_O = 1.4\text{W}$    |     | 93%   |     |               |

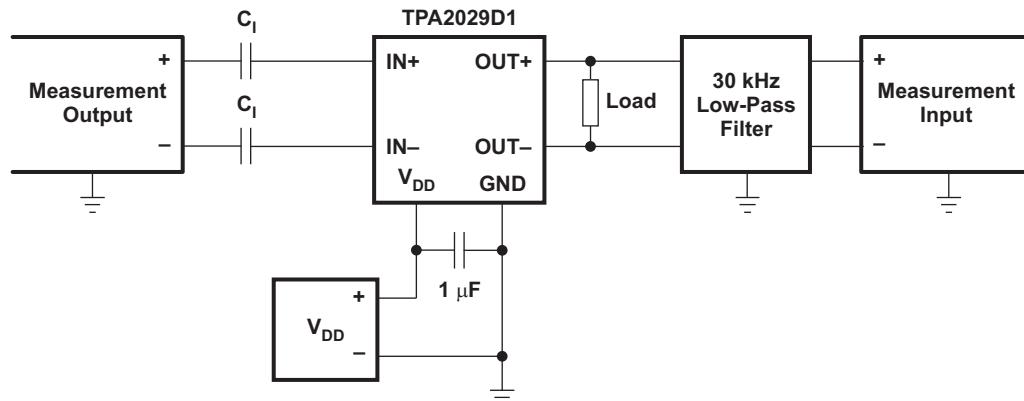

Figure 1. TEST SET-UP FOR GRAPHS

- (1) All measurements were taken with a  $1\mu\text{F}$   $C_L$  (unless otherwise noted.)

- (2) A  $33\mu\text{H}$  inductor was placed in series with the load resistor to emulate a small speaker for efficiency measurements.

- (3) The 30-kHz low-pass filter is required, even if the analyzer has an internal low-pass filter. An RC low-pass filter ( $1\text{k}\Omega$   $4.7\text{nF}$ ) is used on each output for the data sheet graphs.

## TYPICAL CHARACTERISTICS

with  $C_{(DECOPPLE)} = 1 \mu F$ ,  $C_I = 1 \mu F$ .

All THD + N graphs are taken with outputs out of phase (unless otherwise noted).

All data is taken on left channel.

### Table of Graphs

|                                   |                               | <b>FIGURE</b>         |

|-----------------------------------|-------------------------------|-----------------------|

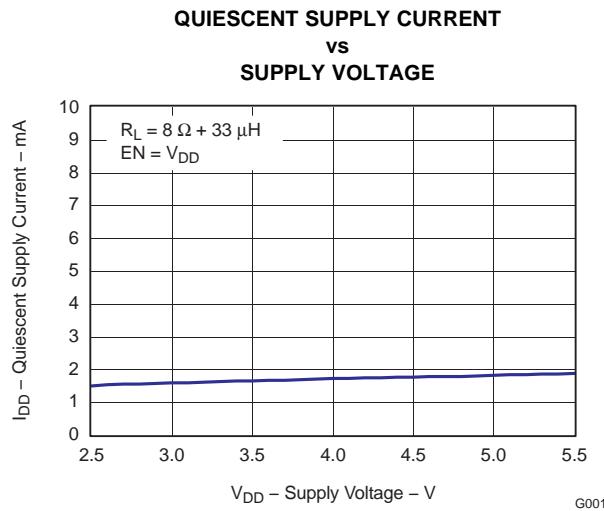

| Quiescent supply current          | vs Supply voltage             | Figure 2              |

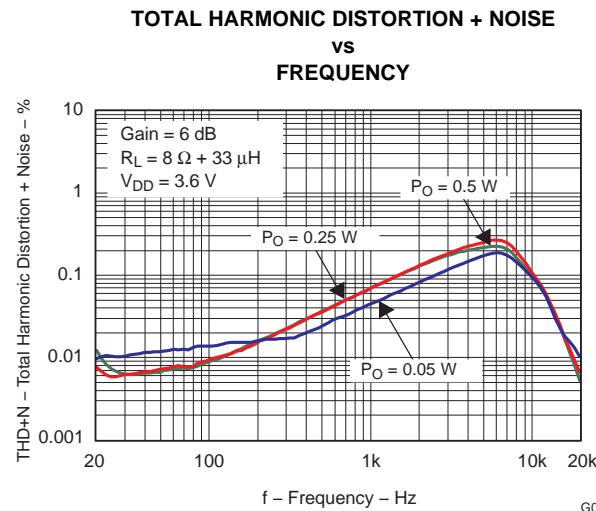

| Total harmonic distortion + noise | vs Frequency                  | Figure 3              |

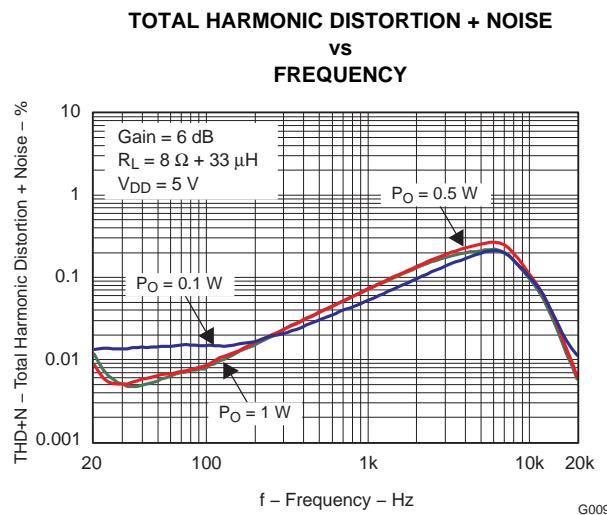

| Total harmonic distortion + noise | vs Frequency                  | Figure 4              |

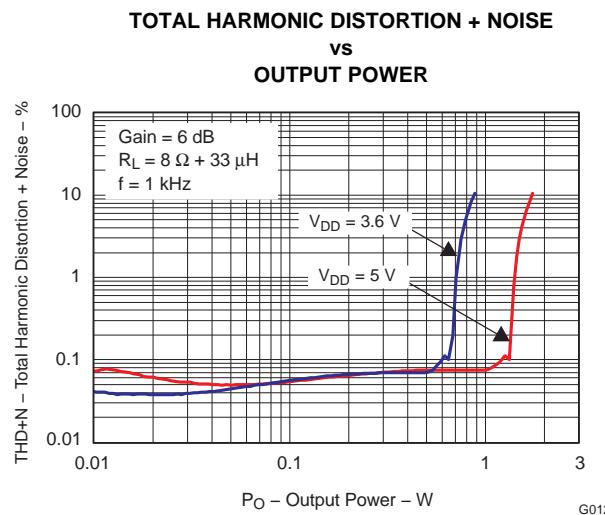

| Total harmonic distortion + noise | vs Output power               | Figure 5              |

| Supply ripple rejection ratio     | vs Frequency                  | Figure 6              |

| Efficiency                        | vs Output power (per channel) | Figure 7              |

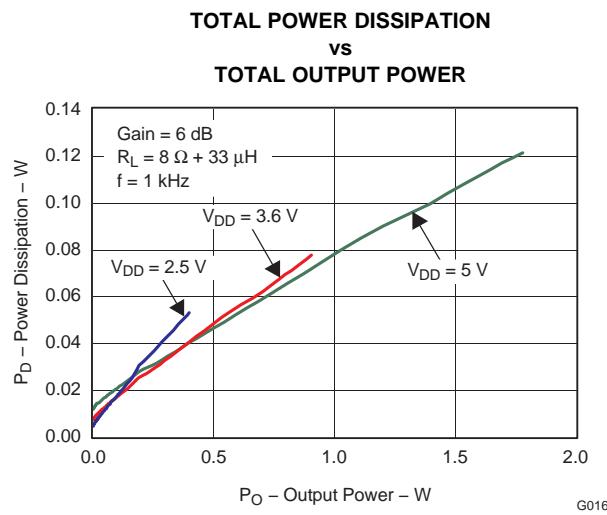

| Total power dissipation           | vs Total output power         | Figure 8              |

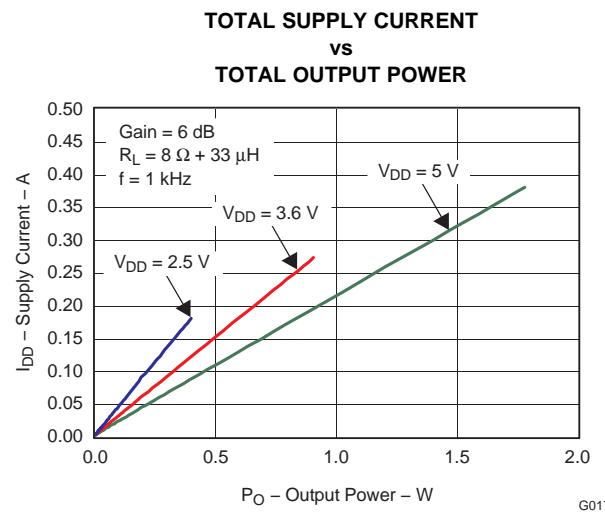

| Total supply current              | vs Total output power         | Figure 9              |

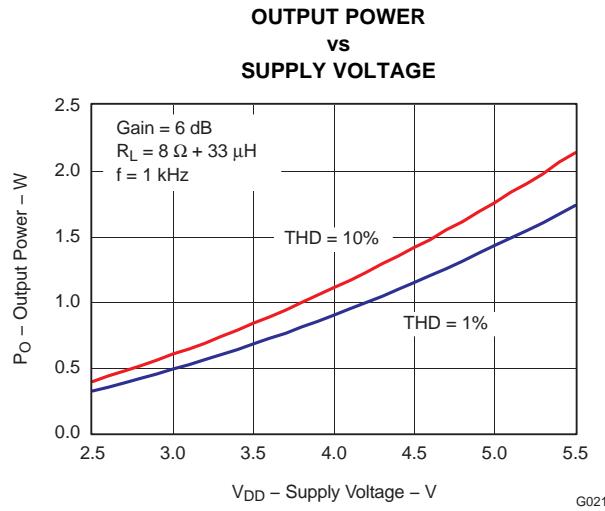

| Output power                      | vs Supply voltage             | Figure 10 , Figure 11 |

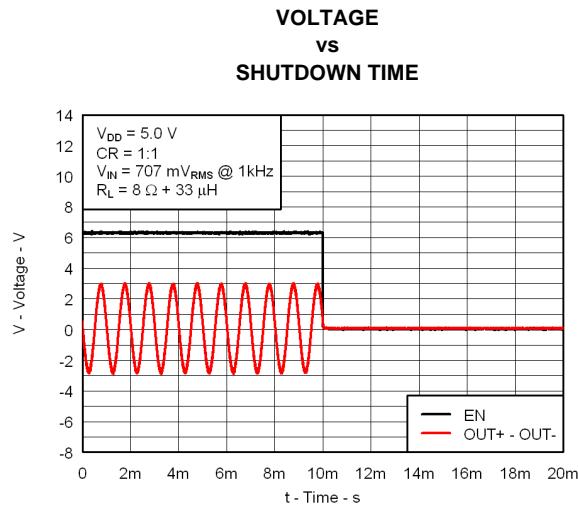

| Shutdown time                     |                               | Figure 12             |

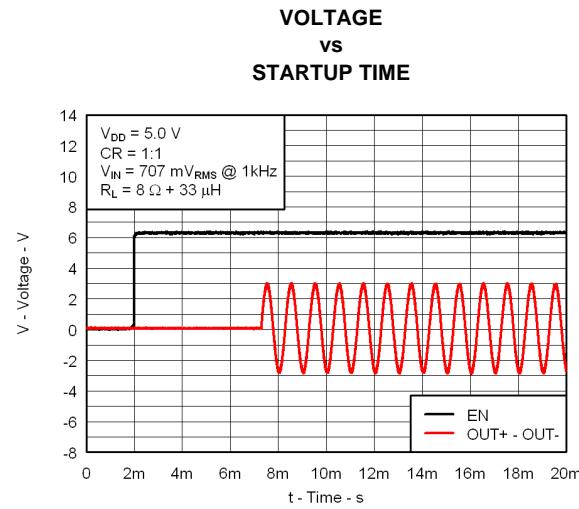

| Startup time                      |                               | Figure 13             |

**Figure 2.**

**Figure 3.**

Figure 4.

Figure 5.

Figure 6.

Figure 7.

Figure 8.

Figure 9.

**Figure 10.**

**Figure 11.**

**Figure 12.**

**Figure 13.**

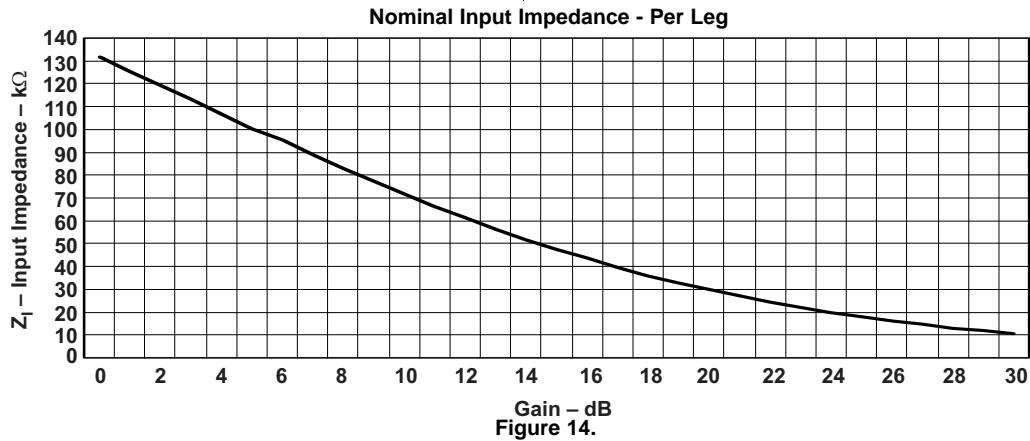

**Figure 14.**

## APPLICATION INFORMATION

### AUTOMATIC GAIN CONTROL

The Automatic Gain Control (AGC) feature provides continuous automatic gain adjustment to the amplifier through an internal PGA. This feature enhances the perceived audio loudness and at the same time prevents speaker damage from occurring (Limiter function).

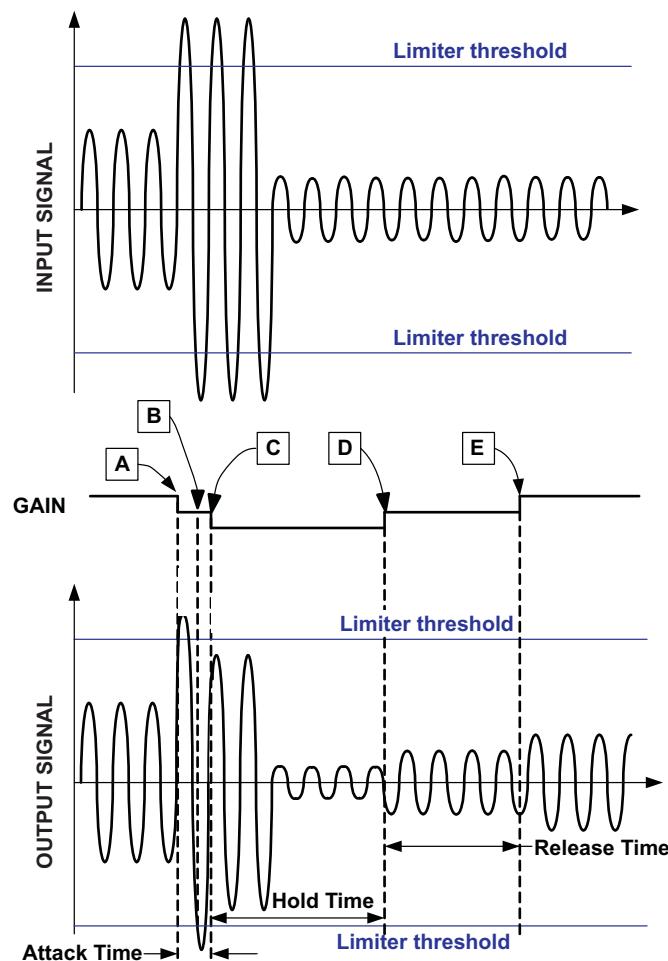

The AGC works by detecting the audio input envelope. The gain changes depending on the amplitude, the limiter level, the compression ratio, and the attack and release time. The gain changes constantly as the audio signal increases and/or decreases to create the compression effect. The gain step size for the AGC is 0.5 dB. If the audio signal has near-constant amplitude, the gain does not change. [Figure 15](#) shows how the AGC works.

- Gain decreases with no delay; attack time is reset. Release time and hold time are reset.

- Signal amplitude above limiter level, but gain cannot change because attack time is not over.

- Attack time ends; gain is allowed to decrease from this point forward by one step. Gain decreases because the amplitude remains above limiter threshold. All times are reset

- Gain increases after release time finishes and signal amplitude remains below desired level. All times are reset after the gain increase.

- Gain increases after release time is finished again because signal amplitude remains below desired level. All times are reset after the gain increase.

**Figure 15. Input and Output Audio Signal vs Time**

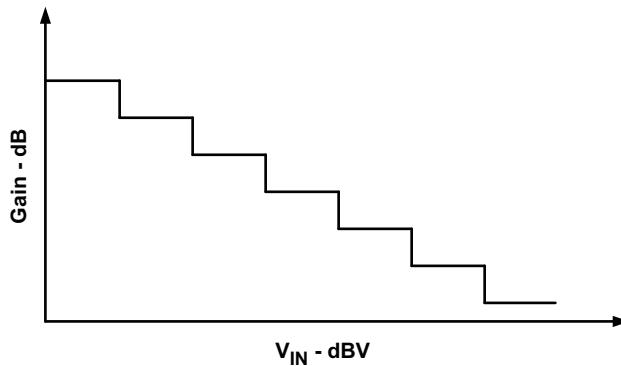

Since the number of gain steps is limited the compression region is limited as well. The following figure shows how the gain changes vs. the input signal amplitude in the compression region.

**Figure 16. Input Signal Voltage vs Gain**

Thus the AGC performs a mapping of the input signal vs. the output signal amplitude.

Pins AGC1 and AGC 2 are used to enable/disable the limiter, compression, and noise gate function. [Table 1](#) shows each function.

**Table 1. FUNCTION DEFINITION FOR AGC1 AND AGC2**

| AGC1 | AGC2 | Function                                                    |

|------|------|-------------------------------------------------------------|

| 0    | 0    | AGC Function disabled                                       |

| 0    | 1    | AGC Limiter Function enabled                                |

| 1    | 0    | AGC, Limiter, and Compression Functions enabled             |

| 1    | 1    | AGC, Limiter, Compression, and Noise Gate Functions enabled |

The default values for the TPA2029D1 AGC function are given in [Table 2](#). The default values can be changed at the factory during production. Refer to the TI representative for assistance with different default value requests.

**Table 2. AGC DEFAULT VALUES**

| AGC Parameters       | TPA2029D1             |

|----------------------|-----------------------|

| Attack Time          | 14.084 ms / 6 dB step |

| Release Time         | 822 ms/ 6 dB step     |

| Hold Time            | off                   |

| Fixed Gain           | 9 dB                  |

| NoiseGate Threshold  | 4 mV                  |

| Output Limiter Level | 9 dBV                 |

| Max Gain             | 30 dB                 |

| Compression Ratio    | 2:1                   |

## DECOUPLING CAPACITOR ( $C_s$ )

The TPA2029D1 is a high-performance Class-D audio amplifier that requires adequate power supply decoupling to ensure the efficiency is high and total harmonic distortion (THD) is low. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) 1- $\mu$ F ceramic capacitor (typically) placed as close as possible to the device PVDD lead works best. Placing this decoupling capacitor close to the TPA2029D1 is important for the efficiency of the Class-D amplifier, because any resistance or inductance in the trace between the device and the capacitor can cause a loss in efficiency. For filtering lower-frequency noise signals, a 4.7  $\mu$ F or greater capacitor placed near the audio power amplifier would also help, but it is not required in most applications because of the high PSRR of this device.

## INPUT CAPACITORS ( $C_I$ )

The input capacitors and input resistors form a high-pass filter with the corner frequency,  $f_C$ , determined in [Equation 1](#).

$$f_C = \frac{1}{(2\pi \times R_I \times C_I)} \quad (1)$$

The value of the input capacitor is important to consider as it directly affects the bass (low frequency) performance of the circuit. Speakers in wireless phones cannot usually respond well to low frequencies, so the corner frequency can be set to block low frequencies in this application. Not using input capacitors can increase output offset. [Equation 2](#) is used to solve for the input coupling capacitance. If the corner frequency is within the audio band, the capacitors should have a tolerance of  $\pm 10\%$  or better, because any mismatch in capacitance causes an impedance mismatch at the corner frequency and below.

$$C_I = \frac{1}{(2\pi \times R_I \times f_C)} \quad (2)$$

## COMPONENT LOCATION

Place all the external components very close to the TPA2029D1. Placing the decoupling capacitor,  $C_s$ , close to the TPA2029D1 is important for the efficiency of the Class-D amplifier. Any resistance or inductance in the trace between the device and the capacitor can cause a loss in efficiency.

## EFFICIENCY AND THERMAL INFORMATION

The maximum ambient temperature depends on the heat-sinking ability of the PCB system. The derating factor for the packages are shown in the dissipation rating table. Converting this to  $\theta_{JA}$  for the W CSP package:

$$\theta_{JA} = \frac{1}{\text{Derating Factor}} = \frac{1}{0.0095} = 105^\circ\text{C/W} \quad (3)$$

Given  $\theta_{JA}$  of  $100^\circ\text{C/W}$ , the maximum allowable junction temperature of  $150^\circ\text{C}$ , and the maximum internal dissipation of 0.4 W for 3 W output power into 4- $\Omega$  load, 5-V supply, from [Figure 7](#), the maximum ambient temperature can be calculated with the following equation.

$$T_{A\text{Max}} = T_{J\text{Max}} - \theta_{JA} P_{D\text{MAX}} = 150 - 105 (0.4) = 108^\circ\text{C} \quad (4)$$

[Equation 4](#) shows that the calculated maximum ambient temperature is  $108^\circ\text{C}$  at maximum power dissipation with a 5-V supply and 4- $\Omega$  a load. The TPA2029D1 is designed with thermal protection that turns the device off when the junction temperature surpasses  $150^\circ\text{C}$  to prevent damage to the IC. Also, using speakers more resistive than 8- $\Omega$  dramatically increases the thermal performance by reducing the output current and increasing the efficiency of the amplifier.

## OPERATION WITH DACS AND CODECS

In using Class-D amplifiers with CODECs and DACs, sometimes there is an increase in the output noise floor from the audio amplifier. This occurs when mixing of the output frequencies of the CODEC/DAC mix with the switching frequencies of the audio amplifier input stage. The noise increase can be solved by placing a low-pass filter between the CODEC/DAC and audio amplifier. This filters off the high frequencies that cause the problem and allow proper performance. See the functional block diagram.

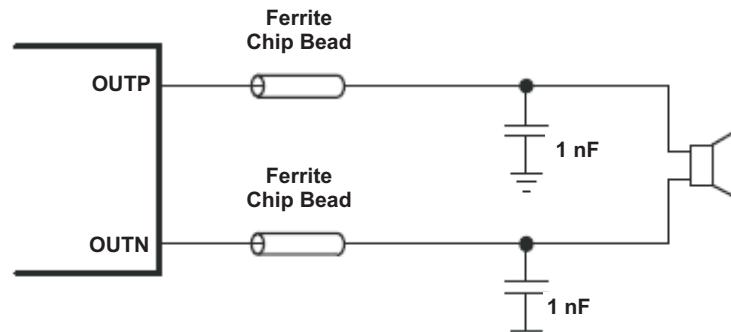

## FILTER FREE OPERATION AND FERRITE BEAD FILTERS

A ferrite bead filter can often be used if the design is failing radiated emissions without an LC filter and the frequency sensitive circuit is greater than 1 MHz. This filter functions well for circuits that just have to pass FCC and CE because FCC and CE only test radiated emissions greater than 30 MHz. When choosing a ferrite bead, choose one with high impedance at high frequencies, and low impedance at low frequencies. In addition, select a ferrite bead with adequate current rating to prevent distortion of the output signal.

Use an LC output filter if there are low frequency (< 1 MHz) EMI sensitive circuits and/or there are long leads from amplifier to speaker. [Figure 17](#) shows typical ferrite bead and LC output filters.

**Figure 17. Typical Ferrite Bead Filter (Chip bead example: TDK: MPZ1608S221A)**

## PACKAGE INFORMATION

### Package Dimensions

The package dimensions for this YZF package are shown in the table below. See the package drawing at the end of this data sheet for more details.

**Table 3. YZF Package Dimensions**

| Packaged Devices | D                                        | E                                        |

|------------------|------------------------------------------|------------------------------------------|

| TPA2029D1YF      | Min = 1594 $\mu$ m<br>Max = 1654 $\mu$ m | Min = 1594 $\mu$ m<br>Max = 1654 $\mu$ m |

## REVISION HISTORY

### Changes from Revision December 2011 (\*) to Revision A

### Page

- Added [Figure 14](#) ..... 9

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPA2029D1YZFR         | Active        | Production           | DSBGA (YZF)   9 | 3000   LARGE T&R      | Yes         | SNAGCU                               | Level-1-260C-UNLIM                | -40 to 85    | QWI                 |

| TPA2029D1YZFR.B       | Active        | Production           | DSBGA (YZF)   9 | 3000   LARGE T&R      | Yes         | SNAGCU                               | Level-1-260C-UNLIM                | -40 to 85    | QWI                 |

| TPA2029D1YZFT         | Active        | Production           | DSBGA (YZF)   9 | 250   SMALL T&R       | Yes         | SNAGCU                               | Level-1-260C-UNLIM                | -40 to 85    | QWI                 |

| TPA2029D1YZFT.B       | Active        | Production           | DSBGA (YZF)   9 | 250   SMALL T&R       | Yes         | SNAGCU                               | Level-1-260C-UNLIM                | -40 to 85    | QWI                 |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

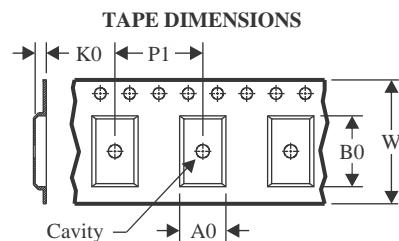

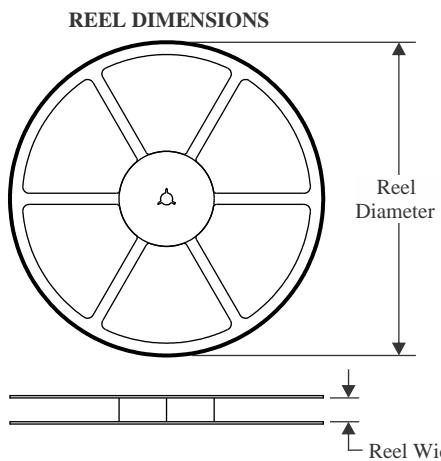

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

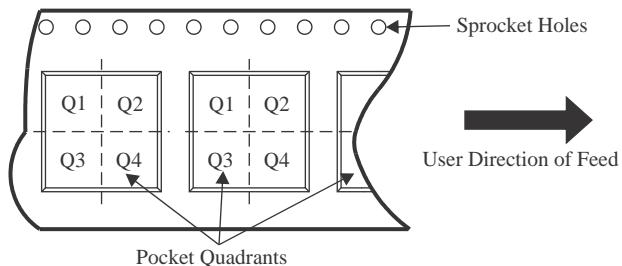

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPA2029D1YZFR | DSBGA        | YZF             | 9    | 3000 | 180.0              | 8.4                | 1.71    | 1.71    | 0.81    | 4.0     | 8.0    | Q1            |

| TPA2029D1YZFT | DSBGA        | YZF             | 9    | 250  | 180.0              | 8.4                | 1.71    | 1.71    | 0.81    | 4.0     | 8.0    | Q1            |

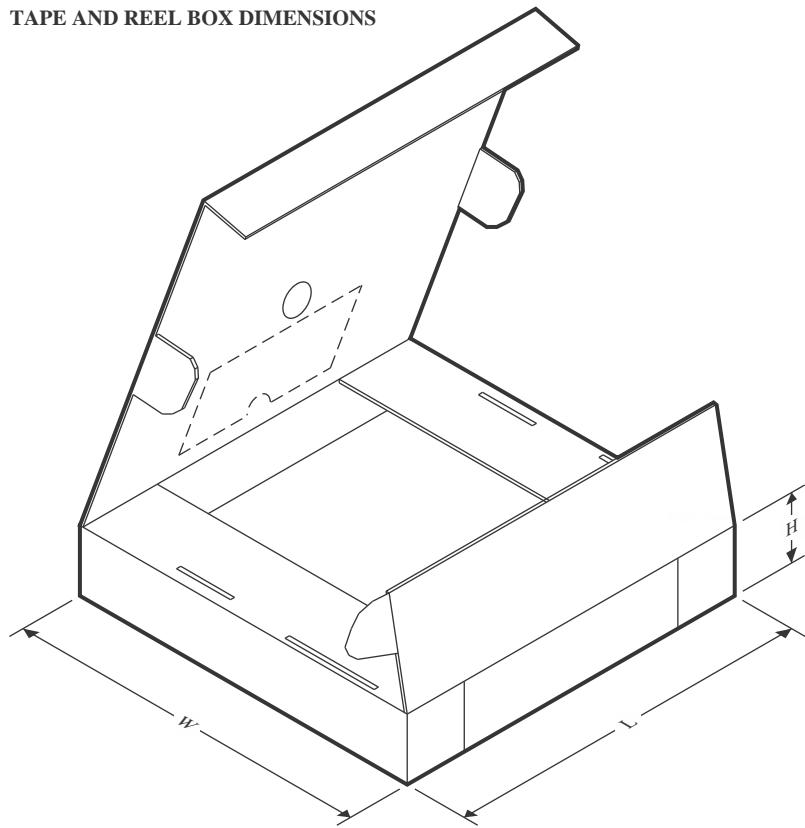

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPA2029D1YZFR | DSBGA        | YZF             | 9    | 3000 | 182.0       | 182.0      | 20.0        |

| TPA2029D1YZFT | DSBGA        | YZF             | 9    | 250  | 182.0       | 182.0      | 20.0        |

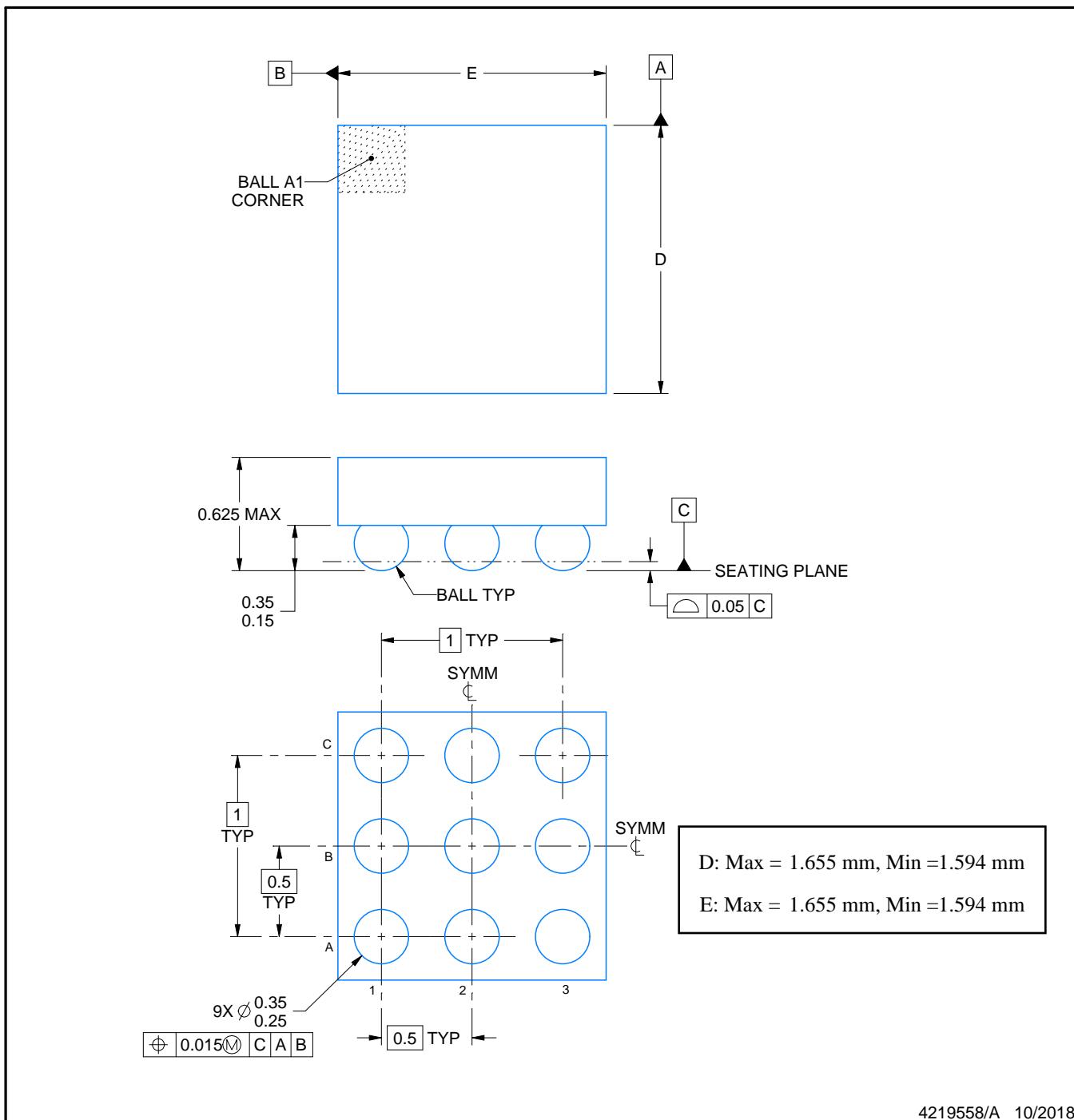

# PACKAGE OUTLINE

YZF0009

DSBGA - 0.625 mm max height

DIE SIZE BALL GRID ARRAY

4219558/A 10/2018

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

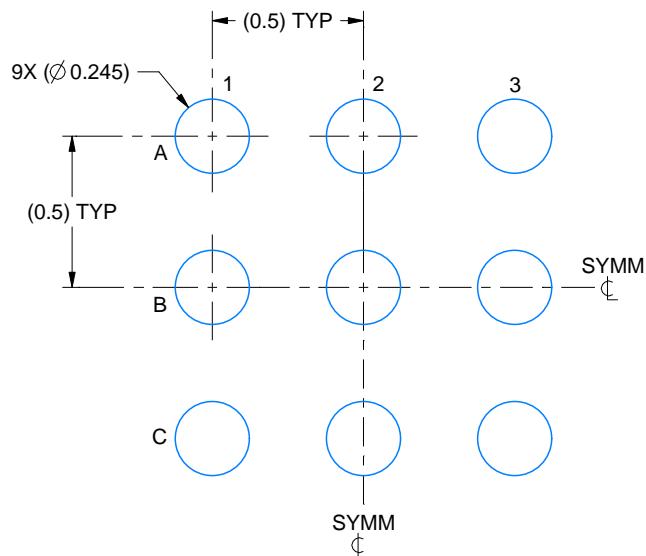

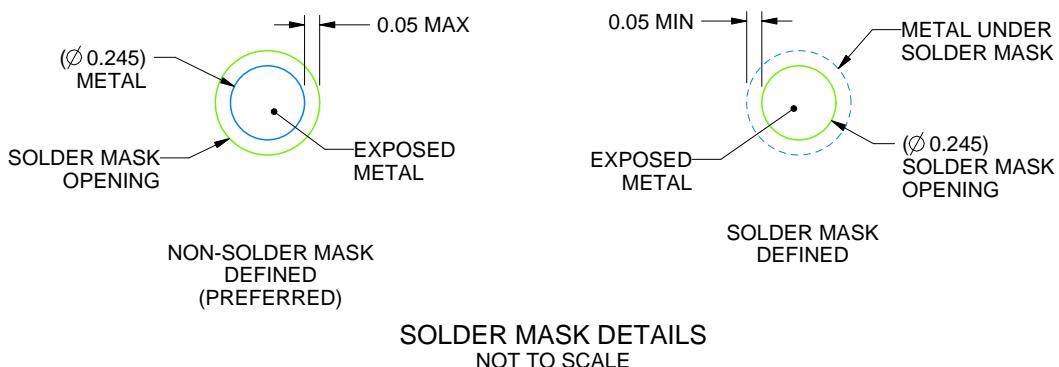

# EXAMPLE BOARD LAYOUT

YZF0009

DSBGA - 0.625 mm max height

DIE SIZE BALL GRID ARRAY

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 40X

4219558/A 10/2018

NOTES: (continued)

- Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints.

See Texas Instruments Literature No. SNVA009 ([www.ti.com/lit/snva009](http://www.ti.com/lit/snva009)).

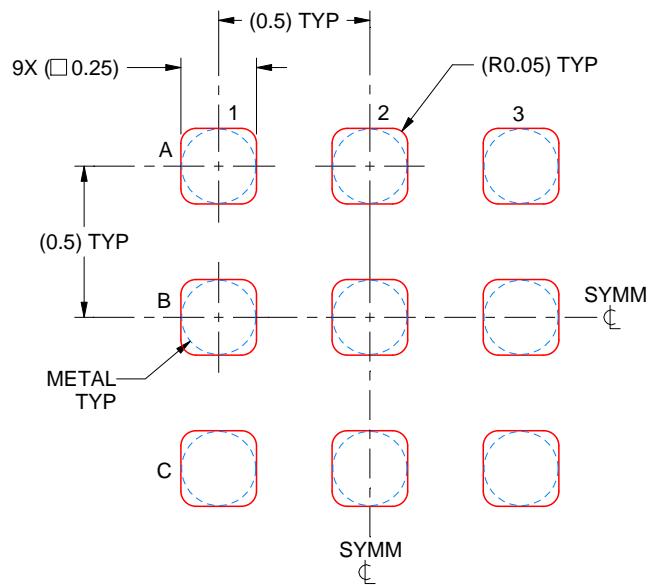

# EXAMPLE STENCIL DESIGN

YZF0009

DSBGA - 0.625 mm max height

DIE SIZE BALL GRID ARRAY

SOLDER PASTE EXAMPLE

BASED ON 0.1 mm THICK STENCIL

SCALE: 40X

4219558/A 10/2018

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2026，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月