TMP431, TMP432

ZHCSKD0I - SEPTEMBER 2009 - REVISED OCTOBER 2019

# 具有串联电阻、 η 因数和自动 Beta 补偿的 TMP43x ±1°C 温度传感器

# 1 特性

- ±1°C 远程二极管传感器

- ±1°C 本地温度传感器

- 自动 Beta 补偿

- η 因数校正

- 可编程阈值限制

- 两线制, SMBus™串行接口

- 最小和最大温度监控器

- 多接口地址

- ALERT/THERM2 引脚配置

- 二极管故障检测

### 2 应用

- LCD、DLP、®LCOS 投影仪

- 服务器

- 工业控制器

- 中央办公电信设备

- 台式机和笔记本电脑

- 存储区域网络 (SAN)

- 工业用和医疗用设备

- 处理器和 FPGA 温度监视

# 3 说明

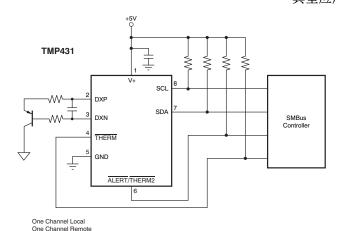

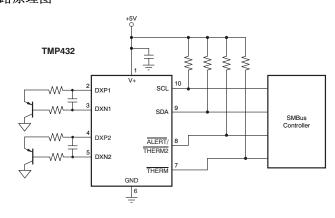

TMP431 和 TMP432 均是具有内置本地温度传感器的远程温度传感器监视器。远程温度传感器二极管连接的晶体管通常是低成本、NPN 或 PNP 类型的晶体管或二极管,这些器件是微控制器、微处理器或 FPGA 必不可少的组成部分。

针对多个器件制造商的远程精度均为±1°C,无需校准。两线制串行接口可接受 SMBus 写入字节、读取字节、发送字节和接收字节命令,以便对警报阈值进行编程并读取温度数据。

TMP43X 包括 Beta 补偿(校正)、串联电阻抵消、可编程非理想性因子、可编程分辨率、可编程阈值限制、最小和最大温度监视器、宽远程温度测量范围(高达150°C)、二极管故障检测和温度报警功能。

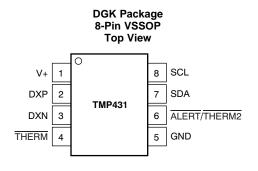

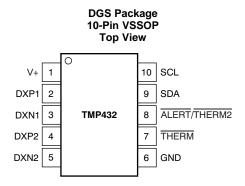

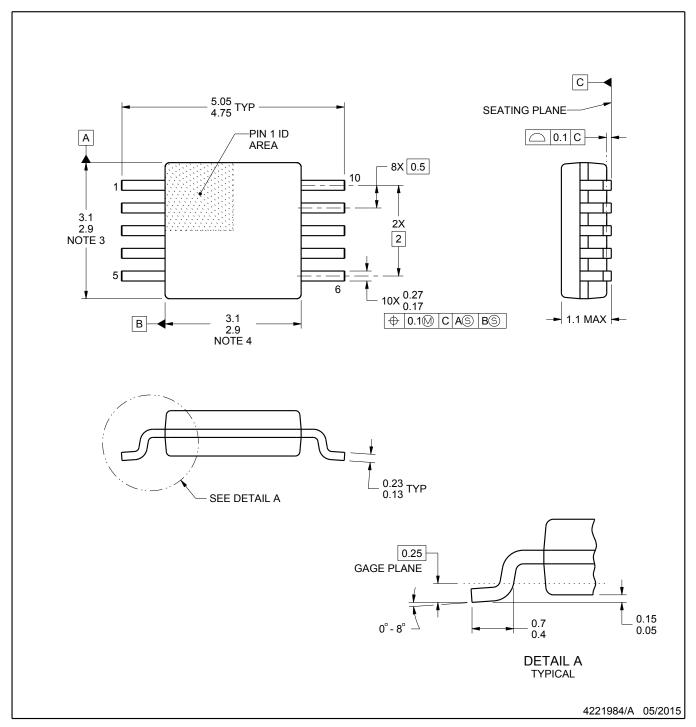

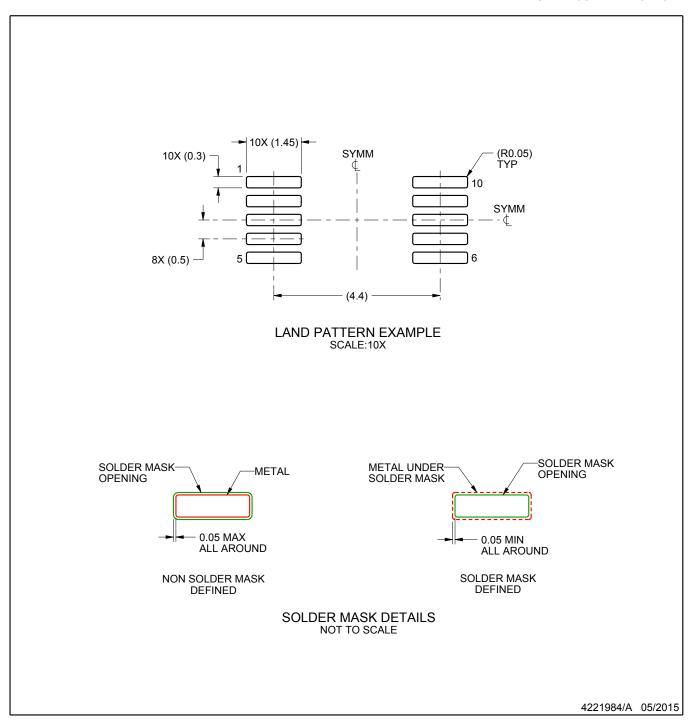

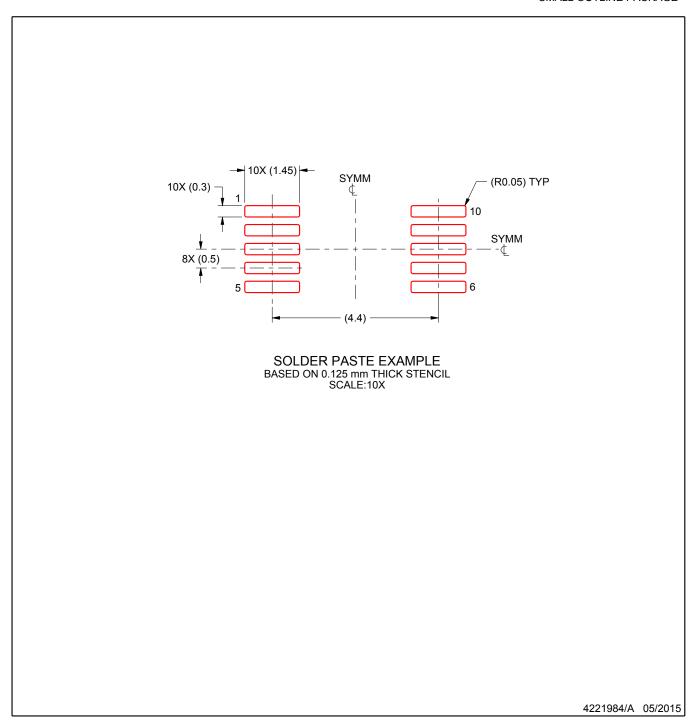

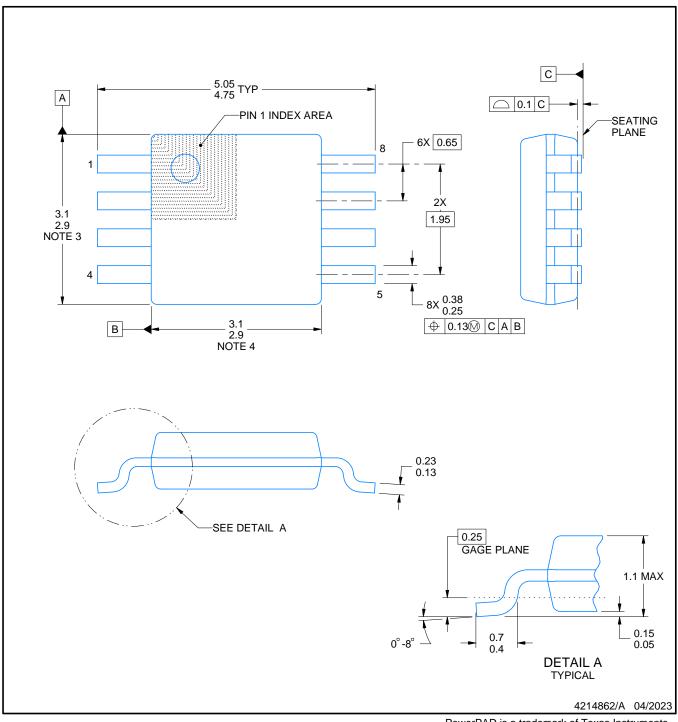

TMP431 采用 VSSOP-8 封装, TMP432 采用 VSSOP-10 封装。

### 器件信息(1)

| 器件型号   | 封装         | 封装尺寸 (标称值)      |

|--------|------------|-----------------|

| TMP431 | VSSOP (8)  | 3.00mm × 3.00mm |

| TMP432 | VSSOP (10) | 3.00mm × 3.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

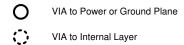

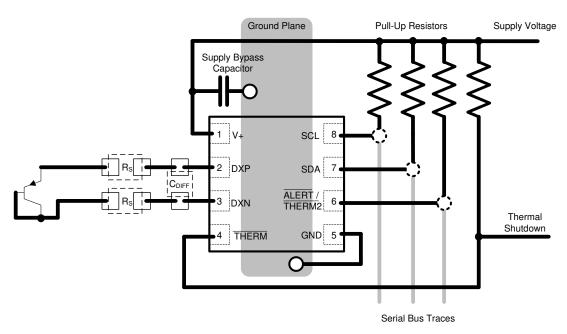

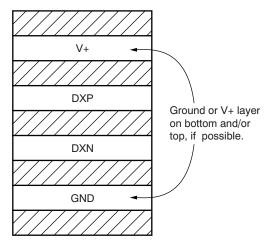

### 典型应用电路原理图

One Channel Local Two Channels Remote

$\triangle$

| $\neg$ | $\Rightarrow$ |

|--------|---------------|

| -      | ملب           |

| -      | w             |

| _ | at the                               |    |                                |      |

|---|--------------------------------------|----|--------------------------------|------|

| 1 | 特性 1                                 |    | 8.4 Device Functional Modes    |      |

| 2 | 应用 1                                 |    | 8.5 Programming                |      |

| 3 | 说明1                                  |    | 8.6 Register Maps              | 20   |

| 4 | 修订历史记录 2                             | 9  | Application and Implementation | 33   |

| 5 | Pin Configuration and Functions 4    |    | 9.1 Application Information    | 33   |

| 6 | Specifications4                      |    | 9.2 Typical Application        | 33   |

| ٠ | 6.1 Absolute Maximum Ratings         | 10 | Power Supply Recommendations   | 36   |

|   | 6.2 ESD Ratings                      | 11 | Layout                         | . 36 |

|   | 6.3 Recommended Operating Conditions |    | 11.1 Layout Guidelines         | 36   |

|   | 6.4 Thermal Information              |    | 11.2 Layout Examples           | 37   |

|   | 6.5 Electrical Characteristics 6     | 12 | 器件和文档支持                        | 39   |

|   | 6.6 Timing Requirements              |    | 12.1 相关链接                      | 39   |

|   | 6.7 Typical Characteristics8         |    | 12.2 社区资源                      | 39   |

| 7 | Parameter Measurement Information    |    | 12.3 商标                        | 39   |

| 8 | Detailed Description 11              |    | 12.4 静电放电警告                    | 39   |

| Ŭ | 8.1 Overview                         |    | 12.5 Glossary                  | 39   |

|   | 8.2 Functional Block Diagram         | 13 | 机械、封装和可订购信息                    |      |

|   | 8.3 Feature Description              |    |                                |      |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| CI | hanges from Revision H (March 2016) to Revision I                                                                                                                                                                         | Page           |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •  | Added acknowledgement information to the SMBus Alert Function section                                                                                                                                                     | 19             |

| •  | Added register comparison information to the Limit Registers section                                                                                                                                                      | 23             |

| •  | Removed sentence from the <i>TMP432 Status Register</i> section: Clearing the Status Register bits does not clear the state of the ALERT pin; an SMBus alert response address command must be used to clear the ALERT pin | 26             |

| •  | Added new ALERT pin information to the Configuration Register 1 section                                                                                                                                                   | 26             |

| •  | Changed extended measurement range from: (-55°C to 150°C) to: (-64°C to 191°C)                                                                                                                                            | 26             |

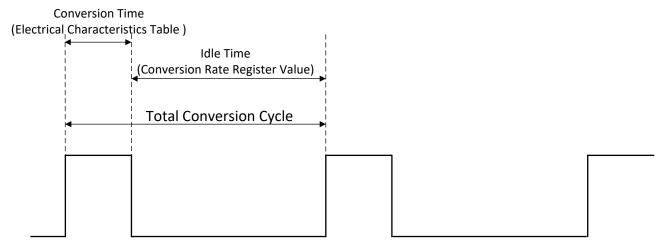

| •  | Added Conversion Rate Timing Diagram                                                                                                                                                                                      | 28             |

| •  | Split the $\eta$ table column into $\eta$ = 1.008 and $\eta$ = 1.000 in the $\eta$ -Factor Range table                                                                                                                    | 30             |

| CI | hanges from Revision G (December 2015) to Revision H                                                                                                                                                                      | Page           |

| •  | Changed row 1B in Table 4                                                                                                                                                                                                 |                |

| •  |                                                                                                                                                                                                                           |                |

|    | Changed 7th paragraph of TMP432 Status Register section                                                                                                                                                                   | 26             |

| •  | Changed Open Status Register section                                                                                                                                                                                      | 26<br>31       |

| •  | Changed Open Status Register section                                                                                                                                                                                      | 26<br>31<br>32 |

|    | Changed Open Status Register section                                                                                                                                                                                      | 26<br>31<br>32 |

| •  | Changed Open Status Register section                                                                                                                                                                                      | 26<br>31<br>32 |

| Changes from Revision E (December 2012) to Revision F                                                     | Page |

|-----------------------------------------------------------------------------------------------------------|------|

| Added five new register descriptions                                                                      | 31   |

| Changes from Revision D (November 2012) to Revision E                                                     | Page |

| • 通篇将 MSOP-10 更改为 VSSOP-10                                                                                | 1    |

| Changes from Revision C (February 2011) to Revision D                                                     | Page |

| • 通篇将 MSOP-8 更改为 VSSOP-8                                                                                  | 1    |

| Changes from Revision B (April 2010) to Revision C                                                        | Page |

| Revised Figure 14                                                                                         | 16   |

| Updated Figure 15                                                                                         | 17   |

| Changed Figure 16                                                                                         | 18   |

| Revised Figure 17                                                                                         | 18   |

| Updated Serial Bus Address section for TMP431C, TMP431D device versions                                   | 19   |

| Added footnote (3) to TMP431 Register Map                                                                 | 21   |

| Revised information about power-on reset value of THERM limit registers in <i>Limit Registers</i> section | 24   |

| Changes from Revision A (November 2009) to Revision B                                                     | Page |

| Corrected Equation 7                                                                                      |      |

| Changes from Original (September 2009) to Revision A                                                      | Page |

| 己更改 通篇更改了 TMP432 的器件状态                                                                                    |      |

| Corrected bit D6 value in Configuration Register 1 in TMP431 Register Map                                 | 21   |

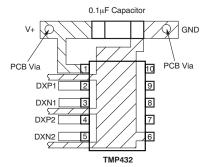

# 5 Pin Configuration and Functions

#### **Pin Functions**

|              | PIN    |        | 1/0 | DESCRIPTION                                                                                                   |  |  |

|--------------|--------|--------|-----|---------------------------------------------------------------------------------------------------------------|--|--|

| NAME         | TMP432 | TMP431 | 1/0 | DESCRIPTION                                                                                                   |  |  |

| ALERT/THERM2 | 8      | 6      | 0   | Digital alert (reconfigurable as second thermal flag), active low, open-drain; requires pullup resistor to V+ |  |  |

| DXN          | _      | 3      | I   | Analog negative connection to remote temperature sensor                                                       |  |  |

| DXN1         | 3      | _      | I   | Analog channel 1 negative connection to remote temperature sensor                                             |  |  |

| DXN2         | 5      | _      | I   | Analog channel 2 negative connection to remote temperature sensor                                             |  |  |

| DXP          | _      | 2      | I   | I Analog positive connection to remote temperature sensor                                                     |  |  |

| DXP1         | 2      | _      | I   | Analog channel 1 positive connection to remote temperature sensor                                             |  |  |

| DXP2         | 4      | _      | I   | Analog channel 2 positive connection to remote temperature sensor                                             |  |  |

| GND          | 6      | 5      | _   | Ground                                                                                                        |  |  |

| SCL          | 10     | 8      | I   | Digital serial clock line for SMBus, open-drain; requires pullup resistor to V+                               |  |  |

| SDA          | 9      | 7      | I/O | Bidirectional digital, serial data line for SMBus, open-drain; requires pullup resistor to V+                 |  |  |

| THERM        | 7      | 4      | 0   | Digital, thermal flag, active low, open-drain; requires pullup resistor to V+                                 |  |  |

| V+           | 1      | 1      | _   | Power supply, positive (2.7 V to 5.5 V)                                                                       |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                                    | MIN  | MAX      | UNIT |

|---------------------------------------|------------------------------------|------|----------|------|

| Power supply, V <sub>S</sub>          |                                    |      | 7        | V    |

| TMD421 input voltage                  | Pins 2, 3, and 6                   | -0.5 | V+ + 0.5 | ٧    |

| 「MP431 input voltage                  | Pins 4, 7, and 8                   | -0.5 | 7        | ٧    |

| TMD422 input voltage                  | Pins 2, 3, 4, 5, and 8             | -0.5 | V+ + 0.5 | V    |

| TMP432 input voitage                  | Pins 7, 9, and 10                  | -0.5 | 7        | ٧    |

| Input current                         |                                    |      | 10       | mA   |

| Operating temperature                 | Operating temperature              |      | 127      | °C   |

| Junction temperature, T <sub>J</sub>  | nction temperature, T <sub>J</sub> |      | 150      | °C   |

| Storage temperature, T <sub>stg</sub> |                                    | -60  | 130      | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|             |  |                                                                     | VALUE | UNIT |

|-------------|--|---------------------------------------------------------------------|-------|------|

|             |  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±4000 |      |

| $V_{(ESD)}$ |  | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

| (===)       |  | Machine model (MM)                                                  | ±200  |      |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                                | MIN | NOM | MAX | UNIT |

|------------------------------------------------|-----|-----|-----|------|

| Supply voltage                                 | 2.7 | 3.3 | 5.5 | V    |

| Operating free-air temperature, T <sub>A</sub> | -40 |     | 125 | °C   |

### 6.4 Thermal Information

|                      |                                              | TMP431      | TMP432      |      |

|----------------------|----------------------------------------------|-------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DGK (VSSOP) | DGS (VSSOP) | UNIT |

|                      |                                              | 8 PINS      | 10 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 168.2       | 164.6       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 59.7        | 39          | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 90.1        | 85.9        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 7.7         | 1.6         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 88.4        | 84.2        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A         | N/A         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

at  $T_A = -40$ °C to 125°C and V+ = 2.7 V to 5.5 V (unless otherwise noted)

|                      | PARAMETER                            | TEST CONDITIONS                                                                 | MIN     | TYP                  | MAX      | UNIT |

|----------------------|--------------------------------------|---------------------------------------------------------------------------------|---------|----------------------|----------|------|

| TEMPERA              | TURE ERROR                           |                                                                                 |         |                      |          |      |

|                      |                                      | $T_A = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$                     |         | ±1.25                | ±2.5     |      |

| TE <sub>LOCAL</sub>  | Local temperature sensor             | T <sub>A</sub> = 0°C to 100°C, V+ = 3.3 V                                       |         | ±0.25                | ±1       | °C   |

|                      |                                      | $T_A = 0$ °C to 100°C, $T_{DIODE} = -40$ °C to 150°C, V+ = 3.3 V                |         | ±0.25                | ±1       |      |

| TE <sub>REMOTE</sub> | Remote temperature sensor (1)        | $T_A = -40$ °C to 100°C, $T_{DIODE} = -40$ °C to 150°C, $V_{+} = 3.3 \text{ V}$ |         | ±0.5                 | ±1.5     | °C   |

|                      |                                      | $T_A = -40$ °C to 125°C, $T_{DIODE} = -40$ °C to 150°C                          |         | ±3                   | ±5       |      |

|                      | vs supply (local, remote)            | V+ = 2.7 V to 5.5 V                                                             |         | ±0.2                 | ±0.5     | °C/V |

| TEMPERA              | TURE MEASUREMENT CONVERSION          | ON TIME (PER CHANNEL)                                                           |         |                      |          |      |

|                      | Local channel                        |                                                                                 | 12      | 15                   | 17       | ms   |

|                      | Remote channel,                      | RC = 1                                                                          | 97      | 126                  | 137      |      |

|                      | beta correction enabled (2)          | RC = 0                                                                          | 36      | 47                   | 52       | ms   |

|                      | Remote channel,                      | RC = 1                                                                          | 72      | 93                   | 100      |      |

|                      | beta correction disabled (3)         | RC = 0                                                                          | 33      | 44                   | 47       | ms   |

| TEMPERA              | TURE MEASUREMENT RESOLUTIO           | N                                                                               |         |                      |          |      |

|                      | Local channel                        |                                                                                 |         | 12                   |          | Bits |

|                      | Remote channel                       |                                                                                 |         | 12                   |          | Bits |

| TEMPERA              | TURE MEASUREMENT REMOTE SE           | NSOR SOURCE CURRENTS                                                            |         |                      |          |      |

|                      | High                                 | Series resistance (beta correction) (4)                                         |         | 120                  |          | μА   |

|                      | Medium-high                          |                                                                                 |         | 60                   |          | μА   |

|                      | Medium-low                           |                                                                                 |         | 12                   |          | μА   |

|                      | Low                                  |                                                                                 |         | 6                    |          | μА   |

|                      |                                      |                                                                                 |         | 1.000(2)             |          | -    |

| η                    | Remote transistor ideality factor    | TMP43x optimized ideality factor                                                |         | 1.008 <sup>(3)</sup> |          |      |

| β                    | Beta correction range                |                                                                                 | 0.1     |                      | 27       |      |

| SMBus IN             | TERFACE                              |                                                                                 |         |                      | <u> </u> |      |

| V <sub>IH</sub>      | Logic input high voltage (SCL, SDA)  |                                                                                 | 2.1     |                      |          | V    |

| V <sub>IL</sub>      | Logic input low voltage (SCL, SDA)   |                                                                                 |         |                      | 0.8      | V    |

|                      | Hysteresis                           |                                                                                 |         | 500                  |          | mV   |

|                      | SMBus output low sink current        |                                                                                 | 6       |                      |          | mA   |

| V <sub>OL</sub>      | SDA output low voltage               | I <sub>OUT</sub> = 6 mA                                                         |         | 0.15                 | 0.4      | V    |

|                      | Logic input current                  | $0 \le V_{IN} \le 6 V$                                                          | -1      |                      | 1        | μА   |

|                      | SMBus input capacitance (SCL, SDA)   |                                                                                 |         | 3                    |          | pF   |

|                      | SMBus clock frequency                |                                                                                 |         |                      | 3.4      | MHz  |

|                      | SMBus timeout                        |                                                                                 | 25      | 32                   | 35       | ms   |

|                      | SCL falling edge to SDA valid time   |                                                                                 |         |                      | 1        | μS   |

| DIGITAL O            | UTPUTS                               |                                                                                 | <u></u> |                      |          |      |

| V <sub>OL</sub>      | Output low voltage                   | I <sub>OUT</sub> = 6 mA                                                         |         | 0.15                 | 0.4      | V    |

| I <sub>OH</sub>      | High-level output leakage current    | V <sub>OUT</sub> = V+                                                           |         | 0.1                  | 1        | μА   |

|                      | ALERT/THERM2 output low sink current | ALERT/THERM2 forced to 0.4 V                                                    | 6       |                      |          | mA   |

|                      | THERM output low sink current        | THERM2 forced to 0.4 V                                                          | 6       |                      |          | mA   |

<sup>(1)</sup> Tested with less than  $5-\Omega$  effective series resistance and 100-pF differential input capacitance.  $T_A$  is the ambient temperature of the TMP43x.  $T_{\text{DIODE}}$  is the temperature at the remote diode sensor.

<sup>(2)</sup> Beta correction configuration set to 1000 and sensor is GND collector-connected (PNP collector to ground).

(3) Beta correction configuration set to 0111 or sensor is diode-connected (base shorted to collector).

If beta correction is disabled (0111), then up to  $1-k\Omega$  of series line resistance is cancelled; if beta correction is enabled (1xxx), up to  $300~\Omega$  is cancelled.

# **Electrical Characteristics (continued)**

at  $T_A = -40$ °C to 125°C and V+ = 2.7 V to 5.5 V (unless otherwise noted)

|       | PARAMETER                   | TEST CONDITIONS                                            | MIN | TYP | MAX | UNIT |

|-------|-----------------------------|------------------------------------------------------------|-----|-----|-----|------|

| POWER | SUPPLY                      |                                                            |     |     |     |      |

| V+    | Specified voltage range     |                                                            | 2.7 |     | 5.5 | V    |

|       |                             | 0.0625 conversions per second, V+ = 3.3 V                  |     | 35  | 45  | μА   |

|       |                             | Eight conversions per second, V+ = 3.3 V <sup>(5)</sup>    |     | 0.7 | 1   | mA   |

| $I_Q$ | Quiescent current           | Serial bus inactive, shutdown mode                         |     | 3   | 10  |      |

|       |                             | Serial bus active, f <sub>S</sub> = 400 kHz, shutdown mode |     | 90  |     | μΑ   |

|       |                             | Serial bus active, f <sub>S</sub> = 3.4 MHz, shutdown mode |     | 350 |     |      |

| UVLO  | Undervoltage lockout        |                                                            | 2.3 | 2.4 | 2.6 | V    |

| POR   | Power-on reset threshold    |                                                            |     | 1.6 | 2.3 | V    |

|       | Specified temperature range |                                                            | -40 |     | 125 | °C   |

|       | Storage temperature range   |                                                            | -60 |     | 130 | °C   |

<sup>(5)</sup> Beta correction disabled.

# 6.6 Timing Requirements<sup>(1)</sup>

|                      |                                                                                   |                | FAST M           | ODE  | HIGH-SPEE        | D MODE | UNIT |

|----------------------|-----------------------------------------------------------------------------------|----------------|------------------|------|------------------|--------|------|

|                      |                                                                                   |                | MIN              | MAX  | MIN              | MAX    | UNII |

| f <sub>(SCL)</sub>   | SCL operating frequency                                                           | V+             | 0.001            | 0.4  | 0.001            | 2.5    | MHz  |

| t <sub>(BUF)</sub>   | Bus free time between STOP and STA                                                | ART condition  | 600              |      | 160              |        | ns   |

| t <sub>(HDSTA)</sub> | Hold time after repeated START cond<br>After this period, the first clock is gene |                | 100              |      | 100              |        | ns   |

| t <sub>(SUSTA)</sub> | Repeated START condition setup time                                               | 9              | 100              |      | 100              |        | ns   |

| t <sub>(SUSTO)</sub> | STOP condition setup time                                                         | 100            |                  | 100  |                  | ns     |      |

| t <sub>(HDDAT)</sub> | Data hold time                                                                    |                | 0 <sup>(2)</sup> | 900  | 0 <sup>(3)</sup> | 80     | ns   |

| t <sub>(SUDAT)</sub> | Data setup time                                                                   |                | 100              |      | 25               |        | ns   |

| $t_{(LOW)}$          | SCL clock LOW period                                                              | V+             | 1300             |      | 265              |        | ns   |

| t <sub>(HIGH)</sub>  | SCL clock HIGH period                                                             |                | 600              |      | 60               |        | ns   |

| t <sub>F</sub> D     | Data fall time                                                                    |                |                  | 300  |                  | 160    | ns   |

| + 0                  | Clock rise time                                                                   |                |                  | 300  |                  | 40     |      |

| t <sub>R</sub> C     | Clock rise time                                                                   | SCLK ≤ 100 kHz |                  | 1000 |                  |        | ns   |

| t <sub>F</sub> C     | Clock fall time                                                                   |                |                  | 300  |                  | 40     | ns   |

<sup>(1)</sup> Values based on a statistical analysis of a one-time sample of devices. Minimum and maximum values are not specified and not production tested

production tested.

(2) For cases with a fall time of SCL less than 20 ns or where the rise time or fall time of SDA is less than 20 ns, the hold time must be greater than 20 ns.

greater than 20 ns.

(3) For cases with a fall time of SCL less than 10 ns or where the rise or fall time of SDA is less than 10 ns, the hold time must be greater than 10 ns.

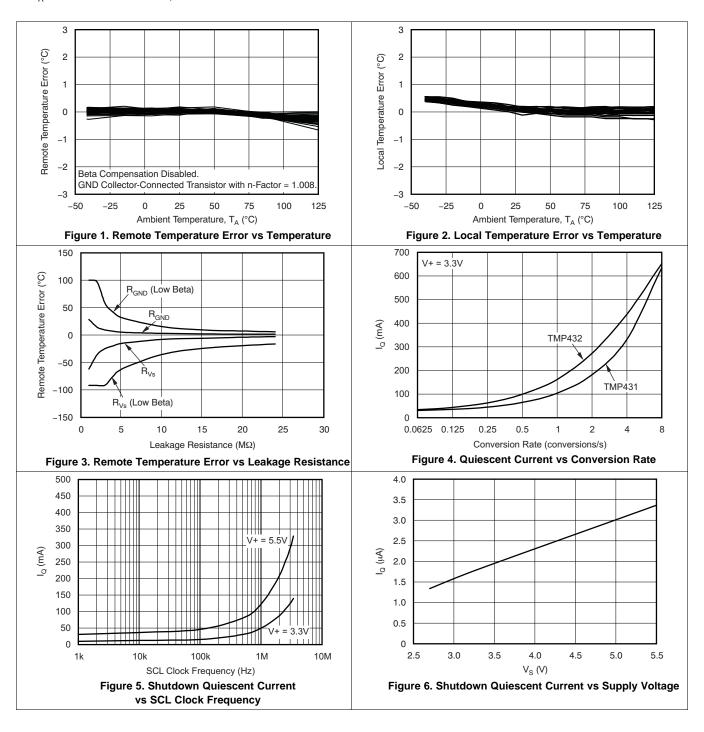

# 6.7 Typical Characteristics

At  $T_A = 25$ °C and V+ = 3.3 V, unless otherwise noted.

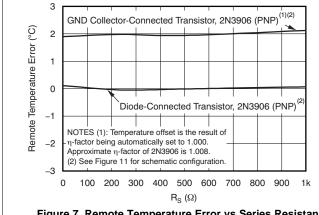

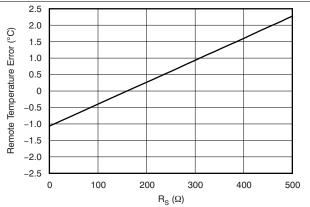

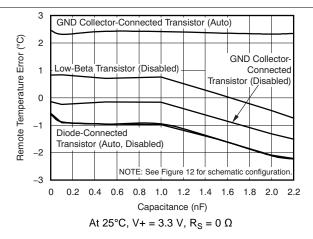

# **Typical Characteristics (continued)**

At  $T_A = 25$ °C and V+ = 3.3 V, unless otherwise noted.

Figure 7. Remote Temperature Error vs Series Resistance

Figure 8. Remote Temperature Error vs Series Resistance (Low-Beta Transistor)

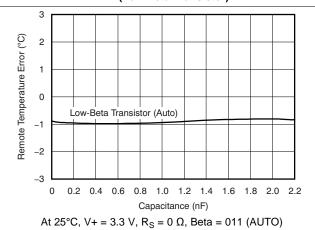

Figure 9. Remote Temperature Error vs Differential Capacitance

Figure 10. Remote Temperature Error vs Differential Capacitance With 45-nm CPU

# 7 Parameter Measurement Information

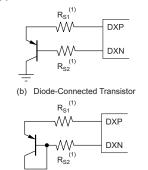

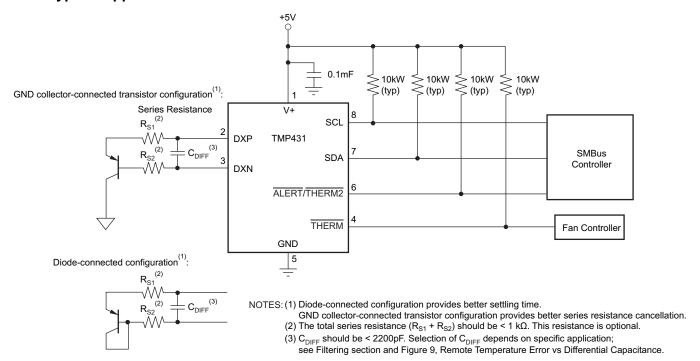

(a) GND Collector-Connected Transistor

(1) The total series resistance  $R_S = R_{S1} + R_{S2}$  must be less than 1 k $\Omega$ ; see *Filtering*.

Figure 11. Series Resistance Configuration

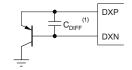

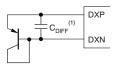

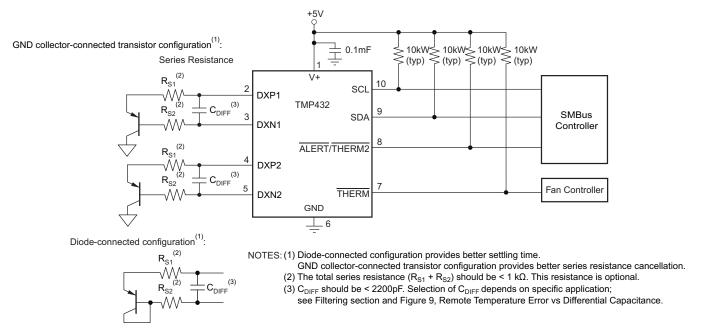

(a) GND Collector-Connected Transistor

(b) Diode-Connected Transistor

(1)  $C_{DIFF}$  must be less than 2200 pF; see *Filtering*.

Figure 12. Differential Capacitance Configuration

# 8 Detailed Description

#### 8.1 Overview

The TMP431 (two-channel) and TMP432 (three-channel) are digital temperature sensors that combine a local die temperature measurement channel and a remote junction temperature measurement channel in a single VSSOP-8 (TMP431) or VSSOP-10 (TMP432) package. They are Two-Wire- and SMBus interface-compatible and are specified over a temperature range of –40°C to 125°C. The TMP43x contain multiple registers for holding configuration information, temperature measurement results, temperature comparator maximum and minimum limits, and status information. User-programmed high and low temperature limits stored in the TMP43x can be used to trigger an overtemperature and undertemperature alarm (ALERT) on local and remote temperatures. Additional thermal limits can be programmed into the TMP43x and used to trigger another flag (THERM) that can be used to initiate a system response to rising temperatures.

For proper remote temperature sensing operation, the TMP431 requires only a transistor connected between DXP and DXN; the TMP432 requires transistors connected between DXP1 and DXN1, and between DXP2 and DXN2.

The SCL and SDA interface pins require pullup resistors as part of the communication bus; ALERT and THERM are open-drain outputs that also need pullup resistors. ALERT and THERM can be shared with other devices if desired for a wired-OR implementation. TI recommends a 0.1-μF power-supply bypass capacitor for good local bypassing.

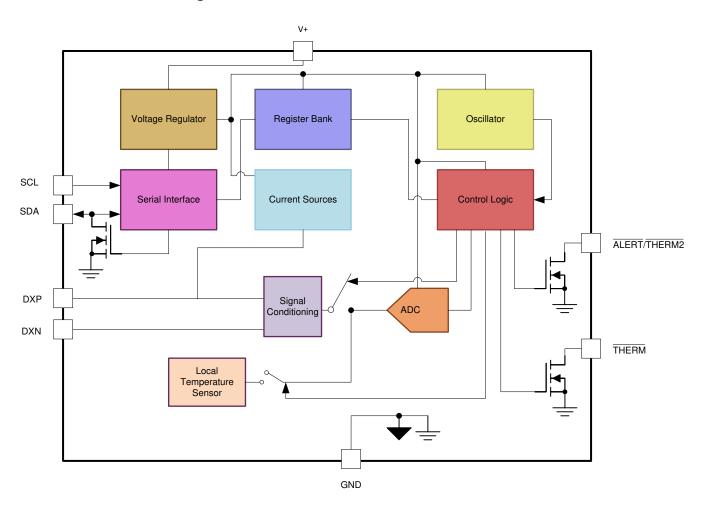

# 8.2 Functional Block Diagram

### 8.3 Feature Description

# 8.3.1 Temperature Measurement Data

Temperature measurement data are taken over a default range of 0°C to 127°C for both local and remote locations. However, measurements from –55°C to 150°C can be made both locally and remotely by reconfiguring the TMP43x for the extended temperature range, as described in this section. Temperature data resulting from conversions within the default measurement range are represented in binary form, as shown in Table 1, Standard Binary column. Note that any temperature below 0°C results in a data value of zero (00h). Likewise, temperatures above 127°C result in a value of 127 (7Fh). The device can be set to measure over an extended temperature range by changing bit 2 of Configuration Register 1 from low to high. The change in measurement range and data format from standard binary to extended binary occurs at the next temperature conversion.

For data captured in the extended temperature range configuration, an offset of 64 (40h) is added to the standard binary value, as shown in Table 1, Extended Binary column. This configuration allows measurement of temperatures as low as -64°C, and as high as 191°C; however, most temperature-sensing diodes only measure with the range of -55°C to 150°C.

Additionally, the TMP43x are rated only for ambient local temperatures ranging from –40°C to 125°C. Parameters in *Absolute Maximum Ratings* must be observed.

Both local and remote temperature data use two bytes for data storage. The high byte stores the temperature with 1°C resolution. The second or low byte stores the decimal fraction value of the temperature and allows a higher measurement resolution; see Table 2.

The measurement resolution for both the local and remote channels is 0.0625°C, and cannot be adjusted.

Table 1. Temperature Data Format (Local and Remote Temperature High Bytes)

|           | LOCAL/REMOTE TEMPERATURE REGISTER HIGH BYTE VALUE (1°C RESOLUTION) |                       |                                |     |  |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------|-----------------------|--------------------------------|-----|--|--|--|--|--|--|--|

| TEMP (°C) | STANDARD                                                           | BINARY <sup>(1)</sup> | EXTENDED BINARY <sup>(2)</sup> |     |  |  |  |  |  |  |  |

|           | BINARY                                                             | HEX                   | BINARY                         | HEX |  |  |  |  |  |  |  |

| -64       | 0000 0000                                                          | 00                    | 0000 0000                      | 00  |  |  |  |  |  |  |  |

| -50       | 0000 0000                                                          | 00                    | 0000 1110                      | 0E  |  |  |  |  |  |  |  |

| -25       | 0000 0000                                                          | 00                    | 0010 0111                      | 27  |  |  |  |  |  |  |  |

| 0         | 0000 0000                                                          | 00                    | 0100 0000                      | 40  |  |  |  |  |  |  |  |

| 1         | 0000 0001                                                          | 01                    | 0100 0001                      | 41  |  |  |  |  |  |  |  |

| 5         | 0000 0101                                                          | 05                    | 0100 0101                      | 45  |  |  |  |  |  |  |  |

| 10        | 0000 1010                                                          | 0A                    | 0100 1010                      | 4A  |  |  |  |  |  |  |  |

| 25        | 0001 1001                                                          | 19                    | 0101 1001                      | 59  |  |  |  |  |  |  |  |

| 50        | 0011 0010                                                          | 32                    | 0111 0010                      | 72  |  |  |  |  |  |  |  |

| 75        | 0100 1011                                                          | 4B                    | 1000 1011                      | 8B  |  |  |  |  |  |  |  |

| 100       | 0110 0100                                                          | 64                    | 1010 0100                      | A4  |  |  |  |  |  |  |  |

| 125       | 0111 1101                                                          | 7D                    | 1011 1101                      | BD  |  |  |  |  |  |  |  |

| 127       | 0111 1111                                                          | 7F                    | 1011 1111                      | BF  |  |  |  |  |  |  |  |

| 150       | 0111 1111                                                          | 7F                    | 1101 0110                      | D6  |  |  |  |  |  |  |  |

| 175       | 0111 1111                                                          | 7F                    | 1110 1111                      | EF  |  |  |  |  |  |  |  |

| 191       | 0111 1111                                                          | 7F                    | 1111 1111                      | FF  |  |  |  |  |  |  |  |

<sup>(1)</sup> Resolution is 1°C per count. Negative numbers are represented in twos complement format.

<sup>(2)</sup> Resolution is 1°C per count. All values are unsigned with a -64°C offset.

Table 2. Decimal Fraction Temperature Data Format (Local and Remote Temperature Low Bytes)

| TEMP (90) | TEMPERATURE REGISTER LOW BYTE VALUE (0.0625°C R | ESOLUTION) <sup>(1)</sup> |

|-----------|-------------------------------------------------|---------------------------|

| TEMP (°C) | STANDARD AND EXTENDED BINARY                    | HEX                       |

| 0         | 0000 0000                                       | 00                        |

| 0.0625    | 0001 0000                                       | 10                        |

| 0.1250    | 0010 0000                                       | 20                        |

| 0.1875    | 0011 0000                                       | 30                        |

| 0.2500    | 0100 0000                                       | 40                        |

| 0.3125    | 0101 0000                                       | 50                        |

| 0.3750    | 0110 0000                                       | 60                        |

| 0.4375    | 0111 0000                                       | 70                        |

| 0.5000    | 1000 0000                                       | 80                        |

| 0.5625    | 1001 0000                                       | 90                        |

| 0.6250    | 1010 0000                                       | A0                        |

| 0.6875    | 1011 0000                                       | В0                        |

| 0.7500    | 1100 0000                                       | CO                        |

| 0.8125    | 1101 0000                                       | D0                        |

| 0.8750    | 1110 0000                                       | E0                        |

| 0.9375    | 1111 0000                                       | F0                        |

<sup>(1)</sup> Resolution is 0.0625°C per count. All possible values are shown.

#### 8.3.2 Beta Compensation

Previous generations of remote junction temperature sensors were operated by controlling the emitter current of the sensing transistor. However, examination of the physics of a transistor shows that  $V_{BE}$  is actually a function of the collector current. If beta is independent of the collector current, then  $V_{BE}$  can be calculated from the emitter current. In earlier generations of processors that contained PNP transistors connected to these temperature sensors, controlling the emitter current provided acceptable temperature measurement results. At 90-nm process geometry and below, however, the beta factor continues to decrease and the premise that it is independent of collector current becomes less certain.

To manage this increasing temperature measurement error, the TMP43x control the collector current instead of the emitter current. The TMP43x automatically detect and choose the correct range depending on the beta factor of the external transistor. This auto-ranging is performed at the beginning of each temperature conversion in order to correct for any changes in the beta factor as a result of temperature variation. The device can operate a PNP transistor with a beta factor as low as 0.1. See <u>Beta Compensation Configuration Register</u> for further information.

#### 8.3.3 Series Resistance Cancellation

Series resistance in an application circuit that typically results from printed circuit-board (PCB) trace resistance and remote line length is automatically cancelled by the TMP43x, preventing what would otherwise result in a temperature offset. A total of up to  $1\text{-k}\Omega$  of series line resistance is cancelled by the TMP43x if beta correction is disabled and up to 300  $\Omega$  of series line resistance is cancelled if beta correction is enabled, eliminating the need for additional characterization and temperature offset correction. See Figure 7 and Figure 8 for details on the effects of series resistance on sensed remote temperature error.

# 8.3.4 Differential Input Capacitance

The TMP43x can tolerate differential input capacitance of up to 2200 pF with minimal change in temperature error. The effect of capacitance on sensed remote temperature error is illustrated in Figure 9 and Figure 10. See *Filtering* for suggested component values where filtering unwanted coupled signals is needed.

#### 8.3.5 Filtering

Remote junction temperature sensors are usually implemented in noisy environments. Noise is frequently generated by fast digital signals and if not filtered properly can induce errors that corrupt temperature measurements. The TMP43x have a built-in 65-kHz filter on the inputs of DXP and DXN to minimize the effects of noise. However, a differential low-pass filter can help attenuate unwanted coupled signals. Exact component values are application-specific. TI also recommends that the capacitor value remains from 0 pF to 2200 pF with a series resistance less than 1 k $\Omega$ .

#### 8.3.6 Sensor Fault

The TMP43x can sense a fault at the DXP input that results from an incorrect diode connection or an open circuit. The detection circuitry consists of a voltage comparator that trips when the voltage at DXP exceeds (V+) - 0.6 V (typical). The comparator output is continuously checked during a conversion. If a fault is detected, the last valid measured temperature is used for the temperature measurement result, the OPEN bit (Status Register, bit 2) is set high, and, if the alert function is enabled,  $\overline{\text{ALERT}}$  asserts low.

When not using the remote sensor with the TMP43x, the DXP and DXN inputs must be connected together to prevent meaningless fault warnings.

#### 8.3.7 THERM and ALERT/THERM2

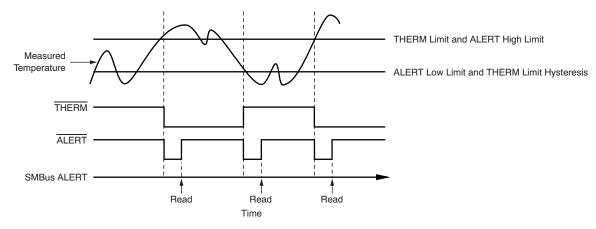

The TMP43x have two pins dedicated to alarm functions, the THERM and ALERT/THERM2 pins. Both pins are open-drain outputs that each require a pullup resistor to V+. These pins can be wire-ORed together with other alarm pins for system monitoring of multiple sensors. The THERM pin provides a thermal interrupt that cannot be software disabled. The ALERT pin is intended for use as an earlier warning interrupt, and can be software disabled, or masked. The ALERT/THERM2 pin can also be configured for use as THERM2, a second THERM pin (Configuration Register 1: AL/TH bit = 1). The default setting configures pin 6 for the TMP431 and pin 8 for the TMP432 to function as ALERT (AL/TH = 0).

The THERM pin asserts low when either the measured local or remote temperature is outside of the temperature range programmed in the corresponding Local/Remote THERM Limit Register. The THERM temperature limit range can be programmed with a wider range than that of the limit registers, which allows  $\overline{ALERT}$  to provide an earlier warning than  $\overline{THERM}$ . The  $\overline{THERM}$  alarm resets automatically when the measured temperature returns to within the THERM temperature limit range minus the hysteresis value stored in the THERM Hysteresis Register. The allowable values of hysteresis are listed in Table 13. The default hysteresis is  $10^{\circ}C$ . When the  $\overline{ALERT/THERM2}$  pin is configured as a second thermal alarm (Configuration Register: bit 7 = x, bit 5 = 1), it functions the same as  $\overline{THERM}$ , but uses the temperatures stored in the Local/Remote Temperature High Limit Registers to set its comparison range.

When ALERT/THERM2 is configured as ALERT (Configuration Register 1: bit 7 = 0, bit 5 = 0), the pin asserts low when either the measured local or remote temperature violates the range limit set by the corresponding Local/Remote Temperature High/Low Limit Registers. This alert function can be configured to assert only if the range is violated a specified number of consecutive times (1, 2, 3, or 4). The consecutive violation limit is set in the Consecutive Alert Register. False alerts that occur as a result of environmental noise can be prevented by requiring consecutive faults. ALERT also asserts low if the remote temperature sensor is open-circuit. When the MASK function is enabled (Configuration Register 1: bit 7 = 1), ALERT is disabled (that is, masked). ALERT resets when the master reads the device address, as long as the condition that caused the alert no longer persists, and the Status Register has been reset.

### 8.4 Device Functional Modes

# 8.4.1 Shutdown Mode (SD)

The TMP43x shutdown mode allows the user to save maximum power by shutting down all device circuitry other than the serial interface, reducing current consumption to typically less than 3  $\mu$ A; see Figure 6. Shutdown mode is enabled when the SD bit of the Configuration Register 1 is high; the device shuts down immediately, aborting the current conversion. When SD is low, the device maintains a continuous conversion state.

### **Device Functional Modes (continued)**

#### 8.4.2 One-Shot Mode

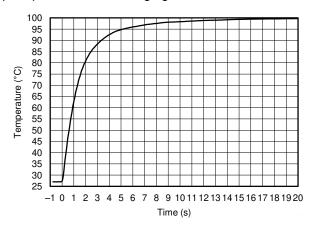

When the TMP43x are in shutdown mode (SD = 1 in the Configuration Register 1), a single conversion on both channels is started by writing any value to the One-Shot Start Register, pointer address 0Fh. This write operation starts one conversion; the TMP43x return to shutdown mode when that conversion completes. The value of the data sent in the write command is irrelevant and is not stored by the TMP43x. When the TMP43x are in shutdown mode, an initial 200 ps is required before a one-shot command can be given. (Note: When a shutdown command is issued, the TMP43x shut down immediately, aborting the current conversion.) This wait time only applies to the 200 ps immediately following shutdown. One-shot commands can be issued without delay thereafter.

### 8.5 Programming

#### 8.5.1 Serial Interface

The TMP43x operate only as slave devices on either the Two-Wire bus or the SMBus. Connections to either bus are made via the open-drain I/O lines, SDA and SCL. The SDA and SCL pins feature integrated spike suppression filters and Schmitt triggers to minimize the effects of input spikes and bus noise. The TMP43x support the transmission protocol for fast (1 kHz to 400 kHz) and high-speed (1 kHz to 2.5 MHz) modes. All data bytes are transmitted MSB first.

#### 8.5.2 Bus Overview

The TMP43x are SMBus interface-compatible. In SMBus protocol, the device that initiates the transfer is called a *master*, and the devices controlled by the master are *slaves*. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions.

To address a specific device, a START condition is initiated. START is indicated by pulling the data line (SDA) from a high to low logic level when SCL is high. All slaves on the bus shift in the slave address byte, with the last bit indicating whether a read or write operation is intended. During the ninth clock pulse, the slave being addressed responds to the master by generating an Acknowledge and pulling SDA low.

Data transfer is then initiated and sent over eight clock pulses followed by an Acknowledge bit. During data transfer SDA must remain stable when SCL is high because any change in SDA when SCL is high is interpreted as a control signal.

When all data are transferred, the master generates a STOP condition. STOP is indicated by pulling SDA from low to high when SCL is high.

# 8.5.3 Timing Diagrams

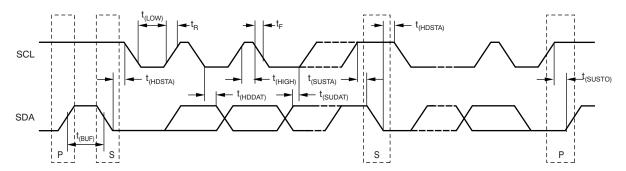

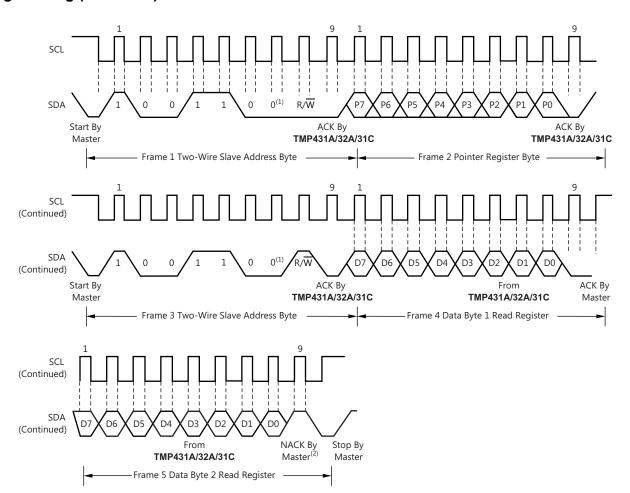

The TMP43x are Two-Wire and SMBus-compatible. Figure 13 to Figure 17 describe the various operations on the TMP43x. Parameters for Figure 13 are defined in Figure 14. Bus definitions are given below:

Bus Idle: Both SDA and SCL lines remain high.

**Start Data Transfer:** A change in the state of the SDA line from high to low when the SCL line is high defines a START condition. Each data transfer is initiated with a START condition.

**Stop Data Transfer:** A change in the state of the SDA line from low to high when the SCL line is high defines a STOP condition. Each data transfer terminates with a STOP or a repeated START condition.

**Data Transfer:** The number of data bytes transferred between a START and a STOP condition is not limited and is determined by the master device. The receiver acknowledges the transfer of data.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an Acknowledge bit. A device that acknowledges must pull down the SDA line during the Acknowledge clock pulse in such a way that the SDA line is stable low during the high period of the Acknowledge clock pulse. Setup and hold times must be taken into account. On a master receive, data transfer termination can be signaled by the master generating a Not-Acknowledge on the last byte that has been transmitted by the slave.

Figure 13. Two-Wire Timing Diagram

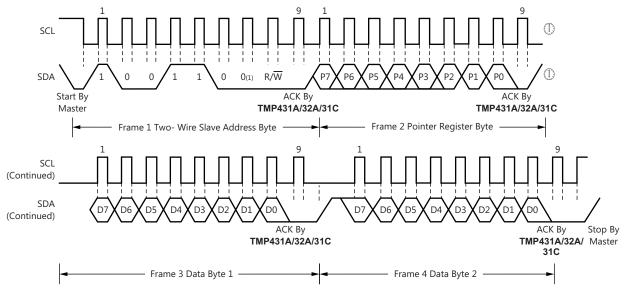

(1) Slave address 1001100 (TMP431A, 32A, and 31C) shown. Slave address changes for TMP431B, 32B, and 31D. See 机械、封装和可订购信息 for more details.

Figure 14. Two-Wire Timing Diagram for Write Word Format

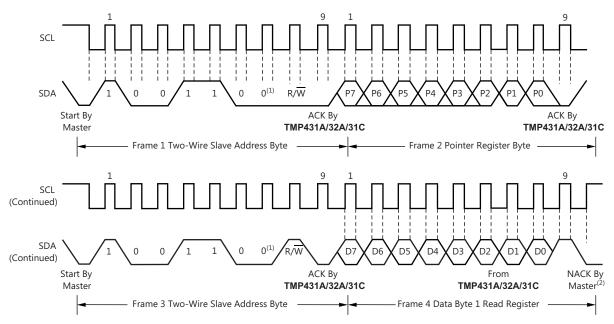

- (1) Slave address 1001100 (TMP431A, 32A, and 31C) shown. Slave address changes for TMP431B, 32B, and 31D. See 机械、封装和可订购信息 for more details.

- (2) Master must leave SDA high to terminate a single-byte read operation.

Figure 15. Two-Wire Timing Diagram for Single-Byte Read Format

- (1) Slave address 1001100 (TMP431A, 32A, and 31C) shown. Slave address changes for TMP431B, 32B, and 31D. See 机械、封装和可订购信息 for more details.

- (2) Master must leave SDA high to terminate a two-byte read operation.

Figure 16. Two-Wire Timing Diagram for Two-Byte Read Format

(1) Slave address 1001100 (TMP431A, 32A, and 31C) shown. Slave address changes for TMP431B, 32B, and 31D. See 机械、封装和可订购信息 for more details.

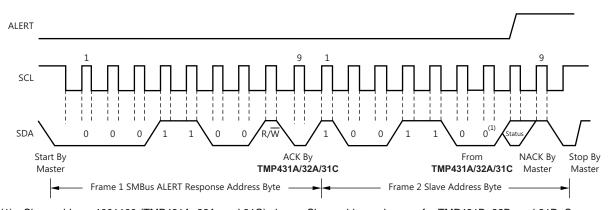

Figure 17. Timing Diagram for SMBus ALERT

#### 8.5.4 Serial Bus Address

To communicate with the TMP43x, the master must first address slave devices via a slave address byte. The slave address byte consists of seven address bits, and a direction bit that indicates the intent of executing a read or write operation.

The address of the TMP431A, 32A, and 31C is 4Ch (1001100b). The address of the TMP431B, 32B, and 31D is 4Dh (1001101b).

### 8.5.5 Read and Write Operations

Accessing a particular register on the TMP43x is accomplished by writing the appropriate value to the Pointer Register. The value for the Pointer Register is the first byte transferred after the slave address byte with the R/W bit low. Every write operation to the TMP43x require a value for the Pointer Register (see Figure 14).

When reading from the TMP43x, the last value stored in the Pointer Register by a write operation is used to determine which register is read by a read operation. To change the register pointer for a read operation, a new value must be written to the Pointer Register. This transaction is accomplished by issuing a slave address byte with the R/W bit low, followed by the Pointer Register byte. No additional data are required. The master can then generate a START condition and send the slave address byte with the R/W bit high to initiate the read command. See Figure 15 for details of this sequence. If repeated reads from the same register are desired, it is not necessary to continually send the Pointer Register bytes, because the TMP43x retain the Pointer Register value until it is changed by the next write operation. Note that register bytes are sent MSB first, followed by the LSB.

#### 8.5.6 Undervoltage Lockout

The TMP43x sense when the power-supply voltage has reached a minimum voltage level for the ADC to function. The detection circuitry consists of a voltage comparator that enables the ADC after the power supply (V+) exceeds 2.45 V (typical). The comparator output is continuously checked during a conversion. The TMP43x do not perform a temperature conversion if the power supply is not valid. The last valid measured temperature is used for the temperature measurement result.

# 8.5.7 Timeout Function

The serial interface of the TMP43x resets if either SCL or SDA are held low for 32 ms (typical) between a START and STOP condition. If the TMP43x are holding the bus low, it releases the bus and waits for a START condition.

### 8.5.8 High-Speed Mode

For the Two-Wire bus to operate at frequencies above 400 kHz, the master device must issue a High-speed mode (Hs-mode) master code (00001XXX) as the first byte after a START condition to switch the bus to high-speed operation. The TMP43x do not acknowledge this byte, but switch the input filters on SDA and SCL and the output filter on SDA to operate in Hs-mode, allowing transfers at up to 2.5 MHz. After the Hs-mode master code has been issued, the master transmits a Two-Wire slave address to initiate a data transfer operation. The bus continues to operate in Hs-mode until a STOP condition occurs on the bus. Upon receiving the STOP condition, the TMP43x switch the input and output filter back to fast-mode operation.

#### 8.5.9 General Call Reset

The TMP43x support reset through the Two-Wire General Call address 00h (0000 0000b). The TMP43x acknowledge the General Call address and respond to the second byte. If the second byte is 06h (0000 0110b), the TMP43x execute a software reset. This software reset restores the power-on reset state to all TMP43x registers, aborts any conversion in progress, and clears the ALERT and THERM pins. The TMP43x take no action in response to other values in the second byte.

### 8.5.10 SMBus Alert Function

The TMP43x support the SMBus Alert function. When pin 6 (for the TMP431) or pin 8 (for the TMP432) is configured as an alert output, the ALERT pin of the TMP43x can be connected as an SMBus Alert signal. When a master detects an alert condition on the ALERT line, the master sends an SMBus Alert command (00011001) on the bus. If the ALERT pin of the TMP43x is active, the devices acknowledge the SMBus Alert command and respond by returning the slave address on the SDA line and release the SMBus alert line after the

acknowledgement of their address. The eighth bit (LSB) of the slave address byte indicates whether the temperature exceeding one of the temperature high limit settings or falling below one of the temperature low limit settings caused the alert condition. This bit is high if the temperature is greater than or equal to one of the temperature high limit settings; this bit is low if the temperature is less than one of the temperature low limit settings. After acknowledging the slave address, the device disengages its ALERT pulldown. The TMP43x disengages the ALERT pulldown by setting the ALERT Mask Bit in the Configuration Register after sending out its address in response to an ARA and releases the ALERT output pin. This command will not clear the previous alert. Once the ALERT Mask bit is activated, the ALERT output pin will be disabled until enabled by software. In order to enable the ALERT, the master must read the ALERT Status Register during the interrupt service routine, and then reset the ALERT Mask bit in the Configuration Register to 0 at the end of the interrupt service. routine. See Figure 18 for details of this sequence.

Figure 18. SMBus Alert Timing Diagram

If multiple devices on the bus respond to the SMBus Alert command, arbitration during the slave address portion of the SMBus Alert command determines which device clears its alert status. If the TMP43x win the arbitration, the ALERT pin becomes inactive at the completion of the SMBus Alert command. If the TMP43x lose the arbitration, the ALERT pin remains active.

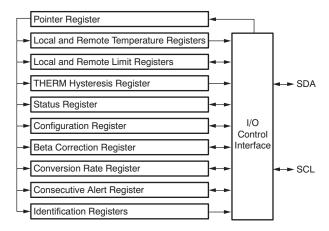

### 8.6 Register Maps

The TMP43x contain multiple registers for holding configuration information, temperature measurement results, temperature comparator maximum, minimum, limits, and status information. These registers are described in Figure 19 and in Table 3 for the TMP431, and in Table 4 for the TMP432.

Figure 19. Internal Register Structure

# **Register Maps (continued)**

# Table 3. TMP431 Register Map

|      | ADDRESS<br>EX)    | POWER-ON          |                  |       |       | BIT DESC | RIPTIONS |       |        |       | REGISTER                                        |

|------|-------------------|-------------------|------------------|-------|-------|----------|----------|-------|--------|-------|-------------------------------------------------|

| READ | WRITE             | RESET (HEX)       | D7               | D6    | D5    | D4       | D3       | D2    | D1     | D0    | DESCRIPTIONS                                    |

| 00   | NA <sup>(1)</sup> | 00                | LT11             | LT10  | LT9   | LT8      | LT7      | LT6   | LT5    | LT4   | Local temperature (high byte)                   |

| 01   | NA                | 00                | RT11             | RT10  | RT9   | RT8      | RT7      | RT6   | RT5    | RT4   | Remote<br>temperature (high<br>byte)            |

| 02   | NA                | 80                | BUSY             | LHIGH | LLOW  | RHIGH    | RLOW     | OPEN  | RTHRM  | LTHRM | Status register                                 |

| 03   | 09                | 00                | MASK             | SD    | AL/TH | 0        | 0        | RANGE | 0      | 0     | Configuration register 1                        |

| 04   | 0A                | 07                | 0                | 0     | 0     | 0        | R3       | R2    | R1     | R0    | Conversion rate register                        |

| 05   | 0B                | 55                | LTH11            | LTH10 | LTH9  | LTH8     | LTH7     | LTH6  | LTH5   | LTH4  | Local temperature<br>high limit (high<br>byte)  |

| 06   | 0C                | 00                | LTL11            | LTL10 | LTL9  | LTL8     | LTL7     | LTL6  | LTL5   | LTL4  | Local temperature low limit (high byte)         |

| 07   | 0D                | 55                | RTH11            | RTH10 | RTH9  | RTH8     | RTH7     | RTH6  | RTH5   | RTH4  | Remote<br>temperature high<br>limit (high byte) |

| 08   | 0E                | 00                | RTL11            | RTL10 | RTL9  | RTL8     | RTL7     | RTL6  | RTL5   | RTL4  | Remote<br>temperature low<br>limit (high byte)  |

| NA   | 0F                | X (2)             | Х                | Х     | Х     | Х        | Х        | Х     | Х      | Х     | One-shot start                                  |

| 10   | NA                | 00                | RT3              | RT2   | RT1   | RT0      | 0        | 0     | 0      | 0     | Remote<br>temperature (low<br>byte)             |

| 13   | 13                | 00                | RTH3             | RTH2  | RTH1  | RTH0     | 0        | 0     | 0      | 0     | Remote<br>temperature high<br>limit (low byte)  |

| 14   | 14                | 00                | RTL3             | RTL2  | RTL1  | RTL0     | 0        | 0     | 0      | 0     | Remote<br>temperature low<br>limit (low byte)   |

| 15   | NA                | 00                | LT3              | LT2   | LT1   | LT0      | 0        | 0     | 0      | 0     | Local temperature (low byte)                    |

| 16   | 16                | 00                | LTH3             | LTH2  | LTH1  | LTH0     | 0        | 0     | 0      | 0     | Local temperature high limit (low byte)         |

| 17   | 17                | 00                | LTL3             | LTL2  | LTL1  | LTL0     | 0        | 0     | 0      | 0     | Local temperature low limit (low byte)          |

| 18   | 18                | 00                | NC7              | NC6   | NC5   | NC4      | NC3      | NC2   | NC1    | NC0   | N-factor correction                             |

| 19   | 19                | 55 <sup>(3)</sup> | RTHL7            | RTHL6 | RTHL5 | RTHL4    | RTHL3    | RTHL2 | RTHL1  | RTHL0 | Remote THERM<br>limit                           |

| 1A   | 1A                | 1C                | 0                | 0     | 0     | REN      | LEN      | RC    | 0      | 0     | Configuration register 2                        |

| 1F   | 1F                | 00                | 0                | 0     | 0     | 0        | 0        | 0     | RIMASK | LMASK | Channel mask                                    |

| 20   | 20                | 55 <sup>(3)</sup> | LTHL7            | LTHL6 | LTHL5 | LTHL4    | LTHL3    | LTHL2 | LTHL1  | LTHL0 | Local THERM limit                               |

| 21   | 21                | 0A                | TH7              | TH6   | TH5   | TH4      | TH3      | TH2   | TH1    | TH0   | THERM hysteresis                                |

| 22   | 22                | 70                | 0                | CTH2  | CTH1  | CTH0     | CALT2    | CALT1 | CALT0  | 0     | Consecutive alert register                      |

| 25   | 25                | 08                | 0                | 0     | 0     | 0        | BC3      | BC2   | BC1    | BC0   | Beta range register                             |

| NA   | FC                | 00                | X <sup>(4)</sup> | Х     | Х     | Х        | Х        | Х     | Х      | Х     | Software reset                                  |

| FD   | NA                | 31                | 0                | 0     | 1     | 1        | 0        | 0     | 0      | 1     | TMP431 device ID                                |

| FE   | NA                | 55                | 0                | 1     | 0     | 1        | 0        | 1     | 0      | 1     | Manufacturer ID                                 |

NA = Not applicable; register is write- or read-only.

X = Indeterminate state.

TMP431C and TMP431D versions have a power-on reset value of 69h.

X = Undefined. Writing any value to this register initiates a software reset; see Software Reset

# Table 4. TMP432 Register Map

| POINTER | ADDRESS           | POWER-ON    |       |       |       | BIT DESC | RIPTIONS |        |        |       | REGISTER                                         |

|---------|-------------------|-------------|-------|-------|-------|----------|----------|--------|--------|-------|--------------------------------------------------|

| READ    | WRITE             | RESET (HEX) | D7    | D6    | D5    | D4       | D3       | D2     | D1     | D0    | DESCRIPTIONS                                     |

| 00      | NA <sup>(1)</sup> | 00          | LT11  | LT10  | LT9   | LT8      | LT7      | LT6    | LT5    | LT4   | Local temperature (high byte)                    |

| 01      | NA                | 00          | RT11  | RT10  | RT9   | RT8      | RT7      | RT6    | RT5    | RT4   | Remote<br>temperature1 (high<br>byte)            |

| 02      | NA                | 80          | BUSY  | 0     | 0     | HIGH     | LOW      | OPEN   | THERM  | 0     | Status register                                  |

| 03      | 09                | 00          | MASK  | SD    | AL/TH | 0        | 0        | RANGE  | 0      | 0     | Configuration register1                          |

| 04      | 0A                | 07          | 0     | 0     | 0     | 0        | R3       | R2     | R1     | R0    | Conversion rate register                         |

| 05      | 0B                | 55          | LTH11 | LTH10 | LTH9  | LTH8     | LTH7     | LTH6   | LTH5   | LTH4  | Local temperature<br>high limit (high<br>byte)   |

| 06      | 0C                | 00          | LTL11 | LTL10 | LTL9  | LTL8     | LTL7     | LTL6   | LTL5   | LTL4  | Local temperature<br>low limit (high byte)       |

| 07      | 0D                | 55          | RTH11 | RTH10 | RTH9  | RTH8     | RTH7     | RTH6   | RTH5   | RTH4  | Remote<br>temperature1 high<br>limit (high byte) |

| 08      | 0E                | 00          | RTL11 | RTL10 | RTL9  | RTL8     | RTL7     | RTL6   | RTL5   | RTL4  | Remote<br>temperature1 low<br>limit (high byte)  |

| NA      | 0F                | X (2)       | X     | Х     | Х     | Х        | Х        | Х      | Х      | Х     | One-shot start                                   |

| 10      | NA                | 00          | RT3   | RT2   | RT1   | RT0      | 0        | 0      | 0      | 0     | Remote<br>temperature1 (low<br>byte)             |

| 13      | 13                | 00          | RTH3  | RTH2  | RTH1  | RTH0     | 0        | 0      | 0      | 0     | Remote<br>temperature1 high<br>limit (low byte)  |

| 14      | 14                | 00          | RTL3  | RTL2  | RTL1  | RTL0     | 0        | 0      | 0      | 0     | Remote<br>temperature1 low<br>limit (low byte)   |

| 15      | 15                | 55          | RTH11 | RTH10 | RTH9  | RTH8     | RTH7     | RTH6   | RTH5   | RTH4  | Remote<br>temperature2 high<br>limit (high byte) |

| 16      | 16                | 00          | RTL11 | RTL10 | RTL9  | RTL8     | RTL7     | RTL6   | RTL5   | RTL4  | Remote<br>temperature2 low<br>limit (high byte)  |

| 17      | 17                | 00          | RTH3  | RTH2  | RTH1  | RTH0     | 0        | 0      | 0      | 0     | Remote<br>temperature2 high<br>limit (low byte)  |

| 18      | 18                | 00          | RTL3  | RTL2  | RTL1  | RTL0     | 0        | 0      | 0      | 0     | Remote<br>temperature2 low<br>limit (low byte)   |

| 19      | 19                | 55          | RTHL7 | RTHL6 | RTHL5 | RTHL4    | RTHL3    | RTHL2  | RTHL1  | RTHL0 | Remote therm limit                               |

| 1A      | 1A                | 55          | RTHL7 | RTHL6 | RTHL5 | RTHL4    | RTHL3    | RTHL2  | RTHL1  | RTHL0 | Remote2 therm<br>limit                           |

| 1B      | 1B                | 00          | 0     | 0     | 0     | 0        | 0        | R2OPEN | R10PEN | 0     | Open status                                      |

| 1F      | 1F                | 00          | 0     | 0     | 0     | 0        | 0        | R2MASK | R1MASK | LMASK | Channel mask                                     |

| 20      | 20                | 55          | LTHL7 | LTHL6 | LTHL5 | LTHL4    | LTHL3    | LTHL2  | LTHL1  | LTHL0 | Local therm limit                                |

| 21      | 21                | 0A          | TH7   | TH6   | TH5   | TH4      | TH3      | TH2    | TH1    | TH0   | Therm limit hysteresis                           |

| 22      | 22                | 70          | 0     | CTH2  | CTH1  | CTH0     | CALT2    | CALT1  | CALT0  | 0     | Consecutive alert register                       |

| 23      | NA                | 00          | RT11  | RT10  | RT9   | RT8      | RT7      | RT6    | RT5    | RT4   | Remote<br>temperature2 (high<br>byte)            |

| 24      | NA                | 00          | RT3   | RT2   | RT1   | RT0      | 0        | 0      | 0      | 0     | Remote<br>temperature2 (low<br>byte)             |

| 25      | 25                | 08          | 0     | 0     | 0     | 0        | BC3      | BC2    | BC1    | BC0   | Ch. 1 beta range selection                       |

| 26      | 26                | 08          | 0     | 0     | 0     | 0        | BC3      | BC2    | BC1    | BC0   | Ch. 2 beta range selection                       |

| 27      | 27                | 00          | NC7   | NC6   | NC5   | NC4      | NC3      | NC2    | NC1    | NC0   | N-factor correction remote1                      |

| 28      | 28                | 00          | NC7   | NC6   | NC5   | NC4      | NC3      | NC2    | NC1    | NC0   | N-factor correction remote2                      |

<sup>(1)</sup> NA = Not applicable; register is write- or read-only.(2) Indeterminate state.

#### Table 4. TMP432 Register Map (continued)

| POINTER | ADDRESS | POWER-ON    |                  |      |      | BIT DESC | RIPTIONS |         |         |        | REGISTER                                |

|---------|---------|-------------|------------------|------|------|----------|----------|---------|---------|--------|-----------------------------------------|

| READ    | WRITE   | RESET (HEX) | D7               | D6   | D5   | D4       | D3       | D2      | D1      | D0     | DESCRIPTIONS                            |

| 29      | NA      | 00          | Т3               | T2   | T1   | T0       | 0        | 0       | 0       | 0      | Local temperature (low byte)            |

| 35      | 35      | 00          | 0                | 0    | 0    | 0        | 0        | R2HIGH  | R1HIGH  | LHIGH  | High limit status                       |

| 36      | 36      | 00          | 0                | 0    | 0    | 0        | 0        | R2LOW   | R1LOW   | LLOW   | Low limit status                        |

| 37      | 37      | 00          | 0                | 0    | 0    | 0        | 0        | R2THERM | R1THERM | LTHERM | Therm status                            |

| 3D      | 3D      | 00          | LTH3             | LTH2 | LTH1 | LTH0     | 0        | 0       | 0       | 0      | Local temperature high limit (low byte) |

| 3E      | 3E      | 00          | LTL3             | LTL2 | LTL1 | LTL0     | 0        | 0       | 0       | 0      | Local temperature low limit (low byte)  |

| 3F      | 3F      | 3C          | 0                | 0    | REN2 | REN      | LEN      | RC      | 0       | 0      | Configuration register2                 |

| NA      | FC      | 00          | X <sup>(3)</sup> | Х    | Х    | Х        | Х        | Х       | Х       | Х      | Software reset                          |

| FD      | NA      | 32          | 0                | 0    | 1    | 1        | 0        | 0       | 1       | 0      | TMP432 device ID                        |

| FE      | NA      | 55          | 0                | 1    | 0    | 1        | 0        | 1       | 0       | 1      | Manufacturer ID                         |

<sup>(3)</sup> X = Undefined. Writing any value to this register initiates a software reset; see Software Reset.

### 8.6.1 Pointer Register

Figure 19 illustrates the internal register structure of the TMP43x. The 8-bit Pointer Register is used to address a given data register. The Pointer Register identifies which of the data registers must respond to a read or write command on the Two-Wire bus. This register is set with every write command. A write command must be issued to set the proper value in the Pointer Register before executing a read command. Table 3 describes the pointer address of the registers available in the TMP431. Table 4 describes the address of the registers available in the TMP432. The power-on reset (POR) value of the Pointer Register is 00h (0000 0000b).

#### 8.6.2 Temperature Registers

The TMP431 has four 8-bit registers that hold temperature measurement results. The TMP432 has six 8-bit registers that hold temperature measurement results. Both the local channel and the remote channel have a high byte register that contains the most significant bits (MSBs) of the temperature analog-to-digital converter (ADC) result and a low byte register that contains the least significant bits (LSBs) of the temperature ADC result. The local channel high byte address for the TMP43x is 00h; the local channel low byte address is 15h for the TMP431 and 29h for the TMP432. The remote channel high byte is at address 01h; the remote channel low byte address is 10h. For the TMP432, the second remote channel high byte address is 23h; the second remote channel low byte is 24h. These registers are read-only and are updated by the ADC each time a temperature measurement is completed.

The TMP43x contain circuitry to assure that a low byte register read command returns data from the same ADC conversion as the immediately preceding high byte read command. This assurance remains valid only until another register is read. For proper operation, the high byte of a temperature register must be read first. The low byte register must be read in the next read command. The low byte register can be left unread if the LSBs are not needed. Alternatively, the temperature registers can be read as a 16-bit register by using a single two-byte read command from address 00h for the local channel result, or from address 01h for the remote channel result (23h for the second remote channel result). The high byte is output first, followed by the low byte. Both bytes of this read operation are from the same ADC conversion. The power-on reset value of both temperature registers is 00h.

## 8.6.3 Limit Registers

The TMP43x have registers for setting comparator limits for both the local and remote measurement channels. These registers have read and write capability. The High and Low Limit Registers for both channels span two registers, as do the temperature registers. These registers are only compared to at the end of every conversion cycle, and not immediately after updating the register value. The local temperature high limit is set by writing the high byte to pointer address 0Bh and writing the low byte to pointer address 16h for the TMP431 and 3Dh for the TMP432, or by using a single two-byte write command (high byte first) to pointer address 0Bh.

The local temperature high limit is obtained by reading the high byte from pointer address 05h and the low byte from pointer address 16h for the TMP4341 and 3Dh for the TMP432, or by using a two-byte read command from pointer address 05h. The power-on reset value of the local temperature high limit is 55h, 00h (85°C in standard temperature mode; 21°C in extended temperature mode).

Similarly, the local temperature low limit is set by writing the high byte to pointer address 0Ch and writing the low byte to pointer address 17h for the TMP431 and 3Eh for the TMP432, or by using a single two-byte write command to pointer address 0Ch. The local temperature low limit is read by reading the high byte from pointer address 06h and the low byte from pointer address 17h and 3Eh for the TMP432, or by using a two-byte read from pointer address 06h. The power-on reset value of the local temperature low limit register is 00h, 00h (0°C in standard temperature mode; –64°C in extended mode).

The remote temperature high limit for the TMP431 (remote temperature1 high limit for the TMP432) is set by writing the high byte to pointer address 0Dh and writing the low byte to pointer address 13h, or by using a two-byte write command to pointer address 0Dh. The remote temperature high limit is obtained by reading the high byte from pointer address 07h and the low byte from pointer address 13h, or by using a two-byte read command from pointer address 07h. The power-on reset value of the Remote Temperature High Limit Register is 55h, 00h (85°C in standard temperature mode; 21°C in extended temperature mode).

The remote temperature low limit for the TMP431 (remote temperature1 low limit for the TMP432) is set by writing the high byte to pointer address 0Eh and writing the low byte to pointer address 14h, or by using a two-byte write to pointer address 0Eh. The remote temperature low limit is read by reading the high byte from pointer address 08h and the low byte from pointer address 14h, or by using a two-byte read from pointer address 08h. The power-on reset value of the Remote Temperature Low Limit Register is 00h, 00h (0°C in standard temperature mode; –64°C in extended mode).