## 4-TO-2 DVI/HDMI SWITCH

#### **FEATURES**

- A 4-to-2 Single-Link or 2-to-1 Dual-Link DVI/HDMI Physical Layer Switch

- Compatible with HDMI 1.3a

- Supports 2.25 Gbps Signaling Rate for 480i/p, 720i/p, and 1080i/p Resolutions up to 12-Bit Color Depth

- Integrated Receiver Terminations

- 8-dB Receiver Equalizer Compensates for Losses From Standard HDMI Cables

- Selectable Output De-Emphasis Compensates for Losses From Flat Cables

- High-Impedance Outputs When Disabled

- I<sup>2</sup>C Repeater Isolates Bus Capacitance at Both Ends

- TMDS Inputs HBM ESD Protection Exceeds 6 kV

- 3.3-V Supply Operation

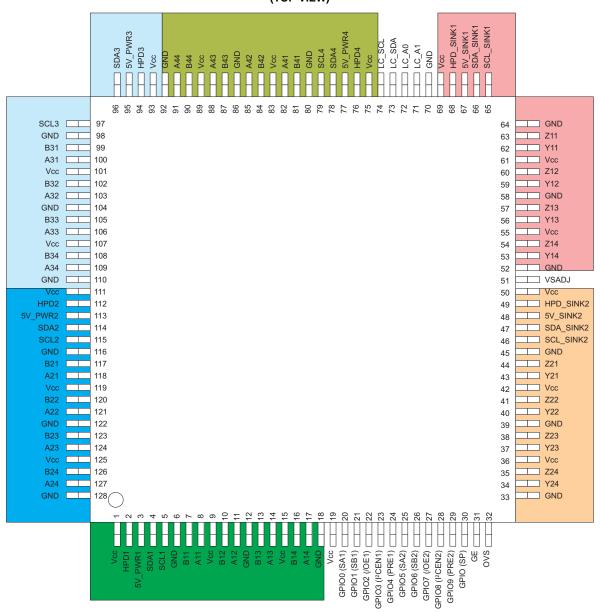

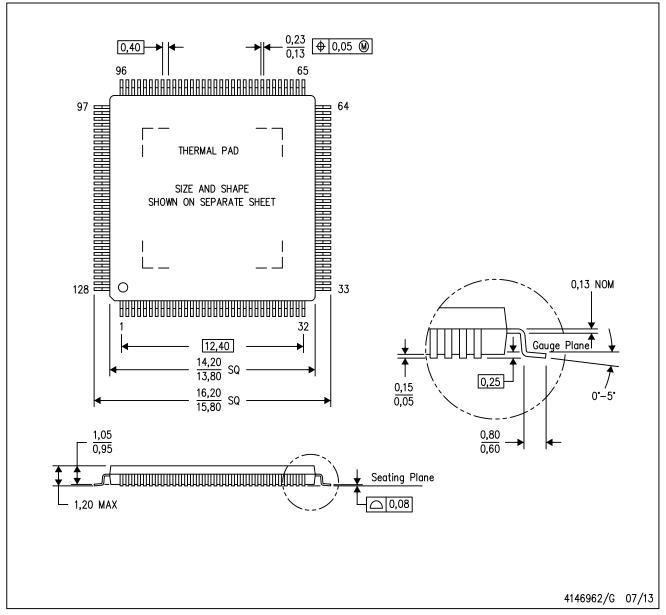

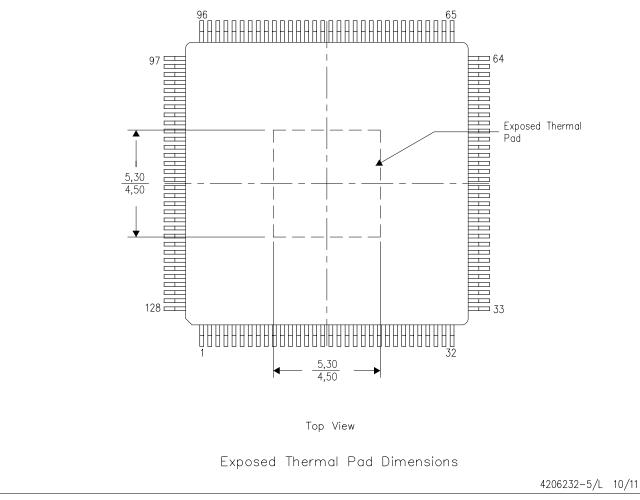

- 128-Pin TQFP Package

- ROHS Compatible and 260°C Reflow Rated

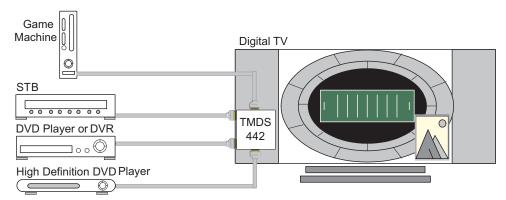

#### **APPLICATIONS**

- Digital TV

- Digital Projector

- Audio Video Receiver

- DVI or HDMI Switch

#### DESCRIPTION

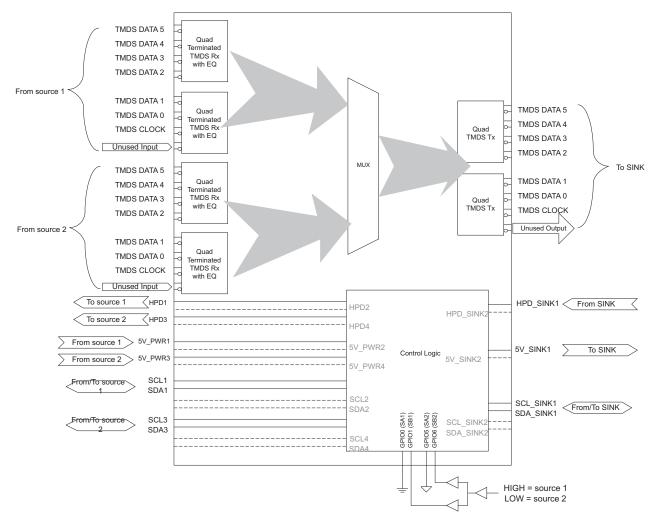

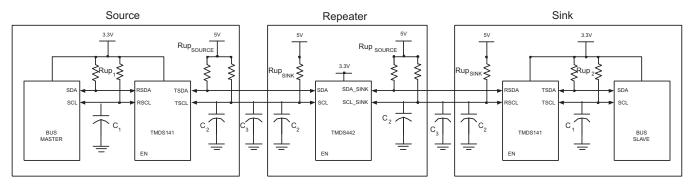

The TMDS442, 4-to-2 port DVI/HDMI switch, allows up to 4 digital video interface (DVI) or high-definition multimedia interface (HDMI) ports to be switched to two independent display blocks. The essential requirement of picture-in-picture display from two digital audiovisual sources is having two individual DVI or HDMI receivers in a digital display system. TMDS442 supports two DVI or HDMI receivers to enable multiple-source selection (picture-in-picture), as well as supports acting as a 4-input 1-output video switch.

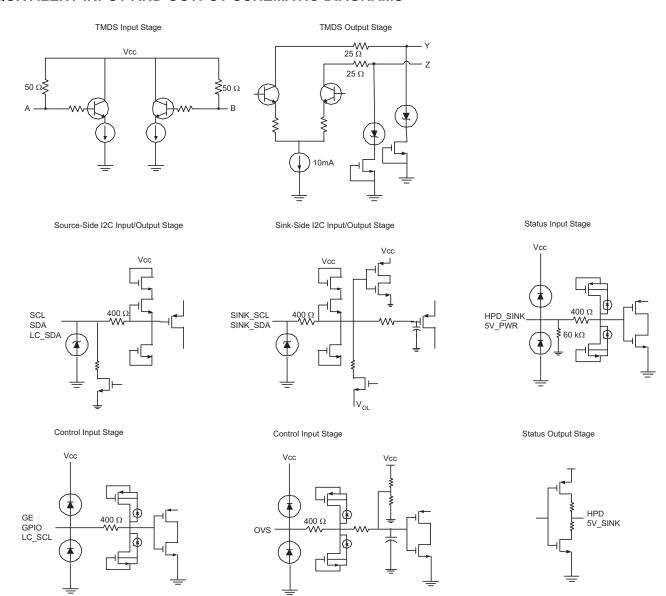

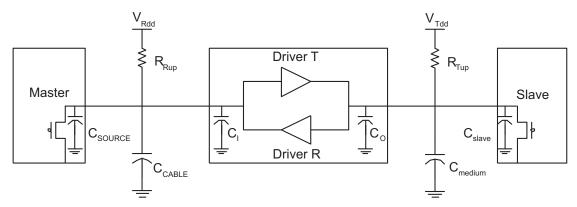

Each input or output port contains one 5-V power indicator (5V\_PWR), one hot plug detector (HPD), a pair of  $I^2C$  interface signals (SCL/SDA), and four TMDS channels supporting data rates up to 2.25 Gbps. The 5-V power indicator and the hot plug detector are pulled down with internal resistors, forcing a low state on these pins until receiving a valid high signal. The  $I^2C$  interface is constructed by an  $I^2C$  repeater circuit to isolate the capacitance form both ends of the buses. TMDS receivers integrate  $50-\Omega$  termination resistors pulled up to  $V_{CC}$ , which eliminates the need for external terminations. An 8-dB input equalization cooperates to each TMDS receiver inputs to optimize system performance through 5-meter or longer DVI or HDMI compliant cables.

#### TYPICAL APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

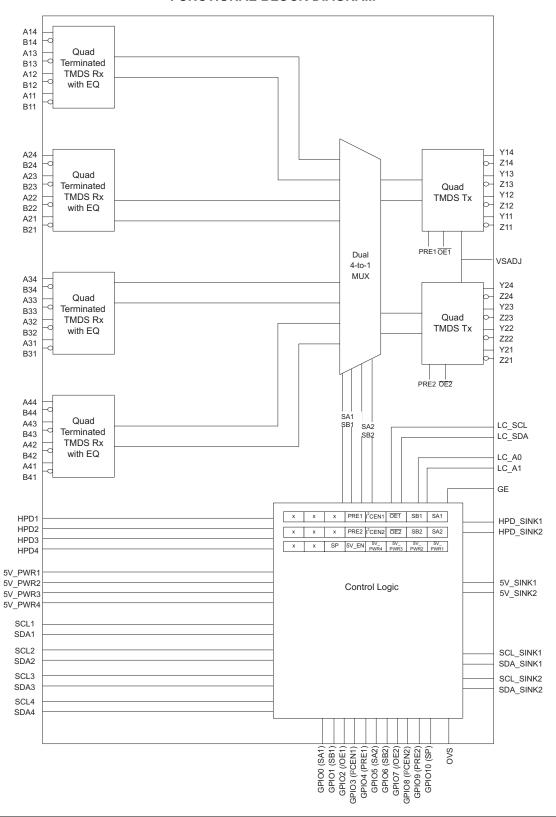

A precision resistor is connected externally from the VSADJ pin to ground, for setting the differential output voltage to be compliant with the TMDS standard for all TMDS driver outputs. The PRE pin controls the TMDS output to be operated under either a standard TMDS mode or an AC de-emphasis mode. When PRE = high, a 3-dB AC de-emphasis TMDS output swing is selected to pre-condition the output signals to overcome signal impairments that may exist between the output of the TMDS442 and the HDMI receiver placed at a remote location.

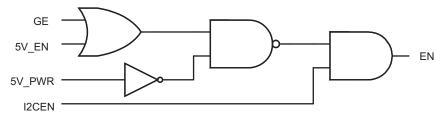

Each sink output port can be configured with the SA, SB,  $\overline{OE}$ , I2CEN, and PRE pins. SA1, SB1,  $\overline{OE1}$ , I2CEN1, and PRE1 regulate the behaviour of sink port 1; SA2, SB2,  $\overline{OE2}$ , I2CEN2, and PRE2 regulate the behaviour of sink port 2. These control signals are hard-wire controlled by GPIO interface, or through a local I<sup>2</sup>C interface. When GE = low, the configurations are done through a local I<sup>2</sup>C interface, LC\_SCL, LC\_SDA, LC\_A0, and LC\_A1 pins, and the 5V\_EN can be programmed through the local I<sup>2</sup>C interface. It is default high after device powered on. When GE = high, the configurations are done through GPIO pins regardless the value of the 5V\_EN in the internal I<sup>2</sup>C registers.

The two bit source selector pins, SA and SB, determine the source transferred to the sink port. The internal multiplexer interconnects the TMDS channels and I<sup>2</sup>C interface from the selected source port to the sink port. The HPD output of the selected source port follows the status of the HPD\_SINK. Since two of the source ports will always be unconnected to any output, the I<sup>2</sup>C interfaces of unselected ports are isolated and the HPD outputs of an unselected port are pulled low.

The TMDS outputs of each of the sink ports are enabled based on the  $\overline{OE}$  signal and 5V\_PWR signal (from the selected source port). When  $\overline{OE}$  is low, for an output port, and the 5V\_PWR signal from the selected source port is high, the TMDS output signals are enabled; otherwise they are disabled, and high impedance.

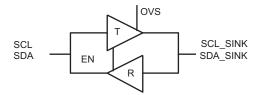

The I<sup>2</sup>C driver at sink side, SCL\_SINK and SDA\_SINK, are enabled by setting I2CEN high. When I2CEN is low, the I<sup>2</sup>C driver can not forward a low state to the I<sup>2</sup>C bus connected at the sink port. A hard wire output voltage select pin, OVS, allows adjustable output voltage level to SCL\_SINK and SDA\_SINK to optimise noise margins while interfacing to different HDMI receivers. The I<sup>2</sup>C driver of each source port, SCL and SDA, is controlled by its 5V\_PWR signal. A valid 5-V signal appearing at the input of 5V\_PWR enables the I<sup>2</sup>C driver of the source port.

The device is packaged in a 128-pin PowerPAD TQFP package and characterized for operation from 0°C to 70°C.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **FUNCTIONAL BLOCK DIAGRAM**

#### PNP PACKAGE (TOP VIEW)

#### **TERMINAL FUNCTIONS**

| TERMI                                                                                | NAL                                                                               | 1/0 | DESCRIPTION                                                                                                                                          |  |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                                                                                 | NO.                                                                               | I/O | DESCRIPTION                                                                                                                                          |  |

| A11, A12, A13, A14<br>A21, A22, A23, A24<br>A31, A32, A33, A34<br>A41, A42, A43, A44 | 8, 11, 14, 17<br>118, 121, 124,<br>127<br>100, 103, 106,<br>109<br>82, 85, 88, 91 | I   | Source port 1 TMDS positive inputs<br>Source port 2 TMDS positive inputs<br>Source port 3 TMDS positive inputs<br>Source port 4 TMDS positive inputs |  |

| B11, B12, B13, B14<br>B21, B22, B23, B24<br>B31, B32, B33, B34<br>B41, B42, B43, B44 | 7, 10, 13, 16<br>117, 120, 123,<br>126<br>99, 102, 105, 108<br>81, 84, 87, 90     | I   | Source port 1 TMDS negative inputs<br>Source port 2 TMDS negative inputs<br>Source port 3 TMDS negative inputs<br>Source port 4 TMDS negative inputs |  |

# **TERMINAL FUNCTIONS (continued)**

| TERMIN                                               | IAL                                                                                      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                     |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                                                 | NO.                                                                                      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                     |  |

| Y11, Y12, Y13, Y14<br>Y21, Y22, Y23, Y24             | 62, 59, 56, 53<br>43, 40, 37, 34                                                         | 0   | Sink port 1 TMDS positive outputs Sink port 2 TMDS positive outputs                                                                                                                                                                                                                             |  |

| Z11, Z12, Z13, Z14<br>Z21, Z22, Z23, Z24             | 63, 60, 57, 54<br>44, 41, 38, 35                                                         | 0   | Sink port 1 TMDS negative outputs Sink port 2 TMDS negative outputs                                                                                                                                                                                                                             |  |

| SCL1<br>SDA1                                         | 54                                                                                       | Ю   | Source Port 1 DDC I <sup>2</sup> C clock line<br>Source Port 1 DDC I <sup>2</sup> C data line                                                                                                                                                                                                   |  |

| SCL2<br>SDA2                                         | 115<br>114                                                                               | Ю   | Source Port 2 DDC I <sup>2</sup> C clock line<br>Source Port 2 DDC I <sup>2</sup> C data line                                                                                                                                                                                                   |  |

| SCL3<br>SDA3                                         | 97<br>96                                                                                 | Ю   | Source Port 3 DDC I <sup>2</sup> C clock line<br>Source Port 3 DDC I <sup>2</sup> C data line                                                                                                                                                                                                   |  |

| SCL4<br>SDA4                                         | 79<br>78                                                                                 | Ю   | Source Port 4 DDC I <sup>2</sup> C clock line<br>Source Port 4 DDC I <sup>2</sup> C data line                                                                                                                                                                                                   |  |

| SCL_SINK1<br>SDA_SINK1                               | 65<br>66                                                                                 | Ю   | Sink port 1 DDC I <sup>2</sup> C clock line<br>Sink port 1 DDC I <sup>2</sup> C data line                                                                                                                                                                                                       |  |

| SCL_SINK2<br>SDA_SINK2                               | 46<br>47                                                                                 | Ю   | Sink port 2 DDC I <sup>2</sup> C clock line<br>Sink port 2 DDC I <sup>2</sup> C data line                                                                                                                                                                                                       |  |

| HPD1<br>HPD2<br>HPD3<br>HPD4                         | 2<br>112<br>94<br>76                                                                     | 0   | Source Port 1 hot plug detector output Source Port 2 hot plug detector output Source Port 3 hot plug detector output Source Port 4 hot plug detector output                                                                                                                                     |  |

| HPD_SINK1<br>HPD_SINK2                               | 68<br>49                                                                                 | I   | Sink port 1 hot plug detector input<br>Sink port 2 hot plug detector input                                                                                                                                                                                                                      |  |

| 5V_PWR1<br>5V_PWR 2<br>5V_PWR 3<br>5V_PWR 4          | 3<br>113<br>95<br>77                                                                     | I   | Source Port 1 5-V power signal input<br>Source Port 2 5-V power signal input<br>Source Port 3 5-V power signal input<br>Source Port 4 5-V power signal input                                                                                                                                    |  |

| 5V_SINK1<br>5V_SINK 2                                | 67<br>48                                                                                 | 0   | Sink Port 1 5-V power indicator output<br>Sink Port 2 5-V power indicator output                                                                                                                                                                                                                |  |

| LC_SCL<br>LC_SDA                                     | 74<br>73                                                                                 | Ю   | Local I <sup>2</sup> C clock line<br>Local I <sup>2</sup> C data line                                                                                                                                                                                                                           |  |

| LC_A0<br>LC_A1                                       | 72<br>71                                                                                 | 1   | Local I <sup>2</sup> C address bit 0<br>Local I <sup>2</sup> C address bit 1                                                                                                                                                                                                                    |  |

| GE                                                   | 31                                                                                       | I   | GPIO Enable L: Local I <sup>2</sup> C pins are active, GPIO pins are high impedance H: GPIO pins are active, local I <sup>2</sup> C pins are high impedance                                                                                                                                     |  |

| GPIO0<br>GPIO1<br>GPIO2<br>GPIO3<br>GPIO4            | 20<br>21<br>22<br>23<br>24                                                               | I   | SA1 – Sink port 1 source selector  SB1 – Sink port 1 source selector  OE1 – Sink port 1 TMDS output enable  I2CEN1 – Sink port 1 DDC I <sup>2</sup> C output enable  PRE1 – Sink port 1 TMDS AC de-emphasis mode selector                                                                       |  |

| GPIO5<br>GPIO6<br>GPIO7<br>GPIO8<br>GPIO10<br>GPIO11 | 25<br>26<br>27<br>28<br>29<br>30<br>32                                                   | I   | SA2 – Sink port 2 source selector SB2 – Sink port 2 source selector OE2 – Sink port 2 TMDS output enable I2CEN2 – Sink port 2 DDC I <sup>2</sup> C output enable PRE2 – Sink port 2 TMDS AC de-emphasis mode selector SP – Sink priority selector OVS – SCL_SINK/SDA_SINK output voltage select |  |

| VSADJ                                                | 51                                                                                       | ļ   | TMDS compliant voltage swing control                                                                                                                                                                                                                                                            |  |

| Vcc                                                  | 1, 9, 15, 19 36,<br>42, 50, 55, 61 69,<br>75, 83, 89, 93<br>101, 107, 111,<br>119, 125   |     | Power supply                                                                                                                                                                                                                                                                                    |  |

| GND                                                  | 6, 12, 18, 33, 39,<br>45, 52, 58, 64 70,<br>80, 86, 92 98,<br>104, 110, 116,<br>122, 128 |     | Ground                                                                                                                                                                                                                                                                                          |  |

## **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

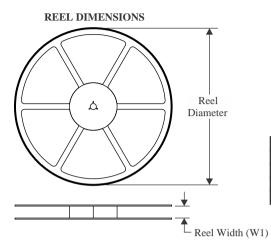

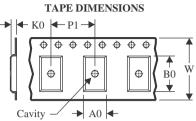

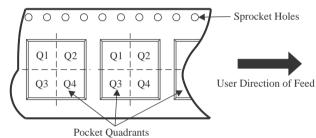

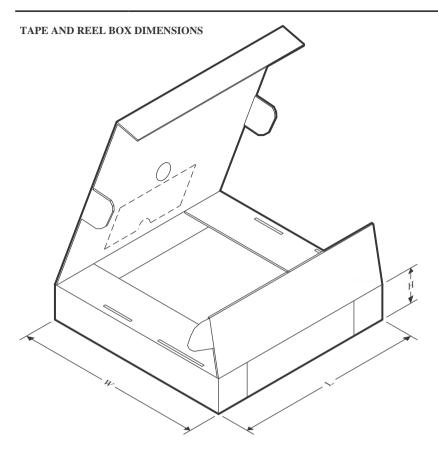

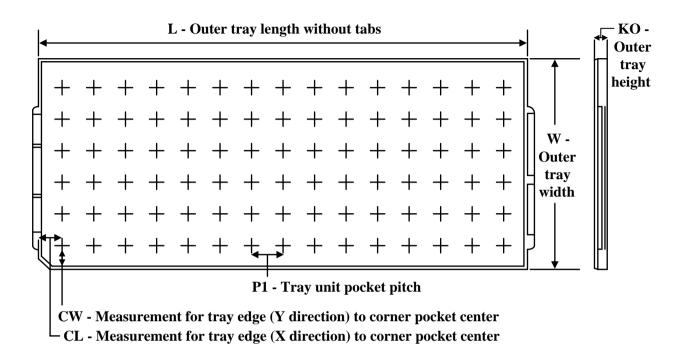

## ORDERING INFORMATION(1)

| PART NUMBER | PART MARKING | PACKAGE                |

|-------------|--------------|------------------------|

| TMDS442PNP  | TMDS442      | 128-PIN TQPF           |

| TMDS442PNPR | TMDS442      | 128-PIN TQPF Tape/Reel |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                                                                                                                                                                                                                                                                                 |                                                      |               |  | UNIT          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------|--|---------------|

| CC Supply voltage range (2)  Voltage range Aim*, Bim  Yjm, Zjm, , Vsadjj, HPDi, 5V_SINKj, LC_SCL, LC_SDA, LC_A0, LC_A1, GE, GPIO  SCLi, SCL_SINKj, SDAi, SDA_SINKj, HPD_SINKj, 5V_PWRi  Human body model (3)  Charged-device model (4) (all pins)  Machine model (5) (all pins) |                                                      | –0.5 V to 4 V |  |               |

|                                                                                                                                                                                                                                                                                 | Aim*, Bim                                            |               |  | 2.5 V to 4 V  |

| Voltage range                                                                                                                                                                                                                                                                   | Yjm, Zjm, , Vsadjj, HPDi, 5V_SINKj, L0               | -0.5V to 4 V  |  |               |

|                                                                                                                                                                                                                                                                                 | SCLi, SCL_SINKj, SDAi, SDA_SINKj, HPD_SINKj, 5V_PWRi |               |  | –0.5 V to 6 V |

|                                                                                                                                                                                                                                                                                 | Human body modal <sup>(3)</sup>                      | Aim, Bim      |  | ±6 kV         |

| Electrostatio discharge                                                                                                                                                                                                                                                         | Truman body moder                                    | All pins      |  | ±5 kV         |

| Electrostatic discharge                                                                                                                                                                                                                                                         | Charged-device model (4) (all pins)                  | ±1500 V       |  |               |

|                                                                                                                                                                                                                                                                                 | Machine model <sup>(5)</sup> (all pins)              |               |  | ±200 V        |

| Continuous power dissipa                                                                                                                                                                                                                                                        | Continuous power dissipation                         |               |  |               |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

- Tested in accordance with JEDEC Standard 22, Test Method A114-B Tested in accordance with JEDEC Standard 22, Test Method C101-A

- Tested in accordance with JEDEC Standard 22, Test Method A115-A

#### **DISSIPATION RATINGS**

| PACKAGE      | PACKAGE PCB JEDEC STANDARD T <sub>A</sub> ≤ 25°C |            | DERATING FACTOR $^{(1)}$<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |  |

|--------------|--------------------------------------------------|------------|---------------------------------------------------------|---------------------------------------|--|

| 128-TQFP PNP | Low-K <sup>(2)</sup>                             | 2129.47 mW | 21.2947 mW/°C                                           | 1171.20 mW                            |  |

| 128-TQFP PNP | High-K <sup>(3)</sup>                            | 4308.48 mW | 43.0848 mW/°C                                           | 2369.66 mW                            |  |

- This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

- In accordance with the Low-K thermal metric definitions of EIA/JESD51-3

- In accordance with the High-K thermal metric definitions of EIA/JESD51-7

## THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                | PARAMETER                            | TEST CONDITIONS                                                                                                                                                                                                                                                                  | MIN | TYP  | MAX  | UNIT |

|----------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| $R_{\thetaJB}$ | Junction-to-board thermal resistance |                                                                                                                                                                                                                                                                                  |     | 7.86 |      | °C/W |

| $R_{\thetaJC}$ | Junction- to-case thermal resistance |                                                                                                                                                                                                                                                                                  |     | 19.5 |      | °C/W |

| $P_D$          | Device power dissipation             | $\begin{array}{l} V_{IH}=V_{CC},V_{IL}=V_{CC}\text{ - }0.6\text{ V},R_{T}=50\Omega,AV_{CC}=3.3\text{ V},\\ V_{CC}=3.6\text{ V},R_{VSADJ}=4.6\text{ k}\Omega,PRE=Low\text{ or high}\\ Ai/Bi(2:4)=1.65\text{ Gbps HDMI data pattern},\\ Ai/Bi(1)=165\text{ MHz clock} \end{array}$ |     |      | 1431 | mW   |

## RECOMMENDED OPERATING CONDITIONS

|                    |                                                  | MIN                  | NOM  | MAX                 | UNIT  |

|--------------------|--------------------------------------------------|----------------------|------|---------------------|-------|

| V <sub>CC</sub>    | Supply voltage                                   | 3                    | 3.3  | 3.6                 | V     |

| T <sub>A</sub>     | Operating free-air temperature                   | 0                    |      | 70                  | °C    |

| TMDS DI            | FFERENTIAL PINS (A/B)                            |                      |      |                     |       |

| V <sub>IC</sub>    | Input common mode voltage                        | V <sub>CC</sub> -400 |      | V <sub>CC</sub> +10 | mV    |

| $V_{\text{ID}}$    | Receiver peak-to-peak differential input voltage | 150                  |      | 1560                | mVp-p |

| R <sub>VSADJ</sub> | Resistor for TMDS compliant voltage swing range  | 4.6                  | 4.64 | 4.68                | kΩ    |

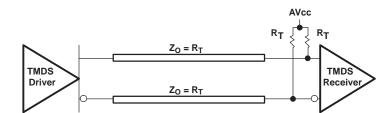

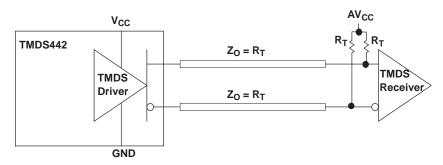

| AV <sub>CC</sub>   | TMDS Output termination voltage, see Figure 3    | 3                    | 3.3  | 3.6                 | V     |

| R <sub>T</sub>     | Termination resistance, see Figure 3             | 45                   | 50   | 55                  | Ω     |

|                    | Signaling rate                                   | 0                    |      | 2.25                | Gbps  |

| CONTRO             | L PINS (LC_A0, LC_A1, GE, GPIO)                  | 1                    |      |                     |       |

| V <sub>IH</sub>    | LVTTL High-level input voltage                   | 2                    |      | $V_{CC}$            | V     |

Copyright © 2006-2007, Texas Instruments Incorporated

**RECOMMENDED OPERATING CONDITIONS (continued)**

|                 |                                        | MIN                | NOM MAX            | UNIT |

|-----------------|----------------------------------------|--------------------|--------------------|------|

| $V_{IL}$        | LVTTL Low-level input voltage          | GND                | 0.8                | V    |

| CONTR           | OL PINS (OVS)                          |                    |                    |      |

| $V_{IH}$        | LVTTL High-level input voltage         | 3                  | 3.6                | V    |

| V <sub>IL</sub> | LVTTL Low-level input voltage          | -0.5               | 0.5                | V    |

| STATU           | S PINS (HPD_SINK, 5V_PWR)              |                    |                    |      |

| V <sub>IH</sub> | High-level input voltage               | 2                  | 5.3                | V    |

| V <sub>IL</sub> | Low-level input voltage                | GND                | 0.8                | V    |

| DDC I/C         | PINS (SCL_SINK, SDA_SINK)              |                    | ·                  |      |

| V <sub>IH</sub> | High-level input voltage               | 0.7V <sub>CC</sub> | 5.5                | V    |

| $V_{IL}$        | Low-level input voltage                | -0.5               | 0.3V <sub>CC</sub> | V    |

| $V_{ILC}$       | Low-level input voltage contention (1) | -0.5               | 0.4                | V    |

| DDC I/C         | PINS (SCL, SDA)                        |                    |                    |      |

| V <sub>IH</sub> | High-level input voltage               | 2.1                | 5.5                | V    |

| $V_{IL}$        | Low-level input voltage                | -0.5               | 1.5                | V    |

| LOCAL           | I <sup>2</sup> C PINS (LC_SCL, LC_SDA) | •                  | 1                  |      |

| $V_{IH}$        | High-level input voltage               | 0.7V <sub>CC</sub> | V <sub>CC</sub>    | V    |

| V <sub>IL</sub> | Low-level input voltage                | -0.5               | 0.3V <sub>CC</sub> | V    |

<sup>(1)</sup>  $V_{IL}$  specification is for the first low level seen by the SCL\_SINK/SDA\_SINK lines.  $V_{ILC}$  is for the second and subsequent low levels seen by the SCL\_SINK/SDA\_SINK lines.

## **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                              | TEST COND                                                                                                                                                                                          | ITIONS             | MIN                                        | TYP <sup>(1)</sup> | MAX                   | UNIT                  |

|----------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------|--------------------|-----------------------|-----------------------|

| Icc                  | Supply current                                                         | $V_{IH} = V_{CC}, V_{IL} = V_{CC} - 0.$<br>$AV_{CC} = 3.3 \text{ V},$<br>Ai/Bi(2:4) = 1.65-Gbps H<br>Ai/Bi(1) = 165-MHz Pixe                                                                       | IDMI data pattern, |                                            | 250                | 412 <sup>(2)</sup>    | mA                    |

| P <sub>D</sub>       | Power dissipation                                                      | $\begin{array}{l} V_{IH}=V_{CC},V_{IL}=V_{CC}-0.4\text{V},R_T=50\Omega,\\ AV_{CC}=3.3\text{V},\\ Ai/Bi(2:4)=1.65\text{-Gbps HDMI data pattern},\\ Ai/Bi(1)=165\text{-MHz Pixel clock} \end{array}$ |                    |                                            | 640                | 1344 <sup>(2)</sup>   | mW                    |

| TMDS DIFF            | ERENTIAL PINS (A/B, Y/Z)                                               |                                                                                                                                                                                                    |                    |                                            |                    |                       |                       |

| V <sub>OH</sub>      | Single-ended high-level output voltage                                 |                                                                                                                                                                                                    |                    | AV <sub>CC</sub> -10                       |                    | AV <sub>CC</sub> +10  | mV                    |

| V <sub>OL</sub>      | Single-ended low-level output voltage                                  |                                                                                                                                                                                                    |                    | AV <sub>CC</sub> -600 AV <sub>CC</sub> -40 |                    | AV <sub>CC</sub> -400 | mV                    |

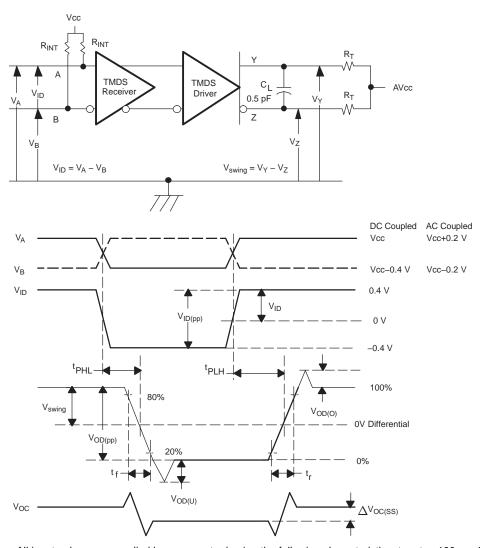

| V <sub>swing</sub>   | Single-ended output swing voltage                                      | See Figure 4, AV <sub>CC</sub> = 3.                                                                                                                                                                | 2.1/               | 400 600                                    |                    | 600                   | mV                    |

| V <sub>OD(O)</sub>   | Overshoot of output differential voltage                               | R <sub>T</sub> = 50 $\Omega$                                                                                                                                                                       | 3 V,               | 15%                                        |                    | 15%                   | 2× V <sub>swing</sub> |

| V <sub>OD(U)</sub>   | Undershoot of output differential voltage                              |                                                                                                                                                                                                    |                    |                                            |                    | 25%                   | $2 \times V_{swing}$  |

| $\Delta V_{OC(SS)}$  | Change in steady-state common-mode output voltage between logic states |                                                                                                                                                                                                    |                    |                                            |                    | 5                     | mV                    |

| I <sub>(O)OFF</sub>  | Single-ended standby output current                                    | $0 \text{ V} \le \text{V}_{CC} \le 1.5 \text{ V},$<br>$A\text{V}_{CC} = 3.3 \text{ V}, R_T = 50 \text{ C}$                                                                                         | Ω                  | -10                                        |                    | 10                    | μΑ                    |

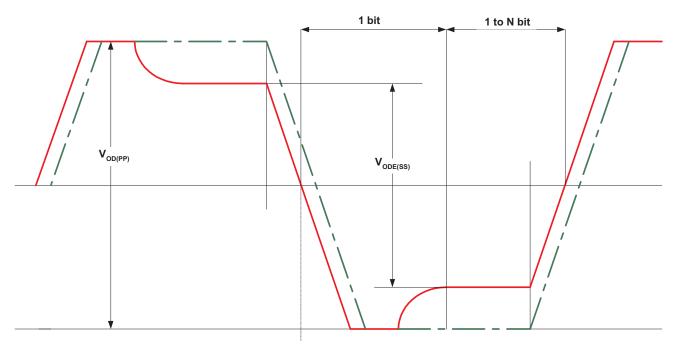

| V <sub>OD(pp)</sub>  | Peak-to-peak output differential voltage                               | See Figure 5, PRE = Hid                                                                                                                                                                            | ab                 | 800                                        |                    | 1200                  |                       |

| V <sub>ODE(SS)</sub> | Steady state output differential voltage with de-emphasis              | $AV_{CC} = 3.3 \text{ V}, R_T = 50 \Omega$                                                                                                                                                         |                    | 560                                        |                    | 840                   | mVp-p                 |

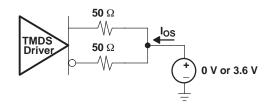

|                      | Chart aircuit autaut aurrent                                           | Can Figure 6                                                                                                                                                                                       | PRE = Low          | -12                                        |                    | 12                    | A                     |

| I <sub>(OS)</sub>    | Short circuit output current                                           | See Figure 6                                                                                                                                                                                       | PRE = High         | -15                                        |                    | 15                    | mA                    |

| V <sub>I(open)</sub> | Single-ended input voltage under high impedance input or open input    | Ι <sub>Ι</sub> = 10 μΑ                                                                                                                                                                             |                    | V <sub>CC</sub> -10                        |                    | V <sub>CC</sub> +10   | mV                    |

| R <sub>INT</sub>     | Input termination resistance                                           | V <sub>IN</sub> = 2.9 V                                                                                                                                                                            |                    | 45                                         | 50                 | 55                    | Ω                     |

| STATUS PI            | NS (HPD_SINK, 5V_PWR)                                                  |                                                                                                                                                                                                    | <u>'</u>           |                                            |                    | '                     |                       |

All typical values are at 25°C and with a 3.3-V supply. The maximum rating is characterized under 3.6 V  $\rm V_{CC}.$ (2)

# **ELECTRICAL CHARACTERISTICS (continued)**

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                       | TEST CONI                                     | DITIONS                                       | MIN  | TYP <sup>(1)</sup> | MAX      | UNIT |

|----------------------|-----------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|------|--------------------|----------|------|

|                      | Himb lavel distalling at a consta                               | V <sub>IH</sub> = 5.3 V                       |                                               | -150 |                    | 150      |      |

| I <sub>IH</sub>      | High-level digital input current                                | V <sub>IH</sub> = 2 V or V <sub>CC</sub>      |                                               | -85  |                    | 85       | μA   |

| I <sub>IL</sub>      | Low-level digital input current                                 | V <sub>IL</sub> = GND or 0.8 V                |                                               | -20  |                    | 20       | μA   |

| STATUS P             | PINS (HPD, 5V_SINK)                                             | <u> </u>                                      | "                                             |      |                    |          |      |

| V <sub>OH</sub>      | High-level output voltage                                       | $I_{OH} = -4 \text{ mA}$                      |                                               | 2.4  |                    | $V_{CC}$ | V    |

| V <sub>OL</sub>      | Low-level output voltage                                        | I <sub>OL</sub> = 4 mA                        |                                               | GND  |                    | 0.4      | V    |

| CONTROL              | . PINS (LC_A0, LC_A1, GE, GPIO)                                 |                                               | -                                             |      |                    | '        |      |

| I <sub>IH</sub>      | High-level digital input current                                | V <sub>IH</sub> = 2 V or V <sub>CC</sub>      |                                               | -10  |                    | 10       | μA   |

| I <sub>IL</sub>      | Low-level digital input current                                 | V <sub>IL</sub> = GND or 0.8 V                |                                               | -10  |                    | 10       | μA   |

| Cı                   | Input capacitance                                               | V <sub>I</sub> = GND or V <sub>CC</sub>       |                                               |      |                    | 10       | pF   |

| DDC I/O P            | INS (SCL_SINK, SDA_SINK)                                        |                                               | -                                             |      |                    | '        |      |

|                      |                                                                 | V <sub>I</sub> = 5.5 V                        |                                               | -50  |                    | 50       |      |

| I <sub>lkg</sub>     | Input leakage current                                           | $V_I = V_{CC}$                                |                                               | -10  |                    | 10       | μA   |

| I <sub>он</sub>      | High-level output current                                       | V <sub>O</sub> = 3.6 V                        |                                               | -10  |                    | 10       | μΑ   |

| I <sub>IL</sub>      | Low-level input current                                         | V <sub>IL</sub> = GND                         |                                               | -40  |                    | 40       | μA   |

|                      | Low-level output voltage                                        |                                               | OVS = NC                                      | 470  |                    | 620      |      |

| $V_{OL}$             |                                                                 | $I_{OL}$ = 400 $\mu A$ or 4 mA                | OVS = GND                                     | 620  |                    | 775      | V    |

|                      |                                                                 |                                               | OVS = V <sub>CC</sub>                         | 775  |                    | 950      |      |

|                      |                                                                 |                                               | OVS = NC                                      |      | 70                 |          |      |

| $V_{OL}$ - $V_{ILC}$ | Low-level input voltage below output<br>low-level voltage level | Ensured by design                             | OVS = GND                                     |      | 240                |          | mV   |

|                      | low lover vertage lever                                         |                                               | OVS = V <sub>CC</sub>                         | 420  |                    |          |      |

| 0                    | la a sala sala sala sala sala sala sala                         | V <sub>I</sub> = 5.0 V or 0 V, Freq           | = 100 kHz                                     |      |                    | 25       |      |

| C <sub>IO</sub>      | Input/output capacitance                                        | V <sub>I</sub> = 3.0 V or 0 V, Freq           | = 100 kHz                                     |      |                    | 10       | pF   |

| DDC I/O P            | INS (SCL, SDA) AND LOCAL I <sup>2</sup> C PINS (LO              | C_SCL, LC_SDA)                                |                                               |      |                    |          |      |

|                      |                                                                 | V <sub>I</sub> = 5.5 V                        |                                               | -50  |                    | 50       |      |

| l <sub>lkg</sub>     | Input leakage current                                           | $V_I = V_{CC}$                                |                                               | -10  |                    | 10       | μΑ   |

| Іон                  | High-level output current                                       | V <sub>O</sub> = 3.6 V                        |                                               | -10  |                    | 10       | μA   |

| l <sub>IL</sub>      | Low-level input current                                         | V <sub>IL</sub> = GND                         |                                               | -10  |                    | 10       | μΑ   |

| V <sub>OL</sub>      | Low-level output voltage                                        | I <sub>OL</sub> = 4 mA                        |                                               |      |                    | 0.2      | V    |

| 0                    | land to a second second                                         | V <sub>I</sub> = 5.0 V or 0 V, Freq = 100 kHz |                                               |      |                    | 25       |      |

| CI                   | Input capacitance                                               | V <sub>I</sub> = 3.0 V or 0 V, Freq           | V <sub>I</sub> = 3.0 V or 0 V, Freq = 100 kHz |      |                    | 10       | pF   |

## **SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                                     | TEST CONDITIONS                                                                                             | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|----------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| TMDS D               | IFFERENTIAL PINS (Y/Z)                                                        |                                                                                                             |     |                    |     |      |

| t <sub>PLH</sub>     | Propagation delay time, low-to-high-level output                              |                                                                                                             | 250 |                    | 800 | ps   |

| t <sub>PHL</sub>     | Propagation delay time, high-to-low-level output                              |                                                                                                             | 250 |                    | 800 | ps   |

| t <sub>r</sub>       | Differential output signal rise time (20% - 80%)                              |                                                                                                             | 80  |                    | 240 | ps   |

| t <sub>f</sub>       | Differential output signal fall time (20% - 80%)                              |                                                                                                             | 80  |                    | 240 | ps   |

| t <sub>sk(p)</sub>   | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) <sup>(2)</sup>            | See Figure 4, AV <sub>CC</sub> = 3.3 V,<br>$R_T = 50 \Omega$                                                |     |                    | 50  | ps   |

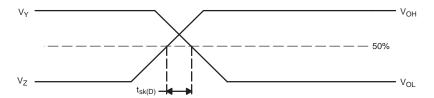

| t <sub>sk(D)</sub>   | Intra-pair differential skew, see Figure 7                                    | 147 = 30 12                                                                                                 |     |                    | 75  | ps   |

| t <sub>sk(o)</sub>   | Inter-pair channel-to-channel output skew (3)                                 |                                                                                                             |     |                    | 150 | ps   |

| t <sub>sk(bb)</sub>  | Bank-to-bank skew                                                             |                                                                                                             |     |                    | 300 | ps   |

| t <sub>sk(pp)</sub>  | Part-to-part skew (4)                                                         |                                                                                                             |     |                    | 1   | ns   |

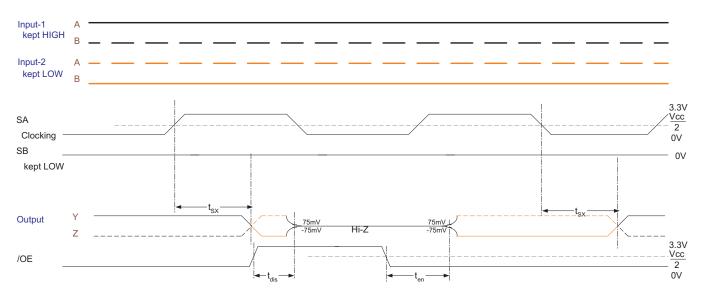

| t <sub>en</sub>      | Enable time                                                                   | 0 5 0                                                                                                       |     |                    | 20  | ns   |

| t <sub>dis</sub>     | Disable time                                                                  | See Figure 8                                                                                                |     |                    | 20  | ns   |

| t <sub>sx</sub>      | TMDS Switch time                                                              |                                                                                                             |     |                    | 20  | ns   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from Y/Z(1), residual jitter                       | See Figure 9, Ai/Bi(1) = 165-MHz clock,                                                                     |     | 10                 | 30  | ps   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from Y/Z(2:4), residual jitter                     | Ai/Bi(2:4) = 1.65-Gbps HDMI pattern, PRE = low Input: 5m 28AWG HDMI cable, Output: 3-Inch 8-mil trace width |     | 48                 | 74  | ps   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from Y/Z(1), residual jitter                       | See Figure 9, Ai/Bi(1) = 225-MHz clock,                                                                     |     | 18                 | 33  | ps   |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter from Y/Z(2:4), residual jitter                     | Ai/Bi(2:4) = 2.25-Gbps HDMI pattern, PRE = low Input: 5m 28AWG HDMI cable, Output: 3-Inch 8-mil trace width |     | 56                 | 71  | ps   |

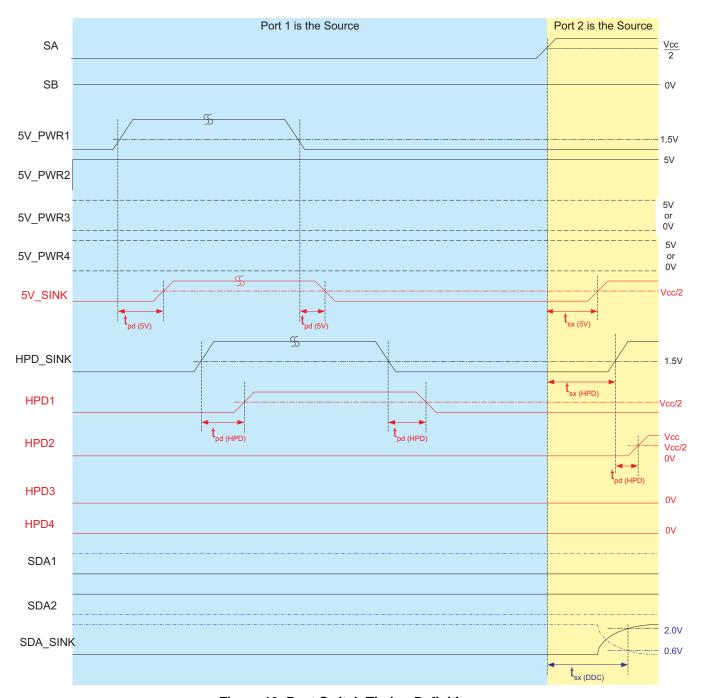

| CONTRO               | OL AND STATUS PINS (HPD_SINK, HPD, 5V_PWR, 5V_SINK)                           |                                                                                                             |     |                    |     |      |

| t <sub>pd(HPD)</sub> | Propagation delay time                                                        |                                                                                                             |     |                    | 15  | ns   |

| t <sub>pd(5V)</sub>  | Propagation delay time                                                        |                                                                                                             |     |                    | 15  | ns   |

| t <sub>sx(HPD)</sub> | HPD Switch time                                                               | See Figure 8  C <sub>L</sub> = 10 pF, C <sub>L(DDC)</sub> = 100 pF                                          |     |                    | 15  | ns   |

| t <sub>sx(5V)</sub>  | 5-V Power switch time                                                         | St- 10 pt , St(BBC) = 100 pt                                                                                |     |                    | 15  | ns   |

| t <sub>sx</sub>      | DDC Switch time                                                               |                                                                                                             |     |                    | 1   | μs   |

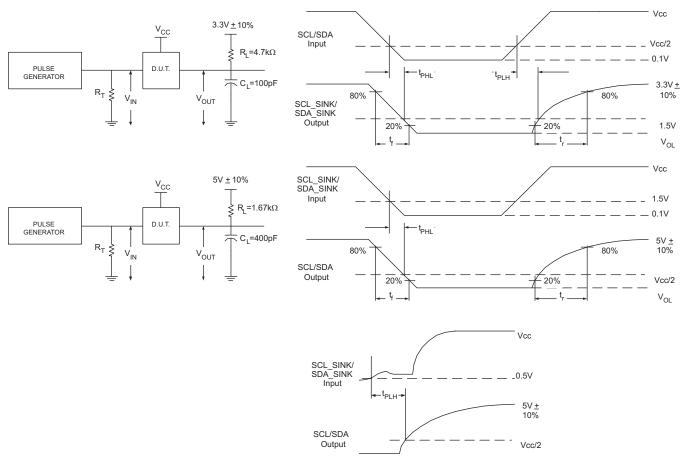

| DDC I/O              | PINS (SCL, SCL_SINK, SDA, SDA_SINK)                                           |                                                                                                             |     |                    |     |      |

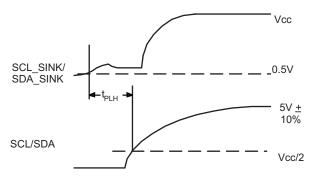

| t <sub>PLH</sub>     | Propagation delay time, low-to-high-level output SCL_SINK/SDA_SINK to SCL/SDA |                                                                                                             | 204 |                    | 459 | ns   |

| t <sub>PHL</sub>     | Propagation delay time, high-to-low-level outputSCL_SINK/SDA_SINK to SCL/SDA  |                                                                                                             | 35  |                    | 140 | ns   |

| t <sub>PLH</sub>     | Propagation delay time, low-to-high-level output SCL/SDA to SCL_SINK/SDA_SINK |                                                                                                             | 194 |                    | 351 | ns   |

| t <sub>PHL</sub>     | Propagation delay time, high-to-low-level output SCL/SDA to SCL_SINK/SDA_SINK | See Figure 11, OVS = NC                                                                                     | 35  |                    | 140 | ns   |

| t <sub>r</sub>       | Output signal rise time, SCL_SINK/SDA_SINK                                    |                                                                                                             | 500 |                    | 800 | ns   |

| t <sub>f</sub>       | Output signal fall time, SCL_SINK/SDA_SINK                                    |                                                                                                             | 20  |                    | 72  | ns   |

| t <sub>r</sub>       | Output signal rise time, SCL/SDA                                              |                                                                                                             | 796 |                    | 999 | ns   |

| t <sub>f</sub>       | Output signal fall time, SCL/SDA                                              |                                                                                                             | 20  |                    | 72  | ns   |

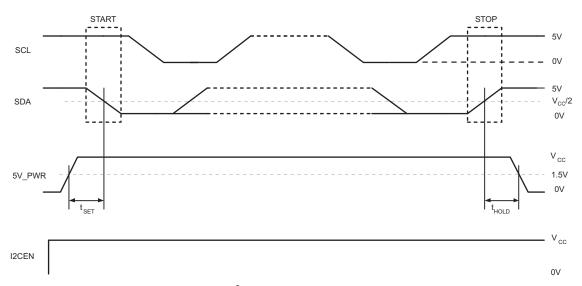

| t <sub>set</sub>     | Enable to start condition                                                     | 0 5 10                                                                                                      | 100 |                    |     | ns   |

| t <sub>hold</sub>    | Enable after stop condition                                                   | See Figure 12                                                                                               | 100 |                    |     | ns   |

- (1) All typical values are at 25°C and with a 3.3-V supply.

- $t_{sk(p)}$  is the magnitude of the time difference between  $t_{PLH}$  and  $t_{PHL}$  of a specified terminal.

- $t_{sk(0)}$  is the magnitude of the difference in propagation delay times between any specified terminals of channel 2 to 4 of a device when inputs are tied together.

- tsk(pp) is the magnitude of the difference in propagation delay times between any specified terminals of channel 2 to 4 of two devices, or between channel 1 of two devices, when both devices operate with the same source, the same supply voltages, at the same temperature, and have identical packages and test circuits.

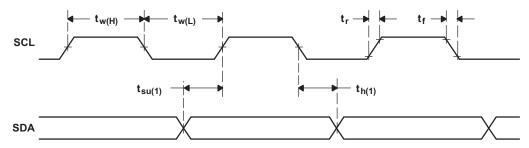

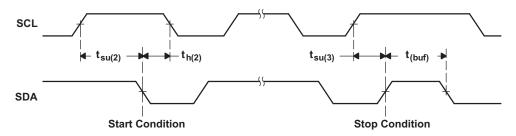

# TIMING CHARACTERISTICS FOR LOCAL I $^2$ C INTERFACE (LC\_SCL, LC\_SDA, LC\_AO, LC\_A1)

|                               | PARAMETER                                        | STANDARD | MODE | FAST MODE |     | UNIT |

|-------------------------------|--------------------------------------------------|----------|------|-----------|-----|------|

|                               | PARAMETER                                        | MIN      | MAX  | MIN       | MAX | UNII |

| $f_{SCL}$                     | Clock frequency, SCL                             |          | 100  |           | 400 | kHz  |

| $t_{w(L)}$                    | Clock low period, SCL low                        | 4.7      |      | 1.3       |     | μs   |

| t <sub>w(H)</sub>             | Clock high period, SCL high                      | 4        |      | 0.6       |     | μs   |

| t <sub>r</sub>                | Rise time, SCL and SDA                           |          | 1000 |           | 300 | μs   |

| t <sub>f</sub>                | Fall time, SCL and SDA                           |          | 300  |           | 300 | μs   |

| t <sub>su(1)</sub>            | Setup time, SDA to SCL                           | 250      |      | 100       |     | μs   |

| t <sub>h(1)</sub>             | Hold time, SCL to SDA                            | 0        |      | 0         |     | μs   |

| t <sub>(buf)</sub>            | BUS Free time between a STOP and START condition | 4.7      |      | 1.3       |     | μs   |

| t <sub>su(2)</sub>            | Setup time, SCL to start condition               | 4.7      |      | 0.6       |     | μs   |

| t <sub>h(2)</sub>             | Hold time, start condition to SCL                | 4        |      | 0.6       |     | μs   |

| t <sub>su(3)</sub>            | Setup time, SCL to stop condition                | 4        |      | 0.6       |     | μs   |

| C <sub>b</sub> <sup>(1)</sup> | Capacitive load for each bus line                |          | 400  |           | 400 | pF   |

<sup>(1)</sup>  $C_b$  is the total capacitance of one bus line in pF.

## PARAMETER MEASUREMENT INFORMATION

A.  $t_{r}$  and  $t_{f}$  are measured at 20% - 80% refered to  $V_{IHmin}$  and  $V_{ILmax}$  levels.

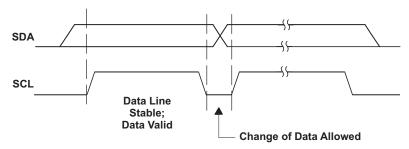

Figure 1. SCL and SDA Timing

Figure 2. Start and Stop Conditions

Figure 3. Typical Termination for TMDS Output Driver

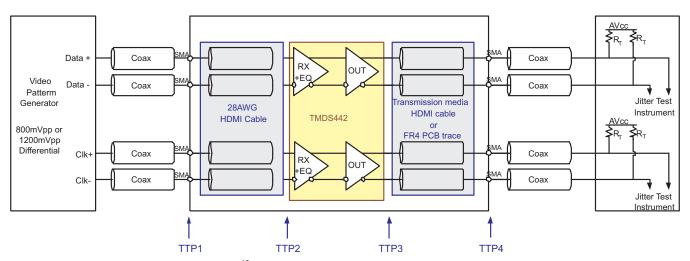

NOTE: PRE = low. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f$  < 100 ps, 100 MHz from Agilent 81250.  $C_L$  includes instrumentation and fixture capacitance within 0.06 m of the D.U.T. Measurement equipment provides a bandwidth of 20 GHz minimum.

Figure 4. TMDS Timing Test Circuit and Definitions

Figure 5. De-Emphasis Output Voltage Waveforms and Duration Measurement Definitions

Figure 6. Short Circuit Output Current Test Circuit

Figure 7. Definition of Intra-Pair Differential Skew

**Figure 8. TMDS Outputs Control Timing Definitions**

- A. All jitters are measured in BER of 10<sup>-12</sup>

- B. The residual jitter reflects the total jitter measured at the TMDS442 output, TP3, subtract the total jitter from the signal generator, TP1

- C. The input cable length and the output transmission media are specified in the test conditions.

Figure 9. Jitter Test Circuit

Figure 10. Post Switch Timing Definitions

Figure 11. I<sup>2</sup>C Timing Test Circuit and Definition

Figure 12. I<sup>2</sup>C Setup and Hold Definition

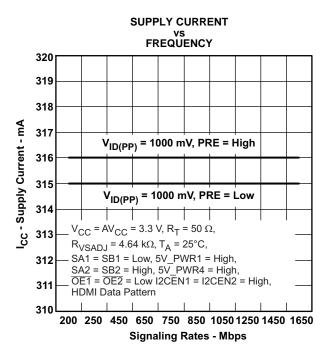

#### TYPICAL CHARACTERISTICS

Figure 13.

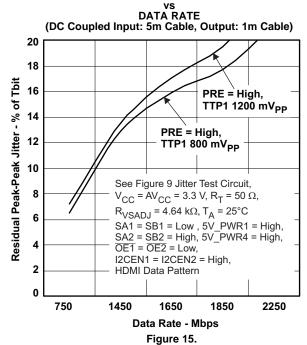

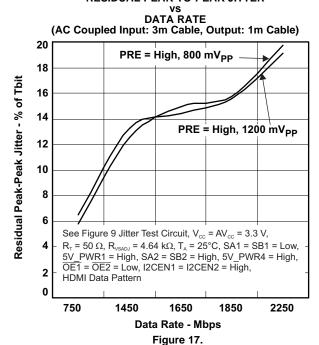

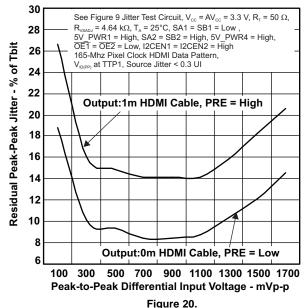

#### **RESIDUAL PEAK-TO-PEAK JITTER**

Figure 14.

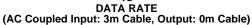

### RESIDUAL PEAK-TO-PEAK JITTER

DATA RATE (DC Coupled Input: 5m Cable, Output: 0m Cable)

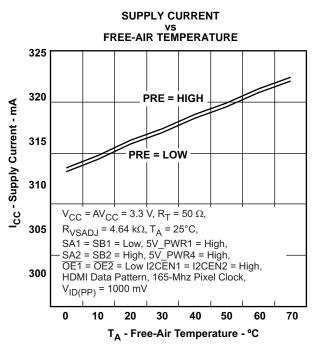

## TYPICAL CHARACTERISTICS (continued)

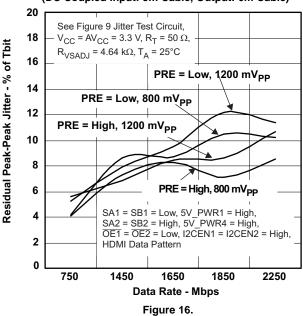

## **RESIDUAL PEAK-TO-PEAK JITTER**

## **RESIDUAL PEAK-TO-PEAK JITTER**

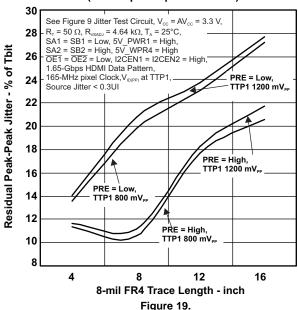

vs 8-MIL FR4 TRACE OUTPUT (DC Coupled Input: 5m Cable)

#### **RESIDUAL PEAK-TO-PEAK JITTER** vs

# **RESIDUAL PEAK-TO-PEAK JITTER**

VS PEAK-TO-PEAK DIFFERENTIAL INPUT VOLTAGE (at TTP1, DC Coupled: 5m Cable)

## **TYPICAL CHARACTERISTICS (continued)**

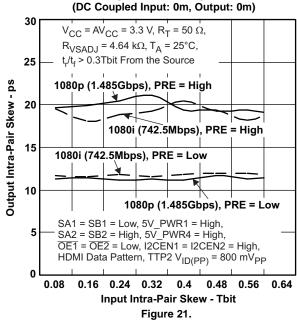

# OUTPUT INTRA-PAIR SKEW vs INPUT INTRA-PAIR SKEW DC Coupled Input: 0m, Output: 0m

## **TYPICAL CHARACTERISTICS (continued)**

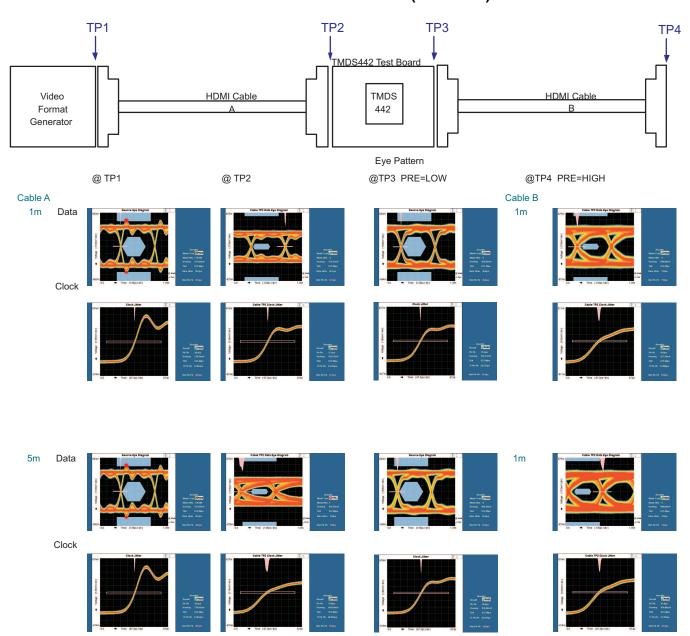

Figure 22. Eye Patterns at 148.5-MHz Pixel Clock

## **DESCRIPTION**

#### **SOURCE SELECTION LOOKUP**

| C  | ONTROL | REGIST | ER BITS | 1/0   | SELECTED             |                                                      | HOT PLUG DE        | TECT STATUS      |          |  |  |

|----|--------|--------|---------|-------|----------------------|------------------------------------------------------|--------------------|------------------|----------|--|--|

| SB | SA     | ŌĒ     | I2CEN   | Y/Z   | SCL_SINK<br>SDA_SINK | HPD1                                                 | HPD2               | HPD3             | HPD4     |  |  |

| L  | L      | L      | Н       | A1/B1 | SCL1<br>SDA1         | HPD_SINK                                             | L                  | L                | L        |  |  |

| L  | Н      | L      | Н       | A2/B2 | SCL2<br>SDA2         | L                                                    | HPD_SINK           | L                | L        |  |  |

| Н  | L      | L      | Н       | A3/B3 | SCL3<br>SDA3         | L                                                    | L                  | HPD_SINK         | L        |  |  |

| Н  | Н      | L      | Н       | A4/B4 | SCL4<br>SDA4         | L                                                    | L                  | L                | HPD_SINK |  |  |

| Χ  | Х      | L      | L       | A/B   | Z                    | HPD_SINK is transmitted to corresponding source port |                    |                  |          |  |  |

| Х  | Х      | Н      | Н       | Z     | SCL<br>SDA           | HPD_SINK is train                                    | nsmitted to corres | ponding source p | oort     |  |  |

| Х  | Х      | Н      | L       | Z     | Z                    | HPD_SINK is trai                                     | nsmitted to corres | ponding source p | oort     |  |  |

# SINK PRIORITY CONTROL (SA1 = SA2 = Low, SB1 = SB2 = Low, OE1 = OE2 = Low, I2CEN1 = I2CEN2 = High)

| SINK PRIORITY | ;     | SINK PORT 1         |       | SINK PORT 2         |           |

|---------------|-------|---------------------|-------|---------------------|-----------|

| SP            | Y1/Z1 | SCL_SINK1/SDA_SINK1 | Y2/Z2 | SCL_SINK2/SDA_SINK2 | HPD1      |

| L             | A1/B1 | SCL1/SDA1           | A1/B1 | Z                   | HPD_SINK1 |

| Н             | A1/B1 | Z                   | A1/B1 | SCL1/SDA1           | HPD_SINK2 |

## 5V\_PWR STATUS (SA = Low, SB = Low, $\overline{OE}$ = Low, I2CEN = High)

|    | CONTROL STATUS SOURCE PLUG IN STATUS |         |       | O SELECTED        | HOT PLUG DETECT STATUS |      |      |      |

|----|--------------------------------------|---------|-------|-------------------|------------------------|------|------|------|

| GE | 5V_EN                                | 5V_PWR1 | Y/Z   | SCL_SINK/SDA_SINK | HPD1                   | HPD2 | HPD3 | HPD4 |

| L  | Н                                    | Н       | A1/B1 | SCL1/SDA1         | HPD_SINK               | L    | L    | L    |

| L  | Н                                    | L       | Z     | Z                 | L                      | L    | L    | L    |

| L  | L                                    | Х       | A1/B1 | SCL1/SDA1         | HPD_SINK               | L    | L    | L    |

| Н  | Х                                    | Н       | A1/B1 | SCL1/SDA1         | HPD_SINK               | L    | L    | L    |

| Н  | Х                                    | L       | Z     | Z                 | L                      | L    | L    | L    |

## I<sup>2</sup>C POINTER REGISTER

| P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|----|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 0  | X  | X  |

- 01, Sink port 1 configuration register

- 10, Sink port 2 configuration register

- 11, Source plug-in status register

Power up default is 0000 0011

#### SINK PORT 1 CONFIGURATION REGISTER

| <b>C7</b> | C6 | C5 | C4   | C3     | C2  | C1  | C0  |

|-----------|----|----|------|--------|-----|-----|-----|

| 0         | 0  | 0  | PRE1 | I2CEN1 | OE1 | SB1 | SA1 |

## Power up default is 0000 1000

## **SINK PORT 2 CONFIGURATION REGISTER**

| C7 | C6 | C5 | C4   | C3     | C2  | C1  | C0  |

|----|----|----|------|--------|-----|-----|-----|

| 0  | 0  | 0  | PRE2 | I2CEN2 | OE2 | SB2 | SA2 |

## Power up default is 0000 1001

## **SOURCE PLUG-IN STATUS REGISTER**

| <b>S</b> 7 | S6 | S5 | S4    | S3      | S2      | S1      | S0      |

|------------|----|----|-------|---------|---------|---------|---------|

| 0          | 0  | SP | 5V_EN | 5V_PWR4 | 5V_PWR3 | 5V_PWR2 | 5V_PWR1 |

## Power up default is 0001 0000

#### **APPLICATION INFORMATION**

#### I<sup>2</sup>C Interface Notes

The I<sup>2</sup>C interface is used to access the internal registers of the TMDS442. I<sup>2</sup>C is a two-wire serial interface developed by Philips Semiconductor (see I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000). The bus consists of a data line (SDA) and a clock line (SCL) with pull-up structures. When the bus is idle, both SDA and SCL lines are pulled high. All the I<sup>2</sup>C compatible devices connect to the I<sup>2</sup>C bus through open drain I/O pins, SDA and SCL. A master device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A slave device receives and/or transmits data on the bus under control of the master device. The TMDS442 works as a slave and supports the standard mode transfer (100 kbps) and fast mode transfer (400 kbps) as defined in the I<sup>2</sup>C-Bus Specification. The TMDS442 has been tested to be fully functional with the high-speed mode (3.4 Mbps) but is not ensured at this time.

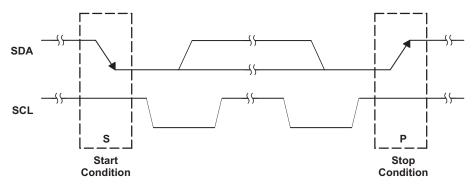

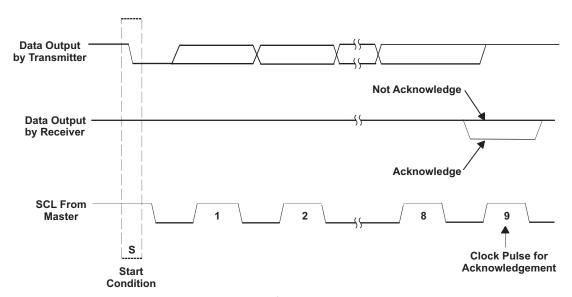

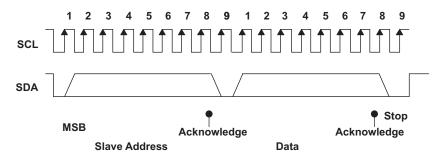

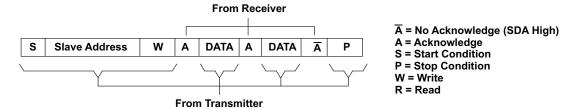

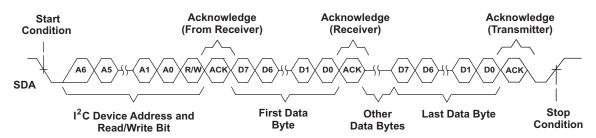

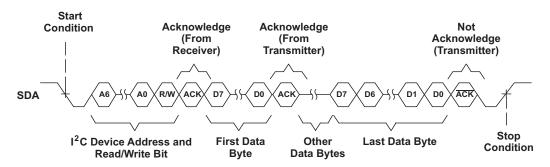

The basic I<sup>2</sup>C start and stop access cycles are shown in Figure 23. The basic access cycle consists of the following:

- A start condition

- · A slave address cycle

- · Any number of data cycles

- A stop condition

Figure 23. I<sup>2</sup>C Start and Stop Conditions

#### General I<sup>2</sup>C Protocol

- The master initiates data transfer by generating a start condition. The start condition is when a high-to-low transition occurs on the SDA line while SCL is high, as shown in Figure 23. All I<sup>2</sup>C-compatible devices should recognize a start condition.

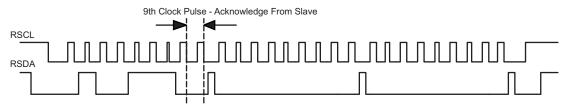

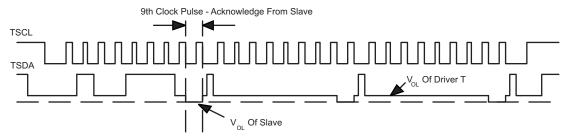

- The master then generates the SCL pulses and transmits the 7-bit address and the read/write direction bit R/W on the SDA line. During all transmissions, the master ensures that data is valid. A valid data condition requires the SDA line to be stable during the entire high period of the clock pulse (see Figure 23). All devices recognize the address sent by the master and compare it to their internal fixed addresses. Only the slave device with a matching address generates an acknowledge (see Figure 25) by pulling the SDA line low during the entire high period of the ninth SCL cycle. On detecting this acknowledge, the master knows that a communication link with a slave has been established.

- The master generates further SCL cycles to either transmit data to the slave (R/W bit 1) or receive data from

the slave (R/W bit 0). In either case, the receiver needs to acknowledge the data sent by the transmitter. So

an acknowledge signal can either be generated by the master or by the slave, depending on which one is the

receiver. The 9-bit valid data sequences consisting of 8-bit data and 1-bit acknowledge can continue as long

as necessary (see Figure 26).

- To signal the end of the data transfer, the master generates a stop condition by pulling the SDA line from low

to high while the SCL line is high (see Figure 23). This releases the bus and stops the communication link

with the addressed slave. All I<sup>2</sup>C compatible devices must recognize the stop condition. Upon the receipt of a

stop condition, all devices know that the bus is released, and they wait for a start condition followed by a

matching address.

Figure 24. I<sup>2</sup>C Bit Transfer

Figure 25. I<sup>2</sup>C Acknowledge

Figure 26. I<sup>2</sup>C Address and Data Cycles

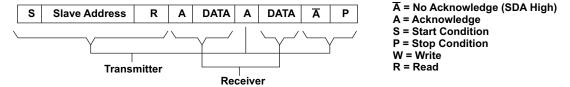

During a write cycle, the transmitting device must not drive the SDA signal line during the acknowledge cycle so that the receiving device may drive the SDA signal low. After each byte transfer following the address byte, the receiving device will pull the SDA line low for one SCL clock cycle. A stop condition will be initiated by the transmitting device after the last byte is transferred. An example of a write cycle can be found in Figure 27 and Figure 28. Note that the TMDS442 does not allow multiple write transfers to occur. See Example – Writing to the TMDS442 section for more information.

During a read cycle, the slave receiver will acknowledge the initial address byte if it decodes the address as its address. Following this initial acknowledge by the slave, the master device becomes a receiver and

acknowledges data bytes sent by the slave. When the master has received all of the requested data bytes from the slave, the not acknowledge (A) condition is initiated by the master by keeping the SDA signal high just before it asserts the stop (P) condition. This sequence terminates a read cycle as shown in Figure 29 and Figure 30. Note that the TMDS442 does not allow multiple read transfers to occur. See Example – Reading from the TMDS442 section for more information.

Figure 27. I<sup>2</sup>C Write Cycle

Figure 28. Multiple Byte Write Transfer

Figure 29. I<sup>2</sup>C Read Cycle

Figure 30. Multiple Byte Read Transfer

## **Slave Address**

Both SDA and SCL must be connected to a positive supply voltage via a pull-up resistor. These resistors should comply with the  $I^2C$  specification that ranges from 2  $k\Omega$  to 19  $k\Omega$ . When the bus is free, both lines are high. The address byte is the first byte received following the START condition from the master device. The first 5 Bits (MSBs) of the address are factory preset to 01011. The next two bits of the TMDS442 address are controlled by

the logic levels appearing on the I2C-A1 and I2C-A0 pins. The I2C-A1 and I2C-A0 address inputs can be connected to  $V_{CC}$  for logic 1, GND for logic 0, or can be actively driven by TTL/CMOS logic levels. The device addresses are set by the state of these pins and are not latched. Thus a dynamic address control system could be utilized to incorporate several devices on the same system. Up to four TMDS442 devices can be connected to the same I<sup>2</sup>C-Bus without requiring additional glue logic. Table 1 lists the possible addresses for the TMDS442.

**FIXED ADDRESSES SELECTABLE WITH ADDRESS PINS READ/WRITE BIT** BIT 7 (MSB) BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 (A1) BIT 1 (A0) BIT 0 (R/W)

**Table 1. TMDS442 Slave Addresses**

## Sink Port Selection Register and Source Plug-In Status Register Description (Sub-Address)

The TMDS442 operates using only a single byte transfer protocol similar to Figure 27 and Figure 29. The internal sub-address registers and the functionality of each can be found in Table 2. When writing to the device, it is required to send one byte of data to the corresponding internal sub-address. If control of two sink ports and source plug-in status is desired, then the master will have to cycle through the sub-addresses (sink ports) one at a time as illustrated in the Example – Writing to the TMDS442 section for the proper procedure of writing to the TMDS442.

During a read cycle, the TMDS442 sends the data in its selected sub-address in a single transfer to the master device requesting the information. See the Example – Reading from the TMDS442 section of this document for the proper procedure on reading from the TMDS442. Upon power up, the TMDS442 registers are in a default value, 0000 0011.

REGISTER NAME

BIT ADDRESS (b<sub>7</sub>b<sub>6</sub>b<sub>5</sub>...b<sub>0</sub>)

Sink port 1

0000 0001

Sink port 2

0000 0010

Source plug-in status

0000 0011

Table 2. TMDS442 Sink Port and Source Plug-In Status Registers Selection

## Sink Port Register Bit Descriptions

Each bit of the first two sub-addresses, sink port 1 and port 2 control registers, allows the user to individually control the functionality of the TMDS442. The benefit of this process allows the user to control the functionality of each sink port independent of the other sink port. The bit description is decoded in Table 3.

Table 3. TMDS442 Sink Port Register Bit Decoder

| BIT     | FUNCTION | BIT VALUES | RESULT                                                 |

|---------|----------|------------|--------------------------------------------------------|

| 7, 6, 5 | Reserved | 000        | Default value                                          |

| 4       | PRE      | 0          | 3dB De-emphasis off                                    |

| 4       | FRE      | 1          | 3dB De-emphasis on                                     |

| 3       | ISCEN    | 0          | Sink side I <sup>2</sup> C buffer is disabled (Hi-Z)   |

| 3       | I2CEN    | 1          | Default value  3dB De-emphasis off  3dB De-emphasis on |

| 2       | OF.      | 0          | Sink side TMDS on                                      |

| 2       | OE       | 1          | Sink side TMDS off (Hi-Z)                              |

Table 3. TMDS442 Sink Port Register Bit Decoder (continued)

| BIT  | FUNCTION | BIT VALUES | RESULT               |

|------|----------|------------|----------------------|

|      |          | 00         | Source port 1 select |

| 1.0  | SB SA    | 01         | Source port 2 select |

| 1, 0 | 3B 3A    | 10         | Source port 3 select |

|      |          | 11         | Source port 4 select |

Bits 7 (MSB), 6 and 5 – Reserved bits without function.

Bit 4 – Controls the TMDS output differential voltage.

Bit 3 – Controls the status of DDC interface, SCL\_SINK and SDA SINK.

Bit 2 – Controls the status of TMDS interface, Y/Z.

Bits 1, and 0 (LSB) - Selects the source input of the TMDS442.

The 5-V plug in status can be read through each bit of the sub-address (source plug-in status) status register. Each bit of the third sub-address, source plug-in status registers, allows the user to read the cable plug-in status based on the appearance of a valid +5-V power signal from each source input port. The bit description is decoded in Table 4.

Table 4. TMDS442 Source Plug-In Status Register Bit Decoder

| BIT  | FUNCTION | BIT VALUES | RESULT                                                                                                                                     |

|------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6 | Reserved | 0 0        | Default value                                                                                                                              |

| 5    | SP       | 0          | Sink port1 is the main display when the same source is selected by both sinks                                                              |

| 5    | SF       | 1          | Sink port2 is the main display when the same source is selected by both sinks                                                              |

| 4    | 5\/      | 0          | TMDS output status is not controlled by the corresponding +5-V power signal                                                                |

| 4    | 5V_EN    | 1          | TMDS output status is controlled by the corresponding +5-V power signal                                                                    |

| 2    | EV DIMDA | 0          | Source side I <sup>2</sup> C buffer is disabled (Hi-Z) When source port 4 is selected by sink, TMDS is Hi-Z                                |

| 3    | 5V_PWR4  | 1          | Source side $I^2C$ buffer is enabled When source port 4 is selected by sink, TMDS is under the control of $\overline{OE}$                  |

| 2    | EV DWD2  | 0          | Source side I <sup>2</sup> C buffer is disabled (Hi-Z)                                                                                     |

| 2    | 5V_PWR3  | 1          | When source port 3 is selected by sink, TMDS is Hi-Z                                                                                       |

|      | SV DIMPO | 0          | Source side I <sup>2</sup> C buffer is disabled (Hi-Z) When source port 2 is selected by sink, TMDS is Hi-Z                                |

| 1    | 5V_PWR2  | 1          | Source side I <sup>2</sup> C buffer is enabled When source port 2 is selected by sink, TMDS is under the control of $\overline{\text{OE}}$ |

| 0    | CV DIMDA | 0          | Source side I <sup>2</sup> C buffer is disabled (Hi-Z) When source port 1 is selected by sink, TMDS is Hi-Z                                |

| 0    | 5V_PWR1  | 1          | Source side I <sup>2</sup> C buffer is enabled When source port 1 is selected by sink, TMDS is under the control of $\overline{\text{OE}}$ |

## **Example - Writing to the TMDS442**

The proper way to write to the TMDS442 is illustrated as follows: