**TLC6A598**

# TLC6A598 电源逻辑 8 位移位寄存器

# 1 特性

Texas

Instruments

- 具有高可靠性和稳健性,适合航空电子设备应用

- 宽工作环境温度范围:-55°C 至 +125°C

- 3V 至 5.5V 的宽 V<sub>CC</sub> 范围

- 八个电源 DMOS 晶体管输出通道

- 350 mA 持续电流

- 1.1A 电流限制能力

- 输出钳位电压,50V

- 低 R<sub>ds(on)</sub> , 1 Ω (典型值)

- 雪崩能量, 90mJ(最大值)

- 保护

- 过流保护

- 开路和短路负载检测

- 串行接口通信误差检测

- 热关断保护

- 针对多级的增强型级联

- 所有寄存器通过单个输入清零

- 循环冗余校验 (CRC)

- 低功耗

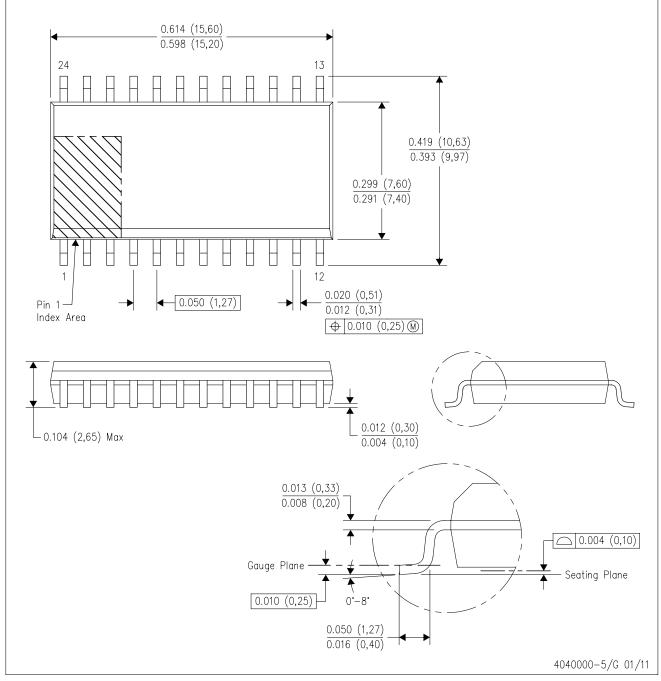

- 24 引脚 SOIC DW 封装

### 2 应用

- 飞行控制系统

- PLC 控制和功能指示器

- 仪表组

- 继电器或螺线管驱动器

- 电器显示面板

- · LED 指示和照明

### 3 说明

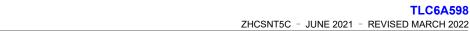

TLC6A598 器件是一款单片、高压、高电流功率 8 位 移位寄存器,专为负载功率要求相对较高的系统(例 如,LED)而设计。

该器件包含内置的输出钳位电压,用于提供电感瞬态保 护。电源驱动器应用包括继电器、螺线管和其他高电流 或高电压负载。每个开漏 DMOS 晶体管都具有独立的 斩波限流电路,以防止在短路情况下损坏。

此器件包含一个8位串入、并出移位寄存器,此寄存 器为一个 8 位 D 类存储寄存器提供数据。输出为低 侧、漏极开路 DMOS 晶体管,额定输出为 50V,连续 灌电流能力为 350mA。内置负载开路和负载短路诊断 机制提供增强的安全保护。器件提供循环冗余校验,以 验证移位寄存器中的寄存器值。在读回模式中,该器件 提供 6 位 CRC 提醒。MCU 可以读回 CRC 提醒并检 查该提醒是否正确,以确定 MCU 与该器件之间的通信 环路是否良好。

TLC6A598 的额定工作环境温度范围为 -55°C 至 125°C。

#### 器件信息(1)

|          | RR 11 1A - C- |                    |  |  |  |  |  |  |  |

|----------|---------------|--------------------|--|--|--|--|--|--|--|

| 器件型号     | 封装            | 封装尺寸(标称值)          |  |  |  |  |  |  |  |

| TLC6A598 | SOIC (24)     | 15.70 mm x 7.50 mm |  |  |  |  |  |  |  |

如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

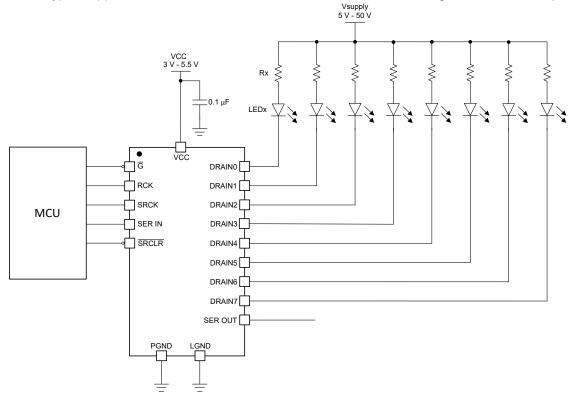

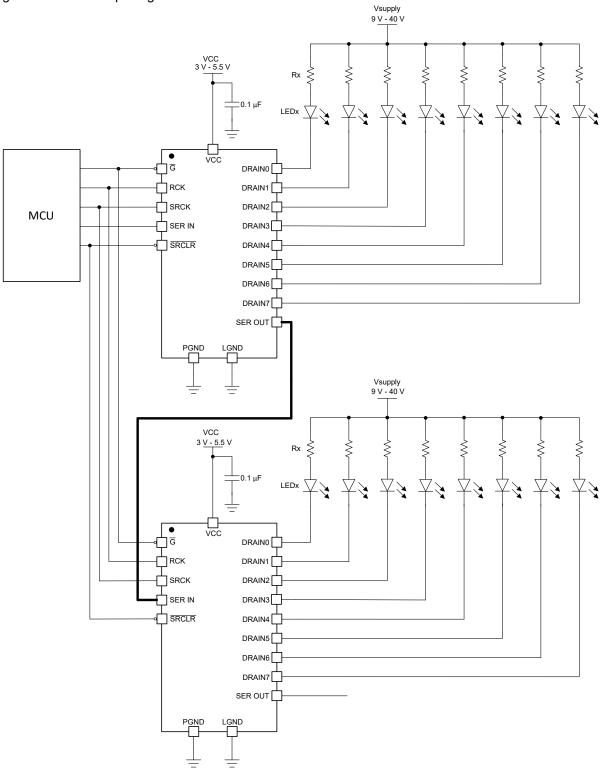

典型应用原理图

### **Table of Contents**

| gister Maps.       1         ation and Implementation       2         plication Information       2         pical Application 1       2         pical Application 2       2         pical Application 3       2         pr Supply Recommendations       2         pr       2         ayout Guidelines       2         property application       2         property Recommendations       2         property Guidelines       2         property Example       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ation and Implementation       2         plication Information       2         pical Application 1       2         pical Application 2       2         pical Application 3       2         or Supply Recommendations       2         at       2         ayout Guidelines       2         ayout Example       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| plication Information       2         pical Application 1       2         pical Application 2       2         pical Application 3       2         rr Supply Recommendations       2         ut       2         ayout Guidelines       2         ayout Example       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

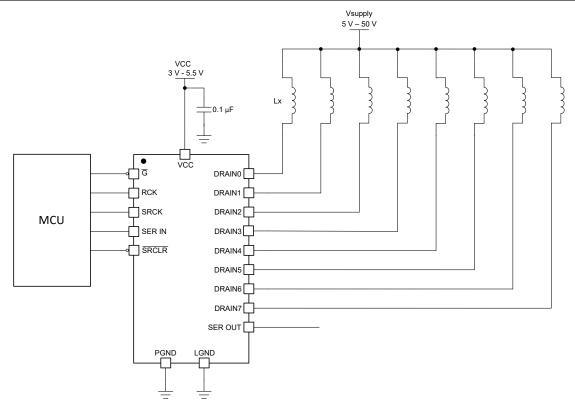

| Dical Application 1       2         Dical Application 2       2         Dical Application 3       2         Ir Supply Recommendations       2         It       2         Bayout Guidelines       2         Bayout Example       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Dical Application 2       2         Dical Application 3       2         Ir Supply Recommendations       2         It       2         Display Recommendations       2         Display Recommend |

| Dical Application 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| r Supply Recommendations 2  ut 2  ayout Guidelines 2  ayout Example 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ayout Guidelines2<br>ayout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ayout Example2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| e and Documentation Support2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 。<br>6收文档更新通知2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| rademarks2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| lectrostatic Discharge Caution2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| · 语表                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| anical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| nation2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 支<br>Ti 三<br>木<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| Changes from Revision B (December 2021) to Revision C (March 2022)                                              | Page |

|-----------------------------------------------------------------------------------------------------------------|------|

| Updated the ESD level in the <i>ESD Ratings</i> , <i>Overview</i> , and <i>Application Information</i> sections | 4    |

| Changes from Revision A (October 2021) to Revision B (December 2021)                                            | Page |

| • 从数据表中删除了所有与汽车相关的信息                                                                                            | 1    |

| Changes from Revision * (June 2021) to Revision A (October 2021)                                                | Page |

| • 将状态从"预告信息"更改为"量产数据"                                                                                           | 1    |

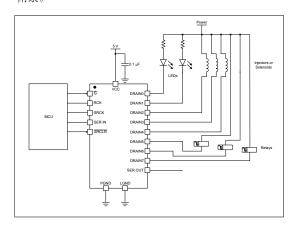

# **5 Pin Configuration and Functions**

图 5-1. DW Package 24-Pin SOIC Top View

表 5-1. Pin Functions

| PIN             |                               | I/O | DESCRIPTION                                                                                                                                                                                            |  |  |  |

|-----------------|-------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME            | NO.                           | 1/0 | DESCRIPTION                                                                                                                                                                                            |  |  |  |

| SRCLR           | 3                             | 1   | Shift register clear, active-low. The storage register transfers data to the output buffer when SRCLR is high. Driving SRCLR low clears all the registers in the device.                               |  |  |  |

| DRAIN0          | 23                            | 0   | Open-drain output                                                                                                                                                                                      |  |  |  |

| DRAIN1          | 24                            | 0   | Open-drain output                                                                                                                                                                                      |  |  |  |

| DRAIN2          | 1                             | 0   | Open-drain output                                                                                                                                                                                      |  |  |  |

| DRAIN3          | 2                             | 0   | Open-drain output                                                                                                                                                                                      |  |  |  |

| DRAIN4          | 11                            | 0   | Open-drain output                                                                                                                                                                                      |  |  |  |

| DRAIN5          | 12                            | 0   | Open-drain output                                                                                                                                                                                      |  |  |  |

| DRAIN6          | 13                            | 0   | Open-drain output                                                                                                                                                                                      |  |  |  |

| DRAIN7          | 14                            | 0   | Open-drain output                                                                                                                                                                                      |  |  |  |

| G               | 4                             | 1   | Output enable, active-low. Channel enable and disable input pin. Having $\overline{G}$ low enables all drain channels according to the output-latch register content. When high, all channels are off. |  |  |  |

| PGND            | 5, 6, 7, 8, 17,<br>18, 19, 20 | _   | Power ground, the ground reference pin for the device. This pin must connect to the ground plane on the PCB.                                                                                           |  |  |  |

| LGND            | 16                            | _   | Signal ground, the ground reference pin for the device. This pin must connect to the ground plane on the PCB.                                                                                          |  |  |  |

| RCK             | 9                             | 1   | Register clock. The data in each shift register stage transfers to the storage register at the rising edge of RCK.                                                                                     |  |  |  |

| SER IN          | 22                            | I   | Serial data input. Data on SER IN loads into the internal register on each rising edge of SRCK.                                                                                                        |  |  |  |

| SER OUT         | 15                            | 0   | Serial data output of the 8-bit serial shift register. The purpose of this pin is to cascade several devices on the serial bus.                                                                        |  |  |  |

| SRCK            | 10                            | 1   | Serial clock input. On each rising SRCK edge, data transfers from SER IN to the internal serial shift registers.                                                                                       |  |  |  |

| V <sub>CC</sub> | 21                            | I   | Power supply pin for the device. TI recommends adding a 0.1- µ F ceramic capacitor close to the pin.                                                                                                   |  |  |  |

# **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                 |                                                                              | MIN   | MAX | UNIT |

|-----------------|------------------------------------------------------------------------------|-------|-----|------|

| VCC             | Supply voltage                                                               | - 0.3 | 7   | V    |

| VI              | logic input voltage, CLR, EN, G1, G2, RCK, SER IN, SRCK                      | - 0.3 | 7   | V    |

| V <sub>DS</sub> | Power DMOS Drain-source voltage                                              | - 0.3 | 65  | V    |

| I <sub>SD</sub> | Continuous source-to-drain diode anode current                               |       | 1   | Α    |

| I <sub>SD</sub> | Pulsed source-to-drain diode anode current                                   |       | 2   | Α    |

| I <sub>D</sub>  | Pulsed drain current, each output, all outputs on, T <sub>A</sub> = 25°C     |       | 1.1 | А    |

| I <sub>D</sub>  | Continuous drain current, each output, all outputs on, T <sub>A</sub> = 25°C |       | 350 | mA   |

| I <sub>D</sub>  | Peak drain current single output, T <sub>A</sub> = 25°C                      |       | 1.1 | Α    |

| E <sub>AS</sub> | Single-pulse avalanche energy, T <sub>A</sub> = 25°C                         |       | 90  | mJ   |

| I <sub>AS</sub> | Avalanche current, T <sub>A</sub> = 25°C                                     |       | 500 | mA   |

| Operating ju    | inction temperature, T <sub>J</sub>                                          | - 55  | 150 | °C   |

| Storage tem     | nperature, T <sub>stg</sub>                                                  | - 65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                         |                                                                           | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------|-------|------|

| V                  | Electroctatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001 <sup>(1)</sup>     | ±7000 | V    |

| V <sub>(ESD)</sub> |                         | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002 <sup>(2)</sup> | ±1500 |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP155 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                    |                                                            | MIN   | NOM | MAX | UNIT |

|--------------------|------------------------------------------------------------|-------|-----|-----|------|

| V <sub>CC</sub>    | Supply voltage                                             | 3     |     | 5.5 | V    |

| I <sub>(nom)</sub> | Nominal output current                                     |       |     | 350 | mA   |

| V <sub>IH</sub>    | High-level input voltage                                   | 2.4   |     |     | V    |

| V <sub>IL</sub>    | Low-level input voltage                                    |       |     | 0.7 | V    |

| I <sub>D</sub>     | Pulsed drain output current, $T_A = 25$ °C, $V_{CC} = 5$ V | - 1.8 |     | 0.6 | А    |

| T <sub>A</sub>     | Operating ambient temperature                              | - 55  |     | 125 | °C   |

Product Folder Links: TLC6A598

### **6.4 Thermal Information**

|                        |                                              | TLC6A598     |      |

|------------------------|----------------------------------------------|--------------|------|

|                        | THERMAL METRIC(1)                            | DW (SOIC-24) | UNIT |

|                        |                                              | 24 PINS      |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 55.5         | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 29.5         | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 30.3         | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 7.3          | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 30.0         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                          | TEST CONDITIONS                                                                             | MIN | TYP  | MAX  | UNIT |

|-----------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------|-----|------|------|------|

| V <sub>(BR)DSX</sub>  | DRAIN0 to DRAIN7 Drain-to-source voltage           | I <sub>D</sub> = 1 mA                                                                       | 50  |      | 65   | V    |

| V <sub>SD</sub>       | Source-to-drain forward voltage                    | IF = 350 mA                                                                                 |     | 0.9  | 1.1  | V    |

| \/                    | High-level output voltage                          | I <sub>OH</sub> = -20 μA                                                                    | 4.9 | 4.99 |      | V    |

| V <sub>OH</sub>       | SER OUT                                            | I <sub>OH</sub> = -4 mA                                                                     | 4.5 | 4.69 |      | V    |

| \ /                   | Low-level output voltage                           | I <sub>OH</sub> = 20 μA                                                                     |     |      | 0.02 | V    |

| V <sub>OL</sub>       | SER OUT                                            | I <sub>OH</sub> = 4 mA                                                                      |     |      | 0.4  | V    |

| Ін                    | High-level input current                           | V <sub>I</sub> = 5 V                                                                        |     |      | 1    | μA   |

| I <sub>IL</sub>       | Low-level input current                            | V <sub>I</sub> = 0 V                                                                        | - 1 |      |      | μA   |

| I <sub>O(chop)</sub>  | Output current at which chopping starts            | T <sub>A</sub> = 25°C                                                                       | 0.6 | 0.8  | 1.1  | Α    |

| 1                     | l - si                                             | V <sub>CC</sub> = 5 V, All outputs off, no clock signal                                     | 180 |      | 300  |      |

| lcc                   | Logic supply current                               | V <sub>CC</sub> = 5 V, All outputs on, no clock signal                                      |     | 300  | 500  | μΑ   |

| I <sub>CC(FRQ)</sub>  | Logic supply current at frequency                  | f <sub>SRCK</sub> = 5 MHz, C <sub>L</sub> = 30 pF, all outputs on                           |     | 360  | 600  | μΑ   |

| I <sub>(nom)</sub>    | Nominal current                                    | V <sub>DS(on)</sub> = 0.5 V, T <sub>C</sub> = 85°C                                          |     | 350  |      | mA   |

|                       | Off state dusin summer                             | V <sub>DS</sub> = 40 V, T <sub>A</sub> = 25°C                                               |     |      | 1    |      |

| DSX                   | Off-state drain current                            | V <sub>DS</sub> = 40 V, T <sub>A</sub> = 125°C                                              |     |      | 1    | μA   |

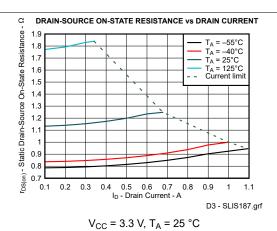

| R <sub>ds(on)</sub>   | Static drain-source on-state resistance            | V <sub>CC</sub> = 5 V, I <sub>D</sub> = 350 mA<br>Single channel on, T <sub>A</sub> = 25°C  |     | 1    | 1.5  | Ω    |

| R <sub>ds(on)</sub>   | Static drain-source on-state resistance            | $V_{CC}$ = 3.3 V, $I_D$ =350 mA<br>Single channel on, $T_A$ = 25°C                          |     | 1.1  | 1.6  | Ω    |

| R <sub>ds(on)</sub>   | Static drain-source on-state resistance            | V <sub>CC</sub> = 5 V, I <sub>D</sub> = 150 mA<br>Single channel on, T <sub>A</sub> = 125°C |     | 1.5  | 2.2  | Ω    |

| R <sub>ds(on)</sub>   | Static drain-source on-state resistance            | $V_{CC}$ = 3.3 V, $I_D$ = 150 mA<br>Single channel on, $T_A$ = 125°C                        |     | 1.6  | 2.3  | Ω    |

| I(O_S_th)             | Load open and short detection threshold            |                                                                                             | 8.5 | 15   | 25   | mA   |

| I(O_S_hys)            | Load open and short detection threshold hysteresis |                                                                                             |     | 5.7  |      | mA   |

| T <sub>SHUTDOWN</sub> | Thermal shutdown threshold                         |                                                                                             | 150 | 175  | 200  | °C   |

# **6.5 Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                   | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------|-----------------|-----|-----|-----|------|

| T <sub>HYS</sub> | Thermal shutdown hysteresis |                 |     | 18  |     | °C   |

# **6.6 Timing Requirements**

|                      |                                                            | MIN | NOM | MAX | UNIT |

|----------------------|------------------------------------------------------------|-----|-----|-----|------|

| t <sub>PLH</sub>     | Propagation delay time from G to output, low-to-high level |     | 30  |     | ns   |

| t <sub>PHL</sub>     | Propagation delay time from G to output, high-to-low level |     | 22  |     | ns   |

| t <sub>r</sub>       | Rise time, drain output                                    |     | 25  |     | ns   |

| t <sub>f</sub>       | Fall time, drain output                                    |     | 35  |     | ns   |

| t <sub>pd</sub>      | Propagation delay time, SRCK falling edge to SEROUT change |     | 10  |     | ns   |

| t <sub>or</sub>      | SEROUT rise time (10% to 90%)                              |     | 3   |     | ns   |

| t <sub>of</sub>      | SEROUT fall time (90% to 10%)                              |     | 2   |     | ns   |

| f <sub>SRCK</sub>    | Serial clock frequency                                     |     |     | 10  | MHz  |

| t <sub>SRCK_WH</sub> | SRCK pulse duration, high                                  | 30  |     |     | ns   |

| t <sub>SRCK_WL</sub> | SRCK pulse duration, low                                   | 30  |     |     | ns   |

| t <sub>su</sub>      | Setup time, SER IN high before SRCK rise                   | 10  |     |     | ns   |

| t <sub>h</sub>       | Hold time, SER IN high after SRCK rise                     | 10  |     |     | ns   |

| t <sub>w</sub>       | SER IN pulse duration                                      | 20  |     |     | ns   |

| t <sub>a</sub>       | Reverse-recovery-current rise time                         |     | 80  |     | ns   |

| t <sub>rr</sub>      | Reverse-recovery time                                      |     | 100 |     | ns   |

| t <sub>d</sub>       | Last SRCK rise to RCK rise                                 | 200 |     |     | ns   |

Product Folder Links: TLC6A598

Submit Document Feedback

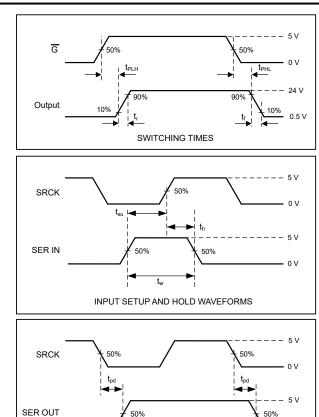

### 6.7 Timing Waveforms

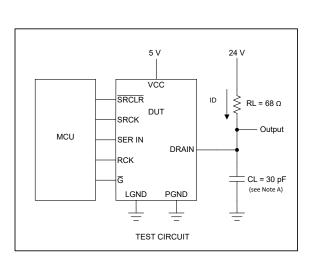

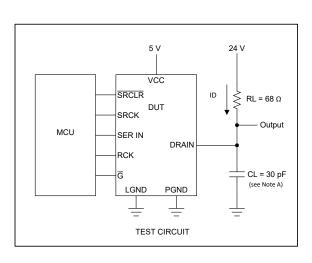

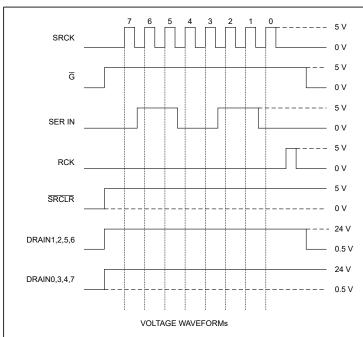

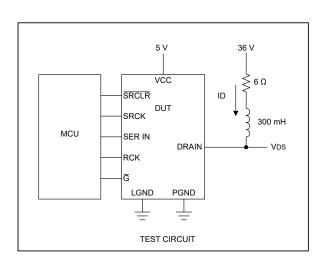

$\boxtimes$  6-1 shows the resistive-load test circuit and voltage waveforms. One can see from  $\boxtimes$  6-1 that with  $\overline{G}$  held low and  $\overline{SRCLR}$  held high, the status of each drain changes on the rising edge of the register clock, indicating the transfer of data to the output buffers at that time.

A. C<sub>L</sub> includes probe and jig capacitance.

图 6-1. Resistive Load Operation

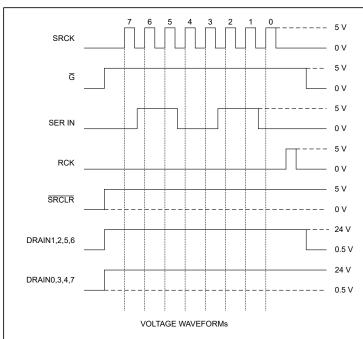

☑ 6-2 shows the SER IN to SER OUT waveform. The output signal appears on the falling edge of the shift register clock (SRCK) because there is a phase inverter at SER OUT (see the *Functional Block Diagram*). As a result, it takes seven and a half periods of SRCK for data to transfer from SER IN to SER OUT.

图 6-2. SER IN to SER OUT Waveform

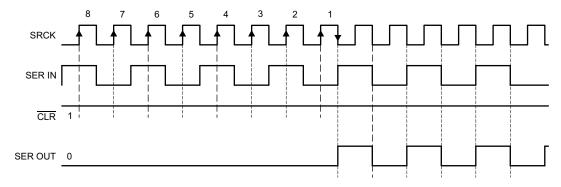

8 6-3 shows the test circuit, switching times, and voltage waveforms.

0 V

SER OUT PROPAGATION DELAY WAVEFORM

A.  $C_L$  includes probe and jig capacitance.

图 6-3. Switching Times and Voltage Waveforms

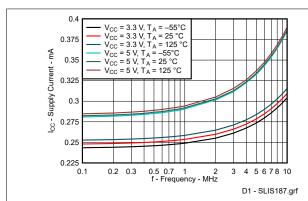

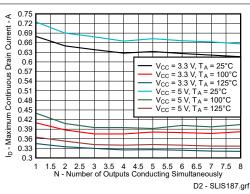

### 6.8 Typical Characteristics

图 6-4. Supply Current vs Frequency

图 6-5. Maximum Continuous Drain Current of Each Output vs Number of Outputs Conducting Simultaneously

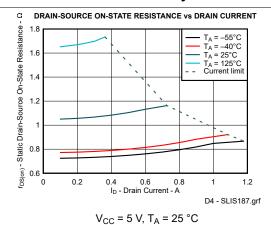

图 6-6. Static Drain-to-Source On-State Resistance vs Drain Current

图 6-7. Static Drain-to-Source On-State Resistance vs Drain Current

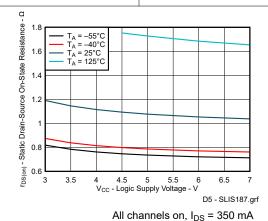

图 6-8. Static Drain-to-Source On-State Resistance vs Supply Voltage

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

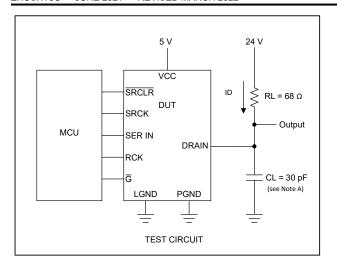

### 7 Parameter Measurement Information

$\overline{SRCLR}$  held high, the status of each drain changes on the rising edge of the register clock, indicating the transfer of data to the output buffers at that time.

A. C<sub>L</sub> includes probe and jig capacitance.

### 图 7-1. Resistive-Load Test Circuit and Voltage Waveforms

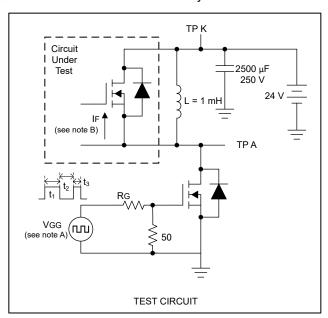

▼ 7-2 shows the reverse recovery current test circuit and waveforms of source to drain diode.

图 7-2. Reverse Recovery Current Test Circuit and Waveforms of Source to Drain Diode

Submit Document Feedback

#### 备注

A. The  $V_{GG}$  amplitude and  $R_G$  are adjusted for di/dt = 14 A/  $\mu$  s. A  $V_{GG}$  double-pulse train is used to set  $I_F$  = 0.35 A, where  $t_1$  = 10  $\mu$  s,  $t_2$  = 7  $\mu$  s, and  $t_3$  = 3  $\mu$  s.

#### 备注

B. The DRAIN terminal under test is connected to the TP K test point. All other terminals are connected together and connected to the TP A test point.

### 备注

C. I<sub>RM</sub> = maximum recovery current.

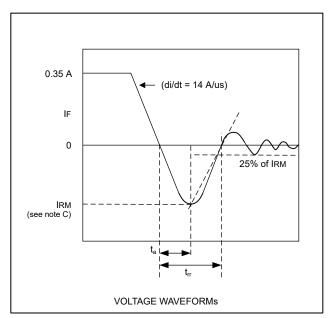

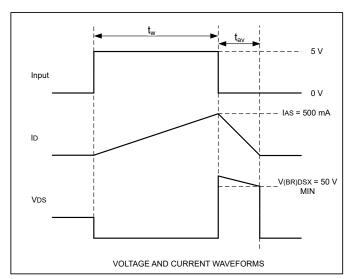

7-3 shows the single pulse avalanche energy test circuit and waveforms.

图 7-3. Single Pulse Avalanche Energy Test Circuit and Waveforms

#### 备注

A. The MCU has the following characteristics:  $t_r \leqslant$  10 ns,  $t_f \leqslant$  10 ns,  $Z_O$  = 50  $\Omega$  .

#### 备注

B. Input pulse duration, tw, is increased until peak current  $I_{AS}$  = 500 mA.

Energy test level is defined as  $E_{AS} = (I_{AS} \times V_{(BR)DSX} \times t_{av}) / 2 = 90 \text{ mJ}.$

### 8 Detailed Description

#### 8.1 Overview

The TLC6A598 device is a monolithic, high-voltage, high-current 8-bit shift register designed to drive relatively high load power such as LEDs. The device contains a built-in voltage clamp on the outputs for inductive transient protection, so it can also drive relays, solenoids, and other low-current or high-voltage loads.

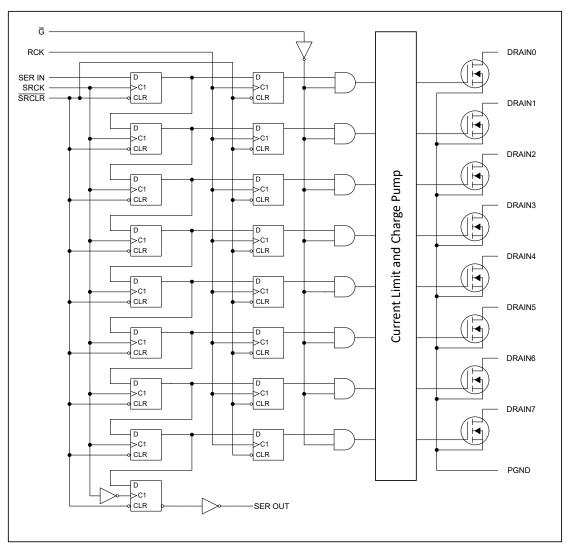

This device contains an 8-bit serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. Data transfers through both the shift and storage registers on the rising edge of the shift register clock (SRCK) and the register clock (RCK) respectively. The storage register transfers data to the output buffer when shift register clear (CLR) is high. When CLR is low, all registers in the device are cleared. When output enable (G) is held high, all data in the output buffers is held low and all drain outputs are off. When G is held low, data from the storage register transfers to the output buffers. When data in the output buffers is low, the DMOS transistor outputs are off. When data is high, the DMOS transistor outputs have sink-current capability.

The serial output (SER OUT) is clocked out of the device on the falling edge of SRCK to provide additional hold time for cascaded applications. This action provides improved performance for applications where clock signals can be skewed, devices are not located near one another, or the system must tolerate electromagnetic interference.

Outputs are low-side, open-drain DMOS transistors with output ratings of 50-V and 350-mA continuous sink-current capability. The current limit decreases as the junction temperature increases for additional device protection. The device also provides up to 7000 V of ESD protection when tested using the human body model and the 1500 V machine model.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Serial-In Interface

The TLC6A598 device contains an 8-bit serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. Data transfer through the shift and storage registers is on the rising edge of the shift register clock (SRCK) and the register clock (RCK), respectively. The storage register transfers data to the output buffer when shift-register clear (SRCLR) is high.

#### 8.3.2 Clear Registers

A logic low on the SRCLR pin clears all registers in the device. TI suggests clearing the device during power up or initialization.

#### 8.3.3 Output Channels

DRAINO - DRAIN7. These pins can survive up to 50-V LED supply voltage.

#### 8.3.4 Register Clock

RCK is the storage-register clock. Data in the storage register appears at the output whenever the output enable  $(\overline{G})$  input signal is high.

#### 8.3.5 Cascade Through SER OUT

By connecting the SER OUT pin to the SER IN input of the next device on the serial bus in cascade, the data transfers to the next device on the falling edge of SRCK. This connection can improve the cascade application reliability, as it can avoid the issue that the second device receives SRCK and data input on the same rising edge of SRCK.

#### 8.3.6 Output Control

Holding the output enable (pin  $\overline{G}$ ) high holds all data in the output buffers low, and all drain outputs are off. Holding  $\overline{G}$  low makes data from the storage register transferred to the output buffers. When data in the output buffers is low, the DMOS transistor outputs are off. When data is high, the DMOS transistor outputs are capable of sinking current. This pin also can be used for global PWM dimming.

#### 8.3.7 Clamping Structure

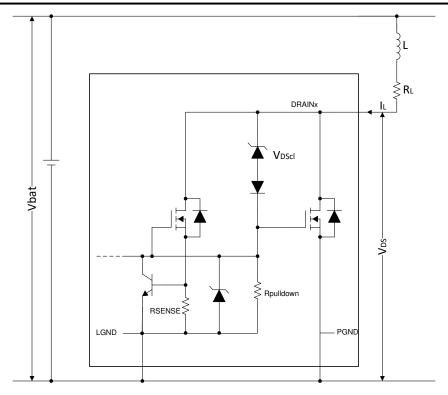

When switching off inductive loads, the potential at pin OUT rises to VDS(CL) potential, because the inductance intends to continue driving the current. The clamping voltage is necessary to prevent destruction of the device. See 8 8-1 for the clamping circuit principle. Nevertheless, the maximum allowed load inductance is limited.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

图 8-1. Output Clamp Implementation

During demagnetization of inductive loads, energy has to be dissipated in the TLC6A598. This energy can be calculated with 方程式 1:

$$E = V_{DS(CL)} \times \left[ \frac{V_{bat} - V_{DS(CL)}}{R_L} \times ln \left( 1 - \frac{R_L \times I_L}{V_{bat} - V_{DS(CL)}} \right) + I_L \right] \times \frac{L}{I_L}$$

(1)

The 方程式 2 simplifies under the assumption of  $R_L = 0$ :

$$E = \frac{1}{2} \times L \times I_L^2 \times \left(1 - \frac{V_{bat}}{V_{bat} - V_{DS(CL)}}\right)$$

(2)

The thermal design of the component limits the maximum energy, which is converted into heat.

#### 8.3.8 Protection Functions

#### 8.3.8.1 Overcurrent Protection

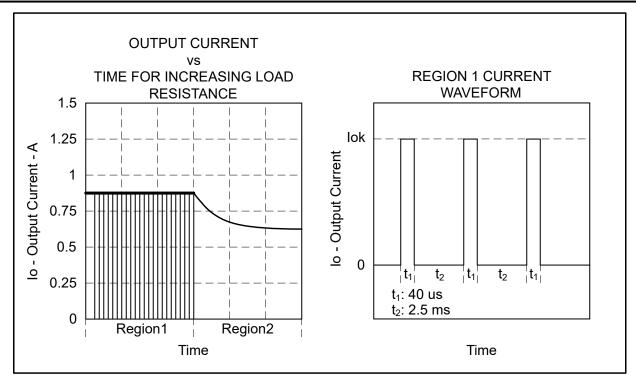

When any output is in on status (the corresponding Data Register bit is set to '1'), if the output current through the MOS is sensed to be larger than  $I_{OK}$ , it enters chopping mode as below.

8-2 illustrates the output current characteristics of the device energizing a load having initially low, increasing resistance, For example, an incandescent lamp. In region 1, chopping occurs and the peak current is limited to  $I_{O(chop)}$ . In region 2, output current is continuous. The same characteristics occur in reverse order when the device energizes a load having an initially high, decreasing resistance.

图 8-2. Chopping-Mode Characteristics

备注

Region 1 duty cycle is approximately 2%.

#### 8.3.8.2 Output Detection

When any output is in on status (the corresponding Data Register bit is set to '1'), if the current goes through any output is sensed to be lower than  $I_{OS\_th}$  mA, then an open load condition or short to ground fault is reported to the fault register while the output does not close automatically.

For the inductive load, during the on status of any output, TI recommends to read the fault regs two times. Because the inductive load leads to error detection results and it needs ignore the first time readout results during the set up process of the output current, TI recommends to read the fault regs again after the current through the load is stable.

#### 8.3.8.3 Serial Communication Error

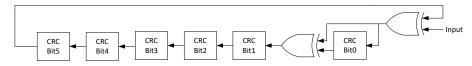

The device provides a cyclic redundancy check to verify register values in the shift registers. In read back mode, the device provides 6 bits of the CRC remainder. The MCU can read back the CRC remainder and check if the remainder is correct to determine whether the communication loop between MCU and device is good. Shift-Register Communication-Fault Detection gives a detailed description of the CRC check.

#### 8.3.8.4 Thermal Shutdown

The device implements an internal thermal shutdown to protect itself if the junction temperature exceeds 175°C (typical). The thermal shutdown forces the device to have an open state when the junction temperature exceeds the thermal trip threshold. After the junction temperature decreases below 160°C (typical), the device begins to operate again.

#### 8.3.9 Interface

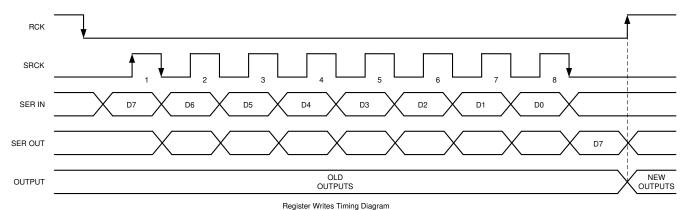

#### 8.3.9.1 Register Write

The TLC6A598 device has a 8-bit configuration register. Data transfers through the shift registers on the rising edge of SRCK and latches into the storage registers on the rising edge of RCK. The data bits control 8 opendrain outputs independently.

图 8-3. Register Write Timing Diagram

#### 8.3.9.2 Register Read

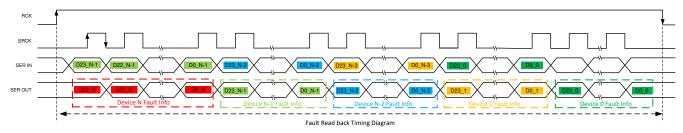

The fault information loads to shift registers on the rising edge of RCK and can be read out on SER OUT. 图 8-4 shows on the rising edge of the RCK signal, the MSB data "DRAIN7 OCP" appears on the SER OUT pin. On each falling edge of SRCK signal, there is 1 bit of data shifted out on the SER OUT pin. There is a total of 24 bits in the fault information registers. REgister Maps describes the details.

图 8-4. Register Read Timing Diagram

#### 8.3.9.3 Shift-Register Communication-Fault Detection

The TLC6A598 device provides a cyclic redundancy check to verify register values in the shift registers. In read back mode, the TLC6A598 device provides 6 bits of the CRC remainder. The MCU can read back the CRC remainder and check if the remainder is correct. The CRC checksum provides a read back method to verify shift register values without altering them.

图 8-5. CRC Check Block Diagram

The TLC6A598 device also checks the configuration register for faulty commands. The TLC6A598 configuration register consists of 8 bits. To generate the CRC checksum, the device first shifts left 6 bits and appends 0s, then bit-wise exclusive-ORs the 14 data bits with the polynomial to get the checksum.

For example, if the configuration data is 0xFF and the polynomial is 0x43 (7' b1000011), the CRC checksum is 0x0D (6' b00 1101).

The MCU can read back the CRC checksum and append it to the LSB of 8 bits, and then the 14 bits of data becomes 0x3FCD. Performing the bit-wise exclusive-OR operation with the polynomial must lead to a residual of 0.

#### 8.4 Device Functional Modes

#### 8.4.1 Operation With V<sub>CC</sub> < 3 V

This device works normally within the range 3 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V. When the operating voltage is lower than 3 V, correct behavior of the device, including communication interface and current capability, is not assured.

### 8.4.2 Operation With 5.5 V $\leq$ V<sub>CC</sub> $\leq$ 7 V

The device works normally in this voltage range, but reliability issues can occur if the device works for a long time in this voltage range.

### 8.5 Register Maps

表 8-1. Register Map

|               | 表 8-1. Register Map     |                 |                 |                 |                 |                 |                 |                 |  |  |

|---------------|-------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|--|

|               |                         |                 | CONFIG          | GURATION REG    | GISTER          |                 |                 |                 |  |  |

| Field name    | DRAIN7                  | DRAIN6          | DRAIN5          | DRAIN4          | DRAIN3          | DRAIN2          | DRAIN1          | DRAIN0          |  |  |

| Default value | 0h                      | 0h              | 0h              | 0h              | 0h              | 0h              | 0h              | 0h              |  |  |

| Bit           | 7                       | 6               | 5               | 4               | 3               | 2               | 1               | 0               |  |  |

|               | FAULT READBACK REGISTER |                 |                 |                 |                 |                 |                 |                 |  |  |

| Bit           | 23                      | 22              | 21              | 20              | 19              | 18              | 17              | 16              |  |  |

| Field name    | DRAIN7_OC<br>P          | DRAIN6_OC<br>P  | DRAIN5_OC<br>P  | DRAIN4_OC<br>P  | DRAIN3_OC<br>P  | DRAIN2_OC<br>P  | DRAIN1_OC<br>P  | DRAIN0_OC<br>P  |  |  |

| Default value | 0h                      | 0h              | 0h              | 0h              | 0h              | 0h              | 0h              | 0h              |  |  |

| Bit           | 15                      | 14              | 13              | 12              | 11              | 10              | 9               | 8               |  |  |

| Field name    | DRAIN7_Oor<br>S         | DRAIN6_Oor<br>S | DRAIN5_Oor<br>S | DRAIN4_Oor<br>S | DRAIN3_Oor<br>S | DRAIN2_Oor<br>S | DRAIN1_Oor<br>S | DRAIN0_Oor<br>S |  |  |

| Default value | 0h                      | 0h              | 0h              | 0h              | 0h              | 0h              | 0h              | 0h              |  |  |

| Bit           | 7                       | 6               | 5               | 4               | 3               | 2               | 1               | 0               |  |  |

| Field name    | TBD                     | TSD             |                 | CRC             |                 |                 |                 |                 |  |  |

| Default value | 0h                      | 0h              |                 |                 | 0               | h               |                 |                 |  |  |

#### 表 8-2 lists the memory-mapped registers for the interface.

### 表 8-2. Interface Registers

| OFFSET ACRONYM |                | REGISTER NAME           | SECTION |

|----------------|----------------|-------------------------|---------|

| 0h             | Config         | Configuration Register  |         |

| 1h             | Fault_Readback | Fault Readback Register |         |

#### 表 8-3. Interface Access Type Codes

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      |                                        |  |  |  |  |

|----------------------------------------|------|----------------------------------------|--|--|--|--|

|                                        | CODE | DESCRIPTION                            |  |  |  |  |

| Read type                              | R    | Read-only                              |  |  |  |  |

| Read to clear                          | RC   | Read to clear the fault                |  |  |  |  |

| Write                                  | W    | Write-only                             |  |  |  |  |

| Reset or Default Value                 | -n   | Value after reset or the default value |  |  |  |  |

Product Folder Links: TLC6A598

Submit Document Feedback

### 8.5.1 Configuration Register(Offset=0h)[reset=0h]

Configuration register is shown in  $\frac{1}{8}$  8-4and described in  $\frac{1}{8}$  8-5.

### 表 8-4. Configuration Register

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| DRAIN7 | DRAIN6 | DRAIN5 | DRAIN4 | DRAIN3 | DRAIN2 | DRAIN1 | DRAIN0 |

| W-0h   |

### 表 8-5. Configuration Register Field Descriptions

| Bit | Field  | Туре | Reset | Description                                                                                                                              |

|-----|--------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DRAIN7 | W    | Oh    | Open-drain output bit for DRAIN7 HIGH=Output power switch enabled LOW=Output power switch disabled                                       |

| 6   | DRAIN6 | W    | 0h    | Open-drain output bit for DRAIN6     HIGH=Output power switch enabled     LOW=Output power switch disabled                               |

| 5   | DRAIN5 | W    | 0h    | <ul> <li>Open-drain output bit for DRAIN5</li> <li>HIGH=Output power switch enabled</li> <li>LOW=Output power switch disabled</li> </ul> |

| 4   | DRAIN4 | W    | 0h    | <ul> <li>Open-drain output bit for DRAIN4</li> <li>HIGH=Output power switch enabled</li> <li>LOW=Output power switch disabled</li> </ul> |

| 3   | DRAIN3 | W    | 0h    | <ul> <li>Open-drain output bit for DRAIN3</li> <li>HIGH=Output power switch enabled</li> <li>LOW=Output power switch disabled</li> </ul> |

| 2   | DRAIN2 | W    | 0h    | <ul> <li>Open-drain output bit for DRAIN2</li> <li>HIGH=Output power switch enabled</li> <li>LOW=Output power switch disabled</li> </ul> |

| 1   | DRAIN1 | W    | 0h    | <ul> <li>Open-drain output bit for DRAIN1</li> <li>HIGH=Output power switch enabled</li> <li>LOW=Output power switch disabled</li> </ul> |

| 0   | DRAIN0 | W    | 0h    | Open-drain output bit for DRAIN0     HIGH=Output power switch enabled     LOW=Output power switch disabled                               |

# 8.5.2 Fault Readback Register(Offset=1h)[reset=0h]

Fault readback is shown in  $\frac{1}{8}$  8-6 and described in  $\frac{1}{8}$  8-7.

### 表 8-6. Fault Readback Register

| 23          | 22                  | 21          | 20          | 19          | 18          | 17          | 16          |

|-------------|---------------------|-------------|-------------|-------------|-------------|-------------|-------------|

| DRAIN7_OCP  | DRAIN6_OCP DRAIN5_C |             | DRAIN4_OCP  | DRAIN3_OCP  | DRAIN2_OCP  | DRAIN1_OCP  | DRAIN0_OCP  |

| RC-0h       | RC-0h               | RC-0h       | RC-0h       | RC-0h       | RC-0h       | RC-0h       | RC-0h       |

| 15          | 14                  | 13          | 12          | 11          | 10          | 9           | 8           |

| DRAIN7_OorS | DRAIN6_OorS         | DRAIN5_OorS | DRAIN4_OorS | DRAIN3_OorS | DRAIN2_OorS | DRAIN1_OorS | DRAIN0_OorS |

Copyright © 2022 Texas Instruments Incorporated

# 表 8-6. Fault Readback Register (continued)

|       | · · · · · · · · · · · · · · · · · · · |       |       |       |       |       |       |  |  |

|-------|---------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| 23    | 22                                    | 21    | 20    | 19    | 18    | 17    | 16    |  |  |

| RC-0h | RC-0h                                 | RC-0h | RC-0h | RC-0h | RC-0h | RC-0h | RC-0h |  |  |

| 7     | 6                                     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

| TBD   | TSD                                   |       | CRC   |       |       |       |       |  |  |

| RC-0h | RC-0h                                 |       | RC-0h |       |       |       |       |  |  |

# 表 8-7. Configuration Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                                                                                                                                                                             |

|-----|-------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23  | DRAIN7_OCP  | RC   | Oh    | <ul> <li>Over current fault flag for DRAIN7, read to clear the fault</li> <li>HIGH=Over current fault detected</li> <li>LOW=Over current fault not detected</li> </ul>                                  |

| 22  | DRAIN6_OCP  | RC   | Oh    | <ul> <li>Over current fault flag for DRAIN6, read to clear the fault</li> <li>HIGH=Over current fault detected</li> <li>LOW=Over current fault not detected</li> </ul>                                  |

| 21  | DRAIN5_OCP  | RC   | Oh    | <ul> <li>Over current fault flag for DRAIN5, read to clear the fault</li> <li>HIGH=Over current fault detected</li> <li>LOW=Over current fault not detected</li> </ul>                                  |

| 20  | DRAIN4_OCP  | RC   | Oh    | <ul> <li>Over current fault flag for DRAIN4, read to clear the fault</li> <li>HIGH=Over current fault detected</li> <li>LOW=Over current fault not detected</li> </ul>                                  |

| 19  | DRAIN3_OCP  | RC   | Oh    | <ul> <li>Over current fault flag for DRAIN3, read to clear the fault</li> <li>HIGH=Over current fault detected</li> <li>LOW=Over current fault not detected</li> </ul>                                  |

| 18  | DRAIN2_OCP  | RC   | Oh    | <ul> <li>Over current fault flag for DRAIN2, read to clear the fault</li> <li>HIGH=Over current fault detected</li> <li>LOW=Over current fault not detected</li> </ul>                                  |

| 17  | DRAIN1_OCP  | RC   | Oh    | <ul> <li>Over current fault flag for DRAIN1, read to clear the fault</li> <li>HIGH=Over current fault detected</li> <li>LOW=Over current fault not detected</li> </ul>                                  |

| 16  | DRAIN0_OCP  | RC   | Oh    | <ul> <li>Over current fault flag for DRAIN0, read to clear the fault</li> <li>HIGH=Over current fault detected</li> <li>LOW=Over current fault not detected</li> </ul>                                  |

| 15  | DRAIN7_OorS | RC   | 0h    | <ul> <li>Open or short to ground fault flag for DRAIN7, read to clear the fault</li> <li>HIGH=Open or short to ground fault detected</li> <li>LOW=Open or short to ground fault not detected</li> </ul> |

| 14  | DRAIN6_OorS | RC   | 0h    | <ul> <li>Open or short to ground fault flag for DRAIN6, read to clear the fault</li> <li>HIGH=Open or short to ground fault detected</li> <li>LOW=Open or short to ground fault not detected</li> </ul> |

Product Folder Links: TLC6A598

表 8-7. Configuration Register Field Descriptions (continued)

| Bit   Field   Type   Reset   Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>D</b> '' | 表 8-7. Configuration Register Field Descriptions (continued) |      |       |                                                         |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------|------|-------|---------------------------------------------------------|--|--|--|--|--|

| the fault  HIGH=Open or short to ground fault detected  LOW=Open or short to ground fault not detected  DRAIN4_OorS  RC  Oh  Open or short to ground fault flag for DRAIN4, read to clear the fault  HIGH=Open or short to ground fault flag for DRAIN4, read to clear the fault  HIGH=Open or short to ground fault flag for DRAIN3, read to clear the fault  HIGH=Open or short to ground fault detected  DRAIN3_OorS  RC  Oh  Open or short to ground fault flag for DRAIN3, read to clear the fault  HIGH=Open or short to ground fault detected  LOW=Open or short to ground fault detected  LOW=Open or short to ground fault detected  LOW=Open or short to ground fault detected  DRAIN2_OorS  RC  Oh  Open or short to ground fault flag for DRAIN2, read to clear the fault  HIGH=Open or short to ground fault detected  LOW=Open or short to ground fault datected  The fault  HIGH=Open or short to ground fault detected  The fault  HIGH=Open or short to ground fault detected  The fault  HIGH=Open or short to ground fault detected  COW=Open or short to ground fault detected  The fault  HIGH=Open or short to ground fault detected  COW=Open or short to ground fault detected  COW=Op | Bit         | Field                                                        | Туре | Reset | Description                                             |  |  |  |  |  |

| the fault  HIGH=Open or short to ground fault detected  LOW=Open or short to ground fault not detected  DRAIN3_OorS  RC  Oh  Open or short to ground fault flag for DRAIN3, read to clear the fault  HIGH=Open or short to ground fault flag for DRAIN3, read to clear the fault  HIGH=Open or short to ground fault flag for DRAIN2, read to clear the fault  HIGH=Open or short to ground fault detected  DRAIN2_OorS  RC  Oh  Open or short to ground fault detected  LOW=Open or short to ground fault not detected  Open or short to ground fault flag for DRAIN1, read to clear the fault  HIGH=Open or short to ground fault flag for DRAIN1, read to clear the fault  HIGH=Open or short to ground fault detected  DRAIN0_OorS  RC  Oh  Open or short to ground fault flag for DRAIN1, read to clear the fault  HIGH=Open or short to ground fault not detected  COW=Open or short to ground fault not detected  LOW=Open or short to ground fault not detected  TOPEN OPEN OPEN OPEN OPEN OPEN OPEN OPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13          | DRAIN5_OorS                                                  | RC   | 0h    | the fault HIGH=Open or short to ground fault detected   |  |  |  |  |  |

| the fault  DRAIN2_OorS  RC  Oh  Open or short to ground fault detected  LOW=Open or short to ground fault not detected  DRAIN1_OorS  RC  Oh  Open or short to ground fault flag for DRAIN2, read to clear the fault  HIGH=Open or short to ground fault not detected  DRAIN1_OorS  RC  Oh  Open or short to ground fault flag for DRAIN1, read to clear the fault  HIGH=Open or short to ground fault flag for DRAIN1, read to clear the fault  HIGH=Open or short to ground fault detected  DRAIN0_OorS  RC  Oh  Open or short to ground fault flag for DRAIN1, read to clear the fault  HIGH=Open or short to ground fault not detected  DRAIN0_OorS  RC  Oh  Open or short to ground fault flag for DRAIN0, read to clear the fault  HIGH=Open or short to ground fault detected  LOW=Open or short to ground fault not detected  TOW=Open or short to ground fault not detected  COW=Open or short to ground fault not detected  TOW=Open or short to ground fault not detected  COW=Open or short to ground fault not det | 12          | DRAIN4_OorS                                                  | RC   | 0h    | the fault • HIGH=Open or short to ground fault detected |  |  |  |  |  |

| by the fault    HIGH=Open or short to ground fault not detected   LOW=Open or short to ground fault flag for DRAIN1, read to clear the fault   HIGH=Open or short to ground fault flag for DRAIN1, read to clear the fault   HIGH=Open or short to ground fault detected   LOW=Open or short to ground fault not detected   LOW=Open or short to ground fault flag for DRAIN0, read to clear the fault   HIGH=Open or short to ground fault flag for DRAIN0, read to clear the fault   HIGH=Open or short to ground fault not detected   LOW=Open or short to ground fault not detected   COW=Open or short to ground fault not detected   LOW=Open or short to ground fault not detected   COW=Open or short to ground fault flag for DRAIN0, read to clear the fault   HIGH=Thermal shutdown detected   LOW=Thermal shutdown not detected   | 11          | DRAIN3_OorS                                                  | RC   | 0h    | the fault • HIGH=Open or short to ground fault detected |  |  |  |  |  |

| the fault  HIGH=Open or short to ground fault detected  LOW=Open or short to ground fault not detected  B DRAINO_OorS  RC  Oh  Open or short to ground fault flag for DRAINO, read to clear the fault  HIGH=Open or short to ground fault detected  LOW=Open or short to ground fault not detected  TBD  RC  Oh  TBD  RC  Oh  TBD  RC  Oh  Thermal-shutdown detection flag, read to clear the fault  HIGH = Thermal shutdown detected  LOW = Thermal shutdown not detected  CRC  CRC  R  Oh  CRC checksum of configuration registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10          | DRAIN2_OorS                                                  | RC   | 0h    | the fault  HIGH=Open or short to ground fault detected  |  |  |  |  |  |