# 3-Channel Low Power SDTV Video Amplifier with I<sup>2</sup>C Control, 6-dB Gain, SAG Correction, 2:1 Input MUX, and Selectable Input Bias Modes

#### **FEATURES**

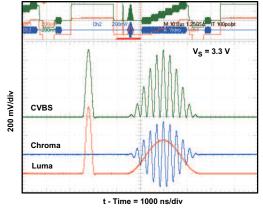

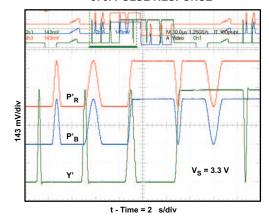

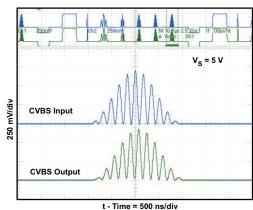

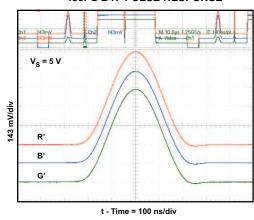

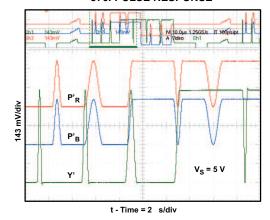

- 3 SDTV Video Amplifiers for CVBS, S-Video, Y'P'<sub>R</sub>P'<sub>R</sub> 480i/576i, or G'B'R' Video Systems

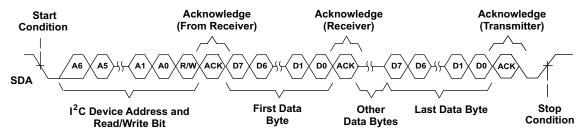

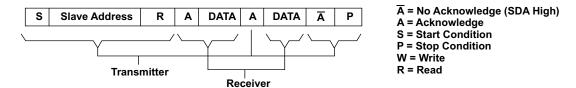

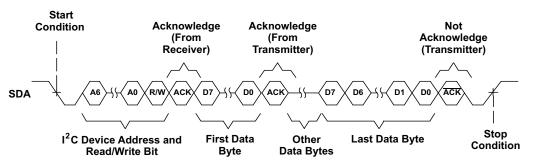

- I<sup>2</sup>C<sup>™</sup> Control of All Functions on Each Channel

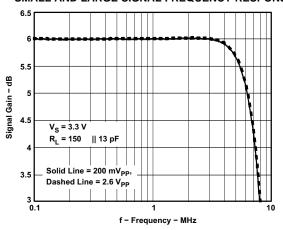

- Integrated Low-Pass Filters

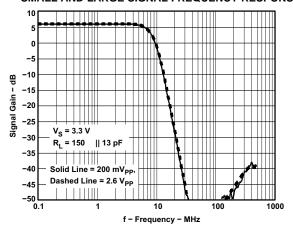

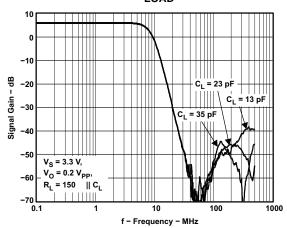

- 5<sup>th</sup> Order, 8-MHz Butterworth

- 0.5-dB Attenuation at 5.5 MHz

- 48-dB Attenuation at 27 MHz

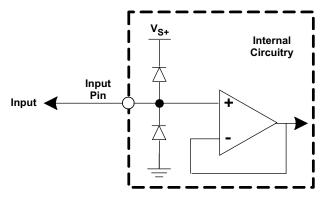

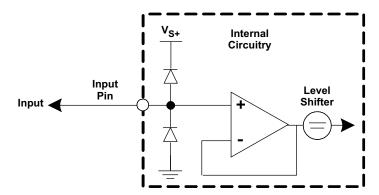

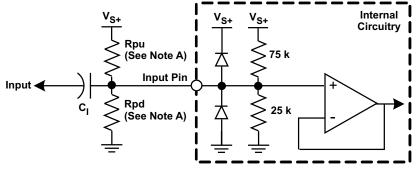

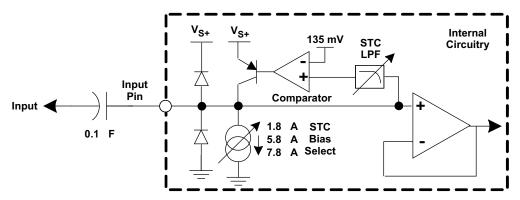

- Selectable Input Bias Modes

- AC-Coupled with Sync-Tip Clamp

- AC-Coupled with Bias

- DC-Coupled with 135-mV Input Shift

- DC-Coupled

- 2:1 Input MUX Allows Multiple Input Sources

- Built-in 6-dB Gain (2 V/V)

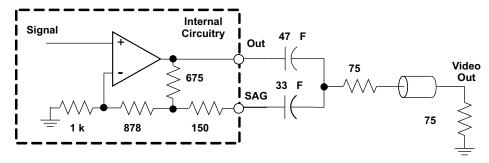

- SAG Correction Capable

- 2.7-V to 5-V Single Supply Operation

- Individual Disable (<1 μA) and Mute Control

- Rail-to-Rail Output:

- Output Swings within 100 mV from the Rails

Which Allows AC or DC Output Coupling

- Able to Drive up to 2 Video Lines 75  $\Omega$

- Low 16.6-mA (3.3 V) Total Quiescent Current

- Low Differential Gain/Phase of 0.07% / 0.12°

#### **APPLICATIONS**

- Set Top Box Output Video Buffering

- PVR/DVDR Output Buffering

- USB/Portable Low Power Video Buffering

#### DESCRIPTION

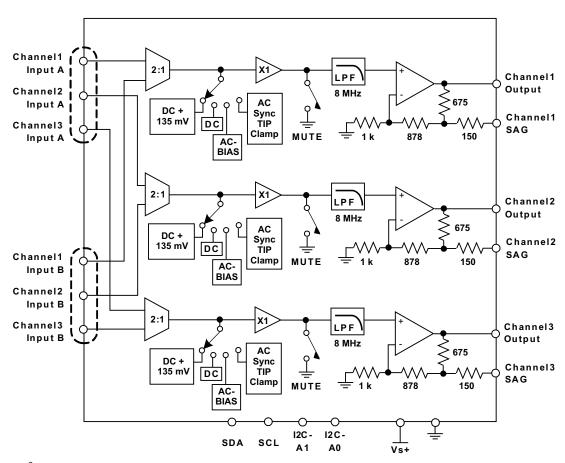

Fabricated using the new complimentary silicon-germanium (SiGe) BiCom-III process, the THS7313 is a low-power, single-supply 2.7-V to 5-V, 3-channel integrated video buffer. It incorporates a 5<sup>th</sup> order Butterworth filter which is useful as a digital-to-analog converter (DAC) reconstruction filter or an analog-to-digital converter (ADC) anti-aliasing filter. The 8-MHz filter is a perfect choice for SDTV video which includes composite (CVBS), S-Video, Y'U'V', G'B'R', and Y'P'<sub>B</sub>P'<sub>R</sub> 480i/576i.

Each channel of the THS7313 is individually I<sup>2</sup>C configurable for all functions which makes it flexible for any application. Its rail-to-rail output stage allows for both ac and dc coupling applications. The 6-dB gain along with the built-in SAG correction allows for maximum flexibility as an output video buffer.

The 16.6 mA total quiescent current at 3.3 V (55 mW) makes it an excellent choice for USB powered or portable video applications. While fully disabled, the THS7313 consumes less than 1  $\mu$ A.

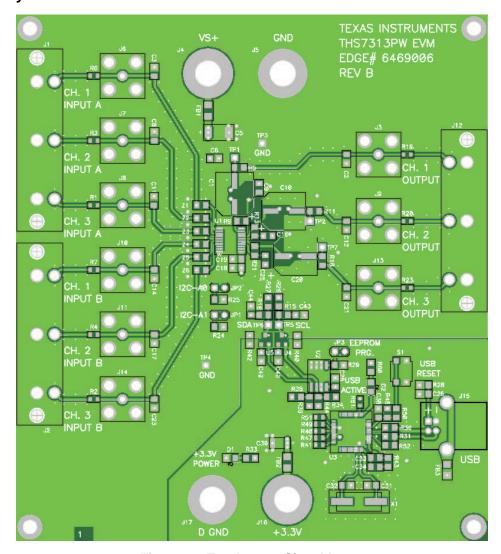

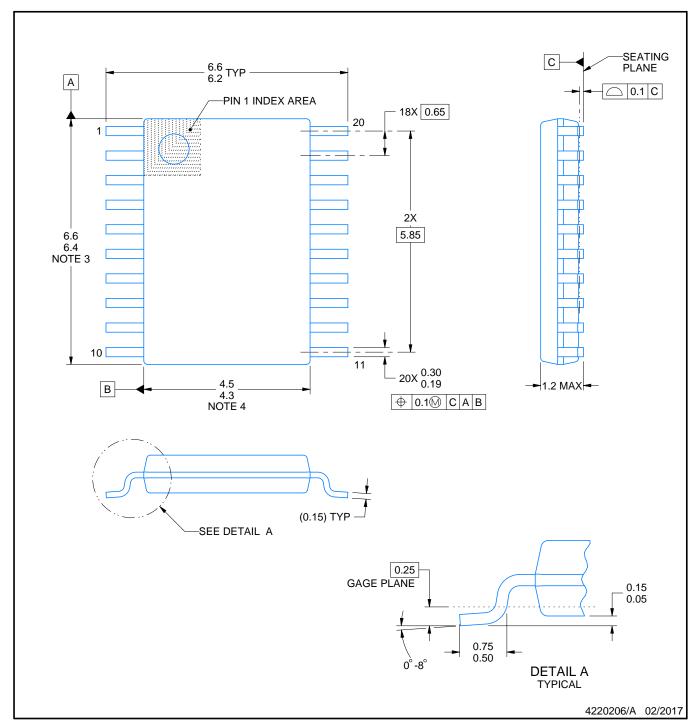

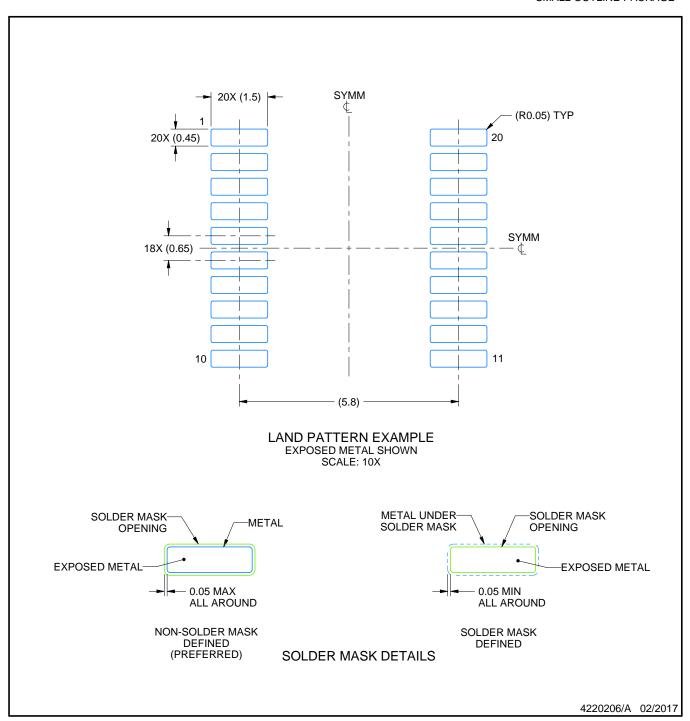

The THS7313 is available in a small lead-free and RoHS compliant TSSOP-20 package.

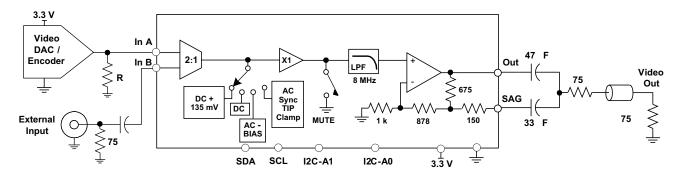

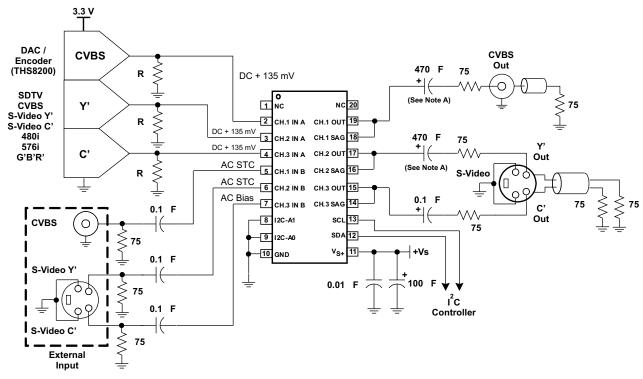

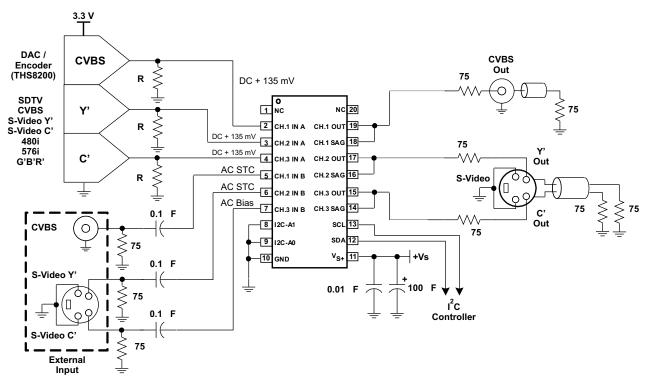

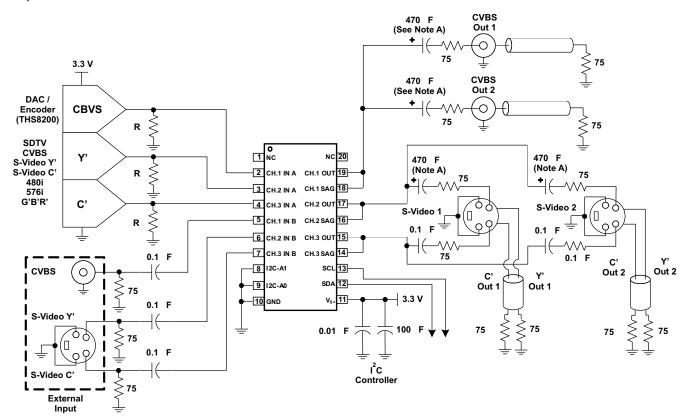

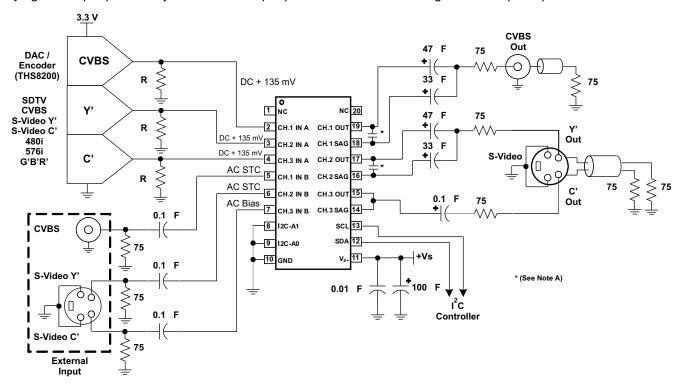

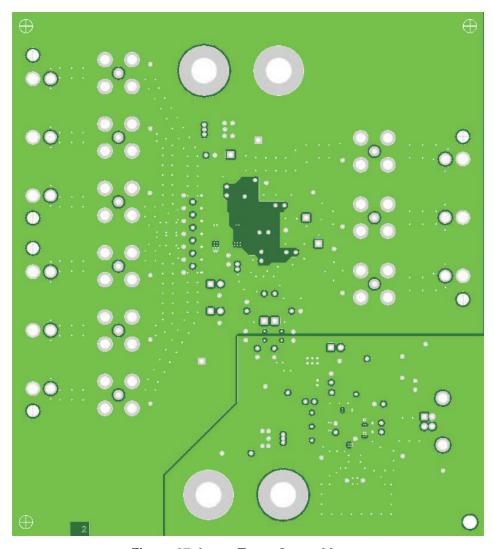

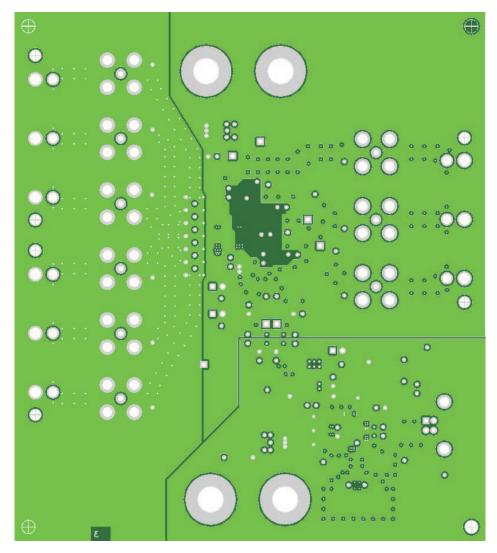

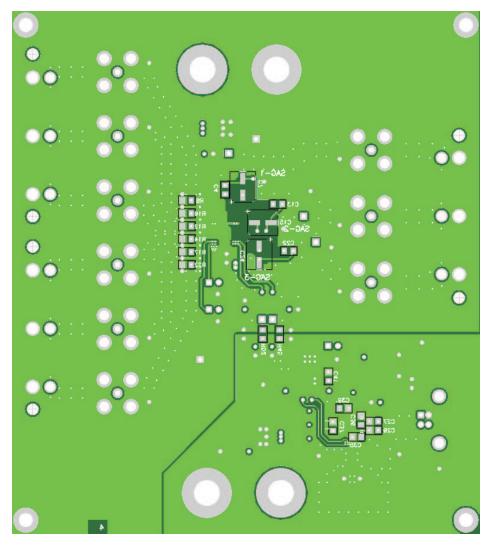

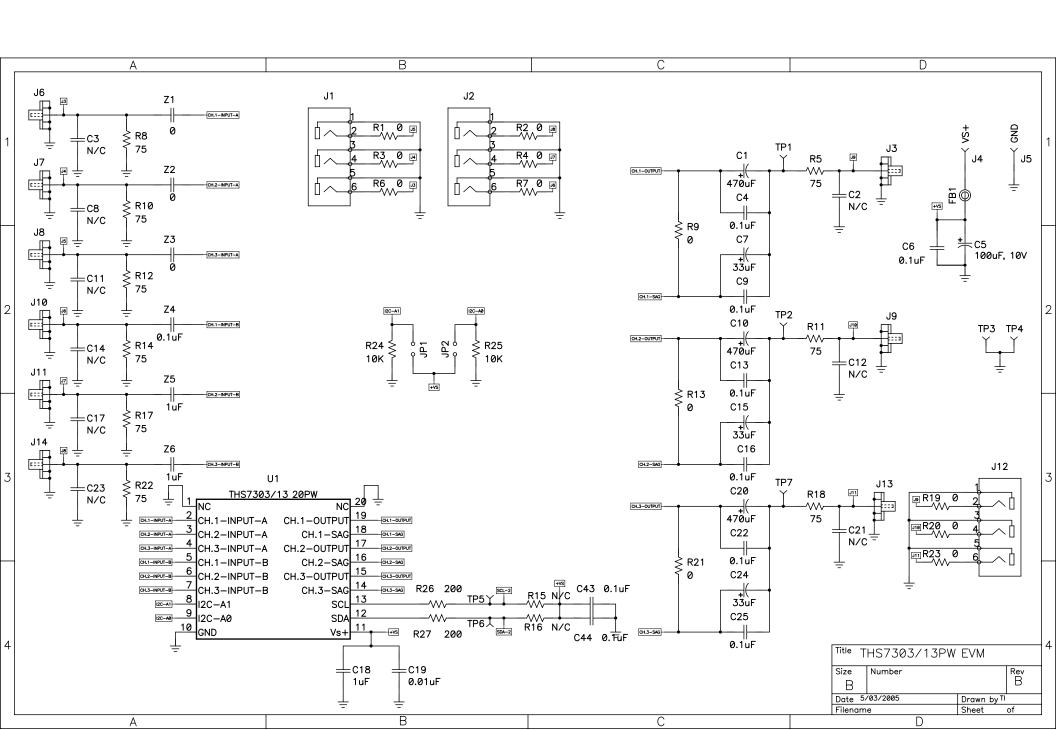

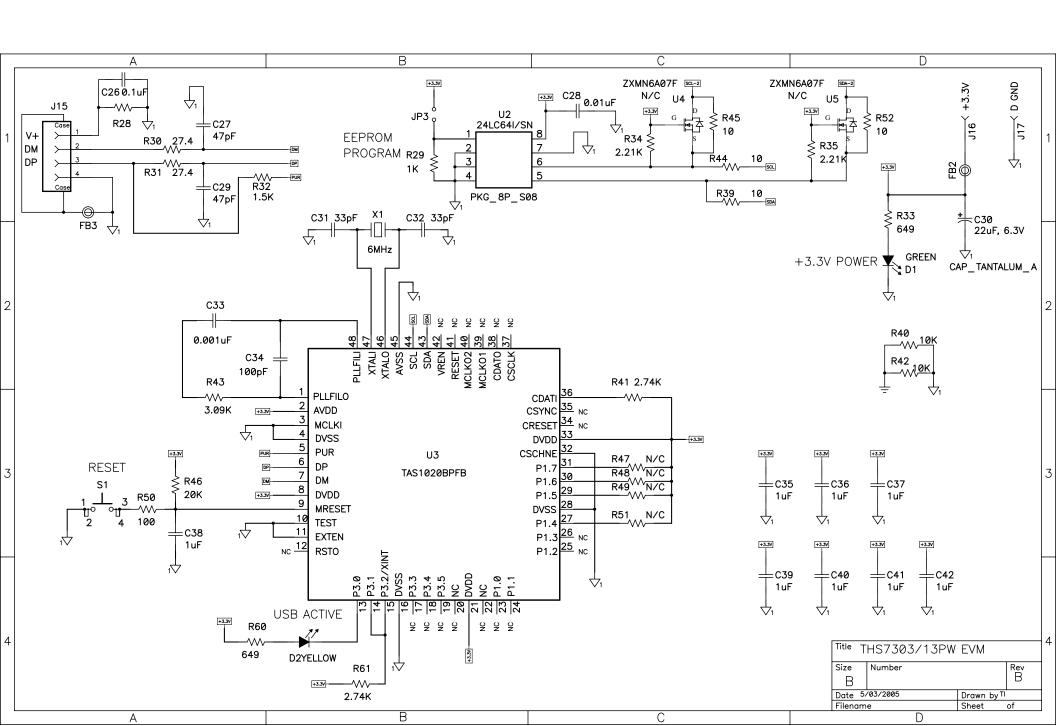

Figure 1. 3.3 V Single-Supply DC-Input/AC-Video Output System w/SAG Correction (1 of 3 Channels Shown)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

I<sup>2</sup>C is a trademark of Philips Electronics.

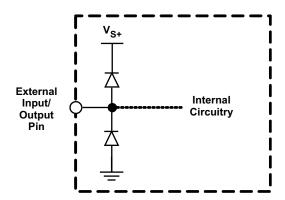

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **DESCRIPTION (CONTINUED)**

As part of the THS7313 flexibility, the 2:1 MUX input can be selected for ac or dc coupled inputs. The ac coupled modes include a sync-tip clamp option for CVBS or Y' signals, or a fixed bias for the  $C/P'_B/P'_R$  channels. The dc input options include a dc input or a dc + 135-mV input offset shift to allow for a full sync dynamic range at the output with 0-V input.

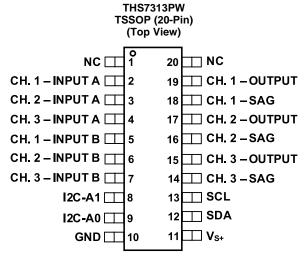

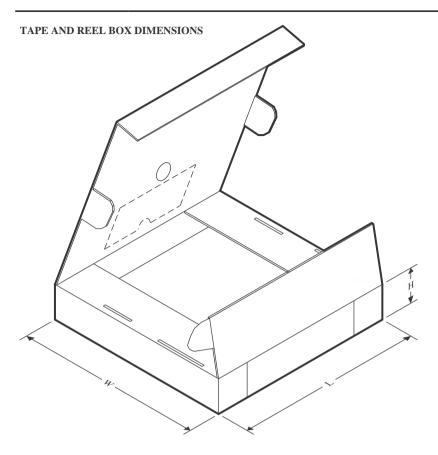

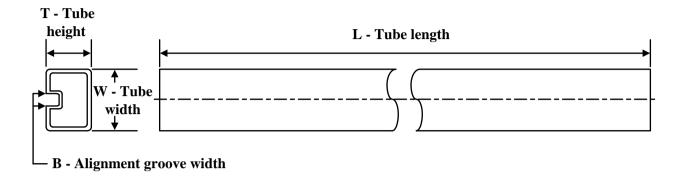

#### PACKAGING/ORDERING INFORMATION

| PACKAGED DEVICES(1) | PACKAGE TYPE | TRANSPORT MEDIA,<br>QUANTITY |

|---------------------|--------------|------------------------------|

| THS7313PW           | TSSOP-20     | Rails, 70                    |

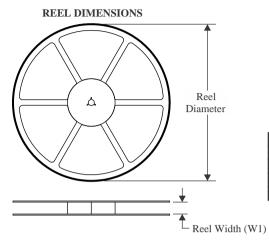

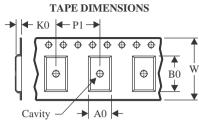

| THS7313PWR          | 1850P-20     | Tape and reel, 2000          |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                |                                                                              | UNIT                         |

|------------------|----------------|------------------------------------------------------------------------------|------------------------------|

| V <sub>SS</sub>  | Supply voltage | e, V <sub>S+</sub> to GND                                                    | 5.5 V                        |

| VI               | Input voltage  |                                                                              | −0.4V to V <sub>S+</sub>     |

| Io               | Output current |                                                                              | ±125 mA                      |

|                  | Continuous po  | ower dissipation                                                             | See Dissipation Rating Table |

| TJ               | Maximum junc   | tion temperature, any condition <sup>(2)</sup>                               | 150°C                        |

| T <sub>J</sub>   | Maximum junc   | tion temperature, continuous operation, long term reliability <sup>(3)</sup> | 125°C                        |

| T <sub>stg</sub> | Storage tempe  | erature range                                                                | −65°C to 150°C               |

|                  | Lead temperat  | ture 1,6 mm (1/16 inch) from case for 10 seconds                             | 300°C                        |

|                  |                | НВМ                                                                          | 2000 V                       |

|                  | ESD ratings    | CDM                                                                          | 750 V                        |

|                  |                | MM                                                                           | 100 V                        |

<sup>(1)</sup> Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied Exposure to absolute maximum rated conditions for extended periods may degrade device reliability.

#### **DISSIPATION RATINGS**

| PACKAGE         | θ <sub>JC</sub><br>(° <b>C/W</b> ) | θJA<br>(°C/W)     | POWER RATING <sup>(1)</sup><br>(T <sub>J</sub> = 125°C) |                       |  |

|-----------------|------------------------------------|-------------------|---------------------------------------------------------|-----------------------|--|

|                 | (°C/VV)                            |                   | T <sub>A</sub> = 25°C                                   | T <sub>A</sub> = 85°C |  |

| TSSOP - 20 (PW) | 32.3                               | 83 <sup>(2)</sup> | 1.2 W                                                   | 0.48 W                |  |

<sup>(1)</sup> Power rating is determined with a junction temperature of 125°C. This is the point where distortion starts to substantially increase and long-term reliability starts to be reduced. Thermal management of the final PCB strives to keep the junction temperature at or below 125°C for best performance and reliability.

<sup>(2)</sup> The absolute maximum junction temperature under any condition is limited by the constraints of the silicon process.

<sup>(3)</sup> The absolute maximum junction temperature for continuous operation is limited by the package constraints. Operation above this temperature may result in reduced reliability and/or lifetime of the device.

<sup>(2)</sup> This data was taken with the JEDEC High-K test PCB. For the JEDEC low-K test PCB, the θ<sub>IA</sub> is 125.8°C.

#### RECOMMENDED OPERATING CONDITIONS

|          |                                 | MIN | NOM MAX | UNIT |

|----------|---------------------------------|-----|---------|------|

| $V_{SS}$ | Supply voltage, V <sub>S+</sub> | 2.7 | 5       | V    |

| $T_A$    | Ambient temperature             | -40 | 85      | °C   |

# ELECTRICAL CHARACTERISTICS, $V_{S+} = 3.3 \text{ V}$

$R_L$  = 150  $\Omega$  to GND, Input Bias = dc, SAG pin shorted to the output pin (unless otherwise noted)

|                                               |                                                     | TYP             | TYP OVERTEMPERATURE |             |                  |       |         |  |

|-----------------------------------------------|-----------------------------------------------------|-----------------|---------------------|-------------|------------------|-------|---------|--|

| PARAMETER                                     | TEST CONDITIONS                                     | 25°C            | 25°C                | 0°C to 70°C | –40°C to<br>85°C | UNITS | MIN/MAX |  |

| AC PERFORMANCE                                |                                                     |                 |                     | 1           |                  |       |         |  |

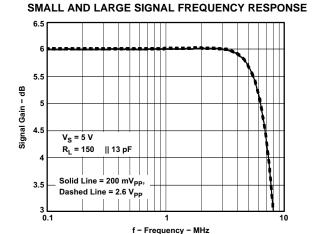

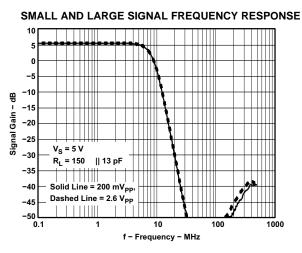

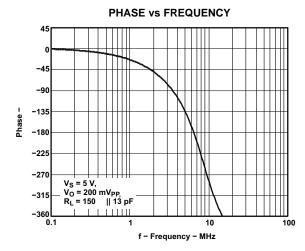

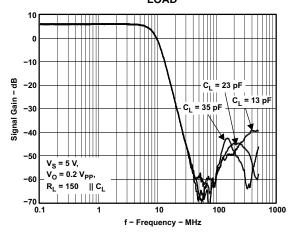

| Small-signal bandwidth<br>(–3 dB)             | V <sub>O</sub> - 0.2 V <sub>PP</sub> <sup>(1)</sup> | 8               | 6.7/9.3             | 6.55/9.45   | 6.5/9.5          | MHz   | Min/Max |  |

| Large-signal bandwidth<br>(–3 dB)             | V <sub>O</sub> - 2 V <sub>PP</sub> <sup>(1)</sup>   | 8               |                     |             |                  | MHz   |         |  |

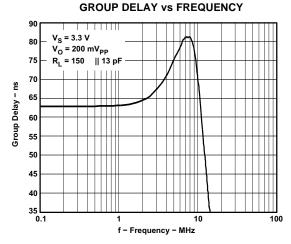

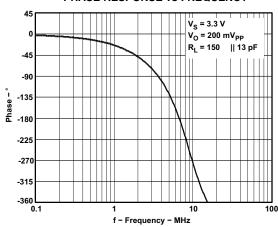

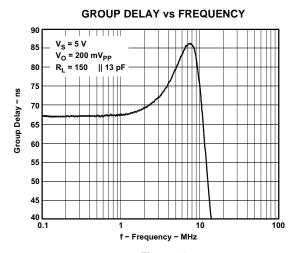

| Group delay                                   | f = 100 kHz                                         | 63              |                     |             |                  | ns    |         |  |

| Group delay variation with respect to 100 kHz | f = 5.1 MHz                                         | 13              |                     |             |                  | ns    |         |  |

| Group delay matching                          | Channel-to-Channel                                  | 0.5             |                     |             |                  | ns    |         |  |

| Attenuation with respect to                   | f = 5.75 MHz                                        | 0.5             | -0.2 / 2            | -0.4 / 2.2  | -0.5 / 2.3       | dB    | Min/Max |  |

| 100 kHz                                       | f = 27 MHz                                          | 48              | 36                  | 35          | 34               | dB    | Min     |  |

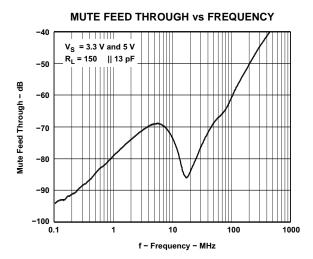

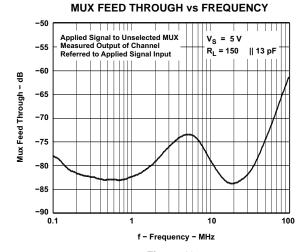

| Mute feed-thru                                | f = 1 MHz                                           | -80             |                     |             |                  | dB    |         |  |

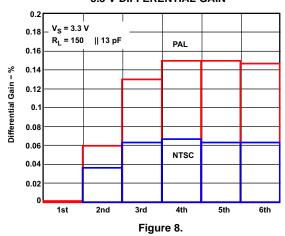

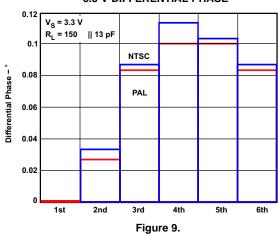

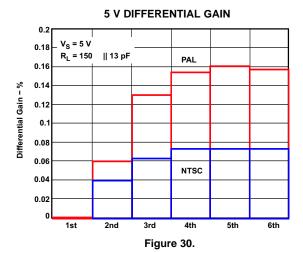

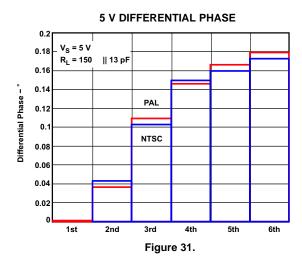

| Differential gain                             | NTSC/PAL                                            | 0.07%/0.15<br>% |                     |             |                  |       |         |  |

| Differential phase                            | NTSC/PAL                                            | 0.12°/0.1°      |                     |             |                  |       |         |  |

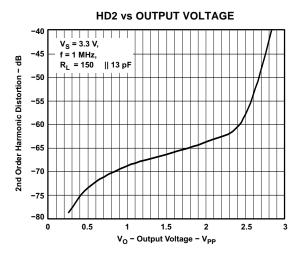

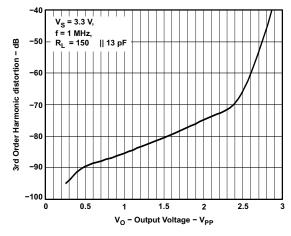

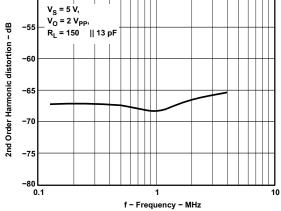

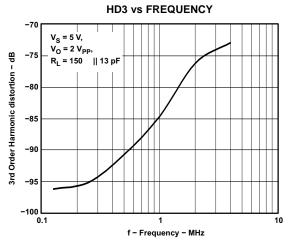

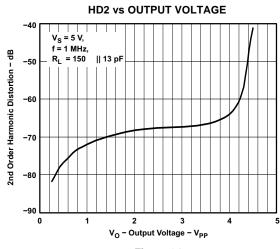

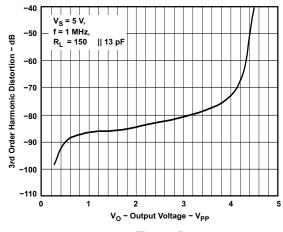

| Total harmonic distortion                     | f = 1 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>       | -62             |                     |             |                  | dB    |         |  |

| Signal to noise ratio                         | Unified weighting 100 kHz to 6 MHz                  | 82              |                     |             |                  | dB    |         |  |

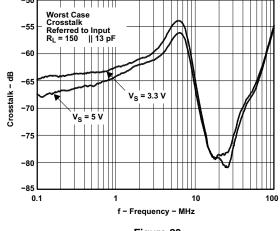

| Channel-to-Channel crosstalk                  | f = 1 MHz                                           | -63             |                     |             |                  | dB    |         |  |

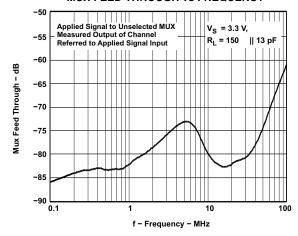

| MUX Isolation                                 | f = 5.1 MHz                                         | 73              |                     |             |                  | dB    |         |  |

| AC gain – All channels                        | f = 100 kHz                                         | 6               | 5.7/6.3             | 5.65/6.35   | 5.65/6.35        | dB    | Min/Max |  |

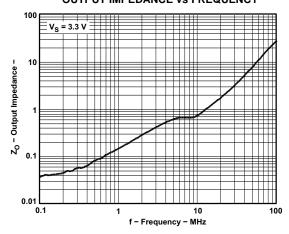

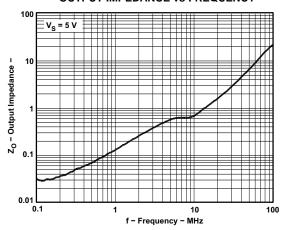

| Output impedance                              | f = 10 MHz                                          | 0.75            |                     |             |                  | Ω     |         |  |

| DC PERFORMANCE                                |                                                     |                 |                     |             |                  |       |         |  |

| Output offset voltage                         | Bias = dc                                           | 35              | 90                  | 95          | 95               | mV    | Max     |  |

| Average offset voltage drift                  | Bias = dc                                           |                 |                     |             | 20               | μV/°C |         |  |

| D:ttt                                         | Bias = dc + 135 mV, V <sub>I</sub> = 0 V            | 290             | 235/345             | 215/360     | 200/375          | mV    | Min/Max |  |

| Bias output voltage                           | Bias = ac                                           | 1.65            | 1.5/1.8             | 1.45/1.85   | 1.45/1.85        | V     | Min/Max |  |

| Sync tip clamp output voltage                 | Bias = ac STC                                       | 290             | 210/370             | 200/380     | 195/385          | mV    | Min/Max |  |

| Input bias current                            | Bias = dc - implies lb out of the pin               | -0.6            | -4                  | -5          | -5               | μΑ    | Max     |  |

| Average bias current drift                    | Bias = dc                                           |                 |                     |             | 10               | nA/°C |         |  |

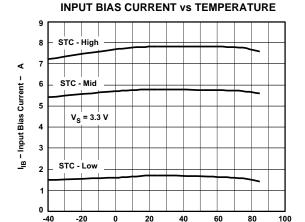

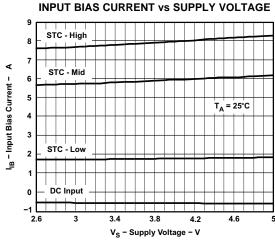

|                                               | Bias = ac STC, Low bias                             | 1.8             | 0.6/3.3             | 0.5/3.5     | 0.4/3.6          | μА    | Min/Max |  |

| Sync tip clamp bias current                   | Bias = ac STC, Mid bias                             | 5.8             | 4.3/8.2             | 4.1/8.4     | 4/8.5            | μА    | Min/Max |  |

|                                               | Bias = ac STC, High bias                            | 7.8             | 6.2/10.8            | 6/11        | 5.9/11.1         | μА    | Min/Max |  |

| INPUT CHARACTERISTICS                         |                                                     |                 |                     |             |                  |       |         |  |

| Input voltage range                           | Bias = dc - limited by output                       | 0/1.57          | 0/1.52              | 0/1.47      | 0/1.47           | V     | Min/Max |  |

|                                               | Bias = ac bias mode                                 | 19              |                     |             |                  | kΩ    |         |  |

| Input resistance                              | Bias = dc, dc + 135 mV, ac STC                      | 3               |                     |             |                  | MΩ    |         |  |

| Input capacitance                             |                                                     | 2               |                     |             |                  | pF    |         |  |

| OUTPUT CHARACTERISTI                          | cs                                                  |                 |                     | <u> </u>    |                  |       |         |  |

|                                               | $R_L = 150 \Omega$ to Midrail                       | 3.15            | 2.9                 | 2.8         | 2.8              | V     | Min     |  |

| High output valtage code =                    | $R_L = 150 \Omega$ to GND                           | 3.05            | 2.85                | 2.75        | 2.75             | V     | Min     |  |

| High output voltage swing                     | $R_L = 75 \Omega$ to Midrail                        | 3.05            | 2.8                 | 2.7         | 2.7              | V     | Min     |  |

|                                               | $R_L = 75 \Omega$ to GND                            | 2.9             | 2.65                | 2.55        | 2.55             | V     | Min     |  |

<sup>(1)</sup> The Min/Max values listed are specified by design only.

# ELECTRICAL CHARACTERISTICS, $V_{S+} = 3.3 \text{ V}$ (continued)

$R_L$  = 150  $\Omega$  to GND, Input Bias = dc, SAG pin shorted to the output pin (unless otherwise noted)

|                                        |                                                         | TYP  | OVERTEMPERATURE |             |                  |       |         |  |

|----------------------------------------|---------------------------------------------------------|------|-----------------|-------------|------------------|-------|---------|--|

| PARAMETER                              | TEST CONDITIONS                                         | 25°C | 25°C            | 0°C to 70°C | –40°C to<br>85°C | UNITS | MIN/MAX |  |

|                                        | $R_L = 150 \Omega$ to Midrail                           | 0.14 | 0.24            | 0.27        | 0.28             | V     | Max     |  |

| Low output voltage awing               | $R_L = 150 \Omega$ to GND                               | 0.09 | 0.17            | 0.2         | 0.21             | V     | Max     |  |

| Low output voltage swing               | $R_L = 75 \Omega$ to Midrail                            | 0.24 | 0.33            | 0.36        | 0.37             | V     | Max     |  |

|                                        | $R_L = 75 \Omega$ to GND                                | 0.09 | 0.17            | 0.2         | 0.21             | V     | Max     |  |

| Output ourrent                         | $R_L = 10 \Omega$ to Midrail, sourcing                  | 70   | 45              | 42          | 40               | mA    | Min     |  |

| Output current                         | $R_L = 10 \Omega$ to Midrail, sinking                   | 70   | 45              | 42          | 40               | mA    | Min     |  |

| POWER SUPPLY                           |                                                         |      |                 |             |                  |       |         |  |

| Maximum operating voltage              |                                                         | 3.3  | 5.5             | 5.5         | 5.5              | V     | Max     |  |

| Minimum operating voltage              |                                                         | 3.3  | 2.6             | 2.6         | 2.6              | V     | Min     |  |

| Maximum quiescent current              | Per channel V <sub>I</sub> = 200 mV                     | 6    | 7.2             | 7.4         | 7.5              | mA    | Max     |  |

| Minimum quiescent current              | Per channel V <sub>I</sub> = 200 mV                     | 6    | 4.8             | 4.6         | 4.5              | mA    | Min     |  |

| Total quiescent current                | All channels ON, V <sub>I</sub> = 200 mV <sup>(2)</sup> | 16.6 |                 |             |                  | mA    |         |  |

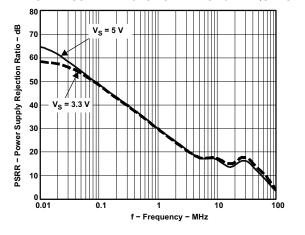

| Power supply rejection (+PSRR)         | V <sub>S+</sub> = 3.5 V to 3.1 V                        | 59   | 37              | 35          | 35               | dB    | Min     |  |

| DISABLE CHARACTERISTI                  | cs                                                      | ļ.   | 1               |             |                  |       |         |  |

| Quiescent current                      | All 3 channels disabled (3)                             | 0.1  |                 |             |                  | μА    |         |  |

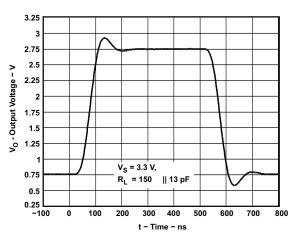

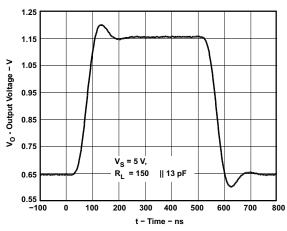

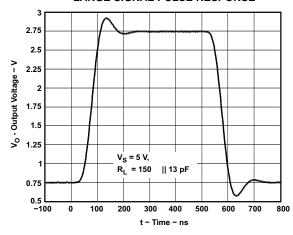

| Turn-on time delay (t <sub>ON</sub> )  | Time reaches 50% of final value after I <sup>2</sup> C  | 5    |                 |             |                  | μs    |         |  |

| Turn-on time delay (t <sub>OFF</sub> ) | control is completed                                    | 2    |                 |             |                  | μs    |         |  |

Due to sharing of internal bias circuitry, the quiescent current, with all channels operating, is less than the single individual channel quiescent current channels added together.

Note that the I<sup>2</sup>C circuitry is still active while in disable mode. The current shown has no activity with the THS7313 I<sup>2</sup>C circuitry.

ELECTRICAL CHARACTERISTICS,  $V_{S+}$  = 5 V R<sub>L</sub> = 150  $\Omega$  to GND, Input Bias = dc, SAG pin shorted to the output pin (unless otherwise noted)

|                                               |                                                     | TYP         | OVERTEMPERATURE |             |                  |       |         |

|-----------------------------------------------|-----------------------------------------------------|-------------|-----------------|-------------|------------------|-------|---------|

| PARAMETER                                     | TEST CONDITIONS                                     | 25°C        | 25°C            | 0°C to 70°C | –40°C to<br>85°C | UNITS | MIN/MAX |

| AC PERFORMANCE                                |                                                     |             |                 |             |                  |       |         |

| Small-signal bandwidth (–3 dB)                | V <sub>O</sub> - 0.2 V <sub>PP</sub> <sup>(1)</sup> | 8           | 6.7/9.3         | 6.55/9.45   | 6.5/9.5          | MHz   | Min/Max |

| Large-signal bandwidth (-3 dB)                | V <sub>O</sub> - 2 V <sub>PP</sub> <sup>(1)</sup>   | 8           |                 |             |                  | MHz   |         |

| Group delay                                   | f = 100 kHz                                         | 67          |                 |             |                  | ns    |         |

| Group delay variation with respect to 100 kHz | f = 5.1 MHz                                         | 13.5        |                 |             |                  | ns    |         |

| Channel-to-Channel group delay variation      | f = 5.1 MHz                                         | 0.5         |                 |             |                  | ns    |         |

| Attenuation with respect to                   | f = 5.75 MHz                                        | 0.5         | -0.2 / 2        | -0.4 / 2.2  | -0.5 / 2.3       | dB    | Min/Max |

| 100 kHz                                       | f = 27 MHz                                          | 48          | 36              | 35          | 34               | dB    | Min     |

| Mute feed-thru                                | f = 1 MHz                                           | -80         |                 |             |                  | dB    |         |

| Differential gain                             | NTSC/PAL                                            | 0.08%/0.16  |                 |             |                  |       |         |

| Differential phase                            | NTSC/PAL                                            | 0.18°/0.18° |                 |             |                  |       |         |

| Total harmonic distortion                     | f = 1 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>       | -67         |                 |             |                  | dB    |         |

| Signal to noise ratio                         | Unified weighting 100 kHz to 6 MHz                  | 82          |                 |             |                  | dB    |         |

| Channel-to-Channel<br>Crosstalk               | f = 1 MHz                                           | -64         |                 |             |                  | dB    |         |

| MUX Isolation                                 | f = 5.1 MHz                                         | 73          |                 |             |                  | dB    |         |

| AC gain – All channels                        | f = 100 kHz                                         | 6           | 5.7/6.3         | 5.65/6.35   | 5.65/6.35        | dB    | Min/Max |

| Output impedance                              | f = 10MHz                                           | 0.7         |                 |             |                  | Ω     |         |

| DC PERFORMANCE                                |                                                     |             |                 |             |                  |       |         |

| Output offset voltage                         | Bias = dc                                           | 30          | 90              | 95          | 95               | mV    | Max     |

| Average offset voltage drift                  | Bias = dc                                           |             |                 |             | 20               | μV/°C |         |

| <b>5</b>                                      | Bias = dc + 135 mV, V <sub>I</sub> = 0 V            | 290         | 235/345         | 215/360     | 200/375          | mV    | Min/Max |

| Bias output voltage                           | Bias = ac                                           | 2.5         | 2.3/2.7         | 2.25/2.75   | 2.25/2.75        | V     | Min/Max |

| Sync tip clamp output voltage                 | Bias = ac STC                                       | 300         | 230/375         | 215/385     | 210/390          | mV    | Min/Max |

| Input bias current                            | Bias = dc - implies lb out of the pin               | -0.6        | -4              | -5          | -5               | μА    | Max     |

| Average bias current drift                    | Bias = dc                                           |             |                 |             | 10               | nA/°C |         |

|                                               | Bias = ac STC, low bias                             | 1.9         | 0.6/3.3         | 0.5/3.5     | 0.4/3.6          | μΑ    | Min/Max |

| Sync tip clamp bias current                   | Bias = ac STC, mid bias                             | 6           | 4.3/8.2         | 4.1/8.4     | 4/8.5            | μΑ    | Min/Max |

|                                               | Bias = ac STC, high bias                            | 8.2         | 6.2/10.8        | 6/11        | 5.9/11.1         | μА    | Min/Max |

| INPUT CHARACTERISTICS                         |                                                     |             |                 |             |                  |       |         |

| Input voltage range                           | Bias = dc - limited by output                       | 0/2.4       | 0/2.35          | 0/2.3       | 0/2.3            | V     | Min/Max |

| Innut resistance                              | Bias = ac bias mode                                 | 19          |                 |             |                  | kΩ    |         |

| Input resistance                              | Bias = dc, dc + 135 mV, ac STC                      | 3           |                 |             |                  | ΜΩ    |         |

| Input capacitance                             |                                                     | 2           |                 |             |                  | pF    |         |

| OUTPUT CHARACTERISTIC                         | cs                                                  |             |                 |             |                  |       |         |

|                                               | $R_L = 150 \Omega$ to midrail                       | 4.8         | 4.4             | 4.3         | 4.3              | V     | Min     |

| High output voltage swing                     | $R_L$ = 150 $\Omega$ to GND                         | 4.65        | 4.2             | 4.1         | 4.1              | V     | Min     |

| i ligh output voltage swillg                  | $R_L = 75 \Omega$ to midrail                        | 4.7         | 4.3             | 4.2         | 4.2              | V     | Min     |

|                                               | $R_L = 75 \Omega$ to GND                            | 4.4         | 4.1             | 4           | 4                | V     | Min     |

|                                               | $R_L = 150 \Omega$ to midrail                       | 0.2         | 0.34            | 0.37        | 0.37             | V     | Max     |

| Low output voltage ewing                      | $R_L$ = 150 $\Omega$ to GND                         | 0.1         | 0.23            | 0.26        | 0.27             | V     | Max     |

| Low output voltage swing                      | $R_L = 75 \Omega$ to Midrail                        | 0.35        | 0.46            | 0.5         | 0.5              | V     | Max     |

|                                               | $R_L = 75 \Omega$ to GND                            | 0.1         | 0.23            | 0.26        | 0.27             | V     | Max     |

<sup>(1)</sup> The Min/Max values listed are specified by design only.

# ELECTRICAL CHARACTERISTICS, $V_{S+} = 5 \text{ V}$ (continued)

$R_L$  = 150  $\Omega$  to GND, Input Bias = dc, SAG pin shorted to the output pin (unless otherwise noted)

|                                                         | TYP                                                                                                                                                                                                                                                                               | OVERTEMPERATURE                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TEST CONDITIONS                                         | 25°C                                                                                                                                                                                                                                                                              | 25°C                                                                                                                                                                                                                                                                                                                                                                                                        | 0°C to 70°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | –40°C to<br>85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | UNITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MIN/MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| $R_L = 10 \Omega$ to Midrail, sourcing                  | 85                                                                                                                                                                                                                                                                                | 60                                                                                                                                                                                                                                                                                                                                                                                                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| $R_L = 10 \Omega$ to Midrail, sinking                   | 85                                                                                                                                                                                                                                                                                | 60                                                                                                                                                                                                                                                                                                                                                                                                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                         |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                         | 5                                                                                                                                                                                                                                                                                 | 5.5                                                                                                                                                                                                                                                                                                                                                                                                         | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                         | 5                                                                                                                                                                                                                                                                                 | 2.6                                                                                                                                                                                                                                                                                                                                                                                                         | 2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Per channel V <sub>I</sub> = 200 mV                     | 6.6                                                                                                                                                                                                                                                                               | 7.9                                                                                                                                                                                                                                                                                                                                                                                                         | 8.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Per channel V <sub>I</sub> = 200 mV                     | 6.6                                                                                                                                                                                                                                                                               | 5.3                                                                                                                                                                                                                                                                                                                                                                                                         | 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| All channels ON, V <sub>I</sub> = 200 mV <sup>(2)</sup> | 18.9                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| V <sub>S+</sub> = 3.5 V to 3.1 V                        | 59                                                                                                                                                                                                                                                                                | 38                                                                                                                                                                                                                                                                                                                                                                                                          | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |