**THS6226A**

ZHCSCI0A - APRIL 2014-REVISED MAY 2014

# THS6226A 门控 H 类,双端口 VDSL2 线路驱动器

### 特性

- 数字式可调节静态电流: 9.4mA 至 24.8mA

- 偏置电流步长: 1.0mA

- 独立的升压和主线路驱动器禁用

- 低功率线路端接模式

- 完全电容器再充电: 200µs

- 低输出电压噪声密度: 6.5nV/√Hz 输入引入电压噪声

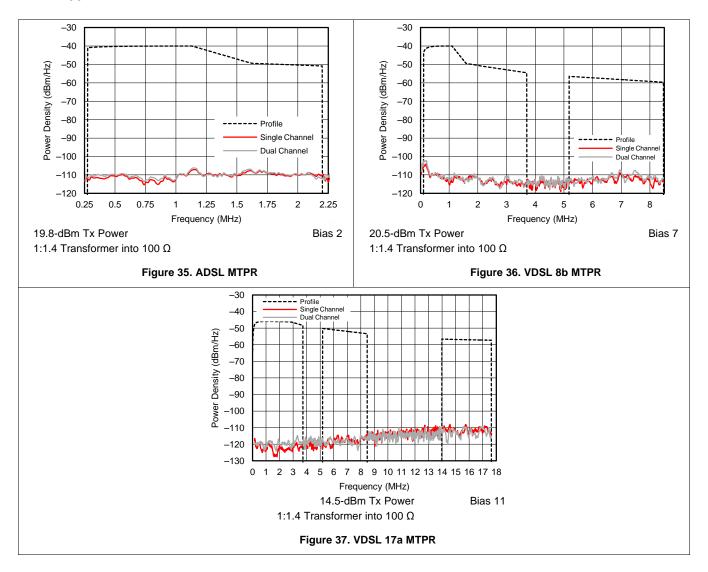

- 低多音频功率比 (MTPR) 失真: 70dB 加上 +19.8dBm G.993.2 — 传输模式 8b

- -83dBc HD3(1MHz, 60Ω 差分)

- 高输出电流: (可向 60Ω 负载输送 383mA 的电

- 宽输出摆幅: 40V<sub>PP</sub> (+12V, 100Ω 差分负载和一 个 1:1.4 变压器)

- 高带宽: 97MHz

- 端口至端口隔离度: 1MHz 时大于 90dB

- 电源抑制比 (PSRR): 在 1MHz 频率下提供了 70dB 的良好隔离

#### 2 应用范围

- 非常适合于所有的 VDSL2 传输模式

- 与 ADSL, ADSL2+ 和 ADSL2++ 系统向后兼容

### 3 说明

THS6226A 是一款双端口, H 类, 电流反馈架构, 差 分线路驱动器放大器系统,此系统非常适合于 xDSL 系统。 该器件旨在应用于超高位速率数字用户线路 2 (VDSL2) 线路驱动器系统,此类系统可启用本地 DTM 信号,同时用良好线性支持高于 20.5dBm 的线路功 率(在高达 8.5MHz 的频率条件下),从而支持 G.993.2 VDSL2 8b 传输模式。 另外, 此器件还拥有 足以支持 14.5dBm 线路功率(在高达 30MHz 的频率 下)的中心局传输的高速度。

此器件的独特架构可实现极小的静态电流,同时仍然实 现超高线性度。 在全偏置条件和 1MHz 频率下,差分 失真为 -91dBc, 并在 5MHz 频率下减少为仅有 -75dBc。 对于并不需要放大器全部性能的线路长度, 放大器的多种固定偏置设定值可提升节能效果。 为了 在所有的系统配置中实现更大的灵活性及节能幅度,以 0.1mA 的偏置电流步长对静态电流进行数字化调节, 调节范围从 7.67mA 至 23mA。 对于那些希望在不传 输时节省更多电能的系统, 此器件可在其线路端接模式 中使用,以保持阻抗匹配。

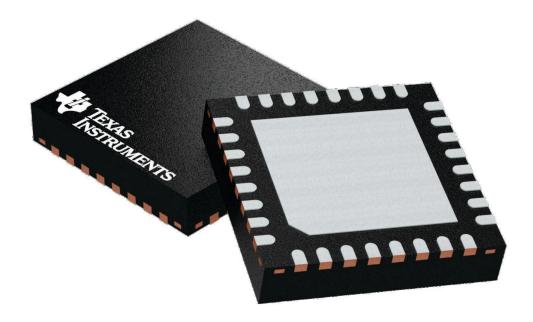

12V 电源上的宽输出摆幅与出色的电流驱动能力相结 合,可实现宽动态余量,从而将失真保持在尽可能低的 水平。 此器件采用超薄四方扁平无引线 (VQFN)-32 PowerPAD™ 封装。

#### 器件信息(1)

| 产品型号     | 封装        | 封装尺寸 (标称值)      |  |  |

|----------|-----------|-----------------|--|--|

| THS6226A | VQFN (32) | 5.00mm x 5.00mm |  |  |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

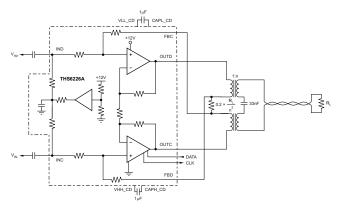

#### 利用 THS6226A 的一个端口的典型 VDSL2 线路驱动 器电路

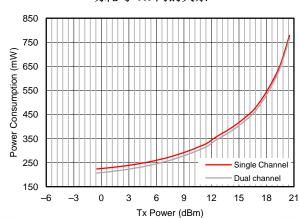

#### 功耗与 Tx 间的关系

|   | 目录                                                     | ₹  |                                      |                |

|---|--------------------------------------------------------|----|--------------------------------------|----------------|

| 1 | 特性1                                                    |    | 7.4 Device Functional Modes          | 1              |

| 2 | 应用范围 1                                                 |    | 7.5 Programming                      | 10             |

| 3 | 说明 1                                                   | 8  | Applications and Implementation      | 19             |

| 4 | 修订历史记录 2                                               |    | 8.1 Application Information          | 19             |

| 5 | Pin Configuration and Functions3                       |    | 8.2 Typical Application              | 19             |

| 6 | Specifications5                                        |    | 8.3 Initialization Set Up            | 2º             |

| U | 6.1 Absolute Maximum Ratings                           | 9  | Power Supply Recommendations         | 2 <sup>2</sup> |

|   | 6.2 Handling Ratings                                   | 10 | Layout                               | 22             |

|   | 6.3 Recommended Operating Conditions                   |    | 10.1 Layout Guidelines               | 22             |

|   | 6.4 Thermal Information                                |    | 10.2 Layout Example                  | 2              |

|   | 6.5 Electrical Characteristics: V <sub>S</sub> = +12 V | 11 | 器件和文档支持                              | 24             |

|   | 6.6 Timing Characteristics 8                           |    | 11.1 文档支持                            | 24             |

|   | 6.7 Typical Characteristics9                           |    | 11.2 Trademarks                      | 24             |

| 7 | Detailed Description                                   |    | 11.3 Electrostatic Discharge Caution | 2              |

|   | 7.1 Overview 14                                        |    | 11.4 Glossary                        |                |

|   | 7.2 Functional Block Diagram                           | 12 | 机械封装和可订购信息                           | 24             |

# 4 修订历史记录

| Cł | hanges from Original (April 2014) to Revision A | Page |

|----|-------------------------------------------------|------|

| •  | Changed HBM parameter in Handling Ratings table | 5    |

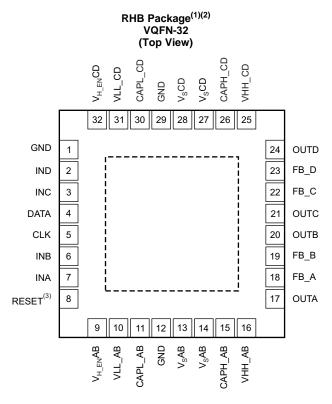

## 5 Pin Configuration and Functions

- (1) The PowerPAD is electrically isolated from all other pins and can be connected to any potential voltage range from  $V_{S-}$  to  $V_{S+}$ . Typically, the PowerPAD is connected to the GND plane because this plane tends to physically be the largest and is able to dissipate the most amount of heat.

- (2) The device defaults to the disabled mode at power-up.

- (3) Default is GND (internal pull-down resistor).

### **Pin Functions**

| ı         | PIN                  | 1/0 | DESCRIPTION                                                                                                       |

|-----------|----------------------|-----|-------------------------------------------------------------------------------------------------------------------|

| NO.       | NAME                 | 1/0 | DESCRIPTION                                                                                                       |

| 1, 12, 29 | GND                  | _   | Analog ground                                                                                                     |

| 2         | IND                  | I   | Input D of amplifier CD                                                                                           |

| 3         | INC                  | I   | Input C of amplifier CD                                                                                           |

| 4         | DATA                 | - 1 | Serial interface data pin                                                                                         |

| 5         | CLK                  | I   | Serial interface CLK pin                                                                                          |

| 6         | INB                  | - 1 | Input B of amplifier AB                                                                                           |

| 7         | INA                  | I   | Input A of amplifier AB                                                                                           |

| 8         | RESET                | - 1 | Reset the internal register to 00h (startup conditions, state machine may require resetting)                      |

| 9         | V <sub>H_EN</sub> AB | I   | Class H mode control pin for amplifier AB                                                                         |

| 10        | VLL_AB               | _   | Amplifier AB low pump supply                                                                                      |

| 11        | CAPL_AB              | _   | Amplifier AB negative voltage pump capacitor pin                                                                  |

| 13, 14    | V <sub>S</sub> AB    | _   | Amplifier AB supply voltage                                                                                       |

| 15        | CAPH_AB              | _   | Amplifier AB positive voltage pump capacitor pin                                                                  |

| 16        | VHH_AB               | _   | Amplifier AB high pump supply                                                                                     |

| 17        | OUTA                 | 0   | Output A of amplifier AB                                                                                          |

| 18        | FB_A                 | - 1 | Feedback for active output impedance of amplifier AB                                                              |

| 19        | FB_B                 | I   | Feedback for active output impedance of amplifier AB                                                              |

| 20        | OUTB                 | 0   | Output B of amplifier AB                                                                                          |

| 21        | OUTC                 | 0   | Output C of amplifier CD                                                                                          |

| 22        | FB_C                 | I   | Feedback for active output impedance of amplifier CD                                                              |

| 23        | FB_D                 | - 1 | Feedback for active output impedance of amplifier CD                                                              |

| 24        | OUTD                 | 0   | Output D of amplifier CD                                                                                          |

| 25        | VHH_CD               | _   | Amplifier CD high pump supply                                                                                     |

| 26        | CAPH_CD              | _   | Amplifier CD positive voltage pump capacitor pin                                                                  |

| 27, 28    | V <sub>S</sub> CD    | _   | Amplifier CD supply voltage                                                                                       |

| 30        | CAPL_CD              | _   | Amplifier CD negative voltage pump capacitor pin                                                                  |

| 31        | VLL_CD               |     | Amplifier CD low pump supply                                                                                      |

| 32        | V <sub>H_EN</sub> CD | I   | Class H mode control pin for amplifier CD                                                                         |

| Pow       | erPAD                | _   | The PowerPAD must be connected to any internal PCB ground plane using multiple vias for good thermal performance. |

### 6 Specifications

### 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                        |                                                                            | MIN                           | MAX  | UNIT |

|----------------------------------------|----------------------------------------------------------------------------|-------------------------------|------|------|

| Cumply voltage CND to V                | Class AB only                                                              |                               | 16.5 | V    |

| Supply voltage, GND to V <sub>S+</sub> | Class H only                                                               |                               | 12.8 | V    |

| Input voltage, V <sub>I</sub>          |                                                                            |                               | 15   | V    |

| Output current, I <sub>O</sub>         | Static dc <sup>(2)</sup>                                                   |                               | ±100 | mA   |

| Continuous power dissipation           |                                                                            | See Thermal Information table |      |      |

|                                        | Maximum junction, any condition, T <sub>J</sub> <sup>(3)</sup>             |                               | 150  | °C   |

| Temperature                            | Maximum junction, continuous operation, long-term reliability, $T_J^{(4)}$ |                               | 130  | °C   |

- (1) Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may degrade device reliability.

- (2) The device incorporates a PowerPAD on the underside of the chip, which functions as a heatsink and must be connected to a thermally dissipating plane for proper power dissipation. Failure to do so may result in exceeding the maximum junction temperature, which could permanently damage the device. See the technical brief PowerPAD™ Thermally Enhanced Package (SLMA002) for more information about using the PowerPAD thermally-enhanced package. Under high-frequency ac operation (> 10 kHz), the short-term output current capability is much greater than the continuous dc output current rating. This short-term output current rating is roughly 8.5 times the dc capability, or approximately ±850 mA.

- (3) The absolute maximum junction temperature under any condition is limited by the constraints of the silicon process.

- (4) The absolute maximum junction temperature for continuous operation is limited by the package constraints. Operation above this temperature may result in reduced reliability or lifetime of the device.

### 6.2 Handling Ratings

|                    |                                            |                                                                           |                                                                                                                                         | MIN  | MAX | UNIT |  |

|--------------------|--------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|--|

| T <sub>stg</sub>   | T <sub>stg</sub> Storage temperature range |                                                                           |                                                                                                                                         |      | 150 | ô    |  |

| V <sub>(ESD)</sub> | Electrostatic discharge                    | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001                     | Supply and ground pins with respect to PowerPad: GND (pins 1, 12, 29), V <sub>S</sub> AB (pins 13, 14), V <sub>S</sub> CD (pins 27, 28) | -1.5 | 1.5 | kV   |  |

| * (ESD)            |                                            |                                                                           | All other pins                                                                                                                          | -2   | 2   |      |  |

|                    |                                            | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins |                                                                                                                                         | -500 | 500 | V    |  |

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                |          | MIN | NOM MAX | UNIT |

|--------------------------------|----------|-----|---------|------|

| Dower cumply veltage renge     | Class H  | 10  | 12.6    | ٧    |

| Power-supply voltage range     | Class AB | 10  | 15      | ٧    |

| Operating junction temperature |          | -40 | 130     | °C   |

#### 6.4 Thermal Information

|                      |                                              | THS6226A   |       |

|----------------------|----------------------------------------------|------------|-------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RHB (VQFN) | UNIT  |

|                      |                                              | 32 PINS    |       |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 35.1       |       |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 22.1       |       |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 7.0        | °C/\/ |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3        | °C/W  |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 6.9        |       |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.3        |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics: $V_S = +12 \text{ V}$

At  $T_A = 25$ °C,  $R_{MATCH} = 10.2 \Omega$ , transformer turn ratio 1:1.4,  $R_L = 100 - \Omega$  differential at transformer output, full bias mode, and active impedance circuit configuration, unless otherwise noted. Each port is tested independently.

|          | PARAMETER                              | CONDITIONS                                                                             | MIN | TYP    | MAX                                   | UNIT     | TEST<br>LEVEL <sup>(1)</sup> |

|----------|----------------------------------------|----------------------------------------------------------------------------------------|-----|--------|---------------------------------------|----------|------------------------------|

| AC PER   | FORMANCE                               |                                                                                        |     |        |                                       |          |                              |

|          | Small-signal bandwidth, -3 dB          | V <sub>O</sub> = 2 V <sub>PP</sub> , differential at<br>OUTCD and OUTAB, gain = 19 V/V |     | 97     |                                       | MHz      | С                            |

|          | 0.1-dB bandwidth flatness              | $V_O = 2 V_{PP}$                                                                       |     | 30     |                                       | MHz      | С                            |

|          | Large-signal bandwidth                 | $V_O = 7.5 V_{PP}$                                                                     |     | 80     |                                       | MHz      | С                            |

| SR       | Slew rate (10% to 90% level)           | V <sub>O</sub> = 15-V step, differential                                               |     | 1750   |                                       | V/µs     | С                            |

|          | Rise-and-fall time                     | V <sub>O</sub> = 2 V <sub>PP</sub>                                                     |     | 3.6    |                                       | ns       | С                            |

| LIDO     | Constant beautiful distantian          | Full bias, f = 1 MHz, $V_O$ = 2 $V_{PP}$ , $R_L$ = 60- $\Omega$ differential           |     | -87    |                                       | dBc      | С                            |

| HD2      | Second-harmonic distortion             | Full bias, f = 5 MHz, $V_O$ = 2 $V_{PP}$ , $R_L$ = 60- $\Omega$ differential           |     | -73    |                                       | dBc      | С                            |

| LIDO     | Third because is distantian            | Full bias, f = 1 MHz, $V_O = 2 V_{PP}$ , $R_L = 60-\Omega$ differential                |     | -83    |                                       | dBc      | С                            |

| HD3      | Third-harmonic distortion              | Full bias, f = 5 MHz, $V_O$ = 2 $V_{PP}$ , $R_L$ = 60- $\Omega$ differential           |     | -71    |                                       | dBc      | С                            |

|          | Differential input voltage noise       | f = 1 MHz, input-referred                                                              |     | 6.5    |                                       | nV/√Hz   | С                            |

| DC PER   | FORMANCE                               |                                                                                        |     |        |                                       |          |                              |

|          | Differential gain                      | Closed-loop configuration                                                              |     | 19     |                                       | V/V      | С                            |

|          | Differential gain error <sup>(2)</sup> | T <sub>A</sub> = 25°C                                                                  |     |        | ±8%                                   |          | Α                            |

| .,       |                                        | T <sub>A</sub> = 25°C                                                                  |     | ±1     | ±10                                   | mV       | Α                            |

| $V_{IO}$ | Input offset voltage                   | $T_A = -40$ °C to 85°C                                                                 |     |        | ±11                                   | mV       | В                            |

|          | Input offset voltage drift             |                                                                                        |     |        | 15                                    | μV/°C    | В                            |

|          | Input offset voltage matching          | Channels 1 to 2 and 3 to 4 only,<br>T <sub>A</sub> = 25°C                              |     | ±1     | ±10                                   | mV       | А                            |

| INPUT (  | CHARACTERISTICS                        | ·                                                                                      | *   |        | • • • • • • • • • • • • • • • • • • • |          | •                            |

|          | Noninverting input resistance          |                                                                                        |     | 2    2 |                                       | kΩ    pF | С                            |

|          | Input bias voltage                     | T <sub>A</sub> = 25°C                                                                  | 5.8 | 6      | 6.2                                   | V        | Α                            |

<sup>(1)</sup> Test levels: (A) 100% tested at 25°C. Overtemperature limits set by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

<sup>(2)</sup> Negative feedback loop only.

## Electrical Characteristics: $V_S = +12 \text{ V}$ (continued)

At  $T_A = 25$ °C,  $R_{MATCH} = 10.2 \Omega$ , transformer turn ratio 1:1.4,  $R_L = 100 - \Omega$  differential at transformer output, full bias mode, and active impedance circuit configuration, unless otherwise noted. Each port is tested independently.

|                | PARAM                     | ETER                                                                                              | CONDITIONS                                                                                         | MIN  | TYP  | MAX  | UNIT | TEST<br>LEVEL <sup>(1)</sup> |

|----------------|---------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|------|------|------|------------------------------|

| OUTPU          | T CHARACTERIS             | TICS                                                                                              |                                                                                                    |      |      |      |      |                              |

|                |                           |                                                                                                   | R <sub>1</sub> = 60-Ω differential, class H                                                        | 16   | 17.5 |      | V    | Α                            |

|                |                           |                                                                                                   | $R_L$ = 60-Ω differential, class H operation <sup>(3)(4)</sup> , each output, $T_A$ = 25°C         | -4   | -5.5 |      | V    | А                            |

|                | <b>.</b>                  | Voltage swing                                                                                     | - (3)(4)                                                                                           | 15.7 |      |      | V    | В                            |

|                | Class H<br>output         |                                                                                                   | $T_A = -40$ °C to 85°C <sup>(3)(4)</sup>                                                           | -3.7 |      |      | V    | В                            |

|                |                           | Current                                                                                           | $R_L$ = 60-Ω differential, class H operation, $T_A$ = 25°C                                         | ±333 | ±383 |      | mA   | Α                            |

|                |                           | (sourcing, sinking)                                                                               | $T_A = -40$ °C to 85°C                                                                             | ±323 |      |      | mA   | В                            |

|                |                           |                                                                                                   | $R_L = 60-\Omega$ differential, normal operation <sup>(3)</sup> ,                                  | 9.9  | 10.1 |      | V    | Α                            |

|                |                           | Valta na ancia a                                                                                  | each output, T <sub>A</sub> = 25°C                                                                 | 2.1  | 1.9  |      | V    | А                            |

|                | Ol AD                     | Voltage swing                                                                                     | T 4000 to 0500(3)                                                                                  | 9.8  |      |      | V    | В                            |

|                | Class AB<br>output        |                                                                                                   | $T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}^{(3)}$                                           | 2.2  |      |      | V    | В                            |

|                | ·                         | Current                                                                                           | $R_L = 60-\Omega$ differential, normal operation,<br>$T_A = 25^{\circ}C$                           | ±130 | ±137 |      | mA   | Α                            |

|                |                           | (sourcing, sinking)                                                                               | $T_A = -40$ °C to 85°C                                                                             | ±126 |      |      | mA   | В                            |

|                | Short-circuit of          | output current                                                                                    |                                                                                                    |      | 1    |      | Α    | С                            |

| Z <sub>o</sub> | Output impedance          |                                                                                                   | f = 1 MHz, differential                                                                            |      | 25   |      | Ω    | С                            |

|                | Crosstalk                 |                                                                                                   | f = 1 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub> , port 1 to port 2                                 |      | -90  |      | dB   | С                            |

| POWER          | SUPPLY                    |                                                                                                   |                                                                                                    |      |      |      |      |                              |

|                |                           |                                                                                                   | Class AB, T <sub>A</sub> = 25°C                                                                    | 10   | 12   | 15   | V    | Α                            |

|                |                           |                                                                                                   | $T_A = -40$ °C to 85°C                                                                             | 10   |      | 15   | V    | В                            |

|                | Maximum operating voltage |                                                                                                   | Class H                                                                                            | 10   | 12   | 12.6 | V    | В                            |

|                |                           |                                                                                                   | T <sub>A</sub> = -40°C to 85°C                                                                     | 10   |      | 12.6 | V    | В                            |

|                |                           |                                                                                                   | Per port, bias 15, class H enable<br>(power supplies connected together),<br>T <sub>A</sub> = 25°C | 23.4 | 24.6 | 25.8 | mA   | А                            |

|                |                           |                                                                                                   | $T_A = -40$ °C to 85°C                                                                             | 22.9 |      | 26.1 | mA   | В                            |

|                |                           |                                                                                                   | Per port, bias 15, class H disable (power supplies connected together), $T_A = 25^{\circ}C$        | 22.8 | 24.0 | 25.2 | mA   | А                            |

|                |                           |                                                                                                   | T <sub>A</sub> = -40°C to 85°C                                                                     | 22.3 |      | 25.7 | mA   | В                            |

|                |                           |                                                                                                   | Bias current step                                                                                  |      | 1    |      | mA   | С                            |

| IQ             | Quiescent cu              | rrent (I <sub>S+</sub> )                                                                          | Per port, bias 0, class H disable (power supplies connected together), T <sub>A</sub> = 25°C       | 8.5  | 9.7  | 10.9 | mA   | А                            |

|                |                           |                                                                                                   | $T_A = -40$ °C to 85°C                                                                             | 8.0  |      | 11.4 | mA   | В                            |

|                |                           | Per port, line termination mode<br>(B9 = B8 = B7 = B6 = 0)<br>(power supplies connected together) |                                                                                                    | 7.0  |      | mA   | С    |                              |

|                |                           |                                                                                                   | Both ports, main amplifiers and class H disable (B9 = B8 = B7 = B6 = 0)                            |      | 1.9  | 2.4  | mA   | А                            |

|                |                           |                                                                                                   | T <sub>A</sub> = -40°C to 85°C                                                                     |      |      | 2.5  | mA   | В                            |

| PSRR           | Power-supply              | rejection ratio                                                                                   | Differential, from 12 V, GND, T <sub>A</sub> = 25°C                                                | 60   | 70   |      | dB   | Α                            |

|                |                           |                                                                                                   | $T_A = -40$ °C to 85°C                                                                             | 58   |      |      | dB   | В                            |

<sup>(3)</sup> Measured at the amplifier outputs (pins 17, 20, 21, and 24).

<sup>(4)</sup> Capacitor fully charged, no droop.

## Electrical Characteristics: $V_S = +12 \text{ V}$ (continued)

At  $T_A$  = 25°C,  $R_{MATCH}$  = 10.2  $\Omega$ , transformer turn ratio 1:1.4,  $R_L$  = 100- $\Omega$  differential at transformer output, full bias mode, and active impedance circuit configuration, unless otherwise noted. Each port is tested independently.

|                     | PARAMETER           |                      | CONDITIONS                                          | MIN | TYP     | MAX | UNIT     | TEST<br>LEVEL <sup>(1)</sup> |

|---------------------|---------------------|----------------------|-----------------------------------------------------|-----|---------|-----|----------|------------------------------|

| LOGIC               |                     |                      |                                                     |     |         |     |          |                              |

|                     |                     | 1: - 411-1-1         | Logic 1, with respect to GND <sup>(5)</sup>         | 1.9 |         |     | V        | С                            |

|                     |                     | n Input Bias current | Logic 0, with respect to GND <sup>(5)</sup>         |     |         | 0.8 | V        | С                            |

|                     |                     |                      | Logic X = 0.5 V (logic 0), T <sub>A</sub> = 25°C    |     | 10      | 25  | μΑ       | А                            |

|                     | Logic pin           |                      | $T_A = -40$ °C to 85°C                              |     |         | 30  | μΑ       | В                            |

|                     |                     |                      | Logic X = 3.3 V (logic 1), T <sub>A</sub> = 25°C    |     | 66      | 125 | μΑ       | А                            |

|                     |                     |                      | $T_A = -40$ °C to 85°C                              |     |         | 130 | μΑ       | В                            |

|                     |                     | Input impedance      |                                                     |     | 50    1 |     | kΩ    pF | С                            |

| t <sub>d(on)</sub>  | Turn-on time delay  |                      | Time for I <sub>S</sub> to reach 50% of final value |     | 1       |     | μs       | С                            |

| t <sub>d(off)</sub> | Turn-off time delay |                      | Time for I <sub>S</sub> to reach 50% of final value |     | 1       |     | μs       | С                            |

(5) The GND pin usable range is from  $V_{S-}$  to  $(V_{S+}-5\ V)$ .

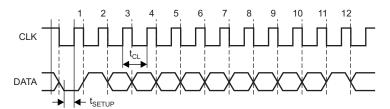

### 6.6 Timing Characteristics

| PARAMETER                    | MIN MAX | UNITS |

|------------------------------|---------|-------|

| t <sub>CL</sub> Clock period | 200     | ns    |

Figure 1. Serial Interface Timing

### 6.7 Typical Characteristics

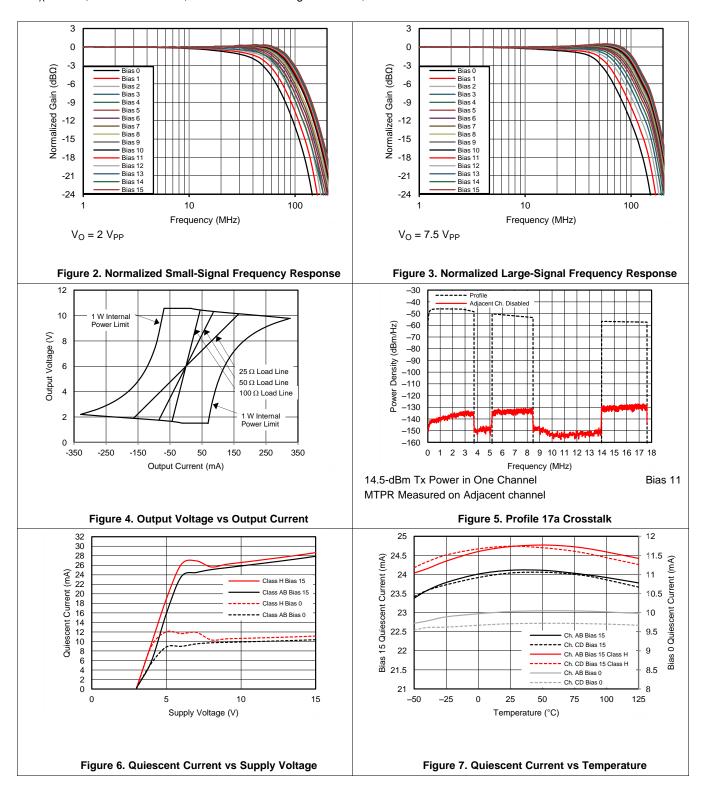

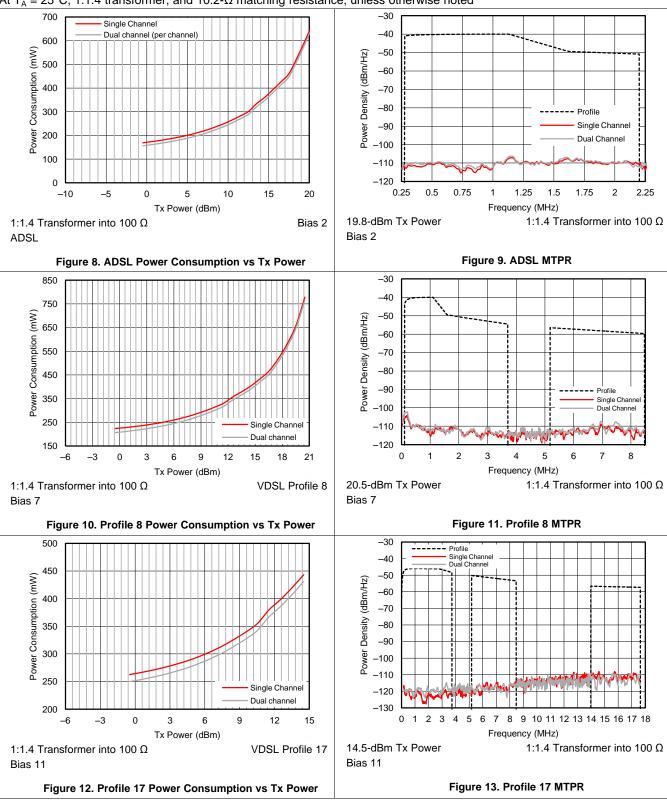

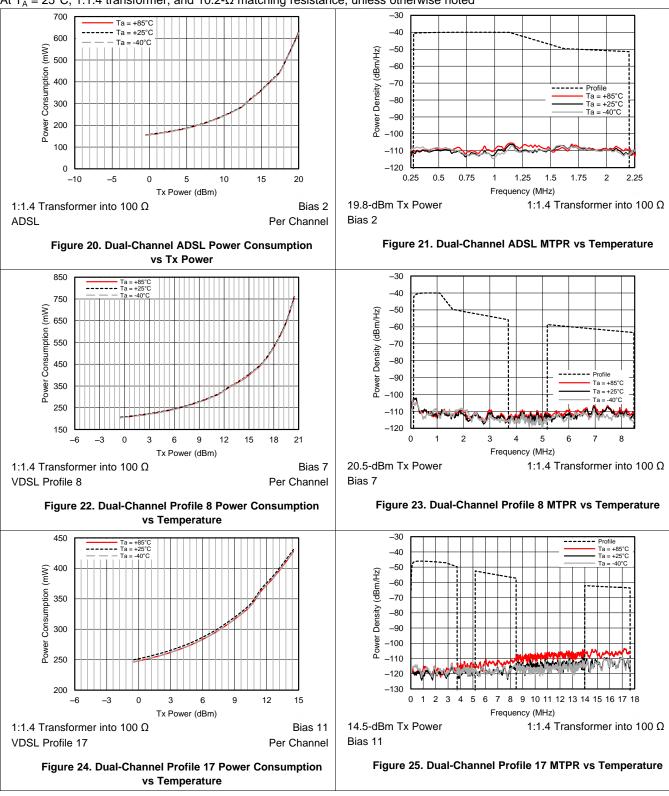

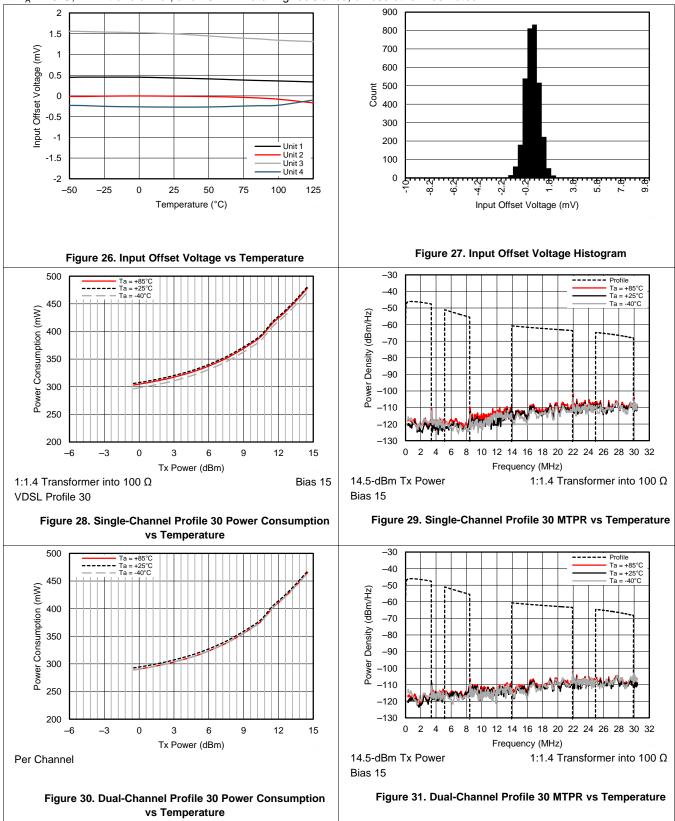

At  $T_A = 25$ °C, 1:1.4 transformer, and 10.2- $\Omega$  matching resistance, unless otherwise noted

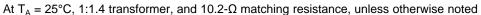

At  $T_A = 25$ °C, 1:1.4 transformer, and 10.2- $\Omega$  matching resistance, unless otherwise noted

vs Temperature

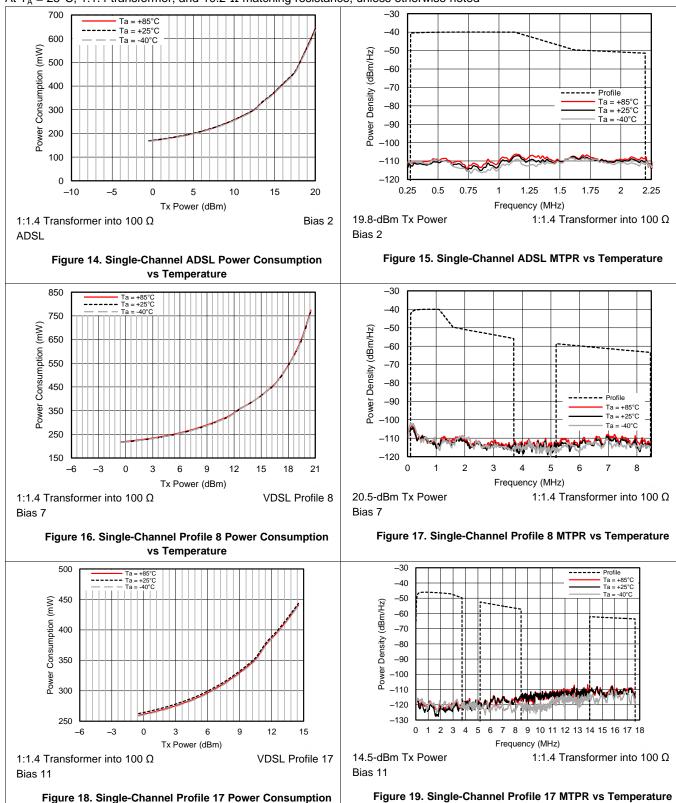

At  $T_A = 25$ °C, 1:1.4 transformer, and 10.2- $\Omega$  matching resistance, unless otherwise noted

At  $T_A = 25$ °C, 1:1.4 transformer, and 10.2- $\Omega$  matching resistance, unless otherwise noted

### 7 Detailed Description

#### 7.1 Overview

The THS6226A class H line driver provides exceptional ac performance in conjunction with wide output voltage swing. The class H operation allows voltage swings to exceed the power supply for short intervals limited only by the charge in the capacitor. In class AB mode, the device is capable of driving a  $100-\Omega$  load from +1.8 V to +10.2 V. In class H mode, under the same conditions, the output voltage range becomes an impressive –5.5 V to +17.5 V, or 46 V<sub>PP</sub> differentially with the capacitor fully charged.

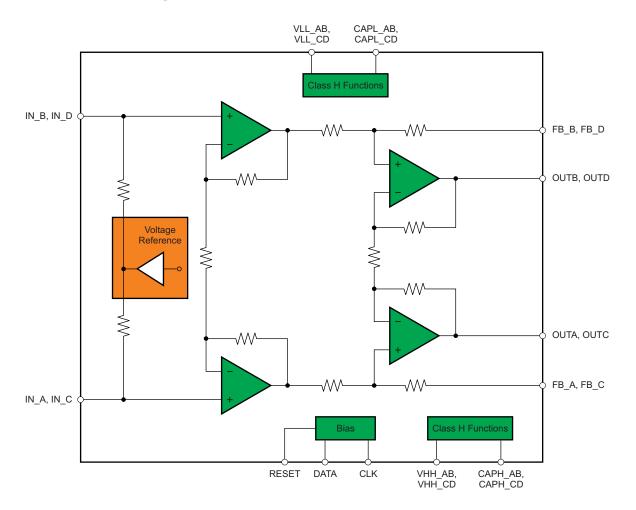

The *Functional Block Diagram* section shows a fully-differential, noninverting amplifier configuration with active impedance. In this configuration, the  $10.2-\Omega$  matching resistor appears through the transformer as  $100~\Omega$ , minimizing reflection on the line. This active impedance scheme also minimizes transmission losses, as compared to passive termination. Device gain is fixed and is equal to 19 V/V from the input to the output of the amplifier (IN<sub>AB/CD</sub>) to OUT<sub>AB/CD</sub>), not including the transformer-turn ratio or the termination loss.

To simplify the implementation as well as to provide design flexibility, the device contains an integrated midsupply buffer that provides the correct biasing to the amplifier core without requiring any external components. Also present is a two-pin serial interface that provides exceptional design flexibility and allows minimal power consumption for each xDSL profile.

### 7.2 Functional Block Diagram

#### 7.3 Feature Description

The device incorporates several hardware and functionality features: a high output current line driver, a charge pump, a voltage reference, a logic circuit, an active impedance, and a RESET pin. The device has two ports. Each port consists of a high output current line driver, a charge pump, and a reference voltage. Common circuits are the RESET feature and the logic circuit.

### 7.3.1 High Output Current Line Driver

The main purpose for the device is to provide a high output current into a heavy load. For the THS6226A, with its xDSL application targeted, the load is typically 100  $\Omega$  and currents as high as 400 mA are supported with excellent linearity. The core of the line driver is a class AB amplifier providing both good efficiency and high current drive capability. The high output line driver is the core of the device and any external circuit interface is located on both the device inputs and output.

#### 7.3.2 Charge Pump

The class H functionality of the device is brought on by the integration of a charge pump. The charge pump is a power-supply function to the line driver. The role of the charge pump is to vary the power supply from (12 V / GND) to (20 V / -8 V) and allow the line driver to support high peak to average ratio (PAR) signals while minimizing power consumption and maintaining excellent linearity. The charge pump is controlled externally by the V<sub>H\_EN</sub> pin. A logic high on the V<sub>H\_EN</sub> pin results in the power supply of the class AB line driver going to (20 V / -8 V), while a logic low on the V<sub>H\_EN</sub> pin results in normal operation under the (12 V / GND) supplies.

#### 7.3.3 Voltage Reference

An internal voltage reference provides the device common-mode input and output voltage.

#### 7.3.4 Logic

The DATA and CLK pins allow access to the internal logic circuit implemented in the device. This logic circuit allows each channel to either be programmed individually for quiescent current, turn the charge pump on or off, disable the main amplifier, or select the line termination mode. For more information on programming, refer to the *Programming* section.

#### 7.3.5 Active Impedance

The line driver incorporates the positive feedback path to provide the termination to the load. For the device, the synthesis factor implemented is 5.

#### 7.3.6 RESET Pin

The RESET pin provides a quick and easy way to disable the two ports immediately if a fault condition on the line occurs.

#### 7.4 Device Functional Modes

There are several functional modes for the device. These functional modes can be accessed with the CLK and DATA pins. Each main line driver quiescent current can be set to 16 different bias modes: bias 0 through bias 15. Additionally, the line driver and class H feature can be controlled to have the following configuration:

- Class AB mode is the main line driver by itself. The output voltage is limited by the (12 V / GND) power-supply rails. The quiescent current is then set by four bits.

- Class H mode is the main line driver used in conjunction with the class H feature. The output voltage is limited by the (20 V / –8 V) internally-generated power-supply rails. The quiescent current of the main line driver is set by four bits, as in class AB mode.

- Line termination mode is the powered-down mode for the line driver. This mode maintains line termination but has reduced linearity performance.

- · Disabled mode.

For more information on these mode, refer to the *Programming* section.

### 7.5 Programming

### 7.5.1 Programming the Device

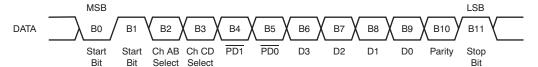

Programming the device is accomplished through a serial interface (pins 4 and 5) and proceeds in the following sequence:

- Two start bits are required (B0 = 0 followed by B1 = 1).

- B2 through B9 are used to program the device. (Table 1 lists the bit descriptions.)

- B10 (described in Table 2) is the parity bit that controls whether the word is loaded or not.

- B11 is the stop bit and must be set to B11 = 1.

Figure 32 shows the required sequence.

**Table 1. DATA Sequence**

| PARAMETER | DESCRIPTION               |

|-----------|---------------------------|

| B0, B1    | Start bits                |

| B2, B3    | Channel select            |

| B4, B5    | Power-down features       |

| B6-B9     | Quiescent current setting |

| B10       | Parity bit                |

| B11       | Stop bit                  |

Table 2. Parity Bit

| B10 | ODD PARITY BIT                                            |

|-----|-----------------------------------------------------------|

| 0   | For an odd number of high bits in B2 to B9, set B10 to 0  |

| 1   | For an even number of high bits in B2 to B9, set B10 to 1 |

Figure 32. DATA Description

#### 7.5.2 Quiescent Current

The <u>devi</u>ce quiesc<u>ent</u> current is dissipated in two main device modules: the class AB and the charge pump. Bits B4 (PD1) and B5 (PD0) select one of the possible four modes of operation:

- 1. Class AB mode (charge pump disabled),

- 2. Class H mode (charge pump enabled),

- 3. Disable mode, or

- 4. Line termination mode (maintains line matching, core amplifier at very low bias mode and charge pump disabled for lowest power consumption possible).

Table 3 lists the details on each bit functionality and the approximate quiescent current. The various power modes are shown in Table 3. For all modes, when B6 through B9 are not defined, set B9 = B8 = B7 = B6 = 0 to achieve the lowest power dissipation possible.

**Table 3. Power Modes**

| B4 (PD1) | B5 (PD0) | POWER-DOWN MODE                                                  | APPROXIMATE I <sub>Q</sub><br>(mA per Port) |

|----------|----------|------------------------------------------------------------------|---------------------------------------------|

| 0        | 0        | Power-down (B9 = B8 = B7 = B6 = 0)                               | 0.85                                        |

| 0        | 1        | Line termination mode (B9 = B8 = B7 = B6 = 0)                    | 4.4                                         |

| 1        | 0        | Class AB driver I <sub>Q</sub> set by B6 to B9, class H disabled | _                                           |

| 1        | 1        | Class AB driver I <sub>Q</sub> set by B6 to B9, class H enabled  | _                                           |

The class AB quiescent current is set by bits B6 to B9, using B4 and B5 for the power-down function and B2 and B3 for channel selection. The approximate quiescent current for the amplifier core is shown in Table 4.

Table 4. Class AB Quiescent Current

| BIAS | B6 (D3) | B7 (D2) | B8 (D1) | B9 (D0) | QUIESCENT CURRENT<br>SETTING | APPROXIMATE I <sub>Q</sub> (mA per Port) |

|------|---------|---------|---------|---------|------------------------------|------------------------------------------|

| 0    | 0       | 0       | 0       | 0       |                              | 9.4                                      |

| 1    | 0       | 0       | 0       | 1       |                              | 10.4                                     |

| 2    | 0       | 0       | 1       | 0       | ADSL2+ mode                  | 11.5                                     |

| 3    | 0       | 0       | 1       | 1       |                              | 12.5                                     |

| 4    | 0       | 1       | 0       | 0       |                              | 13.6                                     |

| 5    | 0       | 1       | 0       | 1       |                              | 14.6                                     |

| 6    | 0       | 1       | 1       | 0       |                              | 15.7                                     |

| 7    | 0       | 1       | 1       | 1       | Profile 8b mode              | 16.7                                     |

| 8    | 1       | 0       | 0       | 0       |                              | 17.8                                     |

| 9    | 1       | 0       | 0       | 1       |                              | 18.8                                     |

| 10   | 1       | 0       | 1       | 0       |                              | 19.8                                     |

| 11   | 1       | 0       | 1       | 1       | Profile 17a mode             | 20.8                                     |

| 12   | 1       | 1       | 0       | 0       |                              | 21.8                                     |

| 13   | 1       | 1       | 0       | 1       |                              | 22.8                                     |

| 14   | 1       | 1       | 1       | 0       |                              | 23.8                                     |

| 15   | 1       | 1       | 1       | 1       |                              | 24.8                                     |

Channel selection is shown in Table 5. Each channel can be programmed independently, or together if both B2 and B3 are set to 1.

**Table 5. Channel Selection**

| B2 (Channel AB) | B3 (Channel CD) | CHANNEL SELECT                            |

|-----------------|-----------------|-------------------------------------------|

| 0               | 0               | Bits B4 to B9 are ignored                 |

| 0               | 1               | Channel B programmed with B4 to B9        |

| 1               | 0               | Channel A programmed with B4 to B9        |

| 1               | 1               | Channels A and B programmed with B4 to B9 |

At startup, the internal register is set as shown in Figure 33.

Figure 33. Internal Register

| 7                     | 6                     | 5       | 4       | 3       | 2       | 1       | 0       |

|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

| Ch. AB Select<br>(B2) | Ch. CD Select<br>(B3) | PD1(B4) | PD0(B5) | D3 (B6) | D2 (B7) | D1 (B8) | D0 (B9) |

| W                     | W                     | W       | W       | W       | W       | W       | W       |

LEGEND: W = Write

In this condition, the total quiescent power dissipation is 10.2 mW per port on a +12-V supply.

### 8 Applications and Implementation

### 8.1 Application Information

The device is a dual-port, very-high-bit-rate digital subscriber line (VDSL), class H line driver. Typically, the signal is generated by a high-speed digital-to-analog converter (DAC). The device drives a twisted pair.

The digital subscriber line (DSL) system is ac-coupled as it transmits information above the audio band. On the input of the line driver, this ac-coupling translates into the series capacitors to isolate the dc voltage coming from the DAC output common-mode voltage. On the output, a transformer is used to help isolate the 48V present between tip and ring of the telephone line.

The transformer can be set to any useful ratio. In practice, the transformer-turn ratio is set between 1:1 and 1:1.4 for the device. As mentioned in the *Feature Description* section, the active impedance synthesis factor is 5. This synthesis factor means that the termination resistor is 1/5th of the load impedance reflected to the transformer secondary. Thus, the correct termination can be selected based on the transformer-turn ratio.

Note that the resulting load detected by the amplifier may affect the amplifier linearity or output voltage swing capabilities.

### 8.2 Typical Application

The typical application circuit for this application is shown in Figure 34.

Figure 34. Typical VDSL Line Driver Circuit Configuration

## **Typical Application (continued)**

### 8.2.1 Design Requirements

**Table 6. Design Requirements**

| DESIGN REQUIREMENT       | CONDITION |

|--------------------------|-----------|

| AC-coupling capacitors   | 0.1 μF    |

| Synthesis factor         | 5         |

| Output transformer ratio | 1:1.4     |

| Surge protection circuit | Not shown |

#### 8.2.2 Detailed Design Procedure

The input capacitor forms a high-pass filter with the device input impedance. This pole must be set at a frequency low enough to not interfere with the desired signal.

The output transformer can be changed to any transformer-turn ratio. Note that the load is expected to be a transmission line with  $100-\Omega$  characteristic impedance. Referred to the transformer secondary, the load detected by the amplifier is  $1/n^2$  with 1:n being the transformer-turn ratio.

Practical limitations force the transformer-turn ratio to be between 1.4:1 and 1:2. At the lighter load detected by the amplifier (1.4:1), the voltage swing is limited by the class H and the maximum achievable swing of the amplifier. At the heaviest load (1:2), the voltage swing is limited by the current drive capability of the amplifier. To satisfy the synthesis impedance factor and the loading, the series resistance ( $R_S$ ) can be set to  $R_S = R_L / 5 = 100 \ \Omega / (5 \times n^2)$ .

For the charge pump, consider the thermal characteristic of the capacitor (X7R, X5R, or Y5V can be used for the charge pump).

For the power-supply bypass, consider using only X7R or X5R because of the better stability of these materials over temperature.

For surge protection, consider adding  $47-\Omega$  resistors in series on the positive feedback path. The secondary protection is also normally added after the series resistance on the secondary transformer.

#### 8.2.3 Application Curves

#### 8.3 Initialization Set Up

After the initial power-up and prior to sending any words to program the device, TI recommends sending a string of twelve 1s (11111111111) to ensure that the state machine is initialized.

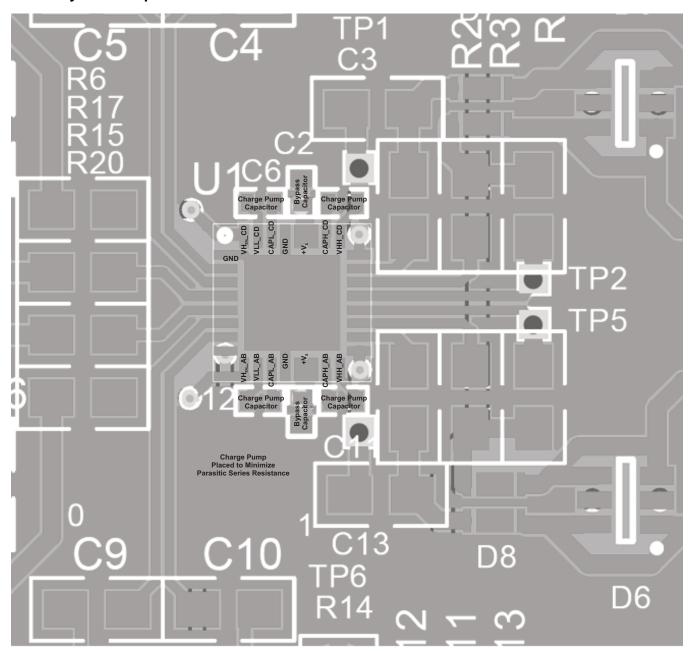

## 9 Power Supply Recommendations

As a result of large recharge current flowing in and out of the four charge pump capacitors during charge pump discharge and recharge events, TI recommends placing bypass capacitors that are at least equal in value to the charge pump capacitor close to each supply voltage pin. A minimum of 2-µF bypass capacitors for each channel are required to minimize any transient appearing on the power supply because both positive and negative charge pump 1-µF bypass capacitors are recharged on the +12-V supply.

### 10 Layout

#### 10.1 Layout Guidelines

Achieving optimum performance with a high-frequency amplifier such as the THS6226A requires careful attention to board layout parasitics and external component types. Recommendations that optimize performance include:

- a. **Minimize parasitic capacitance** to any ac ground for all signal I/O pins. Excessive parasitic capacitance on the inverting input pin can cause instability. In the line driver application, the parasitic capacitance forms a pole with the load detected by the amplifier and may reduce the effective bandwidth of the application circuit, thus leading to degraded performance. To reduce unwanted capacitance, open a window around the signal I/O pins in all ground and power planes around those pins. Otherwise, make sure that ground and power planes are unbroken elsewhere on the board.

- b. **Minimize the distance** (< 0.25") from the power-supply pins to high-frequency 0.1-μF decoupling capacitors. At the device pins, make sure that the ground and power-plane layout are not in close proximity to the signal I/O pins. Avoid narrow power and ground traces to minimize inductance between the pins and decoupling capacitors. Always decouple the power-supply connections with these capacitors. An additional low ESR supply decoupling capacitor (≥ 2 μF, X7R or X5R) to ground is necessary to provide a transient current during the charge pump capacitors recharge.

- c. Careful selection and placement of external components preserves the high-frequency performance of the device. Use very low reactance type resistors. Surface-mount resistors function best and allow a tighter overall layout. Metal-film or carbon composition, axially-leaded resistors also provide good highfrequency performance. Again, keep the leads and printed circuit board traces as short as possible. Never use wire-wound type resistors in a high-frequency application.

- d. Connections to other wideband devices on the board can be made with short, direct traces or through onboard transmission lines. For short connections, consider the trace and the input to the next device as a lumped capacitive load. Use relatively wide traces (50 mils to 100 mils), preferably with ground and power planes opened up around them.

- e. **Do not socket a high-speed part such as the THS6226A.** The additional lead length and pin-to-pin capacitance introduced by the socket can create an extremely troublesome parasitic network that makes achieving a smooth, stable frequency response almost impossible. Best results are obtained by soldering the device onto the board.

## 10.2 Layout Example

Figure 38. Layout Example

### 11 器件和文档支持

#### 11.1 文档支持

#### 11.1.1 相关文档

相关文档如下:

《PowerPAD™ 耐热增强型封装》(, SLMA002

#### 11.2 Trademarks

PowerPAD is a trademark of Texas Instruments, Inc. All other trademarks are the property of their respective owners.

### 11.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms and definitions.

### 12 机械封装和可订购信息

以下页中包括机械封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com 10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking    |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|-----------------|

|                       |        |               |                 |                       |      | (4)                           | (5)                        |              |                 |

| THS6226AIRHBR         | Active | Production    | VQFN (RHB)   32 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | HS6226A<br>IRHB |

| THS6226AIRHBR.A       | Active | Production    | VQFN (RHB)   32 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | HS6226A<br>IRHB |

| THS6226AIRHBT         | Active | Production    | VQFN (RHB)   32 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | HS6226A<br>IRHB |

| THS6226AIRHBT.A       | Active | Production    | VQFN (RHB)   32 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | HS6226A<br>IRHB |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 10-Nov-2025

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 20-Apr-2023

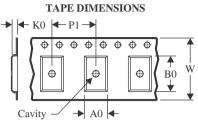

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

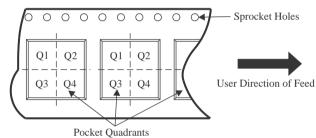

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| THS6226AIRHBR | VQFN            | RHB                | 32 | 3000 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

| THS6226AIRHBT | VQFN            | RHB                | 32 | 250  | 180.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 20-Apr-2023

### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| THS6226AIRHBR | VQFN         | RHB             | 32   | 3000 | 346.0       | 346.0      | 33.0        |

| THS6226AIRHBT | VQFN         | RHB             | 32   | 250  | 210.0       | 185.0      | 35.0        |

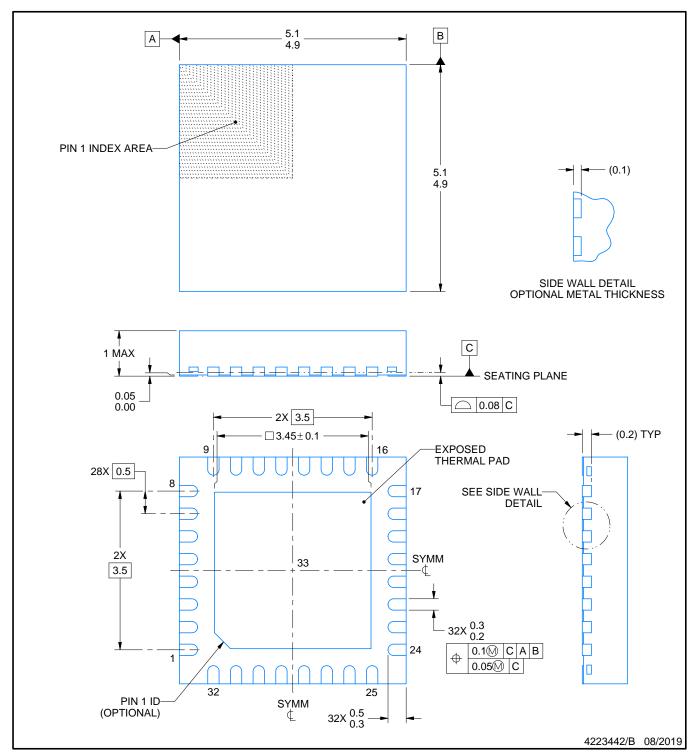

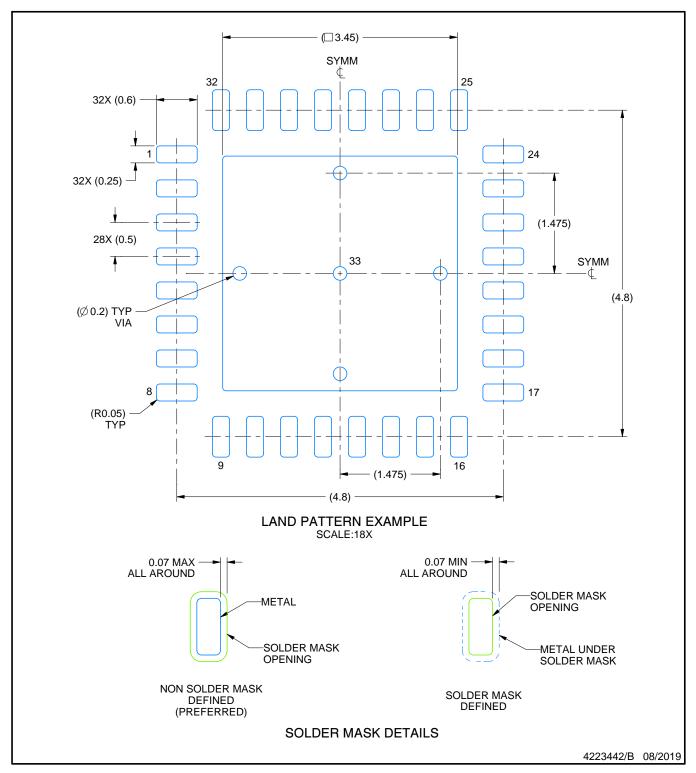

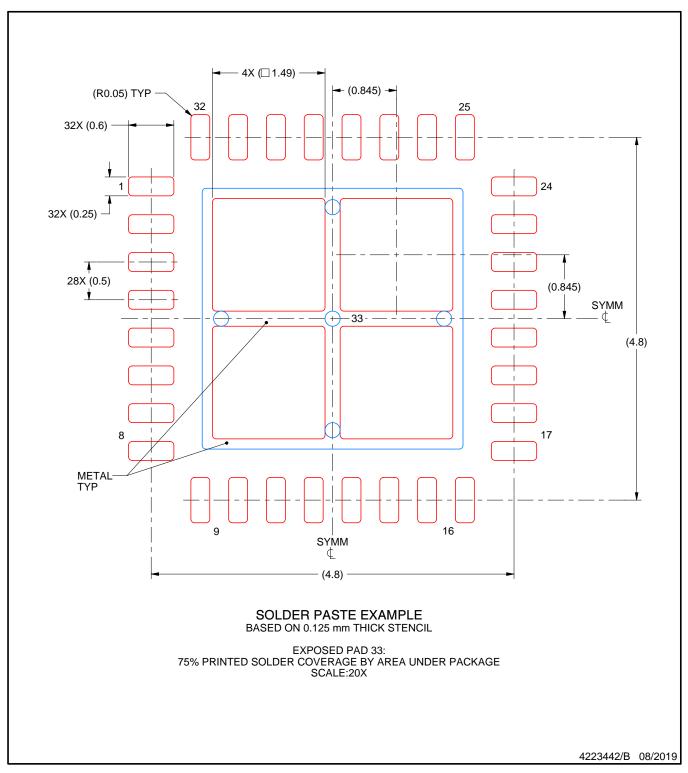

5 x 5, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224745/A

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月