# TDA4VPE-Q1、TDA4APE-Q1 Jacinto™ 汽车级处理器

## 1 特性

### 处理器内核：

- 多达三个 C7x 浮点、矢量 DSP，性能高达 1.0GHz、240GFLOPS、768GOPS

- 多达两个深度学习矩阵乘法加速器 (MMAv2)，性能高达 16TOPS (8b) ( 频率为 1.0GHz )

- 最多两个具有图像信号处理器 (ISP) 和多个视觉辅助加速器的视觉处理加速器 (VPAC)

- 深度和运动处理加速器 (DMPAC)

- 四核 Arm® Cortex®-A72 微处理器子系统，性能高达 2.0GHz

- 每个四核 Cortex®-A72 集群具有 2MB L2 共享缓存

- 每个 Cortex®-A72 内核具有 32KB L1 数据缓存和 48KB L1 指令缓存

- 八个 Arm® Cortex®-R5F MCU，性能高达 1.0GHz

- 32K 指令高速缓存，32K 数据高速缓存，64K L2 TCM

- 隔离 MCU 子系统中有两个 Arm® Cortex®-R5F MCU

- 通用计算分区中有六个 Arm® Cortex®-R5F MCU

- GPU IMG BXS-4-64，256kB 缓存，性能高达 800MHz，50GFLOPS，4GTexels/s (**TDA4VPE**)

- 定制设计的互联结构，支持接近于最高的处理能力

### 存储器子系统：

- 高达 8MB 的片上 L3 RAM ( 具有 ECC 和一致性 )

- ECC 错误保护

- 共享一致性高速缓存

- 支持内部 DMA 引擎

- 多达两个具有 ECC 的外部存储器接口 (EMIF) 模块

- 支持 LPDDR4 存储器类型

- 支持高达 4266MT/s 的速度

- 多达 2 个具有内联 ECC 的 32 位总线，速率高达 34GB/s

- 通用存储器控制器 (GPMC)

- MAIN 域中有 3 个 512KB 片上 SRAM，受 ECC 保护

### 功能安全：

- 以符合功能安全标准为目标 ( 部分器件型号 )

- 专为功能安全应用开发

- 提供相关文档，可辅助完成最高达 ASIL D/SIL 3 级别的、符合 ISO 26262/IEC 61508 标准的功能安全系统设计

- 系统化能力最高达 ASIL-D/SIL-3

- MCU 域的硬件完整性最高达 ASIL-D/SIL-3

- Main 域的硬件完整性最高达 ASIL-B/SIL-2

- Main 域的扩展 MCU (EMCU) 部分的硬件完整性最高达 ASIL-D/SIL-3

- 安全相关认证

- 通过 TÜV SÜD 高达 ASIL D/SIL 3 等级的 ISO 26262/IEC 61508 认证

- 符合 AEC-Q100 标准 ( 以 Q1 结尾的器件型号 )

### 器件安全 ( 在部分器件型号上 ) :

- 安全启动，提供安全运行时支持

- 客户可编程的根密钥，级别高达 RSA-4K 或 ECC-512

- 嵌入式硬件安全模块

- 加密硬件加速器 - 带 ECC 的 PKA、AES、SHA、RNG、DES 和 3DES

### 高速串行接口：

- 集成以太网交换机，支持 4 个外部端口

- 两个端口支持 5Gb、10Gb USXGMII/XFI

- 所有端口均支持 1Gb、2.5Gb SGMII

- 所有端口均可支持 QSGMII。最多可启用 1 个 QSGMII 并使用全部 4 个内部通道

- 多达 2x2L/1x4L PCI-Express® (PCIe) 第 3 代控制器

- 第 1 代 (2.5GT/s)、第 2 代 (5.0GT/s) 和第 3 代 (8.0GT/s) 运行，具有自动协商功能

- 一个 USB 3.0 双重角色设备 (DRD) 子系统

- 增强型超高速第一代端口

- 支持 Type-C 开关

- 可独立配置为 USB 主机、USB 外设或 USB DRD

- 三个 CSI2.0 4L 摄像头串行接口 RX (CSI-RX) 以及两个具有 DPHY 的 CSI2.0 4L TX (CSI-TX)

- 符合 MIPI CSI 1.3 标准 + MIPI-DPHY 1.2

- CSI-RX 支持 1、2、3 或 4 数据通道模式，每通道速率高达 2.5Gbps

- CSI-TX 支持 1、2 或 4 数据通道模式，每通道速率高达 2.5Gbps

本资源的原文使用英文撰写。为方便起见，TI 提供了译文；由于翻译过程中可能使用了自动化工具，TI 不保证译文的准确性。为确认准确性，请务必访问 [ti.com](http://ti.com) 参考最新的英文版本 ( 控制文档 )。

## 以太网：

- 两个 RGMII/RMII 接口

## 汽车接口：

- 20 个模块化控制器局域网 (MCAN) 模块，具有完整 CAN-FD 支持

## 显示子系统：

- 两个 DSI 4L TX (高达 2.5k)

- 1 个 eDP/DP 接口，具有多显示器支持 (MST)

- 一个 DPI

## 音频接口：

- 5 个多通道音频串行端口 (MCASP) 模块

## 视频加速：

- H.264/H.265 编码/解码，高达 960MP/s

## 闪存接口：

- 嵌入式多媒体卡接口 (eMMC™ 5.1)

- 一个安全数字® 3.0/安全数字输入输出 3.0 接口 (SD3.0/SDIO3.0)

- 具有 2 个通道的通用闪存 (UFS 2.1) 接口

- 两个独立闪存接口，配置为

- 一个 OSPI 或 HyperBus™ 或 QSPI 闪存接口，以及

- 一个 QSPI 闪存接口

## 片上系统 (SoC) 架构：

- 16nm FinFET 技术

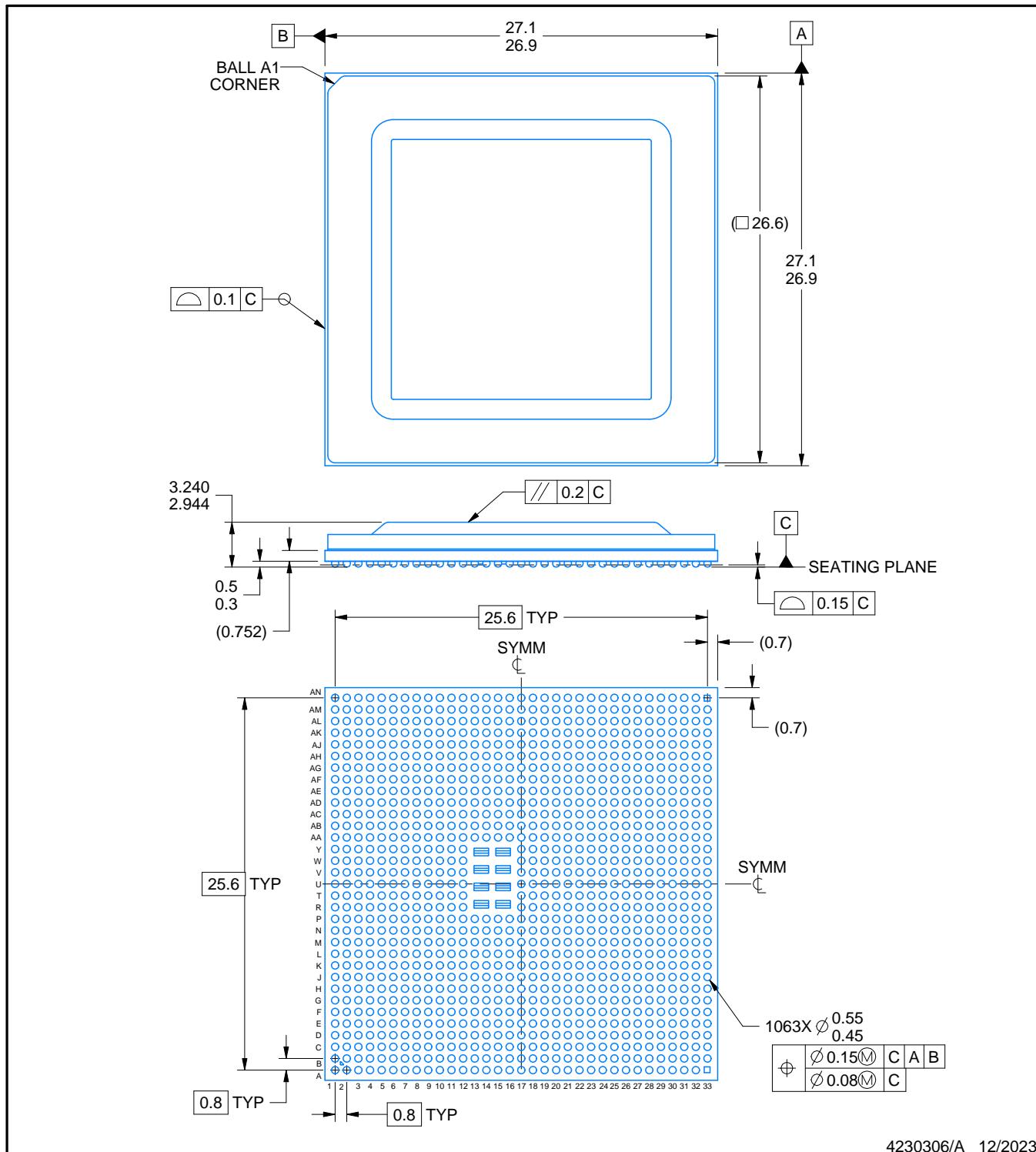

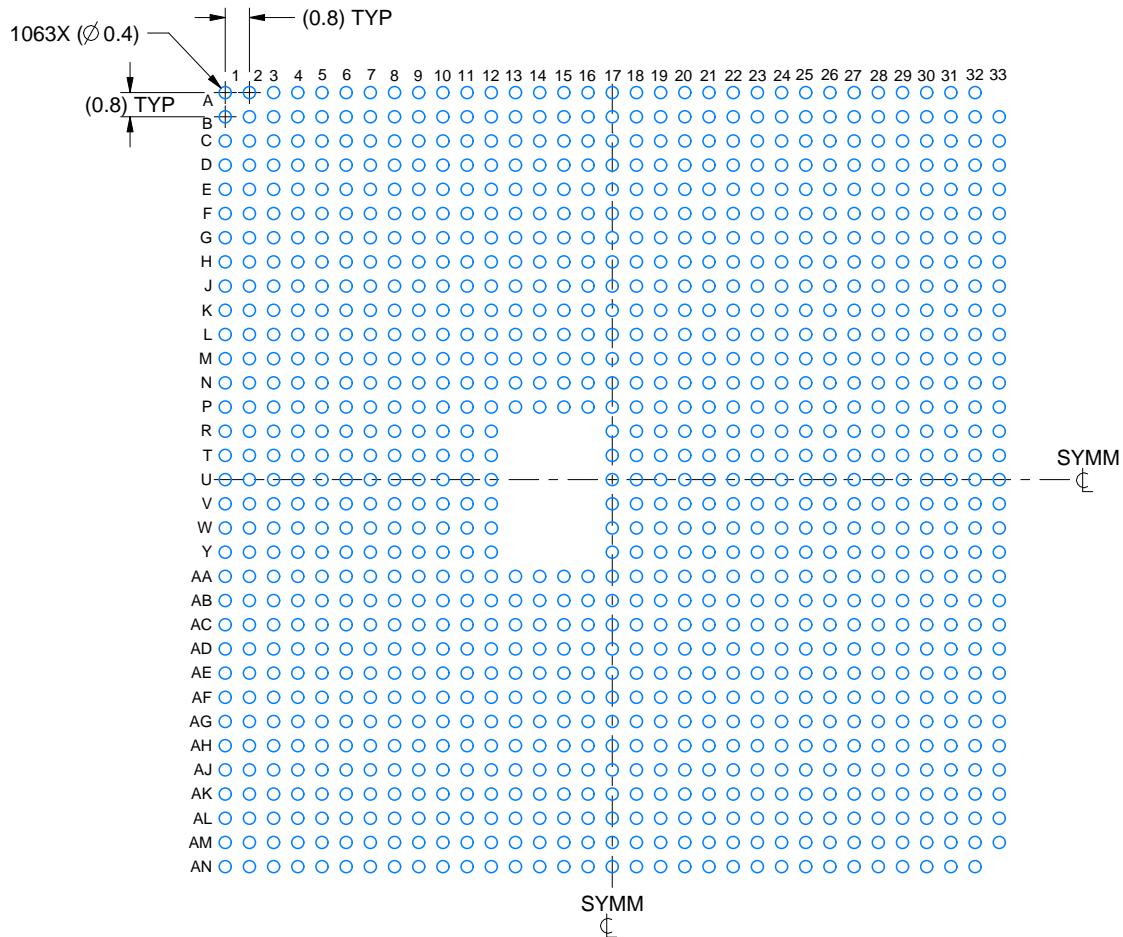

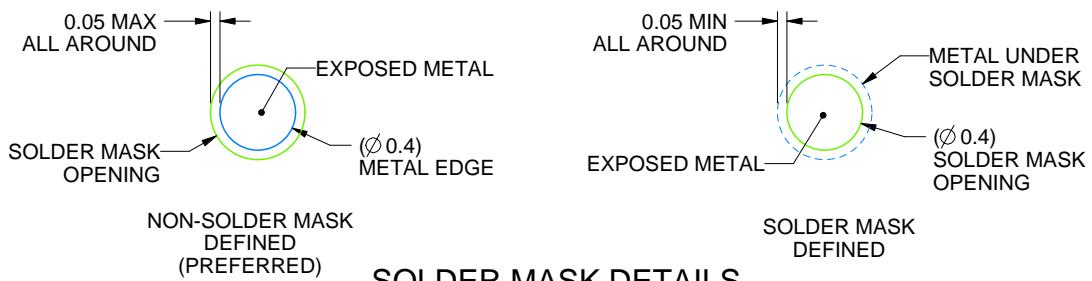

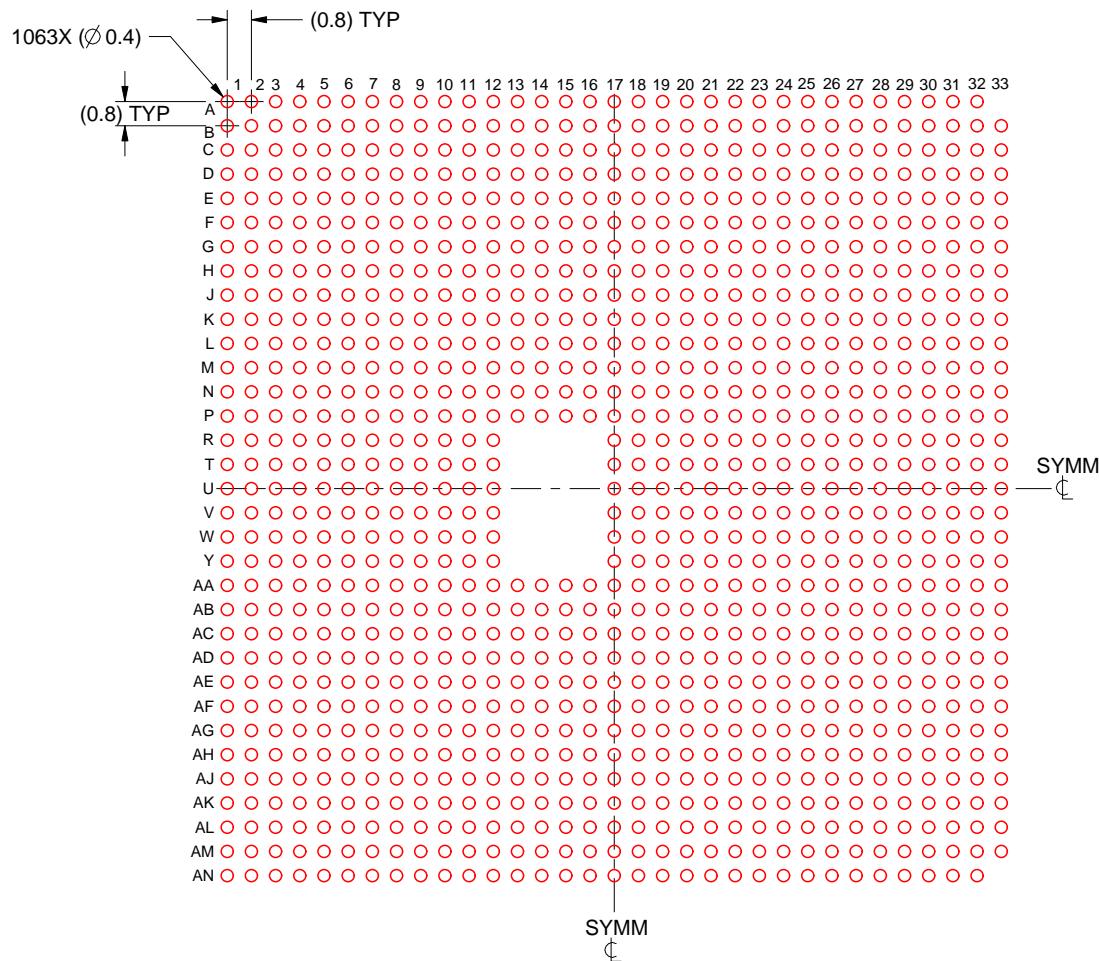

- 27mm × 27mm、0.8mm 间距、1063 引脚 FCBGA (AND)，可实现 IPC 3 级 PCB 布线

## TPS6594-Q1 配套电源管理 IC (PMIC)：

- 功能安全合规性支持最高达 ASIL D/SIL 3

- 灵活的映射，可支持不同的用例

## 2 应用

- 汽车：

- 高级环视和泊车辅助系统

- 自主传感器融合/感知系统，包括摄像头、雷达和激光雷达传感器

- 单传感器和多传感器前置摄像头系统

- 下一代电子后视镜系统

- 非公路用车控制

- ADAS 域控制器

### 3 说明

TDA4VPE-Q1/TDA4APE-Q1 处理器系列基于不断发展的 Jacinto™ 7 架构，面向 ADAS 和自动驾驶车辆 (AV) 应用，基于 TI 在 ADAS 处理器市场上十多年的先进地位所积累的广泛市场知识而构建。在以符合功能安全标准为目标的架构中，独特的高性能计算、深度学习引擎、信号和图像处理专用加速器的组合使 TDA4VPE-Q1/TDA4APE-Q1 器件非常适合多种成像、视觉、雷达、传感器融合和 AI 应用，例如：机器人、移动机械、非公路用车控制器、机器视觉、AI 盒、网关、零售自动化、医疗成像等。TDA4VPE-Q1/TDA4APE-Q1 以业界卓越的功耗/性能比为传统和深度学习算法提供高性能计算，并具有很高的系统集成度，从而使支持集中式 ECU 或独立传感器中多种传感器模式的高级汽车平台实现可扩展性和更低的成本。关键内核包括具有标量和矢量内核的下一代 DSP、专用深度学习和传统算法加速器、用于通用计算的最新 Arm 和 GPU 处理器、集成式下一代成像子系统 (ISP)、视频编解码器、以太网集线器以及隔离式 MCU 岛。所有这些都由汽车级安全硬件加速器提供保护。

#### 主要高性能内核概述

“C7x”下一代 DSP 将 TI 业界先进的 DSP 和 EVE 内核整合到单个性能更高的内核中，并增加了浮点矢量计算功能，从而实现了对旧代码的向后兼容性，同时简化了软件编程。在典型的汽车最高结温 125°C 下运行时，新型“MMAv2”深度学习加速器的单个实例可在业界超低的功率范围内实现高达 8TOPS 的性能。专用的 ADAS/AV 硬件加速器可提供视觉预处理以及距离和运动处理，而不会影响系统性能。

#### 通用计算内核和集成概述

对 Arm® Cortex®-A72 的独立四核集群配置有助于实现多操作系统应用，而且对软件管理程序的需求非常低。四个 Arm® Cortex®-R5F 子系统能够管理低级的时序关键型处理任务，使 Arm® Cortex®-A72 内核不受应用的影响。集成的 IMG BXS-4-64 GPU 可提供高达 50GFLOPS 的性能，从而为增强视觉应用实现动态 3D 渲染。TI 的第 7 代 ISP 以现有出色的 ISP 为基础，能够灵活地处理更广泛的传感器套件，支持更高的位深度，并且具有面向分析应用的特性。集成的诊断和安全功能可支持高达 ASIL-D/SIL-3 级别的操作，同时集成的安全功能可保护数据免受现代攻击。为了实现需要大量数据带宽的系统，提供了 PCIe 集线器和千兆位以太网交换机以及 CSI-2 端口，以支持众多传感器输入的吞吐量。为了进一步集成，TDA4VPE-Q1/TDA4APE-Q1 系列还包含一个 MCU 岛，从而无需使用外部系统微控制器。

#### 封装信息

| 器件型号       | 封装 <sup>(1)</sup>    | 封装尺寸 <sup>(2)</sup> |

|------------|----------------------|---------------------|

| TDA4VPE-Q1 | AND ( FCBGA , 1063 ) | 27mm x 27mm         |

| TDA4APE-Q1 | AND ( FCBGA , 1063 ) | 27mm x 27mm         |

| XJ742S2    | AND ( FCBGA , 1063 ) | 27mm x 27mm         |

(1) 如需更多信息，请参阅 [节 10](#)，机械、封装和可订购信息。

(2) 封装尺寸 (长 × 宽) 为标称值，并包括引脚 (如适用)。

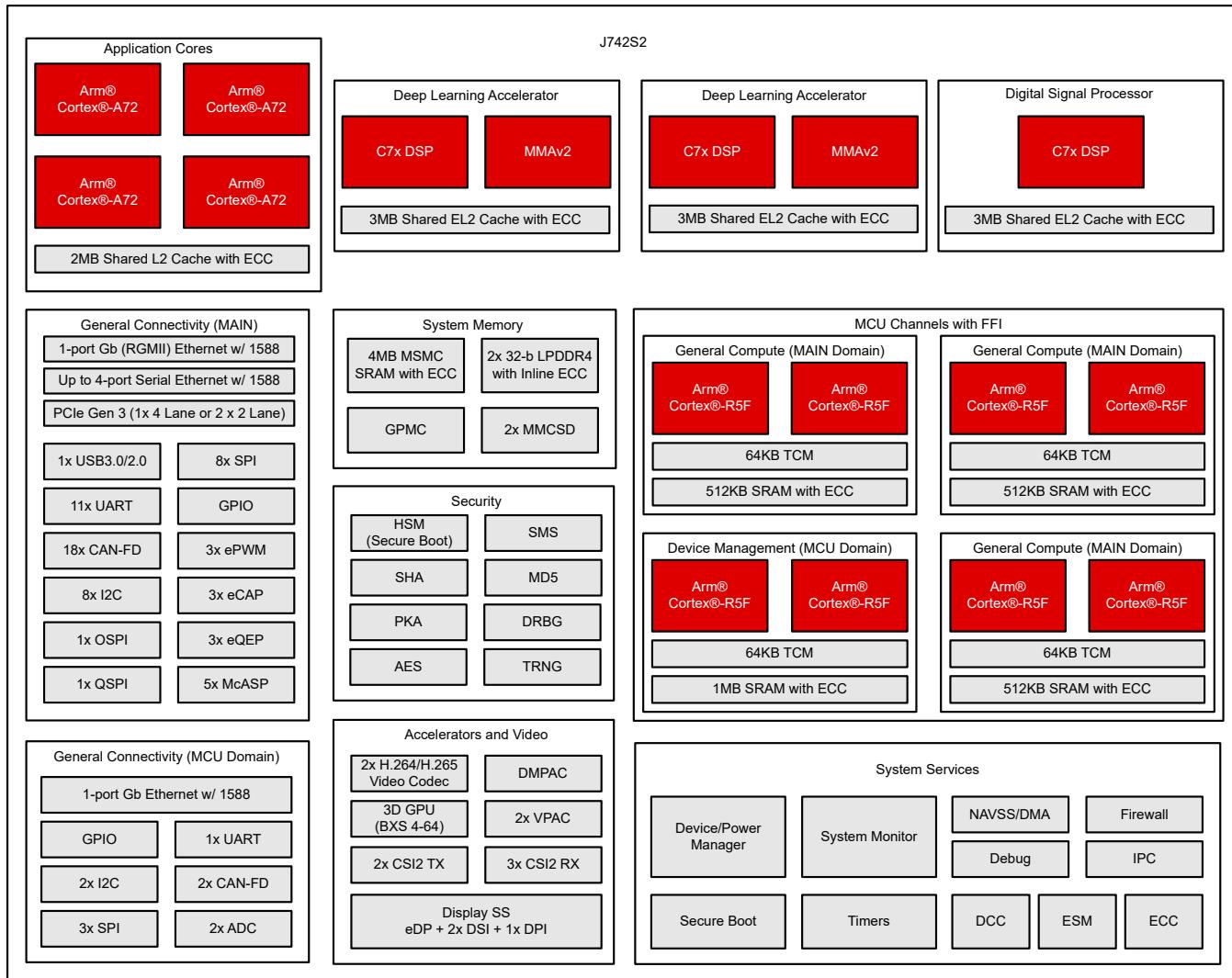

### 3.1 功能方框图

图 3-1 是器件的功能方框图。

#### 备注

要了解 TI 软件开发套件 (SDK) 目前支持的器件功能, 请参阅 [TDA4VH 软件构建表 \(PROCESSOR-SDK-J742S2\)](#)。

图 3-1. 功能方框图

## 内容

|                   |            |                                     |            |

|-------------------|------------|-------------------------------------|------------|

| <b>1 特性</b>       | <b>1</b>   | 6.7 一次性可编程 (OTP) 电子保险丝的 VPP 规格..... | <b>134</b> |

| <b>2 应用</b>       | <b>2</b>   | 6.8 热阻特性.....                       | <b>136</b> |

| <b>3 说明</b>       | <b>3</b>   | 6.9 温度传感器特性.....                    | <b>137</b> |

| 3.1 功能方框图         | <b>4</b>   | 6.10 时序和开关特性.....                   | <b>138</b> |

| <b>4 器件比较</b>     | <b>6</b>   | <b>7 应用、实施和布局</b> .....             | <b>263</b> |

| <b>5 端子配置和功能</b>  | <b>9</b>   | 7.1 器件连接和布局基本准则.....                | <b>263</b> |

| 5.1 引脚图           | <b>9</b>   | 7.2 外设和接口的相关设计信息.....               | <b>263</b> |

| 5.2 引脚属性          | <b>10</b>  | <b>8 器件和文档支持</b> .....              | <b>269</b> |

| 5.3 信号说明          | <b>74</b>  | 8.1 器件命名规则.....                     | <b>269</b> |

| 5.4 引脚连接要求        | <b>119</b> | 8.2 工具与软件.....                      | <b>272</b> |

| <b>6 规格</b>       | <b>123</b> | 8.3 支持资源.....                       | <b>272</b> |

| 6.1 绝对最大额定值       | <b>123</b> | 8.4 商标.....                         | <b>272</b> |

| 6.2 ESD 等级        | <b>124</b> | 8.5 静电放电警告.....                     | <b>272</b> |

| 6.3 通电时间 (POH) 限制 | <b>125</b> | 8.6 术语表.....                        | <b>272</b> |

| 6.4 建议运行条件        | <b>125</b> | <b>9 修订历史记录</b> .....               | <b>272</b> |

| 6.5 运行性能点         | <b>127</b> | <b>10 机械、封装和可订购信息</b> .....         | <b>274</b> |

| 6.6 电气特性          | <b>128</b> | 10.1 封装信息.....                      | <b>274</b> |

## 4 器件比较

表 4-1 展示了 SoC 的特性。

### 备注

要了解 TI 软件开发套件 (SDK) 目前支持的器件功能，请参阅 [TDA4VH 软件构建表 \(PROCESSOR-SDK-J742S2\)](#)。

表 4-1. 器件比较

| 特性 <sup>(9)</sup>           | 参考<br>名称                  | TDA4VPE6               | TDA4APE6               | TDA4VPE4          | TDA4APE4 |

|-----------------------------|---------------------------|------------------------|------------------------|-------------------|----------|

| <b>特性</b>                   |                           |                        |                        |                   |          |

| <b>处理器和加速器</b>              |                           |                        |                        |                   |          |

| 速度等级                        |                           | T                      | T                      | T                 | T        |

| Arm Cortex-A72 微处理器子系统      | Arm A72                   |                        | 四核 <sup>(12)</sup>     |                   |          |

| Arm Cortex-R5F              | Arm R5F                   |                        | 八核                     |                   |          |

|                             | 锁步                        |                        | 可选 <sup>(1)</sup>      |                   |          |

| 安全管理                        | SMS                       |                        | 是                      |                   |          |

| 安全加速器                       | SA                        |                        | 是                      |                   |          |

| C7x 浮点, 矢量 DSP              | C7x DSP                   |                        | 三核                     |                   |          |

| 深度学习加速器                     | MMA                       |                        | 双核                     |                   |          |

| 图形加速器 IMG BXS-4-64          | GPU                       | 是                      | 否                      | 是                 | 否        |

| 深度和运动处理加速器                  | DMPAC                     |                        | 是                      |                   |          |

| 视觉处理加速器                     | VPAC                      | 2                      |                        | 1                 |          |

| 视频编码器/解码器                   | VENC/VDEC                 | 编码/解码 960MP/s          |                        | 编码/解码 480MP/s     |          |

| <b>安全与安防</b>                |                           |                        |                        |                   |          |

| 以符合安全标准为目标                  | 安全                        | 可选 <sup>(1)</sup>      |                        | 可选 <sup>(1)</sup> |          |

| 器件安全性                       | 安全性                       | 可选 <sup>(2)</sup>      |                        | 可选 <sup>(2)</sup> |          |

| 符合 AEC-Q100 标准              | Q1                        | 可选 <sup>(3)</sup>      |                        | 可选 <sup>(3)</sup> |          |

| <b>程序和数据存储</b>              |                           |                        |                        |                   |          |

| MAIN 域中的片上共享存储器 (RAM)       | OCSRAM                    | 3x512KB SRAM           | 3x512KB SRAM           |                   |          |

| MCU 域中的片上共享存储器 (RAM)        | MCU_MSRAM                 | 1MB SRAM               | 1MB SRAM               |                   |          |

| 多核共享存储器控制器                  | MSMC                      | 8MB ( 带 ECC 的片上 SRAM ) | 4MB ( 带 ECC 的片上 SRAM ) |                   |          |

| LPDDR4 DDR 子系统              | DDRSS0 <sup>(5)</sup>     | 32b, 具有内联 ECC          | 32b, 具有内联 ECC          |                   |          |

|                             | DDRSS1 <sup>(5)</sup>     | 32b, 具有内联 ECC          | 32b, 具有内联 ECC          |                   |          |

|                             | DDRSS2 <sup>(4) (5)</sup> |                        | 否                      |                   |          |

|                             | DDRSS3 <sup>(4) (5)</sup> |                        | 否                      |                   |          |

|                             | SECDED                    |                        | 7 位                    |                   |          |

| 通用存储器控制器                    | GPMC                      |                        | 是                      |                   |          |

| <b>外设</b>                   |                           |                        |                        |                   |          |

| 显示子系统                       | DSS                       | 是                      |                        | 是                 |          |

|                             | DSI 4L TX                 | 2                      |                        | 2                 |          |

|                             | eDP 4L                    | 1                      |                        | 1                 |          |

|                             | DPI                       | 1                      |                        | 1                 |          |

| 模块化控制器区域网接口, 具有完整 CAN-FD 支持 | MCAN                      | 20                     |                        | 20                |          |

| 通用 I/O                      | GPIO                      | 155                    |                        | 155               |          |

**表 4-1. 器件比较 (续)**

| 特性 <sup>(9)</sup>                            | 参考<br>名称              | TDA4VPE6                        | TDA4APE6 | TDA4VPE4                        | TDA4APE4 |

|----------------------------------------------|-----------------------|---------------------------------|----------|---------------------------------|----------|

| 内部集成电路接口                                     | I2C                   | 10                              |          | 10                              |          |

| 改进了内部集成电路接口                                  | I3C                   | 1                               |          | 1                               |          |

| 模数转换器                                        | ADC                   | 2                               |          | 2                               |          |

| 带摄像头串行接口的捕获子系统 (CSI2)                        | CSI2.0 4L RX          | 3                               |          | 3                               |          |

|                                              | CSI2.0 4L TX          | 2                               |          | 2                               |          |

| 多通道串行外设接口                                    | MCSPI                 | 11                              |          | 11                              |          |

| 多通道音频串行端口                                    | MCASP0                | 16 个串行器                         |          | 16 个串行器                         |          |

|                                              | MCASP1                | 5 个串行器                          |          | 5 个串行器                          |          |

|                                              | MCASP2                | 5 个串行器                          |          | 5 个串行器                          |          |

|                                              | MCASP3                | 3 个串行器                          |          | 3 个串行器                          |          |

|                                              | MCASP4                | 5 个串行器                          |          | 5 个串行器                          |          |

| 多媒体卡/安全数字接口                                  | MMCSD0                | eMMC<br>( 8 位 )                 |          | eMMC<br>( 8 位 )                 |          |

|                                              | MMCSD1                | SD/SDIO<br>( 4 位 )              |          | SD/SDIO<br>( 4 位 )              |          |

| 通用闪存存储                                       | UFS 2L                | 是                               |          | 是                               |          |

| 闪存子系统 (FSS)                                  | OSPI0                 | 8 位 <sup>(8)</sup>              |          | 8 位 <sup>(8)</sup>              |          |

|                                              | OSPI1 <sup>(10)</sup> | 4 位                             |          | 4 位                             |          |

|                                              | HyperBus              | 是 <sup>(8)</sup>                |          | 是 <sup>(8)</sup>                |          |

| 4 个具有集成型 PHY 的 PCI Express 端口                | PCIE                  | 1x4L 或 2x2L <sup>(6) (11)</sup> |          | 1x4L 或 2x2L <sup>(6) (11)</sup> |          |

| 以太网接口                                        | MCU CPSW2G            | RMII 或 RGMII                    |          | RMII 或 RGMII                    |          |

|                                              | MAIN CPSW2G           | RMII 或 RGMII                    |          | RMII 或 RGMII                    |          |

|                                              | CPSW9G                | 4 端口串行器/解串器 <sup>(6) (7)</sup>  |          | 4 端口串行器/解串器 <sup>(6) (7)</sup>  |          |

| 通用计时器                                        | 计时器                   | 30                              |          | 30                              |          |

| 增强型高分辨率脉宽调制器模块                               | eHRPWM                | 6                               |          | 6                               |          |

| 增强型捕获模块                                      | eCAP                  | 3                               |          | 3                               |          |

| 增强型正交编码器脉冲模块                                 | eQEP                  | 3                               |          | 3                               |          |

| 通用异步接收器/发送器                                  | UART                  | 12                              |          | 12                              |          |

| 具有 SS PHY 的通用串行总线 (USB3.1) 超高速双角色设备 (DRD) 端口 | USB0                  | 是 <sup>(6)</sup>                |          | 是 <sup>(6)</sup>                |          |

- (1) 包括 R5F 锁步和 SIL/ASIL 等级在内的安全特性仅适用于**命名规则说明**表中的器件类型 (Y) 标识符所示的部分器件型号变体。

- (2) 器件安全特性 (包括安全启动和客户可编程密钥) 适用于**命名规则说明**表中的器件类型 (Y) 标识符所示的部分器件型号变体。

- (3) AEC-Q100 鉴定适用于如**命名规则说明**表中的汽车级指示符 (Q1) 标识符所示的部分器件型号变体。

- (4) 此 SoC 的 27mm 封装型号不提供 DDRSS2 和 DDRSS3。如果希望与使用 27mm 封装的系统具有软件兼容性，则不应使用 DDR2/DDR3。

- (5) 必须始终按递增顺序使用 DDRSS0 和 DDRSS1。例如，使用单个 LPDDR 元件时，该元件必须连接到 DDR0\_\* 接口。当使用两个 LPDDR 元件时，它们必须连接到 DDR0\_\* 和 DDR1\_\* 接口。

- (6) DP、SGMII、USB3.0 和 PCIE 共用总共 8 个或 12 个串行器/解串器通道：

- TDA4xPE6 不支持 SERDES2 通道

- TDA4xPE4 不支持 SERDES0 和 SERDES2 通道

- TDA4xPE4 对可用 SERDES 通道上的 PCIe 和 SGMII 具有额外的多路复用限制。引脚属性表“VPE4 APE4”列中显示了串行器/解串器和多路复用器限制。

- (7) **TDA4xPE CPSW** 最多支持 4 个端口。

- 与 TDA4xPE4 相比，TDA4xPE6 支持更高的引脚多路复用灵活性

- 利用 TDA4xPE6，系统设计人员可以根据任何可用端口进行选择，但必须将使用的端口总数限制为四个或更少

- TDA4xPE4 降低了引脚属性表“VPE4 APE4”列中所示的引脚多路复用可用性

以下实例、信号和运行模式适用于 8 个端口：

- PORT1 信号：SGMII1，模式：5Gb、10Gb USXGMII/XFI、2.5Gb SGMII/XAUI、1Gb SGMII、5Gb QSGMII 之一

- PORT2 信号：SGMII2，模式：5Gb、10Gb USXGMII/XFI、2.5Gb SGMII/XAUI、1Gb SGMII、5Gb QSGMII 之一

- PORTn ( n=3 至 8 ) 信号：SGMII<sub>n</sub>，模式：2.5Gb SGMII/XAUI、1Gb SGMII、5Gb QSGMII 之一

如果 QSGMII 用于 SGMII 端口 1 至 4 中的任一个，则 SGMII1/2/3/4 不能用于以太网功能，因为所有 4 个内部 CPSW 端口都映射到选定的 QSGMII SERDES 端口。

如果 QSGMII 用在 SGMII 端口 5 至 8 中的任一个上，则 SGMII5/6/7/8 不能用于以太网功能，因为所有 4 个内部 CPSW 端口都映射到选定的 QSGMII SERDES 端口。

- (8) 2 个同步闪存接口，配置为 OSPI0 和 OSPI1 或 HyperBus 和 OSPI1。

(9) XJ742S2 是超集器件的基本器件型号。软件应限制用于匹配预期生产器件的功能。

(10) OSPI1 模块仅对 4 个引脚进行引脚分配，在一些上下文中被称为 QSPI。

(11) **TDA4xPE PCIe 支持 1x4L 或 2x2L 选项。**

- 与 TDA4xPE4 器件相比，TDA4xPE6 支持更高的引脚多路复用灵活性

- 利用 TDA4xPE6，系统设计人员可以选择任何可用的 PCIe 实例或可用端口，但必须限制为最大 1x4L 或 2x2L

- TDA4xPE4 降低了引脚属性表“VPE4 APE4”列中所示的引脚多路复用可用性

(12) A72SS 四核型号提供一个四核集群，即 A72SS0\_CORE[3:0]。

## 5 端子配置和功能

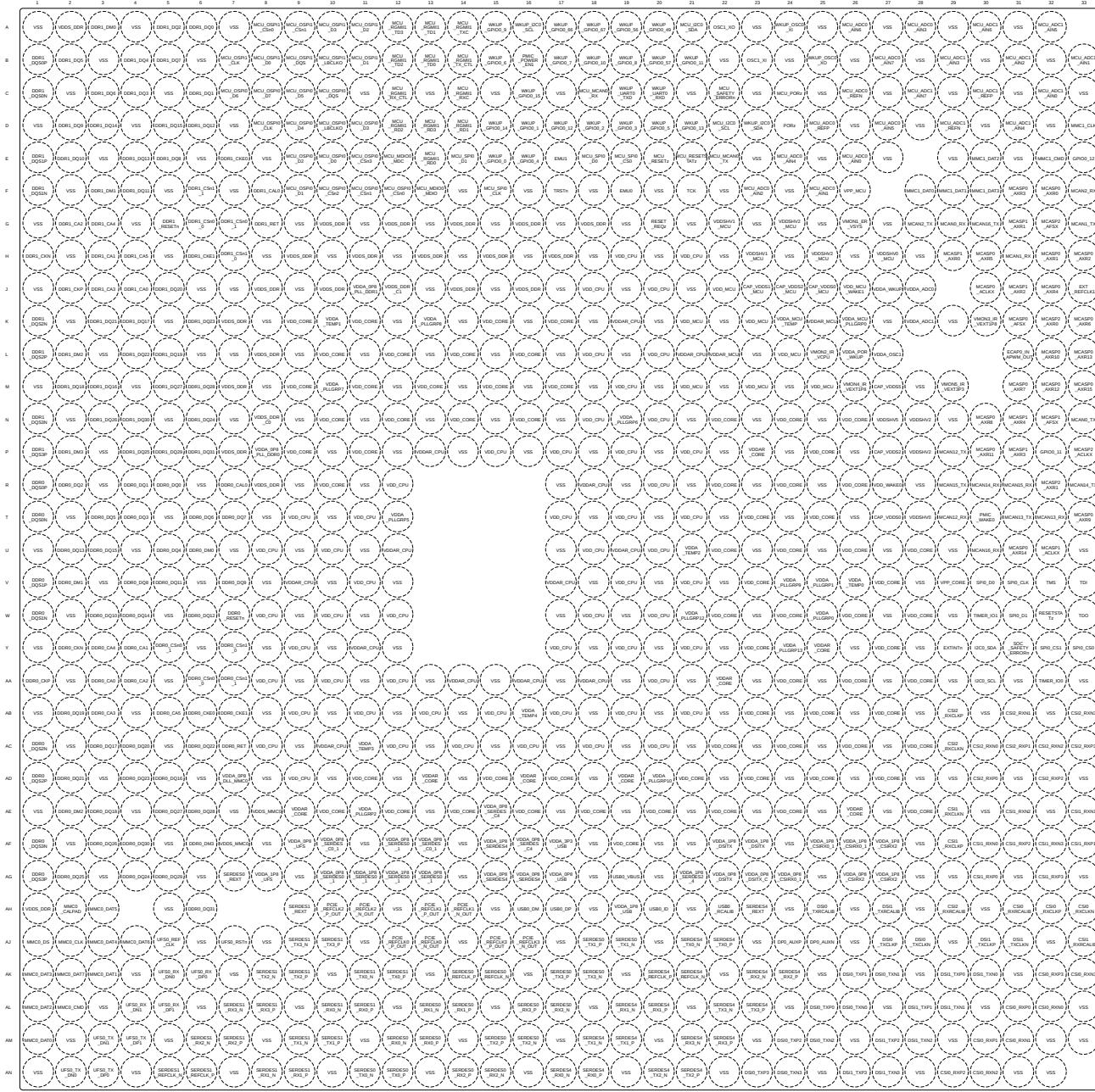

## 5.1 引脚图

### 备注

在整个文档中，术语“焊球”、“引脚”和“端子”可互换使用。仅在提及物理封装时才尝试使用“焊球”。

图 5-1 展示了 1063 球倒装晶片球栅阵列 (FCBGA) 封装的焊球位置，用以快速找到信号名称和球栅编号。该图应与表 5-1 至表 5-118 (引脚属性表和所有信号说明表，包括引脚连接要求表) 配合使用。

图 5-1. AND FCBGA-N1063 引脚图 (顶视图)

## 5.2 引脚属性

以下列表介绍了表 5-1 引脚属性 (AND 封装) 表中每一列的内容：

1. **焊球编号**：分配给 Ball Grid Array 封装每个端子的焊球编号。

2. **焊球名称**：分配给 Ball Grid Array 封装每个端子的焊球名称（该名称通常取自主 MUXMODE 0 信号功能）。

3. **信号名称**：与焊球相关的所有专用和引脚多路复用信号功能的信号名称。

### 备注

许多器件引脚支持多种信号功能。一些信号功能是通过与引脚关联的单层多路复用器来选择的。其他信号功能通过两层或多层多路复用器进行选择，其中一层与引脚相关联，其他层与外围逻辑功能相关联。

**表 5-1 引脚属性 (AND 封装) 表**仅定义了引脚上的信号多路复用。有关引脚信号多路复用的更多信息，请参阅器件 TRM 的器件配置一章中的焊盘配置寄存器一节。有关与外设信号多路复用相关的信息，请参阅器件 TRM 中相应的外设章节。

4. **多路复用模式**：与每个引脚多路复用信号功能相关的 MUXMODE 值：

- a. MUXMODE 0 是主要引脚多路复用信号功能。然而，主要引脚多路复用信号功能不一定是默认引脚多路复用信号功能。

### 备注

“复位之后的多路复用模式”列中的值定义了 MCU\_PORz 被置为无效时选择的默认引脚多路复用信号功能。

- b. MUXMODE 值 1 至 15 可用于引脚多路复用信号功能。然而，并非所有 MUXMODE 值都已实现。仅有的一些有效 MUXMODE 值是引脚属性表中定义为引脚多路复用信号功能的值。只应使用 MUXMODE 的有效值。

- c. 自举定义了 SOC 配置引脚，其中应用于每个引脚的逻辑状态在 PORz\_OUT 的上升沿被锁存。这些输入信号功能固定到各自的引脚，不能通过 MUXMODE 进行编程。

- d. 空框表示不适用。

### 备注

为了使器件正常运行，必须避免以下 MUXMODE 配置。

- 不支持将多个引脚配置为同一引脚多路复用信号功能的输入，因为这可能会产生意外结果。

- 将引脚配置为未定义的引脚多路复用模式将导致引脚行为未定义。

5. **VPE4 APE4**：表示 TDA4VPE4、TDA4APE4 器件支持的 MUXMODE。“否”表示不支持该 MUXMODE。空框表示支持。

6. **类型**：信号类型和方向：

- I = 输入

- O = 输出

- OD = 输出，具有开漏输出功能

- IO = 输入、输出或同时输入和输出

- IOD = 输入、输出或同时输入和输出，具有开漏输出功能

- IOZ = 输入、输出或同时输入和输出，具有三态输出功能

- OZ = 具有三态输出功能的输出

- A = 模拟

- PWR = 电源

- GND = 接地

- CAP = LDO 电容器。

7. **DSIS** : 未选择的输入状态 (DSIS) 指示当 MUXMODE 未选择引脚多路复用信号功能时驱动到子系统输入的状态 ( 逻辑 “0” 、逻辑 “1” 或 “焊盘” 电平 ) 。

- 0 : 逻辑 0 被驱动至子系统输入。

- 1 : 逻辑 1 被驱动至子系统输入。

- 焊盘 : 焊盘的逻辑状态被驱动至子系统输入。

- 空框表示不适用。

8. **复位期间的焊球状态 ( RX/TX/拉动 )** : MCU\_PORz 被置为有效时的端子状态 , 其中 RX 定义输入缓冲器的状态 , TX 定义输出缓冲器的状态 , “拉动” 定义内部拉动电阻器的状态 :

- RX ( 输入缓冲器 )

- 关闭 : 输入缓冲器被禁用。

- 亮 : 输入缓冲器被启用。

- TX ( 输出缓冲器 )

- 关闭 : 输出缓冲器被禁用。

- 低电平 : 输出缓冲器被启用并驱动  $V_{OL}$ 。

- 高电平 : 输出缓冲器被启用并驱动  $V_{OH}$ 。

- 拉动 ( 内部拉电阻器 )

- 关闭 : 内部拉电阻器被关闭。

- 上拉 : 内部上拉电阻器被开启。

- 下拉 : 内部下拉电阻器被开启。

- 不适用 : 不适用。

- 空框表示不适用。

9. **复位之后的焊球状态 ( RX/TX/拉动 )** : MCU\_PORz 被置为无效后的端子状态 , 其中 RX 定义输入缓冲器的状态 , TX 定义输出缓冲器的状态 , “拉动” 定义内部拉动电阻器的状态 :

- RX ( 输入缓冲器 )

- 关闭 : 输入缓冲器被禁用。

- 亮 : 输入缓冲器被启用。

- TX ( 输出缓冲器 )

- 关闭 : 输出缓冲器被禁用。

- SS : 使用 MUXMODE 选择的子系统决定输出缓冲器状态。

- 拉动 ( 内部拉电阻器 )

- 关闭 : 内部拉电阻器被关闭。

- 上拉 : 内部上拉电阻器被开启。

- 下拉 : 内部下拉电阻器被开启。

- 不适用 : 不适用。

- 空框、不适用或 “-” 表示不适用。

10. **复位之后的多路复用模式** : 该列中的值定义了 MCU\_PORz 被置为无效后的默认引脚多路复用信号功能。

- 空框、不适用或 “-” 表示不适用。

11. **I/O 电压值** : 该列介绍了相应电源的 I/O 工作电压选项 ( 如果适用 ) 。

- 空框表示不适用。

- 有关更多信息 , 请参阅 [节 6.4 建议运行条件](#) 中为每个电源定义的有效工作电压范围。

12. **电源** : 相关 I/O 的电源 ( 如果适用 ) 。

- 空框表示不适用。

13. **HYS** : 指示与该 I/O 关联的输入缓冲器是否具有迟滞 :

- 是 : 具有迟滞

- 否 : 不具有迟滞

- 空框表示不适用。

有关更多信息，请参阅[节 6.6 电气特性](#)中的迟滞值。

**14. 缓冲器类型**：该列定义与端子关联的缓冲器类型。该信息可用于确定适用的电气特性表。

空框表示不适用。

有关电气特性，请参阅[节 6.6 电气特性](#)中相应的缓冲器类型表。

**15. 上拉/下拉类型**：指示存在内部上拉或下拉电阻器。可通过软件来启用或禁用上拉和下拉电阻器。

- PU：内部上拉

- PD：内部下拉

- PU/PD：内部上拉和下拉

- 空框表示无内部拉到。

---

#### 备注

不支持将两个引脚配置为同一引脚多路复用信号功能，因为这可能会产生意外结果。适当的软件配置可以轻松防止这种情况发生。

当某焊盘被设定为未由引脚多路复用定义的多路复用模式时，该焊盘的运行方式是未定义的。必须避免这种情况。

---

**16. PADCONFIG 寄存器**：与焊球关联的 IO 焊盘配置寄存器的名称。

**17. PADCONFIG 地址**：与焊球关联的 IO 焊盘配置寄存器的物理地址。

**表 5-1. 引脚属性 (AND 封装)**

| 焊球<br>编号 [1] | 焊球名称 [2]<br>PADCONFIG 寄存器 [16]<br>PADCONFIG 地址 [17] | 信号名称 [3]      | 多路复用<br>模式 [4] | VPE4<br>APE4<br>[5] | 类型 [6] | DSIS<br>[7] | 复位<br>期间的<br>焊球状态<br>( RX/TX/拉空 )<br>[8] | 复位<br>之后的<br>焊球状态<br>( RX/TX/拉空 )<br>[9] | 复位<br>之后的<br>多路复用<br>模式 [10] | I/O<br>工作<br>电压 [11] | 电源 [12]                                 | HYS<br>[13] | 缓冲器<br>类型 [14] | 上拉/<br>下拉<br>类型 [15] |

|--------------|-----------------------------------------------------|---------------|----------------|---------------------|--------|-------------|------------------------------------------|------------------------------------------|------------------------------|----------------------|-----------------------------------------|-------------|----------------|----------------------|

| T27          | CAP_VDDSO                                           | CAP_VDDSO     |                |                     | CAP    |             |                                          |                                          |                              |                      |                                         |             |                |                      |

| J25          | CAP_VDDSO MCU                                       | CAP_VDDSO MCU |                |                     | CAP    |             |                                          |                                          |                              |                      |                                         |             |                |                      |

| J23          | CAP_VDDS1 MCU                                       | CAP_VDDS1 MCU |                |                     | CAP    |             |                                          |                                          |                              |                      |                                         |             |                |                      |

| P27          | CAP_VDDS2                                           | CAP_VDDS2     |                |                     | CAP    |             |                                          |                                          |                              |                      |                                         |             |                |                      |

| J24          | CAP_VDDS2 MCU                                       | CAP_VDDS2 MCU |                |                     | CAP    |             |                                          |                                          |                              |                      |                                         |             |                |                      |

| M27          | CAP_VDD5                                            | CAP_VDD5      |                |                     | CAP    |             |                                          |                                          |                              |                      |                                         |             |                |                      |

| AH33         | CSI0_RXCLKN                                         | CSI0_RXCLKN   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AH32         | CSI0_RXCLKP                                         | CSI0_RXCLKP   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AH31         | CSI0_RXRCALIB                                       | CSI0_RXRCALIB |                |                     | A      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AE29         | CSI1_RXCLKN                                         | CSI1_RXCLKN   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AF29         | CSI1_RXCLKP                                         | CSI1_RXCLKP   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AJ33         | CSI1_RXRCALIB                                       | CSI1_RXRCALIB |                |                     | A      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AC29         | CSI2_RXCLKN                                         | CSI2_RXCLKN   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AB29         | CSI2_RXCLKP                                         | CSI2_RXCLKP   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AH29         | CSI2_RXRCALIB                                       | CSI2_RXRCALIB |                |                     | A      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AL32         | CSI0_RXN0                                           | CSI0_RXN0     |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AM31         | CSI0_RXN1                                           | CSI0_RXN1     |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

表 5-1. 引脚属性 (AND 封装) (续)

| 焊球<br>编号 [1] | 焊球名称 [2]<br>PADCONFIG 寄存器 [16]<br>PADCONFIG 地址 [17] | 信号名称 [3]  | 多路复用<br>模式 [4] | VPE4<br>APE4<br>[5] | 类型 [6] | DSIS<br>[7] | 复位<br>期间的<br>焊球状态<br>( RX/TX/拉空 )<br>[8] | 复位<br>之后的<br>焊球状态<br>( RX/TX/拉空 )<br>[9] | 复位<br>之后的<br>多路复用<br>模式 [10] | I/O<br>工作<br>电压 [11] | 电源 [12]                                 | HYS<br>[13] | 缓冲器<br>类型 [14] | 上拉/<br>下拉<br>类型 [15] |

|--------------|-----------------------------------------------------|-----------|----------------|---------------------|--------|-------------|------------------------------------------|------------------------------------------|------------------------------|----------------------|-----------------------------------------|-------------|----------------|----------------------|

| AN30         | CSI0_RXN2                                           | CSI0_RXN2 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AK33         | CSI0_RXN3                                           | CSI0_RXN3 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AL31         | CSI0_RXP0                                           | CSI0_RXP0 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AM30         | CSI0_RXP1                                           | CSI0_RXP1 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AN29         | CSI0_RXP2                                           | CSI0_RXP2 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AK32         | CSI0_RXP3                                           | CSI0_RXP3 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AF30         | CSI1_RXN0                                           | CSI1_RXN0 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AE33         | CSI1_RXN1                                           | CSI1_RXN1 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AE31         | CSI1_RXN2                                           | CSI1_RXN2 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AF32         | CSI1_RXN3                                           | CSI1_RXN3 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AG30         | CSI1_RXP0                                           | CSI1_RXP0 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AF33         | CSI1_RXP1                                           | CSI1_RXP1 |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

**表 5-1. 引脚属性 (AND 封装) (续)**

| 焊球<br>编号 [1] | 焊球名称 [2]<br>PADCONFIG 寄存器 [16]<br>PADCONFIG 地址 [17] | 信号名称 [3]    | 多路复用<br>模式 [4] | VPE4<br>APE4<br>[5] | 类型 [6] | DSIS<br>[7] | 复位<br>期间的<br>焊球状态<br>( RX/TX/拉动 )<br>[8] | 复位<br>之后的<br>焊球状态<br>( RX/TX/拉动 )<br>[9] | 复位<br>之后的<br>多路复用<br>模式 [10] | I/O<br>工作<br>电压 [11] | 电源 [12]                                 | HYS<br>[13] | 缓冲器<br>类型 [14] | 上拉/<br>下拉<br>类型 [15] |

|--------------|-----------------------------------------------------|-------------|----------------|---------------------|--------|-------------|------------------------------------------|------------------------------------------|------------------------------|----------------------|-----------------------------------------|-------------|----------------|----------------------|

| AF31         | CSI1_RXP2                                           | CSI1_RXP2   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AG32         | CSI1_RXP3                                           | CSI1_RXP3   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX0_1/<br>VDDA_1P8_CSIRX0_1 |             | D-PHY          |                      |

| AC30         | CSI2_RXN0                                           | CSI2_RXN0   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AB31         | CSI2_RXN1                                           | CSI2_RXN1   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AC32         | CSI2_RXN2                                           | CSI2_RXN2   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AB33         | CSI2_RXN3                                           | CSI2_RXN3   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AD30         | CSI2_RXP0                                           | CSI2_RXP0   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AC31         | CSI2_RXP1                                           | CSI2_RXP1   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AD32         | CSI2_RXP2                                           | CSI2_RXP2   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| AC33         | CSI2_RXP3                                           | CSI2_RXP3   |                |                     | I      |             |                                          |                                          |                              | 1.8V                 | VDDA_0P8_CSIRX2/<br>VDDA_1P8_CSIRX2     |             | D-PHY          |                      |

| Y2           | DDR0_CKN                                            | DDR0_CKN    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0                |             | DDR            |                      |

| AA1          | DDR0_CKP                                            | DDR0_CKP    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0                |             | DDR            |                      |

| W7           | DDR0_RESETn                                         | DDR0_RESETn |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0                |             | DDR            |                      |

| AC7          | DDR0_RET                                            | DDR0_RET    |                |                     | I      |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0                |             | DDR            |                      |

| H1           | DDR1_CKN                                            | DDR1_CKN    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1                |             | DDR            |                      |

| J2           | DDR1_CKP                                            | DDR1_CKP    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1                |             | DDR            |                      |

| G5           | DDR1_RESETn                                         | DDR1_RESETn |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1                |             | DDR            |                      |

| G8           | DDR1_RET                                            | DDR1_RET    |                |                     | I      |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1                |             | DDR            |                      |

| AA3          | DDR0_CA0                                            | DDR0_CA0    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0                |             | DDR            |                      |

| Y4           | DDR0_CA1                                            | DDR0_CA1    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0                |             | DDR            |                      |

| AA4          | DDR0_CA2                                            | DDR0_CA2    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0                |             | DDR            |                      |

表 5-1. 引脚属性 (AND 封装) (续)

| 焊球<br>编号 [1] | 焊球名称 [2]<br>PADCONFIG 寄存器 [16]<br>PADCONFIG 地址 [17] | 信号名称 [3]    | 多路复用<br>模式 [4] | VPE4<br>APE4<br>[5] | 类型 [6] | DSIS<br>[7] | 复位<br>期间的<br>焊球状态<br>( RX/TX/拉空 )<br>[8] | 复位<br>之后的<br>焊球状态<br>( RX/TX/拉空 )<br>[9] | 复位<br>之后的<br>多路复用<br>模式 [10] | I/O<br>工作<br>电压 [11] | 电源 [12]                  | HYS<br>[13] | 缓冲器<br>类型 [14] | 上拉/<br>下拉<br>类型 [15] |

|--------------|-----------------------------------------------------|-------------|----------------|---------------------|--------|-------------|------------------------------------------|------------------------------------------|------------------------------|----------------------|--------------------------|-------------|----------------|----------------------|

| AB3          | DDR0_CA3                                            | DDR0_CA3    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| Y3           | DDR0_CA4                                            | DDR0_CA4    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AB5          | DDR0_CA5                                            | DDR0_CA5    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| R7           | DDR0_CAL0                                           | DDR0_CAL0   |                |                     | A      |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AB6          | DDR0_CKE0                                           | DDR0_CKE0   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AB7          | DDR0_CKE1                                           | DDR0_CKE1   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AA6          | DDR0_CSn0_0                                         | DDR0_CSn0_0 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| Y5           | DDR0_CSn0_1                                         | DDR0_CSn0_1 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| Y7           | DDR0_CSn1_0                                         | DDR0_CSn1_0 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AA7          | DDR0_CSn1_1                                         | DDR0_CSn1_1 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| U6           | DDR0_DM0                                            | DDR0_DM0    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| V2           | DDR0_DM1                                            | DDR0_DM1    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AE2          | DDR0_DM2                                            | DDR0_DM2    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AF6          | DDR0_DM3                                            | DDR0_DM3    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| R5           | DDR0_DQ0                                            | DDR0_DQ0    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| R4           | DDR0_DQ1                                            | DDR0_DQ1    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| R2           | DDR0_DQ2                                            | DDR0_DQ2    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| T4           | DDR0_DQ3                                            | DDR0_DQ3    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| U5           | DDR0_DQ4                                            | DDR0_DQ4    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| T3           | DDR0_DQ5                                            | DDR0_DQ5    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| T6           | DDR0_DQ6                                            | DDR0_DQ6    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| T7           | DDR0_DQ7                                            | DDR0_DQ7    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

**表 5-1. 引脚属性 (AND 封装) (续)**

| 焊球<br>编号 [1] | 焊球名称 [2]<br>PADCONFIG 寄存器 [16]<br>PADCONFIG 地址 [17] | 信号名称 [3]  | 多路复用<br>模式 [4] | VPE4<br>APE4<br>[5] | 类型 [6] | DSIS<br>[7] | 复位<br>期间的<br>焊球状态<br>( RX/TX/拉空 )<br>[8] | 复位<br>之后的<br>焊球状态<br>( RX/TX/拉空 )<br>[9] | 复位<br>之后的<br>多路复用<br>模式 [10] | I/O<br>工作<br>电压 [11] | 电源 [12]                  | HYS<br>[13] | 缓冲器<br>类型 [14] | 上拉/<br>下拉<br>类型 [15] |

|--------------|-----------------------------------------------------|-----------|----------------|---------------------|--------|-------------|------------------------------------------|------------------------------------------|------------------------------|----------------------|--------------------------|-------------|----------------|----------------------|

| V4           | DDR0_DQ8                                            | DDR0_DQ8  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| V7           | DDR0_DQ9                                            | DDR0_DQ9  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| W3           | DDR0_DQ10                                           | DDR0_DQ10 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| V5           | DDR0_DQ11                                           | DDR0_DQ11 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| W6           | DDR0_DQ12                                           | DDR0_DQ12 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| U2           | DDR0_DQ13                                           | DDR0_DQ13 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| W4           | DDR0_DQ14                                           | DDR0_DQ14 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| U3           | DDR0_DQ15                                           | DDR0_DQ15 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AD5          | DDR0_DQ16                                           | DDR0_DQ16 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AC3          | DDR0_DQ17                                           | DDR0_DQ17 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AE3          | DDR0_DQ18                                           | DDR0_DQ18 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AB2          | DDR0_DQ19                                           | DDR0_DQ19 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AC4          | DDR0_DQ20                                           | DDR0_DQ20 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AD2          | DDR0_DQ21                                           | DDR0_DQ21 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AC6          | DDR0_DQ22                                           | DDR0_DQ22 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AD4          | DDR0_DQ23                                           | DDR0_DQ23 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AG4          | DDR0_DQ24                                           | DDR0_DQ24 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AG2          | DDR0_DQ25                                           | DDR0_DQ25 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AF3          | DDR0_DQ26                                           | DDR0_DQ26 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AE5          | DDR0_DQ27                                           | DDR0_DQ27 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AE6          | DDR0_DQ28                                           | DDR0_DQ28 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AG5          | DDR0_DQ29                                           | DDR0_DQ29 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

表 5-1. 引脚属性 (AND 封装) (续)

| 焊球<br>编号 [1] | 焊球名称 [2]<br>PADCONFIG 寄存器 [16]<br>PADCONFIG 地址 [17] | 信号名称 [3]    | 多路复用<br>模式 [4] | VPE4<br>APE4<br>[5] | 类型 [6] | DSIS<br>[7] | 复位<br>期间的<br>焊球状态<br>( RX/TX/拉空 )<br>[8] | 复位<br>之后的<br>焊球状态<br>( RX/TX/拉空 )<br>[9] | 复位<br>之后的<br>多路复用<br>模式 [10] | I/O<br>工作<br>电压 [11] | 电源 [12]                  | HYS<br>[13] | 缓冲器<br>类型 [14] | 上拉/<br>下拉<br>类型 [15] |

|--------------|-----------------------------------------------------|-------------|----------------|---------------------|--------|-------------|------------------------------------------|------------------------------------------|------------------------------|----------------------|--------------------------|-------------|----------------|----------------------|

| AF4          | DDR0_DQ30                                           | DDR0_DQ30   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AH6          | DDR0_DQ31                                           | DDR0_DQ31   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| T1           | DDR0_DQS0N                                          | DDR0_DQS0N  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| R1           | DDR0_DQS0P                                          | DDR0_DQS0P  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| W1           | DDR0_DQS1N                                          | DDR0_DQS1N  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| V1           | DDR0_DQS1P                                          | DDR0_DQS1P  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AC1          | DDR0_DQS2N                                          | DDR0_DQS2N  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AD1          | DDR0_DQS2P                                          | DDR0_DQS2P  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AF1          | DDR0_DQS3N                                          | DDR0_DQS3N  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| AG1          | DDR0_DQS3P                                          | DDR0_DQS3P  |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C0 |             | DDR            |                      |

| J4           | DDR1_CA0                                            | DDR1_CA0    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| H3           | DDR1_CA1                                            | DDR1_CA1    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| G2           | DDR1_CA2                                            | DDR1_CA2    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| J3           | DDR1_CA3                                            | DDR1_CA3    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| G3           | DDR1_CA4                                            | DDR1_CA4    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| H4           | DDR1_CA5                                            | DDR1_CA5    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| F8           | DDR1_CAL0                                           | DDR1_CAL0   |                |                     | A      |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| E7           | DDR1_CKE0                                           | DDR1_CKE0   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| H6           | DDR1_CKE1                                           | DDR1_CKE1   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| G6           | DDR1_CSn0_0                                         | DDR1_CSn0_0 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| G7           | DDR1_CSn0_1                                         | DDR1_CSn0_1 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| H7           | DDR1_CSn1_0                                         | DDR1_CSn1_0 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

**表 5-1. 引脚属性 (AND 封装) (续)**

| 焊球<br>编号 [1] | 焊球名称 [2]<br>PADCONFIG 寄存器 [16]<br>PADCONFIG 地址 [17] | 信号名称 [3]    | 多路复用<br>模式 [4] | VPE4<br>APE4<br>[5] | 类型 [6] | DSIS<br>[7] | 复位<br>期间的<br>焊球状态<br>( RX/TX/拉空 )<br>[8] | 复位<br>之后的<br>焊球状态<br>( RX/TX/拉空 )<br>[9] | 复位<br>之后的<br>多路复用<br>模式 [10] | I/O<br>工作<br>电压 [11] | 电源 [12]                  | HYS<br>[13] | 缓冲器<br>类型 [14] | 上拉/<br>下拉<br>类型 [15] |

|--------------|-----------------------------------------------------|-------------|----------------|---------------------|--------|-------------|------------------------------------------|------------------------------------------|------------------------------|----------------------|--------------------------|-------------|----------------|----------------------|

| F6           | DDR1_CSn1_1                                         | DDR1_CSn1_1 |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| A3           | DDR1_DM0                                            | DDR1_DM0    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| F3           | DDR1_DM1                                            | DDR1_DM1    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| L2           | DDR1_DM2                                            | DDR1_DM2    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| P2           | DDR1_DM3                                            | DDR1_DM3    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| A6           | DDR1_DQ0                                            | DDR1_DQ0    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| C6           | DDR1_DQ1                                            | DDR1_DQ1    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| A5           | DDR1_DQ2                                            | DDR1_DQ2    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| C4           | DDR1_DQ3                                            | DDR1_DQ3    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| B4           | DDR1_DQ4                                            | DDR1_DQ4    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| B2           | DDR1_DQ5                                            | DDR1_DQ5    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| C3           | DDR1_DQ6                                            | DDR1_DQ6    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| B5           | DDR1_DQ7                                            | DDR1_DQ7    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| E5           | DDR1_DQ8                                            | DDR1_DQ8    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| D2           | DDR1_DQ9                                            | DDR1_DQ9    |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| E2           | DDR1_DQ10                                           | DDR1_DQ10   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| F4           | DDR1_DQ11                                           | DDR1_DQ11   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| D6           | DDR1_DQ12                                           | DDR1_DQ12   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

| E4           | DDR1_DQ13                                           | DDR1_DQ13   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |

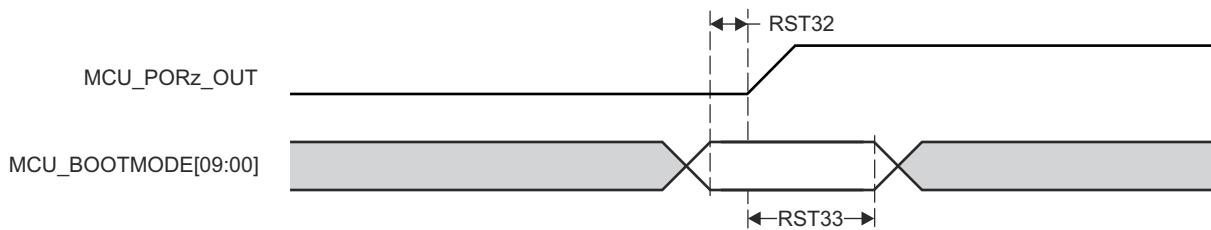

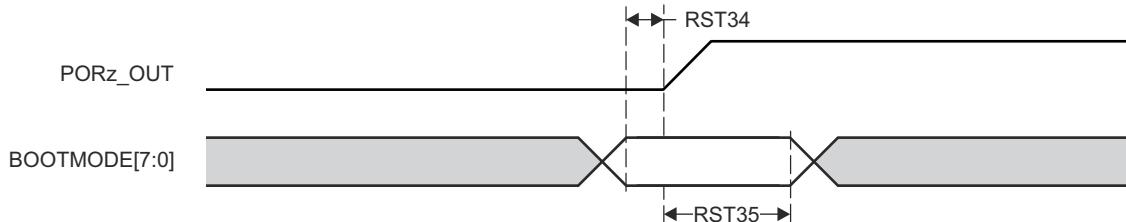

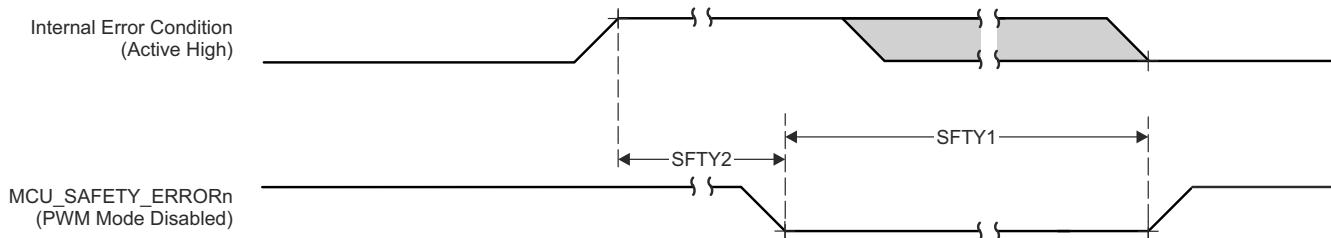

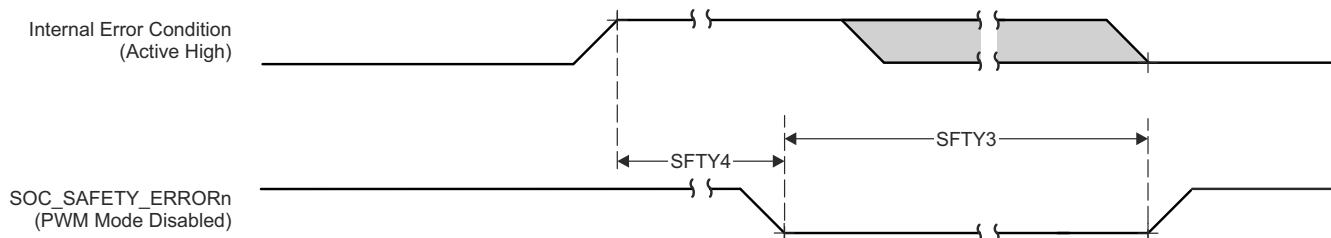

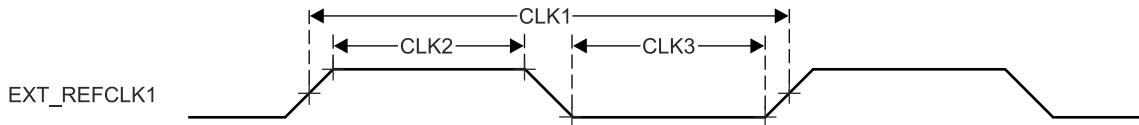

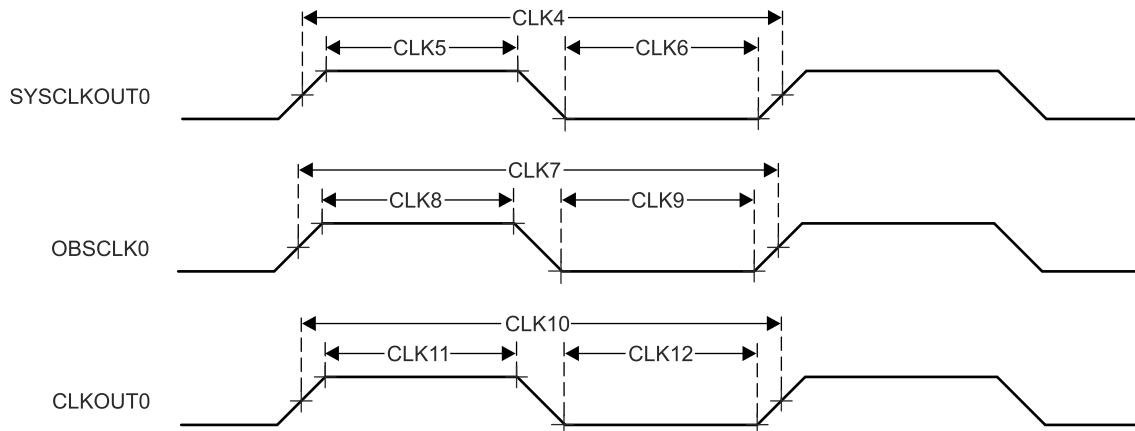

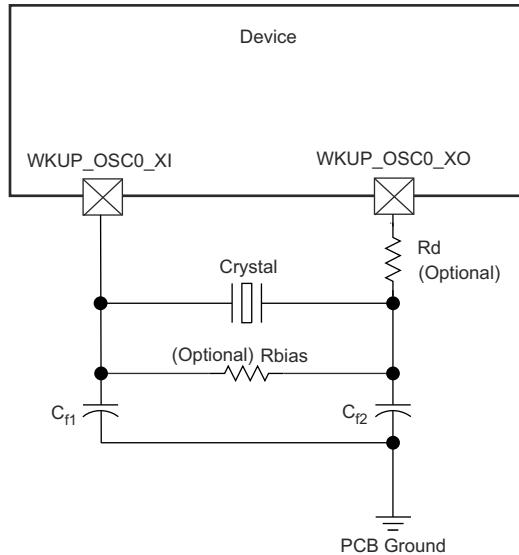

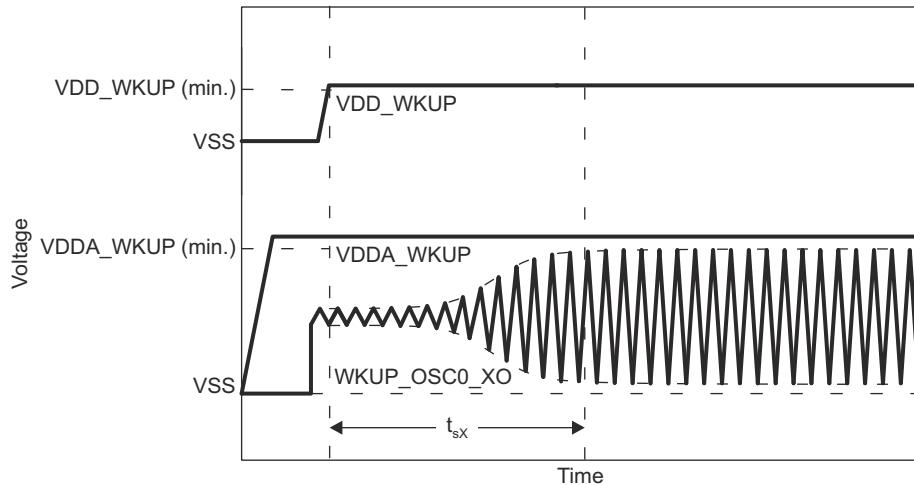

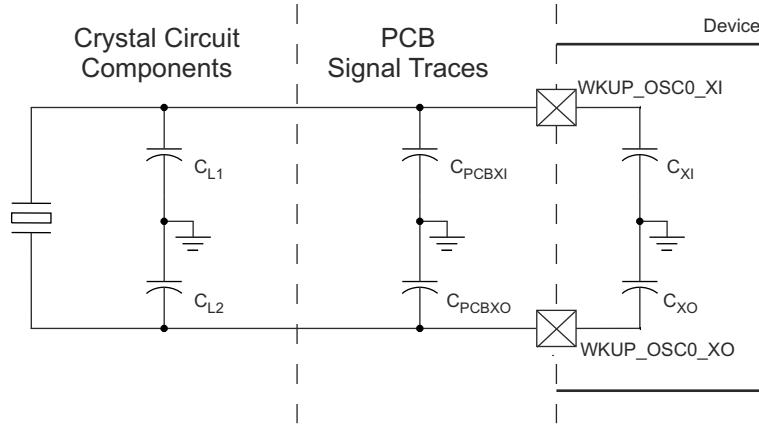

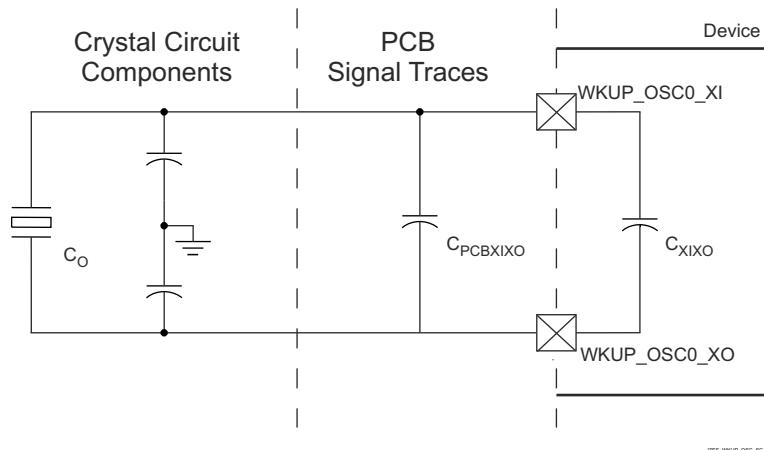

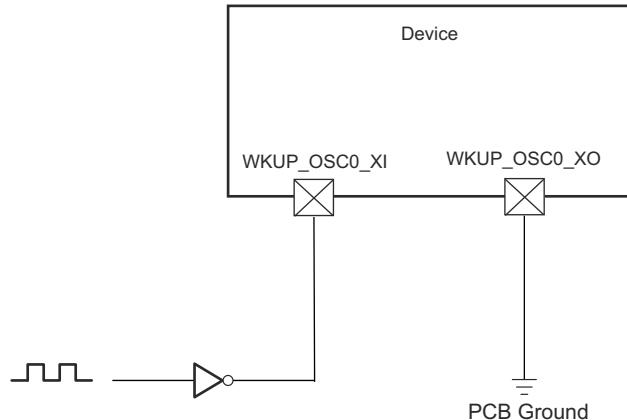

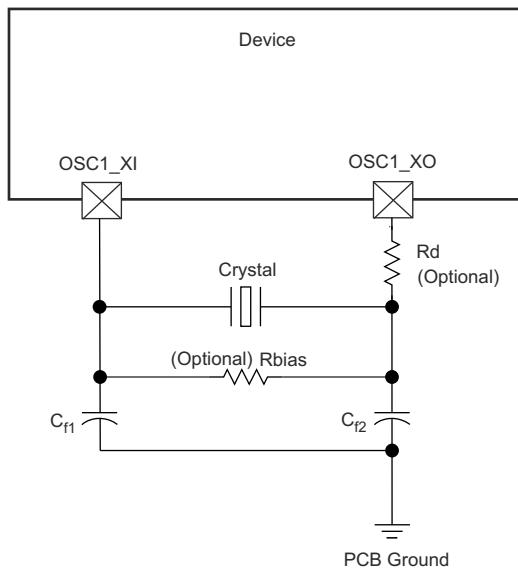

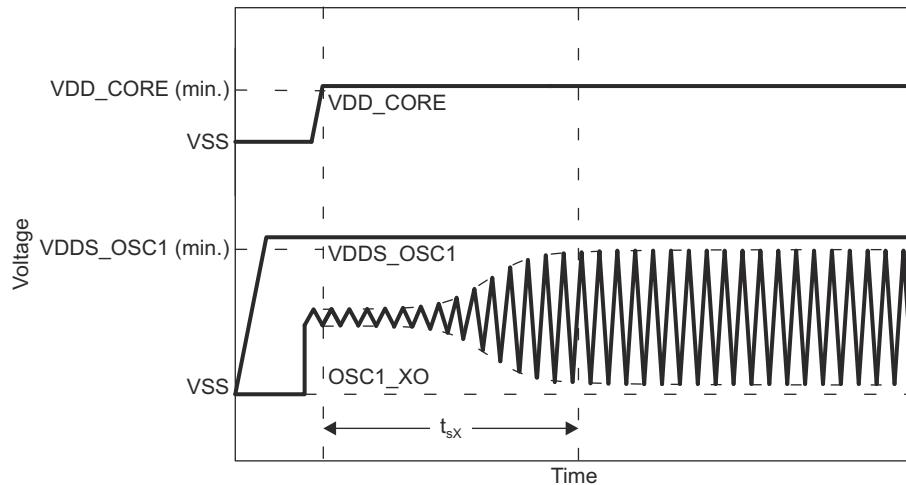

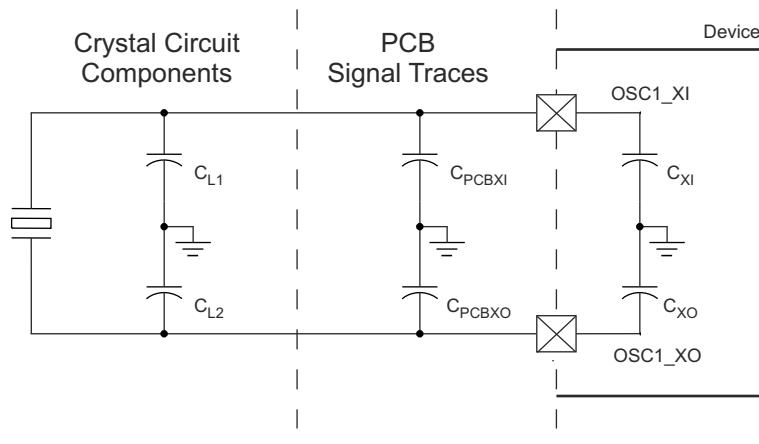

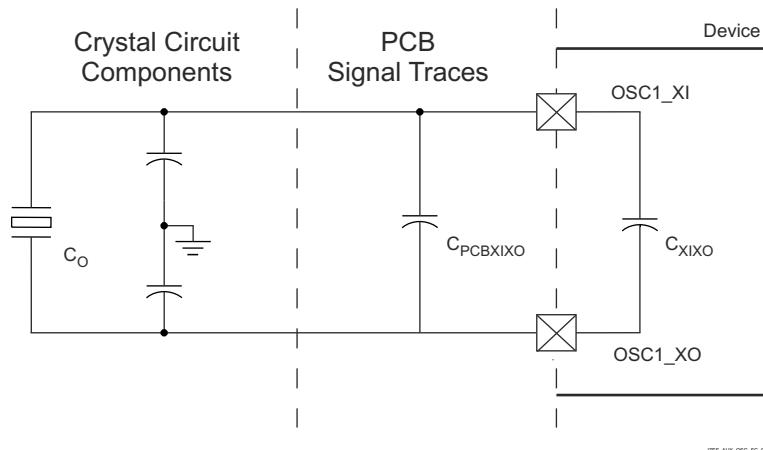

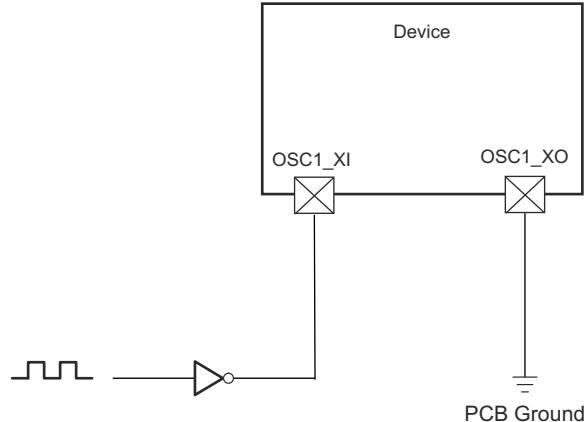

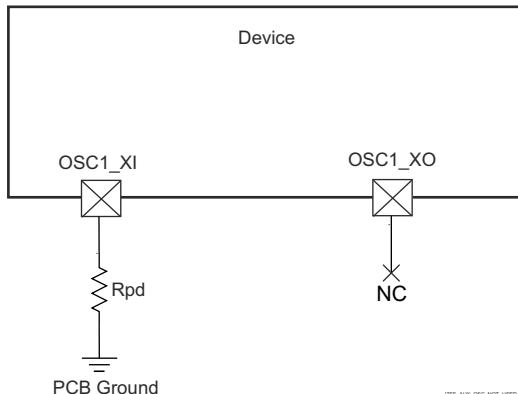

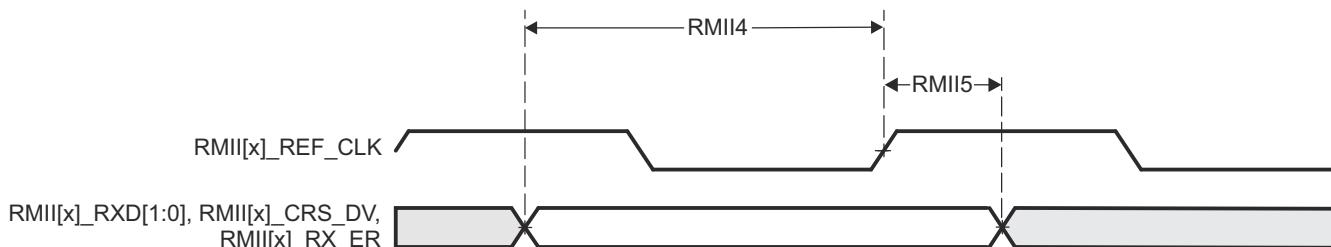

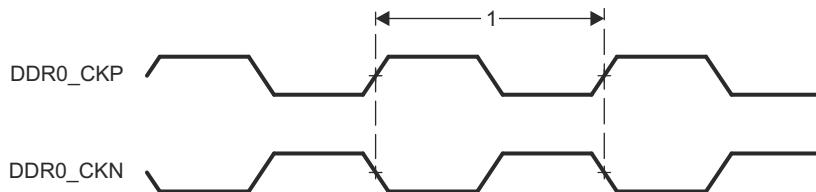

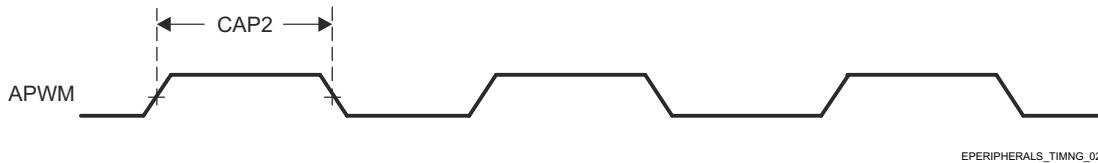

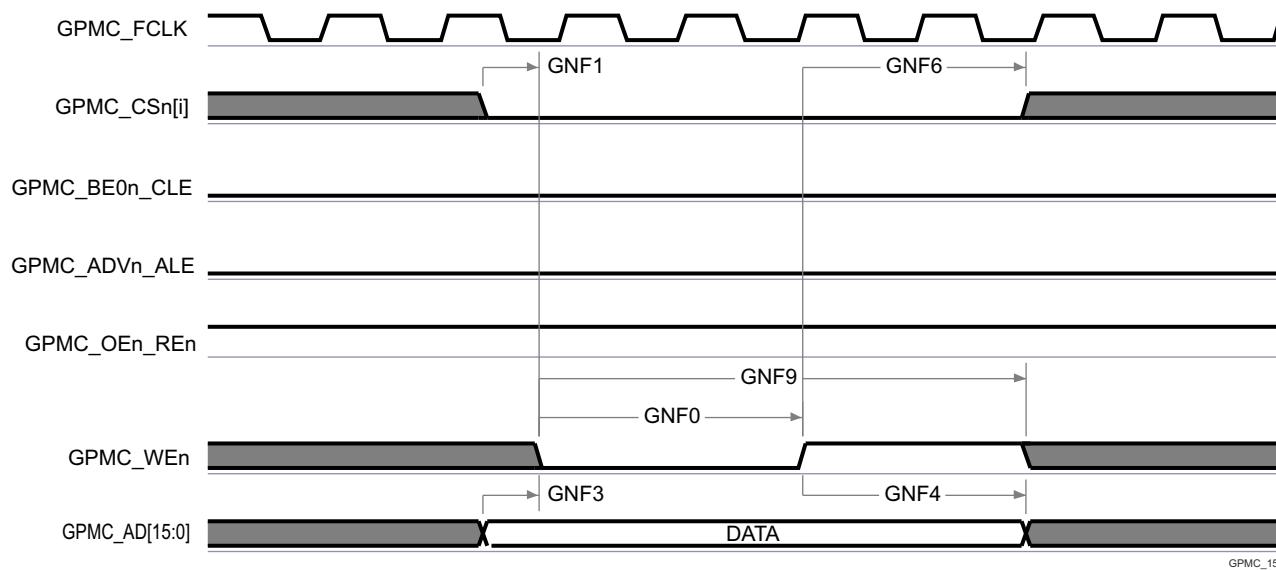

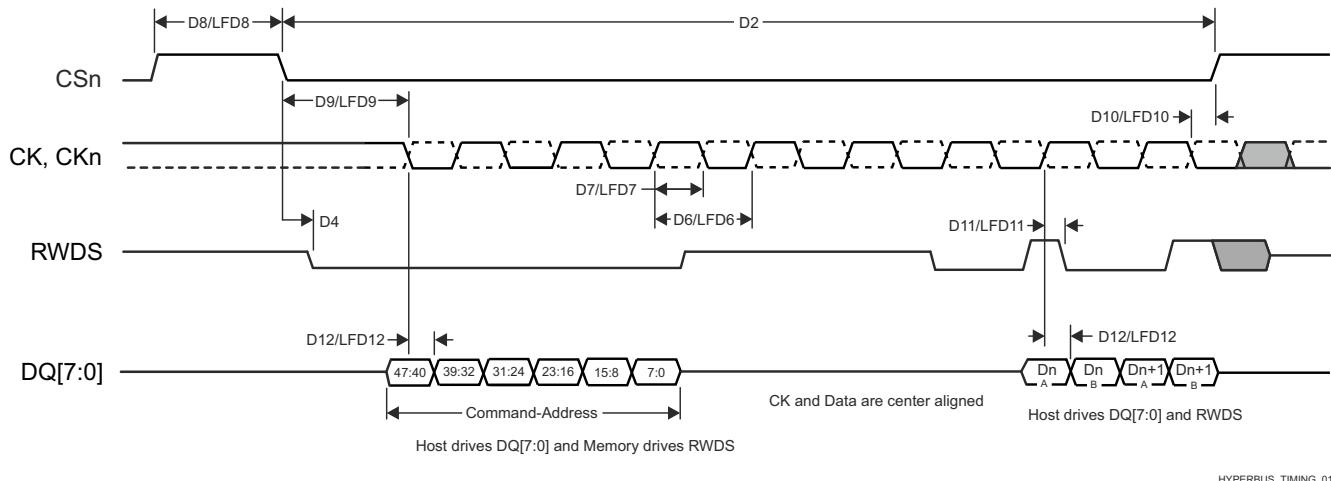

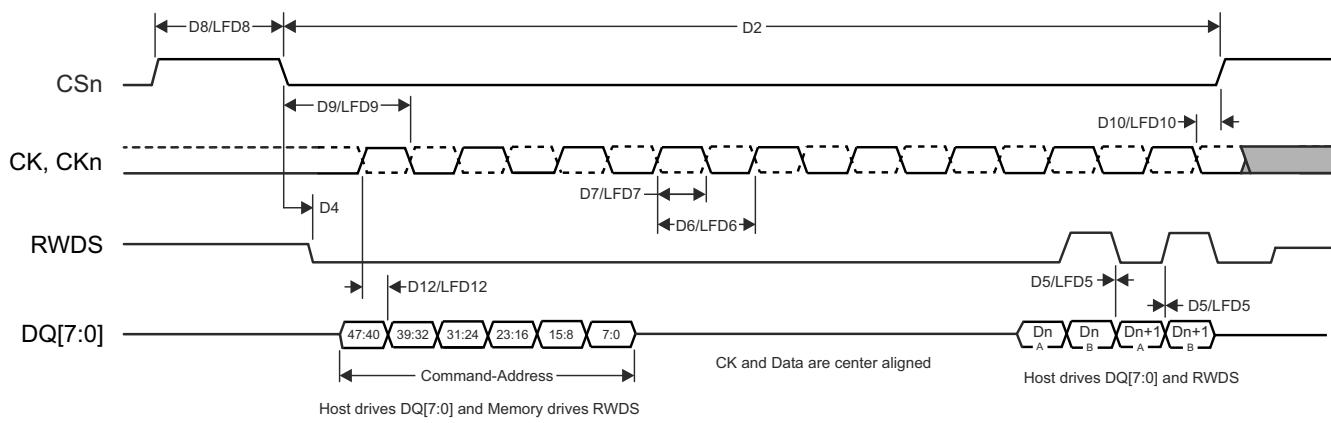

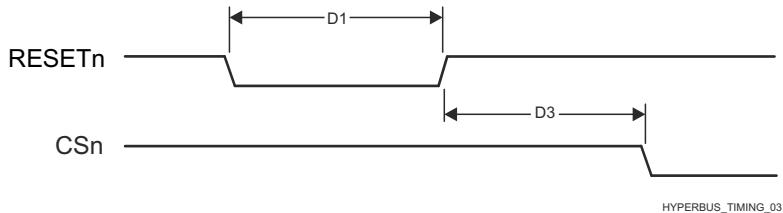

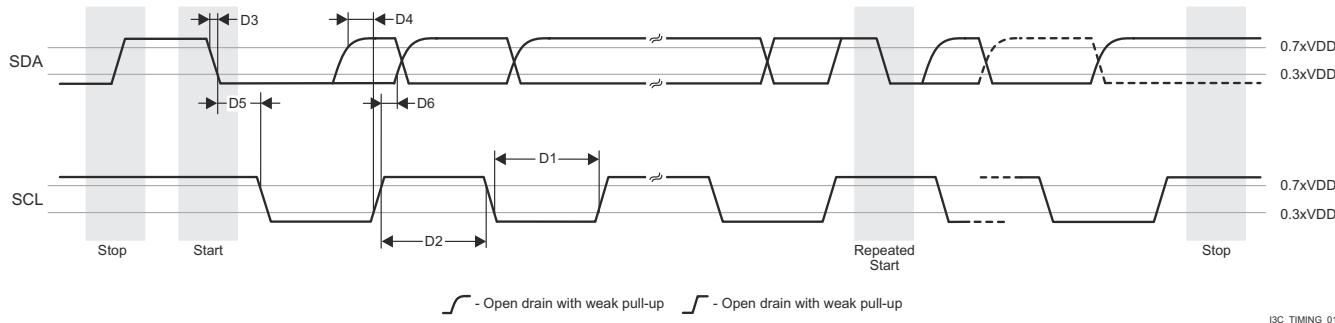

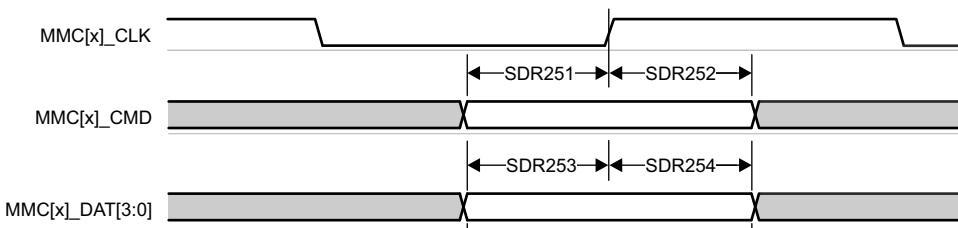

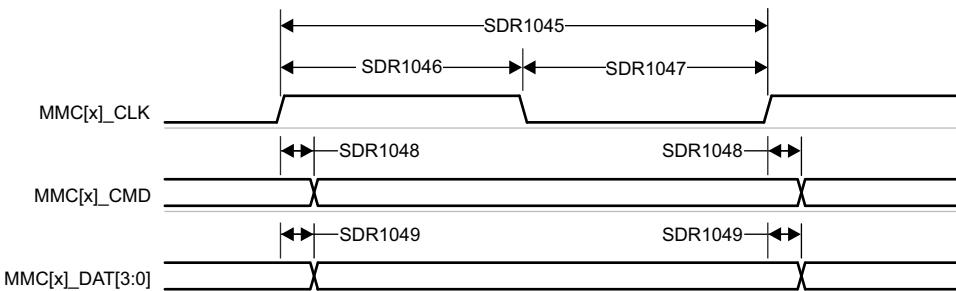

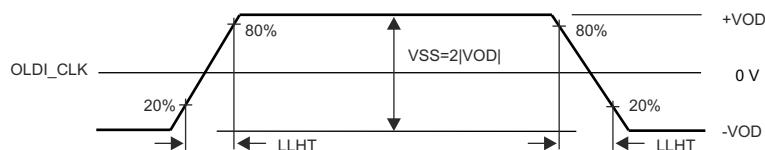

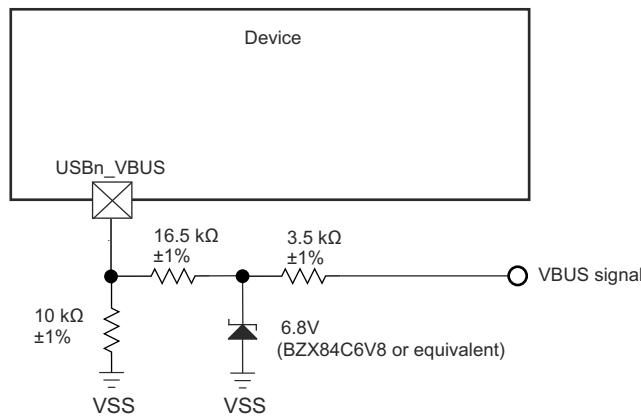

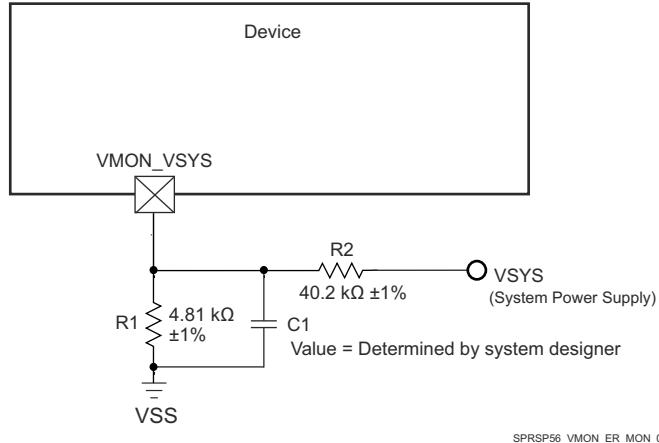

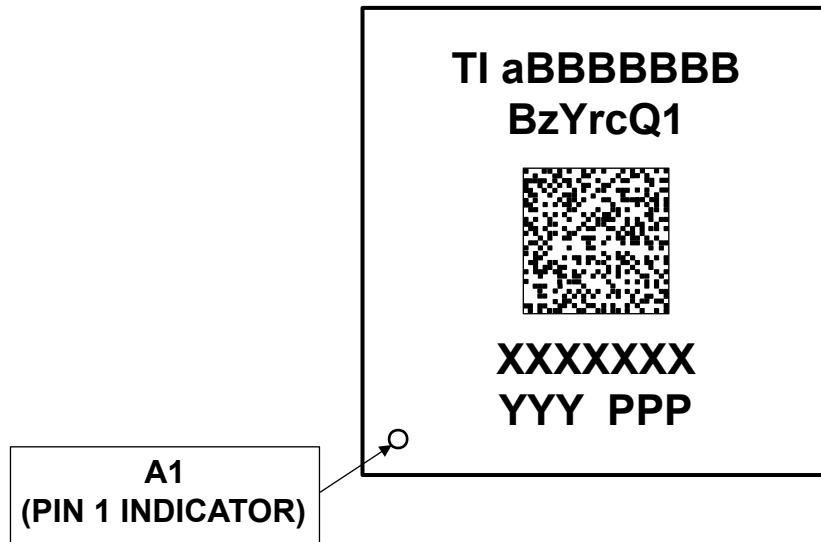

| D3           | DDR1_DQ14                                           | DDR1_DQ14   |                |                     | IO     |             |                                          |                                          |                              | 1.1V                 | VDDS_DDR/<br>VDDS_DDR_C1 |             | DDR            |                      |