## 20-W Stereo Digital Audio Power Amplifier With Feedback

Check for Samples: [TAS5704](#)

### FEATURES

- **Audio Input/Output**

- 20-W into an 8- $\Omega$  Load From an 18-V Supply

- Two Serial Audio Inputs (Four Audio Channels)

- Supports Multiple Output Configurations:

- 2-Ch Bridged Outputs (20 W  $\times$  2)

- 4-Ch Single-Ended Outputs (10 W  $\times$  4)

- 2-Ch Single-Ended + 1-Ch Bridged (2.1) (10 W  $\times$  2 + 20 W)

- **Closed Loop Power Stage Architecture**

- Improved PSRR Reduces Power Supply Performance Requirements

- Higher Damping Factor Provides for Tighter, More Accurate Sound With Improved Bass Response

- Lower EMC Emissions

- Output Power is Independent of Supply Voltage Variation

- **Wide PVCC Range From (10 V to 26 V)**

- **Supports 32-kHz–192-kHz (DVD-Audio) Sample Rates (LJ/RJ/I<sup>2</sup>S)**

- **Line-Level Subwoofer PWM Outputs**

- **Audio/PWM Processing (Hardware Controlled)**

- 4-Step Gain Control (-3dB, 3dB, 9dB, 12dB)

- Soft Mute Control (50% Output Duty Cycle)

- **Factory-Trimmed Internal Oscillator Enables Automatic Detection of Incoming Sample Rates**

- Thermal and Short-Circuit Protection

### DESCRIPTION

The TAS5704 is a 20-W, efficient, digital audio power amplifier for driving stereo bridge-tied speakers. Two serial data inputs allow processing of up to four discrete audio channels and seamless integration to most digital audio processors accepting a wide range of input data and clock rates. A hardware configurable data path allows these channels to be routed to the internal speaker drivers or output via the subwoofer PWM outputs.

The TAS5704 is a slave-only device receiving all clocks from external sources. The TAS5704 operates at a 384-kHz switching rate for 32-, 48-, 96-, and 192-kHz data, and at a 352.8 kHz switching rate for 44.1-, 88.2-, and 176.4-kHz data. The 8x oversampling combined with the fourth-order noise shaper provides a flat noise floor and excellent dynamic range from 20 Hz to 20 kHz.

The closed-loop architecture of the TAS5704 provides several benefits. The high power supply rejection enables superior audio performance from a noisy, low cost supply. The high damping factor allows tighter control over speaker movement resulting in an improved bass response. Finally, switching edge rate control lowers EMC emissions without sacrificing audio performance.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

System Two, Audio Precision are trademarks of Audio Precision, Inc.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

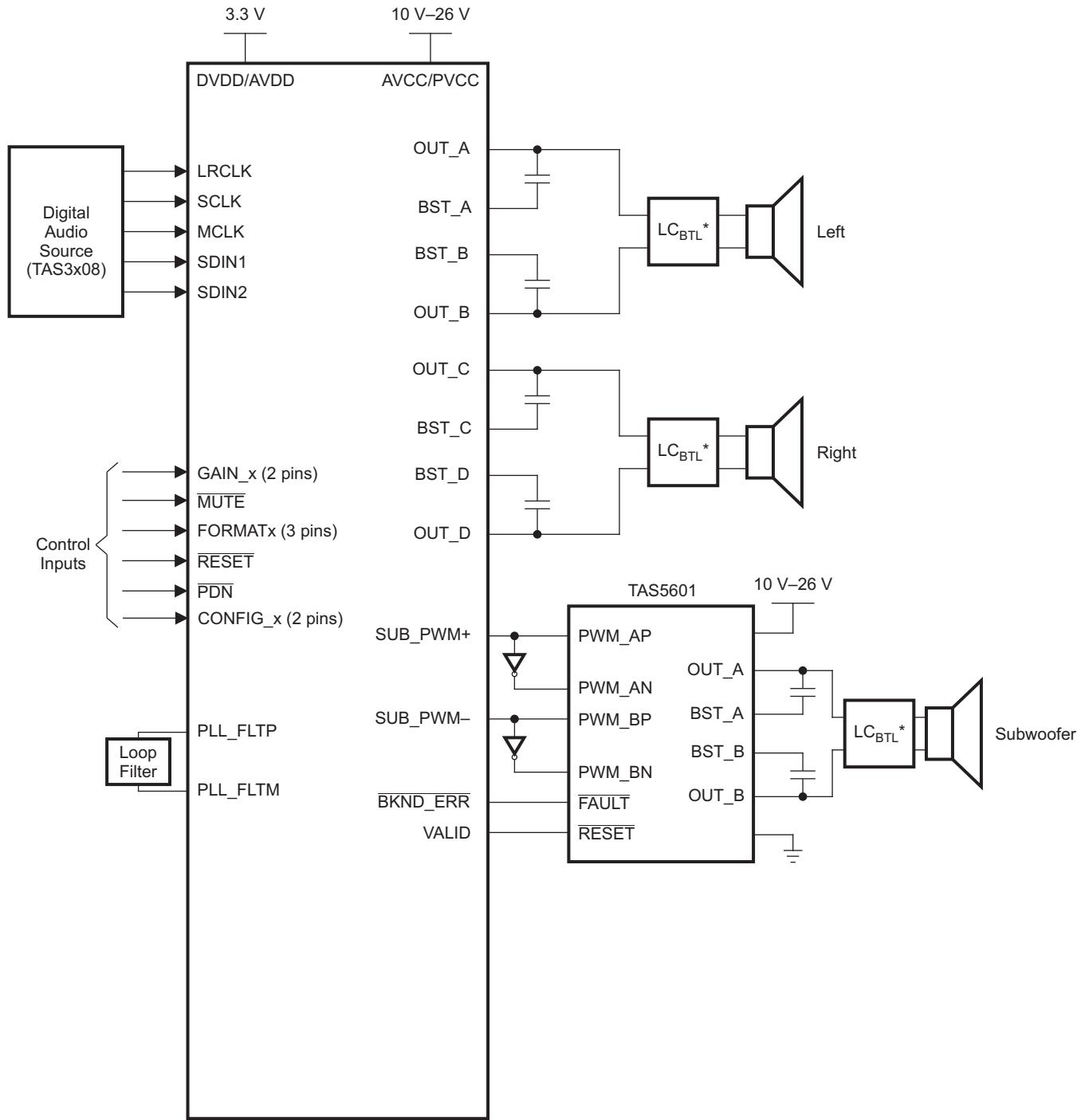

## SIMPLIFIED APPLICATION DIAGRAMS

### Bridge-Tied Load (BTL) Mode

\* Refer to TI Application Note (SLOA119) on LC filter design for BTL (AD/BD mode) configuration.

B0264-02

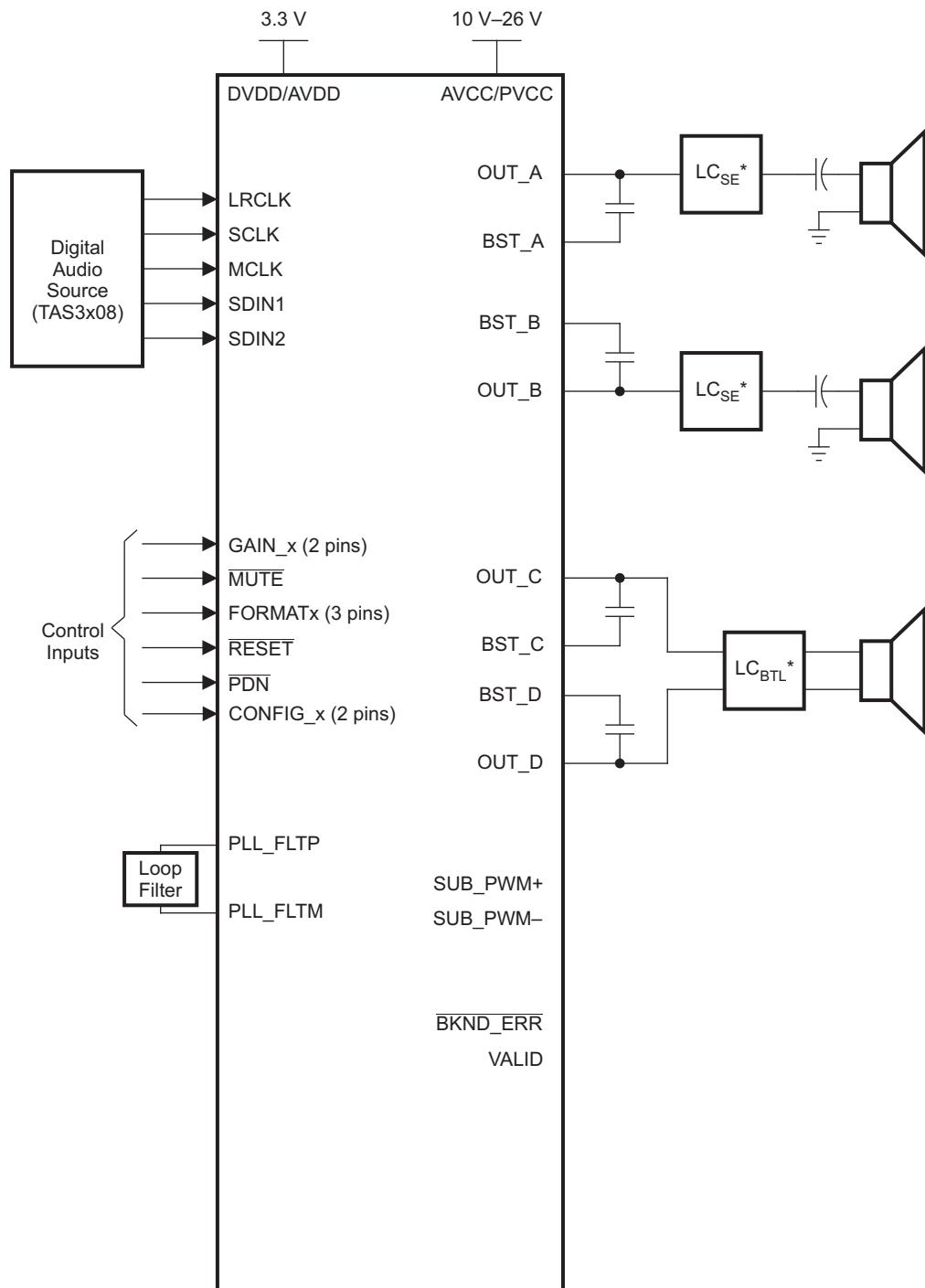

**Single-Ended (SE) 2.1 Mode**

\* Refer to TI Application Note (SLOA119) on LC filter design for SE or BTL configuration.

B0264-05

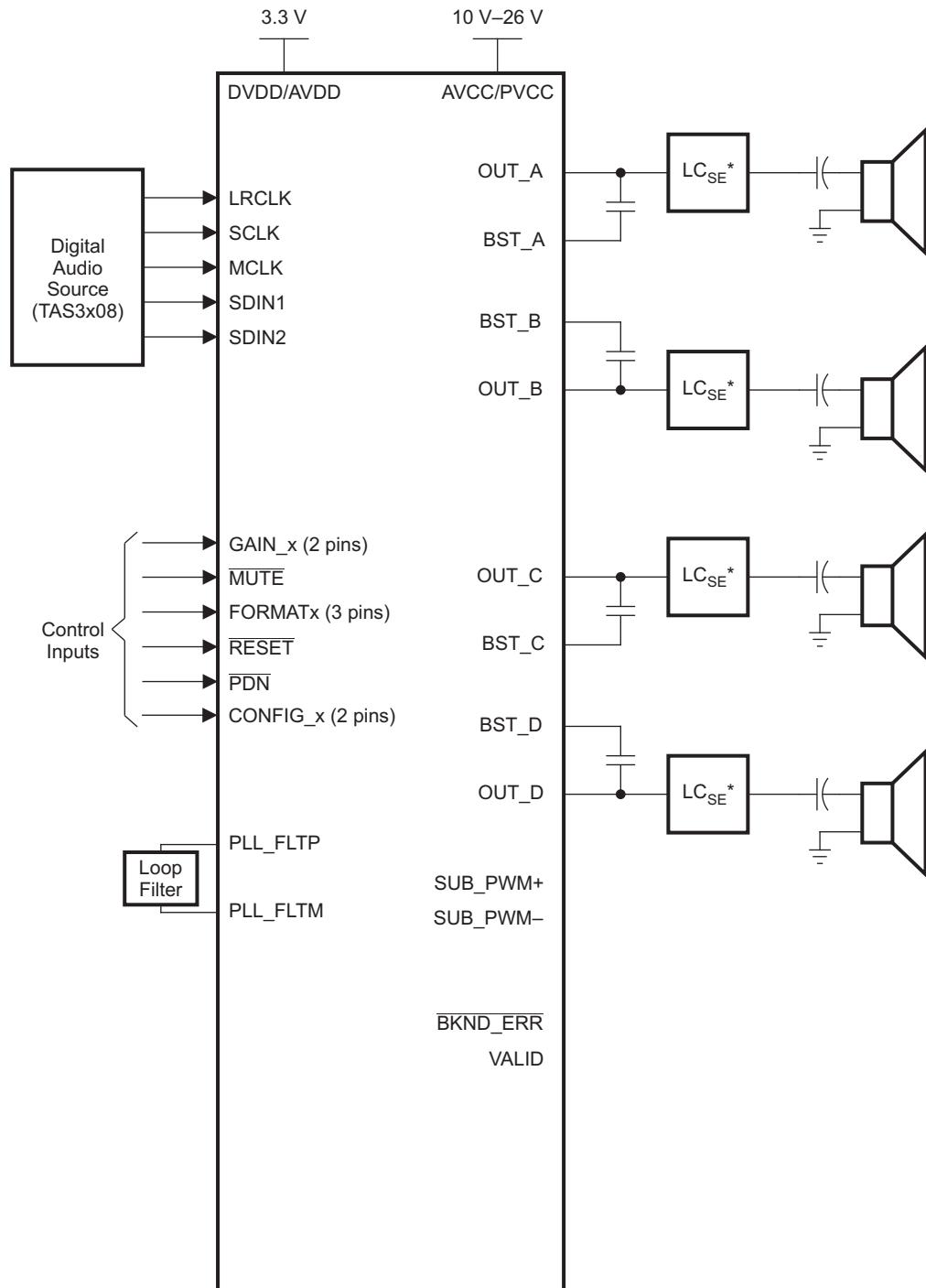

### Single-Ended (SE) 4.0 Mode

\* Refer to TI Application Note (SLOA119) on LC filter design for SE configuration.

B0264-04

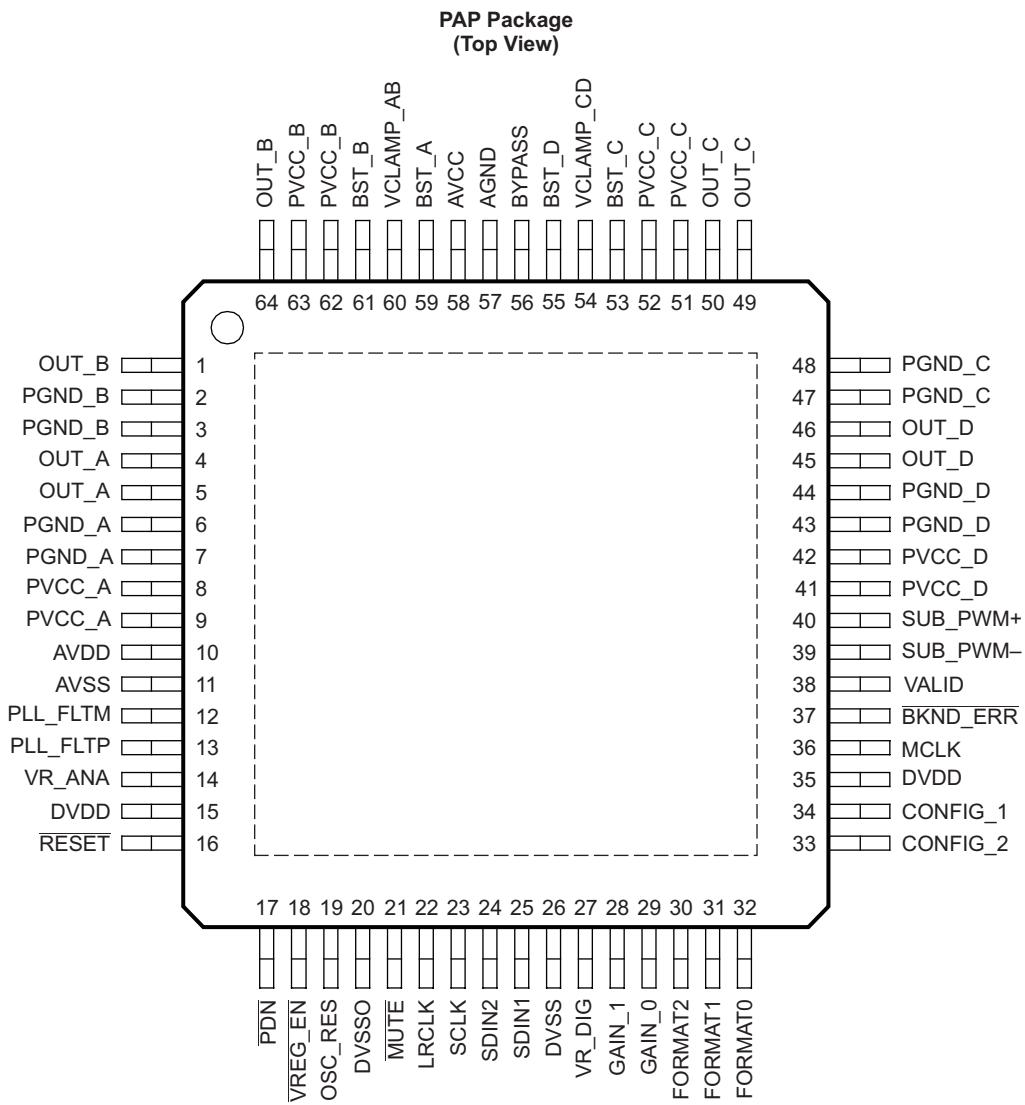

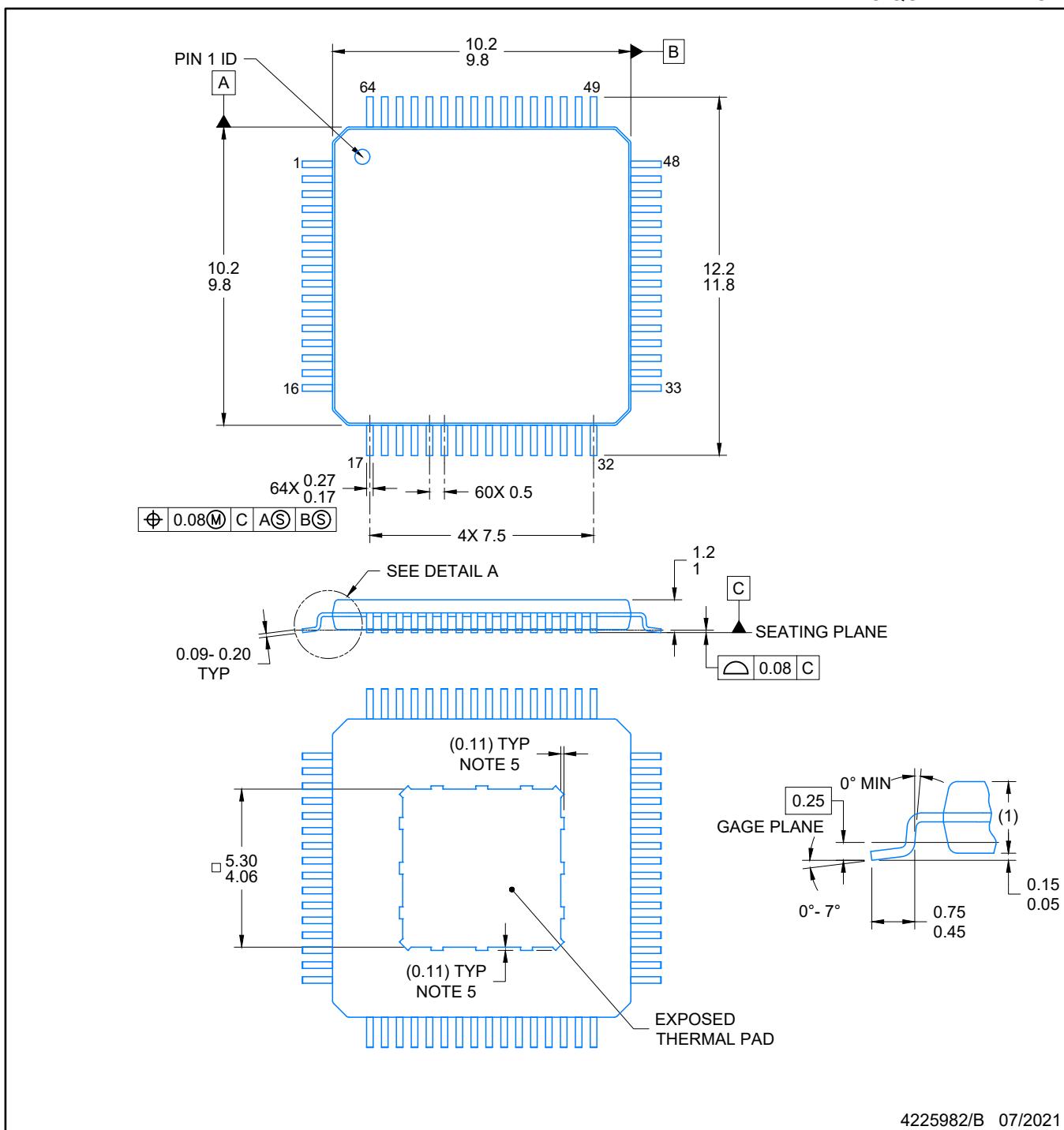

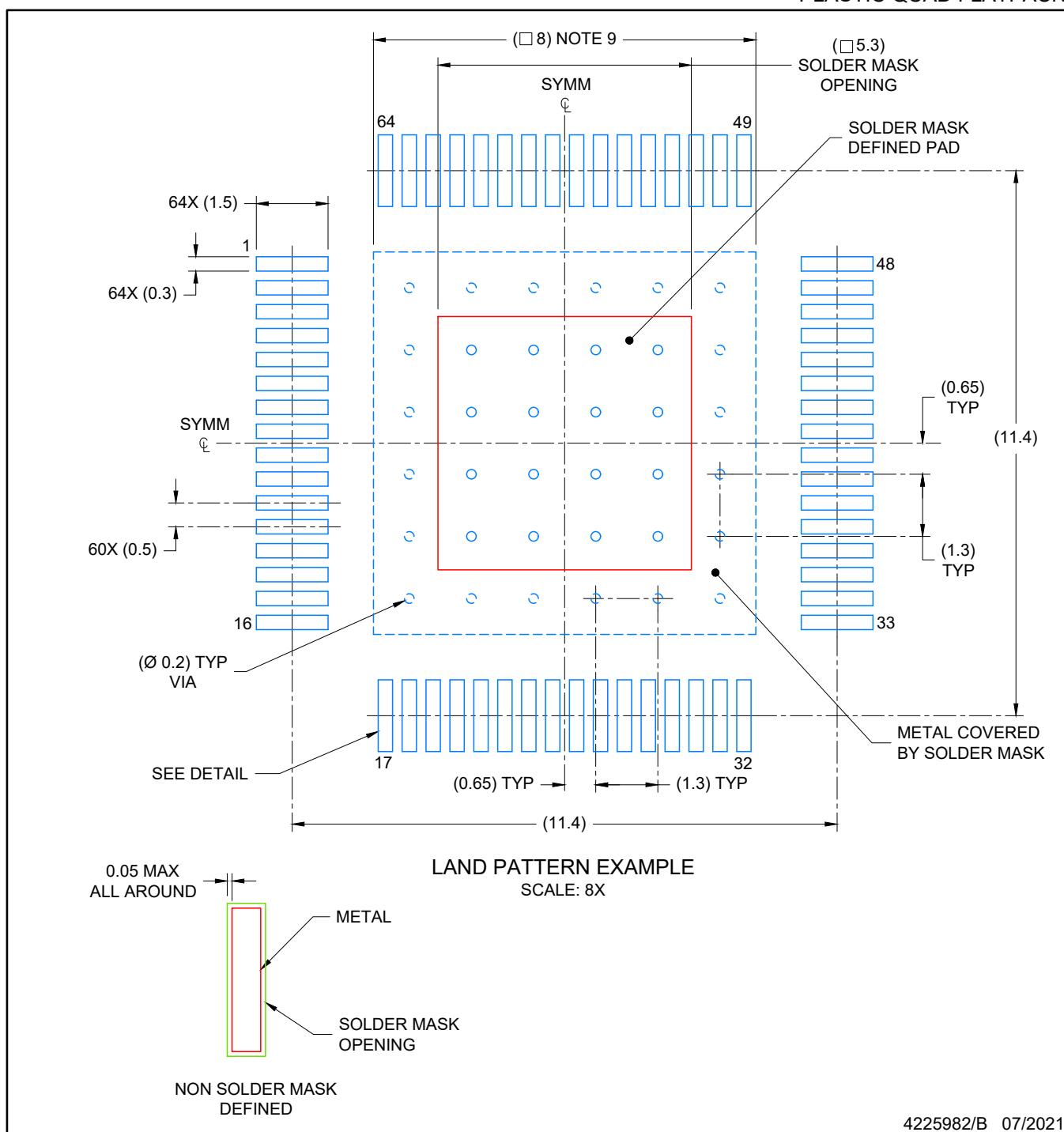

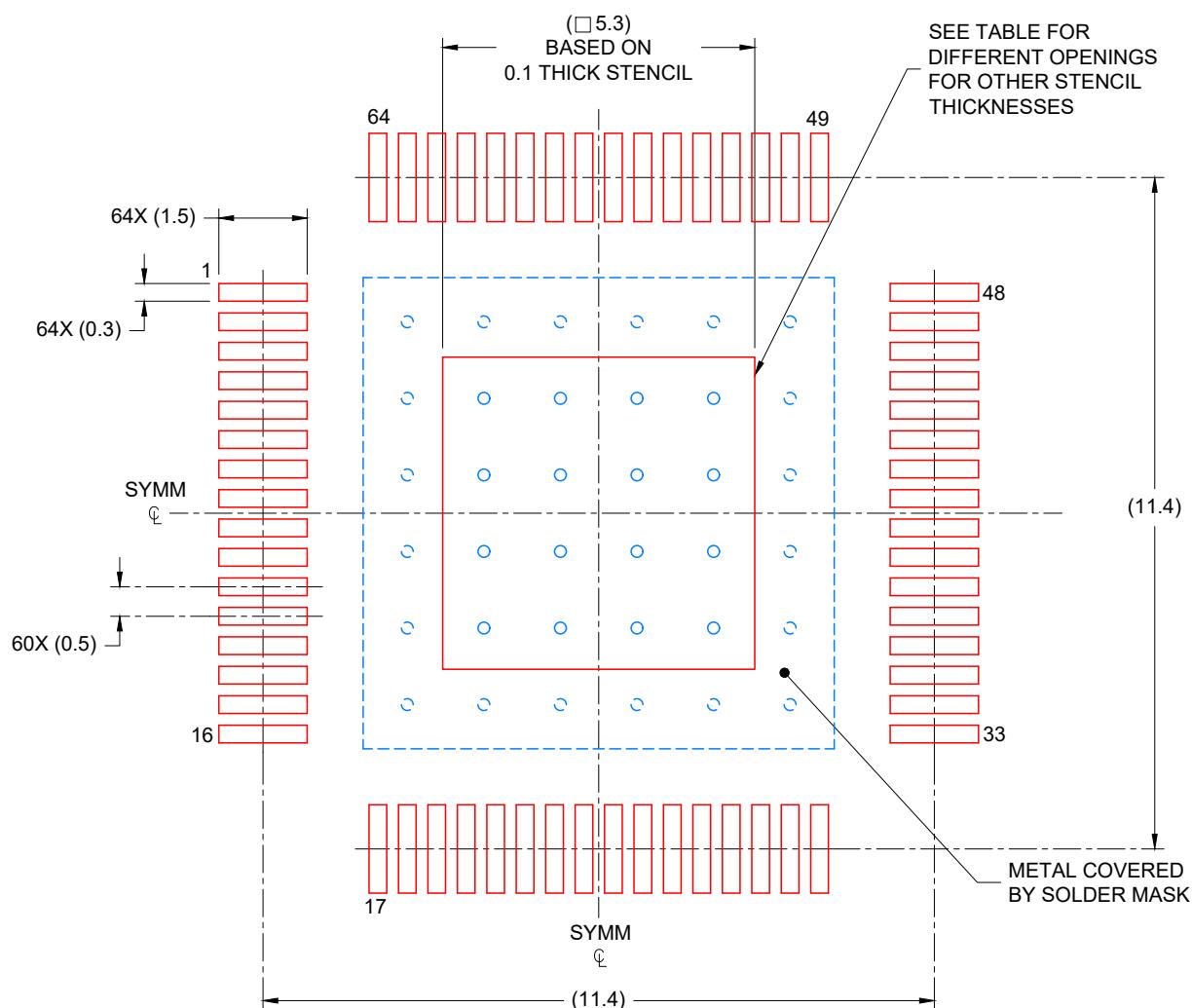

## 64-PIN, HTQFP PACKAGE

P0071-02

## PIN FUNCTIONS

| PIN      |     | TYPE<br>(1) | 5-V<br>TOLERANT | TERMINATION<br>(2) | DESCRIPTION                                                                                                                                                                               |

|----------|-----|-------------|-----------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. |             |                 |                    |                                                                                                                                                                                           |

| AGND     | 57  | P           |                 |                    | Analog ground for power stage                                                                                                                                                             |

| AVCC     | 58  | P           |                 |                    | Analog power supply for power stage. Connect externally to same potential as PVCC.                                                                                                        |

| AVDD     | 10  | P           |                 |                    | 3.3-V analog power supply                                                                                                                                                                 |

| AVSS     | 11  | P           |                 |                    | 3.3-V analog supply ground                                                                                                                                                                |

| BKND_ERR | 37  | DI          |                 | Pullup             | Active low. A back-end error sequence is initiated by applying a logic low to this pin. Connect to an external power stage. If no external power stage is used, connect directly to DVDD. |

| BST_A    | 59  | P           |                 |                    | High-side bootstrap supply for half-bridge A                                                                                                                                              |

(1) TYPE: A = analog; D = 3.3-V digital; P = power/ground/decoupling; I = input; O = output

(2) All pullups are 20- $\mu$ A weak pullups and all pulldowns are 20- $\mu$ A weak pulldowns. The pullups and pulldowns are included to assure proper input logic levels if the terminals are left unconnected (pullups  $\rightarrow$  logic 1 input; pulldowns  $\rightarrow$  logic 0 input). Devices that drive inputs with pullups must be able to sink 50  $\mu$ A while maintaining a logic-0 drive level. Devices that drive inputs with pulldowns must be able to source 50  $\mu$ A while maintaining a logic-1 drive level.

## PIN FUNCTIONS (continued)

| PIN      |           | TYPE<br>(1) | 5-V<br>TOLERANT | TERMINATION<br>(2) | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |

|----------|-----------|-------------|-----------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.       |             |                 |                    |                                                                                                                                                                                                                                                                                                                                          |

| BST_B    | 61        | P           |                 |                    | High-side bootstrap supply for half-bridge B                                                                                                                                                                                                                                                                                             |

| BST_C    | 53        | P           |                 |                    | High-side bootstrap supply for half-bridge C                                                                                                                                                                                                                                                                                             |

| BST_D    | 55        | P           |                 |                    | High-side bootstrap supply for half-bridge D                                                                                                                                                                                                                                                                                             |

| BYPASS   | 56        | O           |                 |                    | Nominally equal to $V_{CC}/8$ . Internal reference voltage for analog cells                                                                                                                                                                                                                                                              |

| CONFIG_1 | 34        | P           |                 | Pulldown           | Input/output configuration.                                                                                                                                                                                                                                                                                                              |

| CONFIG_2 | 33        | P           |                 | Pulldown           | Input/output configuration.                                                                                                                                                                                                                                                                                                              |

| DVDD     | 15,<br>35 | P           |                 |                    | 3.3-V digital power supply                                                                                                                                                                                                                                                                                                               |

| DVSS     | 26        | P           |                 |                    | Digital ground                                                                                                                                                                                                                                                                                                                           |

| DVSSO    | 20        | P           |                 |                    | Oscillator ground                                                                                                                                                                                                                                                                                                                        |

| FORMAT0  | 32        | DI          |                 | Pulldown           | Digital data format select.                                                                                                                                                                                                                                                                                                              |

| FORMAT1  | 31        | DI          |                 | Pulldown           | Digital data format select.                                                                                                                                                                                                                                                                                                              |

| FORMAT2  | 30        | DI          |                 |                    | Digital data format select.                                                                                                                                                                                                                                                                                                              |

| GAIN_0   | 29        | DI          |                 |                    | LSB of gain select. GAIN_0 and GAIN_1 allow 4 possible gain selections.                                                                                                                                                                                                                                                                  |

| GAIN_1   | 28        | DI          |                 |                    | MSB of gain select. GAIN_0 and GAIN_1 allow 4 possible gain selections.                                                                                                                                                                                                                                                                  |

| LRCLK    | 22        | DI          | 5-V             |                    | Input serial audio data left/right clock (sampling rate clock)                                                                                                                                                                                                                                                                           |

| MCLK     | 36        | DI          | 5-V             |                    | Master clock input. The input frequency of this clock can range from 4.9 MHz to 49.2 MHz.                                                                                                                                                                                                                                                |

| MUTE     | 21        | DI          | 5-V             | Pullup             | Performs a soft mute of outputs, active-low. A logic low on this terminal sets the outputs equal to 50% duty cycle. A logic high on this terminal allows normal operation. The mute control provides a noiseless volume ramp to silence. Releasing mute provides a noiseless ramp to previous volume.                                    |

| OSC_RES  | 19        | AO          |                 |                    | Oscillator trim resistor. Connect an 18.2-k $\Omega$ resistor to DVSSO.                                                                                                                                                                                                                                                                  |

| OUT_A    | 4, 5      | O           |                 |                    | Output, half-bridge A                                                                                                                                                                                                                                                                                                                    |

| OUT_B    | 1, 64     | O           |                 |                    | Output, half-bridge B                                                                                                                                                                                                                                                                                                                    |

| OUT_C    | 49,<br>50 | O           |                 |                    | Output, half-bridge C                                                                                                                                                                                                                                                                                                                    |

| OUT_D    | 45,<br>46 | O           |                 |                    | Output, half-bridge D                                                                                                                                                                                                                                                                                                                    |

| PDN      | 17        | DI          | 5-V             | Pullup             | Power down, active-low. $\overline{PDN}$ stops all clocks and outputs stop switching. When $\overline{PDN}$ is released, the device powers up all logic, starts all clocks, and performs a soft start that returns to the previous configuration. Changes to CONFIG_x, FORMATx, and GAIN_x pins are ignored on $\overline{PDN}$ cycling. |

| PGND_A   | 6, 7      | P           |                 |                    | Power ground for half-bridge A                                                                                                                                                                                                                                                                                                           |

| PGND_B   | 2, 3      | P           |                 |                    | Power ground for half-bridge B                                                                                                                                                                                                                                                                                                           |

| PGND_C   | 47,<br>48 | P           |                 |                    | Power ground for half-bridge C                                                                                                                                                                                                                                                                                                           |

| PGND_D   | 43,<br>44 | P           |                 |                    | Power ground for half-bridge D                                                                                                                                                                                                                                                                                                           |

| PLL_FLTM | 12        | AO          |                 |                    | PLL negative loop filter terminal                                                                                                                                                                                                                                                                                                        |

| PLL_FLTP | 13        | AO          |                 |                    | PLL positive loop filter terminal                                                                                                                                                                                                                                                                                                        |

| PVCC_A   | 8, 9      | P           |                 |                    | Power supply input for half-bridge output A                                                                                                                                                                                                                                                                                              |

| PVCC_B   | 62,<br>63 | P           |                 |                    | Power supply input for half-bridge output B                                                                                                                                                                                                                                                                                              |

| PVCC_C   | 51,<br>52 | P           |                 |                    | Power supply input for half-bridge output C                                                                                                                                                                                                                                                                                              |

| PVCC_D   | 41,<br>42 | P           |                 |                    | Power supply input for half-bridge output D                                                                                                                                                                                                                                                                                              |

**PIN FUNCTIONS (continued)**

| PIN       |     | TYPE<br>( <sup>1</sup> ) | 5-V<br>TOLERANT | TERMINATION<br>( <sup>2</sup> ) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-----|--------------------------|-----------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO. |                          |                 |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET     | 16  | DI                       | 5-V             | Pullup                          | Reset, active-low. A system reset is generated by applying a logic low to this terminal. RESET is an asynchronous control signal that sets the VALID outputs low, and places the PWM in the hard-mute state (stops switching). Gain is immediately set to full attenuation. Upon the release of RESET, if PDN is high, the system performs a 4- to 5-ms device initialization and sets the gain, output configuration, and format to the settings determined by the hardware pins. |

| SCLK      | 23  | DI                       | 5-V             |                                 | Serial audio data clock (shift clock). SCLK is the serial audio port input data bit clock.                                                                                                                                                                                                                                                                                                                                                                                         |

| SDIN1     | 25  | DI                       | 5-V             |                                 | Serial audio data-1 input is one of the serial data input ports. SDIN1 supports three discrete (stereo) data formats.                                                                                                                                                                                                                                                                                                                                                              |

| SDIN2     | 24  | DI                       | 5-V             |                                 | Serial audio data-2 input is one of the serial data input ports. SDIN2 supports three discrete (stereo) data formats.                                                                                                                                                                                                                                                                                                                                                              |

| SUB_PWM-  | 39  | DO                       |                 |                                 | Subwoofer negative PWM output                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SUB_PWM+  | 40  | DO                       |                 |                                 | Subwoofer positive PWM output                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VALID     | 38  | DO                       |                 |                                 | Output indicating validity of all PWM channels, active high. Connect this pin to an external power stage or leave floating.                                                                                                                                                                                                                                                                                                                                                        |

| VCLAMP_AB | 60  | P                        |                 |                                 | Internally generated voltage supply for channels A and B gate drive. Not to be used as a supply or connected to any component other than the decoupling capacitor                                                                                                                                                                                                                                                                                                                  |

| VCLAMP_CD | 54  | P                        |                 |                                 | Internally generated voltage supply for channels C and D gate drive. Not to be used as a supply or connected to any component other than the decoupling capacitor                                                                                                                                                                                                                                                                                                                  |

| VR_ANA    | 14  | P                        |                 |                                 | Internally regulated 1.8-V analog supply voltage. This terminal must not be used to power external devices.                                                                                                                                                                                                                                                                                                                                                                        |

| VR_DIG    | 27  | P                        |                 |                                 | Internally regulated 1.8-V digital supply voltage. This terminal must not be used to power external devices.                                                                                                                                                                                                                                                                                                                                                                       |

| VREG_EN   | 18  | DI                       |                 | Pulldown                        | Voltage regulator enable. Connect directly to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

**ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                                              |                                           | VALUE              | UNIT |

|--------------------------------------------------------------|-------------------------------------------|--------------------|------|

| Supply voltage                                               | DVDD, AVDD                                | -0.3 to 3.6        | V    |

|                                                              | PVCC_X                                    | -0.3 to 30         | V    |

| Input voltage                                                | 3.3-V digital input                       | -0.5 to DVDD + 0.5 | V    |

|                                                              | 5-V tolerant <sup>(2)</sup> digital input | -0.5 to 6          | V    |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > 1.8$ V)  |                                           | ±20                | mA   |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > 1.8$ V) |                                           | ±20                | mA   |

| Operating free-air temperature                               |                                           | 0 to 85            | °C   |

| Operating junction temperature range                         |                                           | 0 to 150           | °C   |

| Storage temperature range, $T_{stg}$                         |                                           | -40 to 125         | °C   |

(1) Stresses beyond those listed under *absolute ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *recommended operation conditions* are not implied. Exposure to absolute-maximum conditions for extended periods may affect device reliability.

(2) 5-V tolerant inputs are PDN, RESET, MUTE, SCLK, LRCLK, MCLK, SDIN1, and SDIN2.

## THERMAL INFORMATION

| THERMAL METRIC <sup>(1)(2)</sup> |                                              | TAS5704       | UNITS<br>°C/W |

|----------------------------------|----------------------------------------------|---------------|---------------|

|                                  |                                              | PAP (64 PINS) |               |

| $\theta_{JA}$                    | Junction-to-ambient thermal resistance       | 27            |               |

| $\theta_{JCTop}$                 | Junction-to-case (top) thermal resistance    | 15.6          |               |

| $\theta_{JB}$                    | Junction-to-board thermal resistance         | 12.6          |               |

| $\psi_{JT}$                      | Junction-to-top characterization parameter   | 0.2           |               |

| $\psi_{JB}$                      | Junction-to-board characterization parameter | 7.8           |               |

| $\theta_{JCbot}$                 | Junction-to-case (bottom) thermal resistance | 0.8           |               |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, [SPRA953](#).

(2) For thermal estimates of this device based on PCB copper area, see the [TI PCB Thermal Calculator](#).

## RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                               |                                      | MIN                                                         | NOM | MAX | UNIT          |

|-------------------------------|--------------------------------------|-------------------------------------------------------------|-----|-----|---------------|

| Digital/analog supply voltage | DVDD                                 | 3                                                           | 3.3 | 3.6 | V             |

| Half-bridge supply voltage    | PVCC_xx                              | 10                                                          | 26  |     | V             |

| $V_{IH}$                      | High-level input voltage             | 3.3-V TTL, 5-V tolerant                                     | 2   |     | V             |

| $V_{IL}$                      | Low-level input voltage              | 3.3-V TTL, 5-V tolerant                                     |     | 0.8 | V             |

| $T_A$                         | Operating ambient temperature range  |                                                             | 0   | 85  | °C            |

| $T_J$                         | Operating junction temperature range |                                                             | 0   | 150 | °C            |

| $R_L$ (BTL)                   | Load impedance                       | Output filter: $L = 22 \mu\text{H}$ , $C = 680 \text{nF}$ . | 6.0 | 8   | $\Omega$      |

| $R_L$ (SE)                    |                                      |                                                             | 3.2 | 4   |               |

| $R_L$ (PBTL)                  |                                      |                                                             | 3.2 | 4   |               |

| $L_O$ (BTL)                   | Output-filter inductance             | Minimum output inductance under short-circuit condition     |     | 10  | $\mu\text{H}$ |

| $L_O$ (SE)                    |                                      |                                                             |     | 10  |               |

| $L_O$ (PBTL)                  |                                      |                                                             |     | 10  |               |

## PWM OPERATION AT RECOMMENDED OPERATING CONDITIONS

| PARAMETER                            | TEST CONDITIONS                             | MODE                        | VALUE | UNITS |

|--------------------------------------|---------------------------------------------|-----------------------------|-------|-------|

| Output sample rate 2x–1x oversampled | 32-kHz data rate $\pm 2\%$                  | 12x sample rate             | 384   | kHz   |

|                                      | 44.1-, 88.2-, 176.4-kHz data rate $\pm 2\%$ | 8x, 4x, and 2x sample rates | 352.8 | kHz   |

|                                      | 48-, 96-, 192-kHz data rate $\pm 2\%$       | 8x, 4x, and 2x sample rates | 384   | kHz   |

## PLL INPUT PARAMETERS AND EXTERNAL FILTER COMPONENTS

| PARAMETER                                     | TEST CONDITIONS                                                                               | MIN | TYP | MAX  | UNIT     |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------|-----|-----|------|----------|

| $f_{MCLKI}$ Frequency, MCLK (1 / $t_{cyc2}$ ) |                                                                                               | 4.9 |     | 49.2 | MHz      |

| MCLK duty cycle                               |                                                                                               | 40% | 50% | 60%  |          |

| MCLK minimum high time                        | $\geq 2\text{-V MCLK} = 49.152 \text{ MHz}$ , within the min and max duty cycle constraints   | 8   |     |      | ns       |

| MCLK minimum low time                         | $\leq 0.8\text{-V MCLK} = 49.152 \text{ MHz}$ , within the min and max duty cycle constraints | 8   |     |      | ns       |

| LRCLK allowable drift before LRCLK reset      |                                                                                               |     |     | 4    | MCLKs    |

| External PLL filter capacitor C1              | SMD 0603 Y5V                                                                                  |     | 47  |      | nF       |

| External PLL filter capacitor C2              | SMD 0603 Y5V                                                                                  |     | 4.7 |      | nF       |

| External PLL filter resistor R                | SMD 0603, metal film                                                                          |     | 470 |      | $\Omega$ |

## ELECTRICAL CHARACTERISTICS

DC Characteristics,  $T_A = 25^\circ\text{C}$ ,  $\text{PVCC\_X}$ ,  $\text{AVCC} = 18\text{ V}$ ,  $\text{DVDD} = \text{AVDD} = 3.3\text{ V}$ ,  $R_L = 8\text{ }\Omega$  (unless otherwise noted)

| PARAMETER              |                                                       | TEST CONDITIONS                                                                                                                                       | MIN                                                 | TYP      | MAX           | UNIT             |

|------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------|---------------|------------------|

| $V_{OH}$               | High-level output voltage                             | $3.3\text{-V TTL}$ and $5\text{-V tolerant}$ <sup>(1)</sup>                                                                                           | $I_{OH} = -4\text{ mA}$                             | 2.4      |               | V                |

| $V_{OL}$               | Low-level output voltage                              | $3.3\text{-V TTL}$ and $5\text{-V tolerant}$ <sup>(1)</sup>                                                                                           | $I_{OL} = 4\text{ mA}$                              |          | 0.5           | V                |

| $ V_{OS} $             | Class-D output offset voltage                         |                                                                                                                                                       |                                                     | $\pm 26$ |               | mV               |

| $V_{BYPASS}$           | PVCC/8 reference for analog section                   | No load                                                                                                                                               | 2.2                                                 | 2.26     | 2.3           | V                |

| $I_{IL}$               | Low-level input current                               | $\text{LRCLK}$ , $\text{SCLK}$ , $\text{SDIN}_x$ , $\text{MCLK}$ ,<br>$\text{GAIN}_x$<br>$\text{VREG\_EN}$ , $\text{FORMAT}_x$ ,<br>$\text{CONFIG}_x$ | $V_I = 0\text{ V}$ , $\text{DVDD} = 3.6\text{ V}$   |          | $\pm 2$       | $\mu\text{A}$    |

|                        |                                                       | $\text{BKND\_ERR}$ , $\text{RESET}$ , $\text{PDN}$ ,<br>$\text{MUTE}$                                                                                 | $V_I = 0\text{ V}$ , $\text{DVDD} = 3.6\text{ V}$   |          | $\pm 50$      |                  |

| $I_{IH}$               | High-level input current                              | $\text{RESET}$ , $\text{PDN}$ , $\text{MUTE}$ , $\text{GAIN}_x$ ,<br>$\text{BKND\_ERR}$                                                               | $V_I = 3.6\text{ V}$ , $\text{DVDD} = 3.6\text{ V}$ |          | $\pm 2$       | $\mu\text{A}$    |

|                        |                                                       | $\text{VREG\_EN}$ , $\text{FORMAT}_x$ ,<br>$\text{CONFIG}_x$ , $\text{LRCLK}$ , $\text{SCLK}$ ,<br>$\text{SDIN}_x$ , $\text{MCLK}$                    | $V_I = 3.6\text{ V}$ , $\text{DVDD} = 3.6\text{ V}$ |          | $\pm 50$      |                  |

|                        |                                                       | $\text{RESET}$ , $\text{PDN}$ , $\text{MUTE}$ , $\text{LRCLK}$ ,<br>$\text{SCLK}$ , $\text{SDIN}_x$ , $\text{MCLK}$ , $\text{GAIN}_x$                 | $V_I = 5.5\text{ V}$ , $\text{DVDD} = 3.6\text{ V}$ |          | $\pm 50$      |                  |

| $I_{DD}$               | Digital supply current                                | Supply voltage (DVDD, AVDD)                                                                                                                           | Normal mode                                         | 65       | 80            | $\text{mA}$      |

|                        |                                                       |                                                                                                                                                       | Power down<br>( $\text{PDNZ} = \text{LOW}$ )        | 8        | 16            |                  |

|                        |                                                       |                                                                                                                                                       | Reset ( $\text{RESET} = \text{LOW}$ )               | 23       | 33            |                  |

| $I_{CC}$               | Quiescent supply current                              | No load                                                                                                                                               | 14                                                  | 33       | 57            | mA               |

| $I_{CC(\text{RESET})}$ | Quiescent supply current in reset mode                | No load                                                                                                                                               | 58                                                  | 176      | $\mu\text{A}$ |                  |

| $I_{CC(\text{PDNZ})}$  | Quiescent supply current in power down mode           | No load                                                                                                                                               | 58                                                  | 176      | $\mu\text{A}$ |                  |

| PSRR                   | DC power-supply rejection ratio                       | $\text{PVCC} = 17.5\text{ V to }18.5\text{ V}$                                                                                                        | 60                                                  |          |               | dB               |

| $R_{DS(on)}$           | Drain-source on-state resistance, high-side           | $V_{CC} = 18\text{ V}$ , $I_O = 500\text{ mA}$ ,<br>$T_J = 25^\circ\text{C}$                                                                          | 240                                                 |          |               | $\text{m}\Omega$ |

|                        | Low-side                                              |                                                                                                                                                       | 240                                                 |          |               |                  |

|                        | Total                                                 |                                                                                                                                                       | 480                                                 | 850      |               |                  |

| $t_{ON}$               | Turnon time (SE mode) (CONFIG_2 = 0)                  | $C_{(\text{BYPASS})} = 1\text{ }\mu\text{F}$ ,<br>Time required for the<br>BYPASS pin to reach its<br>final value                                     | 500                                                 |          |               | ms               |

|                        | Turnon time (BTL mode) (CONFIG_2 = 1)                 |                                                                                                                                                       | 30                                                  |          |               |                  |

| $t_{OFF}$              | Turnoff time (SE mode) (CONFIG_2 = 0) <sup>(2)</sup>  |                                                                                                                                                       | 500                                                 |          |               | ms               |

|                        | Turnoff time (BTL mode) (CONFIG_2 = 0) <sup>(2)</sup> |                                                                                                                                                       | 30                                                  |          |               |                  |

(1) 5-V tolerant pins are  $\text{PDN}$ ,  $\text{RESET}$ ,  $\text{MUTE}$ ,  $\text{SCLK}$ ,  $\text{LRCLK}$ ,  $\text{MCLK}$ ,  $\text{SDIN}_1$ , and  $\text{SDIN}_2$ .

(2) For *pop-free* power-off ( $\text{PVDD} = 0\text{ V}$ ), it is recommended that  $\text{PDN}$  be cycled low for at least this period of time before  $\text{PVDD}$  drops below 10 V and  $\text{DVDD}$  drops below 3 V.

**AC Characteristics,  $T_A = 25^\circ\text{C}$ ,  $\text{PVCC\_X}$ ,  $\text{AVCC} = 18 \text{ V}$ ,  $\text{AVDD}, \text{DVDD} = 3.3 \text{ V}$ ,  $\text{R}_L = 8 \Omega$  (unless otherwise noted)<sup>(1)</sup>**

| PARAMETER                                             |                                         | TEST CONDITIONS                                                                                                    | MIN | TYP   | MAX | UNIT             |

|-------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------------------|

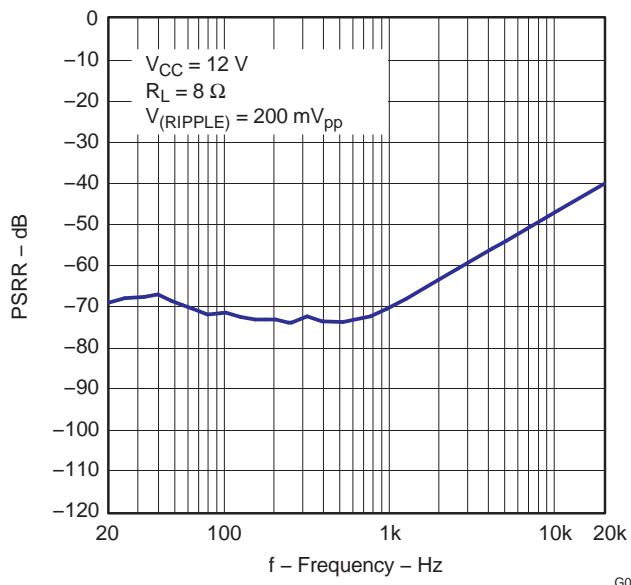

| KSVR                                                  | Supply ripple rejection                 | 100-mV <sub>PP</sub> ripple at 20 Hz–20 kHz, BTL, 50% duty cycle PWM                                               |     | -60   |     | dB               |

| $P_O$                                                 | Continuous output power                 | BTL ( $\text{R}_L = 8 \Omega$ , THD+N = 10%, $f = 1 \text{ kHz}$ , $\text{PVCC} = 18 \text{ V}$ )                  |     | 20.6  |     | W                |

|                                                       |                                         | BTL ( $\text{R}_L = 8 \Omega$ , THD+N = 7%, $f = 1 \text{ kHz}$ , $\text{PVCC} = 18 \text{ V}$ )                   |     | 19.3  |     | W                |

|                                                       |                                         | SE ( $\text{R}_L = 4 \Omega$ , THD+N = 10%, $f = 1 \text{ kHz}$ , $\text{PVCC} = 24 \text{ V}$ )                   |     | 18.1  |     | W                |

|                                                       |                                         | SE ( $\text{R}_L = 4 \Omega$ , THD+N = 7%, $f = 1 \text{ kHz}$ , $\text{PVCC} = 24 \text{ V}$ )                    |     | 17.3  |     | W                |

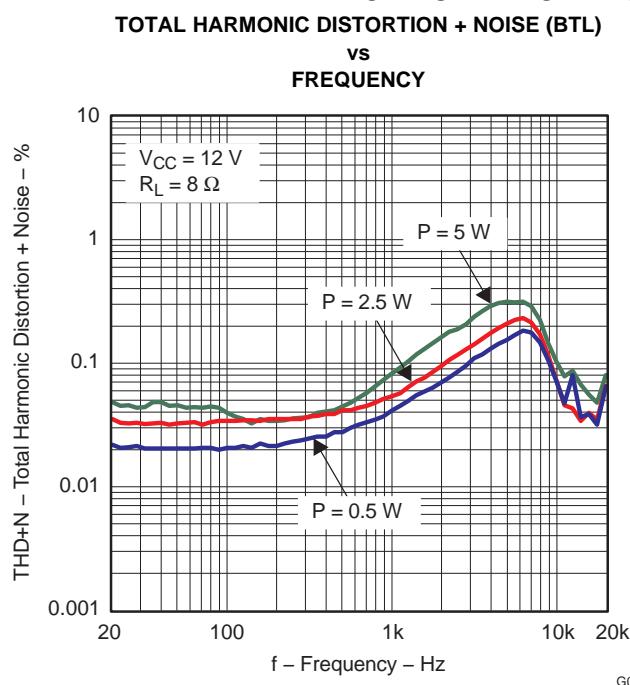

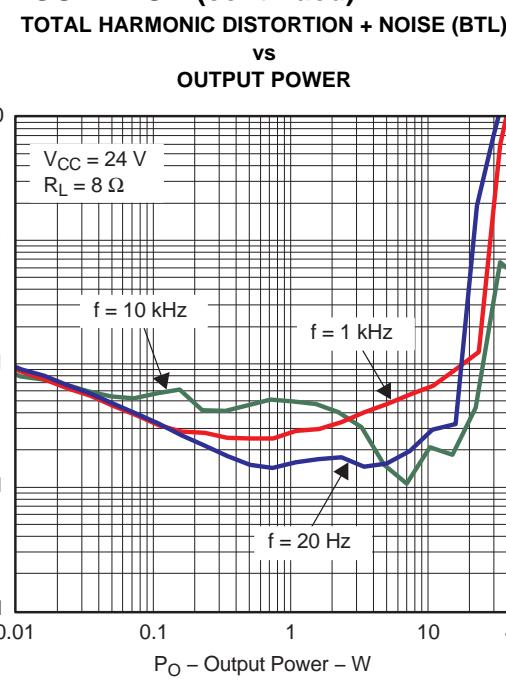

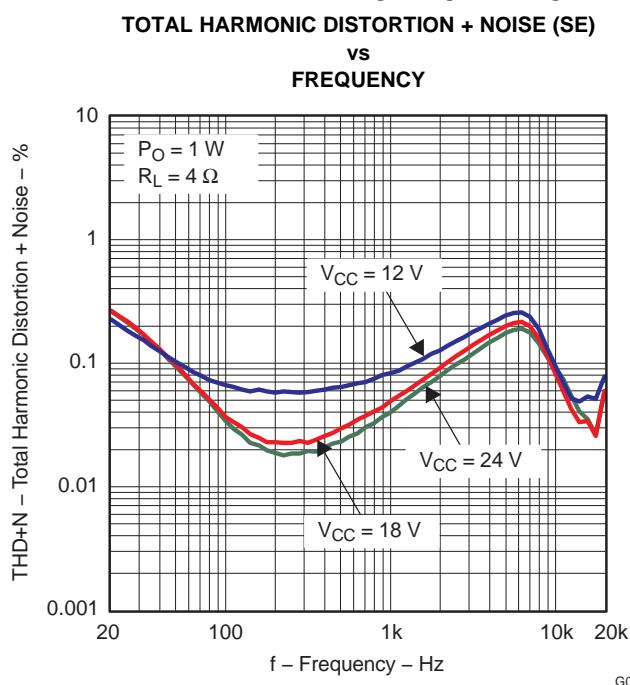

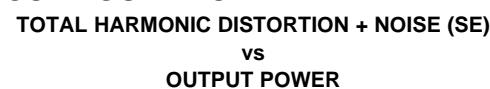

| THD+N                                                 | Total harmonic distortion + noise (SE)  | $\text{V}_{CC} = 24 \text{ V}$ , $\text{R}_L = 4 \Omega$ , $f = 1 \text{ kHz}$ , $P_O = 10 \text{ W}$ (half-power) |     | 0.08% |     |                  |

|                                                       | Total harmonic distortion + noise (BTL) | $\text{V}_{CC} = 18 \text{ V}$ , $\text{R}_L = 8 \Omega$ , $f = 1 \text{ kHz}$ , $P_O = 10 \text{ W}$ (half-power) |     | 0.05% |     |                  |

| $V_n$                                                 | Output integrated noise                 | 20 Hz to 22 kHz (BD mode)                                                                                          |     | 89    |     | $\mu\text{V}$    |

|                                                       |                                         | A-weighted filter; $\text{MUTE} = \text{LOW}$                                                                      |     | -81   |     | dBV              |

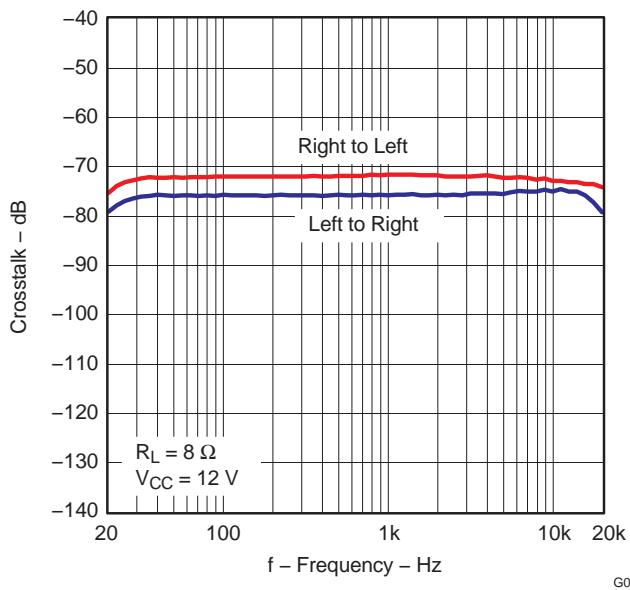

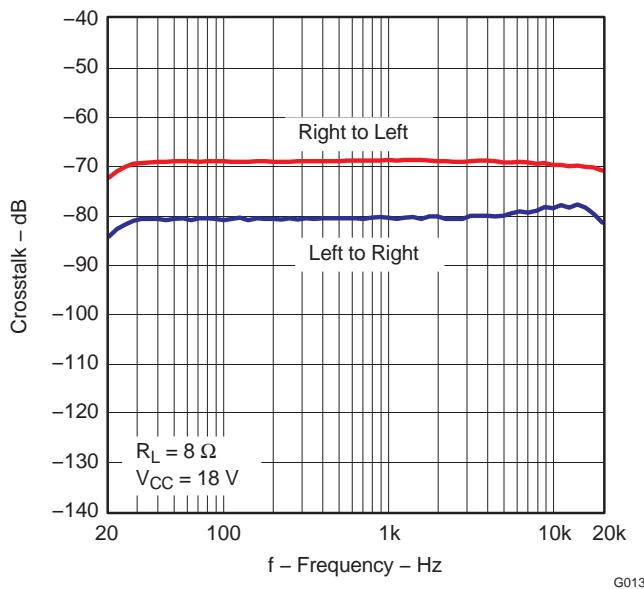

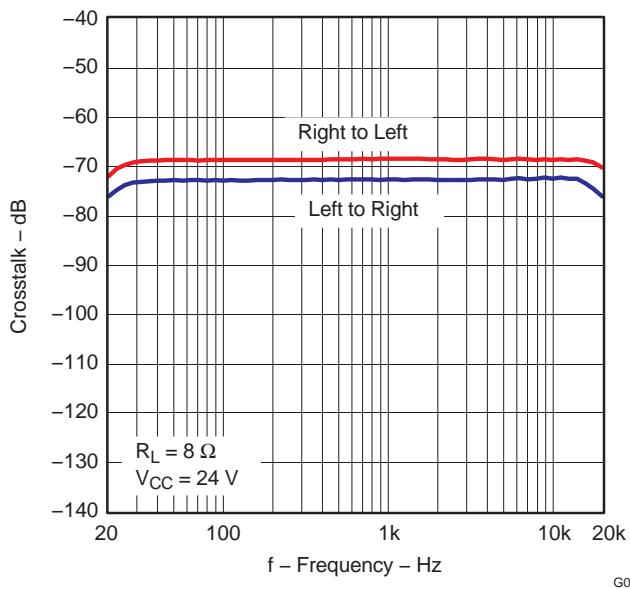

| Crosstalk                                             |                                         | $P_O = 1 \text{ W}$ , $f = 1 \text{ kHz}$                                                                          |     | -69   |     | dB               |

| SNR                                                   | Signal-to-noise ratio                   | Maximum output at THD+N < 1%, $f = 1 \text{ kHz}$ , A-weighted                                                     |     | 100   |     | dB               |

| Thermal trip point (output shutdown, unlatched fault) |                                         |                                                                                                                    |     | 150   |     | $^\circ\text{C}$ |

| Thermal hysteresis                                    |                                         |                                                                                                                    |     | 15    |     | $^\circ\text{C}$ |

(1) All measurement in AD mode (unless otherwise noted).

**AC Characteristics,  $T_A = 25^\circ\text{C}$ ,  $\text{PVCC\_X}$ ,  $\text{AVCC} = 12 \text{ V}$ ,  $\text{AVDD}, \text{DVDD} = 3.3 \text{ V}$ ,  $\text{R}_L = 8 \Omega$  (unless otherwise noted)<sup>(1)</sup>**

| PARAMETER                                             |                                         | TEST CONDITIONS                                                                                                   | MIN | TYP   | MAX | UNIT             |

|-------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------------------|

| KSVR                                                  | Supply ripple rejection                 | 100-mV <sub>PP</sub> ripple at 20 Hz–20 kHz, BTL, 50% duty cycle PWM                                              |     | -60   |     | dB               |

| $P_O$                                                 | Continuous output power                 | BTL ( $\text{R}_L = 8 \Omega$ , THD+N = 10%, $f = 1 \text{ kHz}$ )                                                |     | 9.2   |     | W                |

|                                                       |                                         | BTL ( $\text{R}_L = 8 \Omega$ , THD+N = 7%, $f = 1 \text{ kHz}$ )                                                 |     | 8.7   |     | W                |

|                                                       |                                         | SE ( $\text{R}_L = 4 \Omega$ , THD+N = 10%, $f = 1 \text{ kHz}$ )                                                 |     | 4.5   |     | W                |

|                                                       |                                         | SE ( $\text{R}_L = 4 \Omega$ , THD+N = 7%, $f = 1 \text{ kHz}$ )                                                  |     | 4.2   |     | W                |

| THD+N                                                 | Total harmonic distortion + noise (BTL) | $\text{V}_{CC} = 12 \text{ V}$ , $\text{R}_L = 8 \Omega$ , $f = 1 \text{ kHz}$ , $P_O = 5 \text{ W}$ (half-power) |     | 0.07% |     |                  |

| $V_n$                                                 | Output integrated noise                 | 20 Hz to 22 kHz (BD mode)                                                                                         |     | 89    |     | $\mu\text{V}$    |

|                                                       |                                         | A-weighted filter                                                                                                 |     | -81   |     | dBV              |

| Crosstalk                                             |                                         | $P_O = 1 \text{ W}$ , $f = 1 \text{ kHz}$                                                                         |     | -75   |     | dB               |

| SNR                                                   | Signal-to-noise ratio                   | Maximum output at THD+N < 1%, $f = 1 \text{ kHz}$ , A-weighted                                                    |     | 96    |     | dB               |

| Thermal trip point (output shutdown, unlatched fault) |                                         |                                                                                                                   |     | 150   |     | $^\circ\text{C}$ |

| Thermal hysteresis                                    |                                         |                                                                                                                   |     | 15    |     | $^\circ\text{C}$ |

(1) All measurement in AD mode (unless otherwise noted).

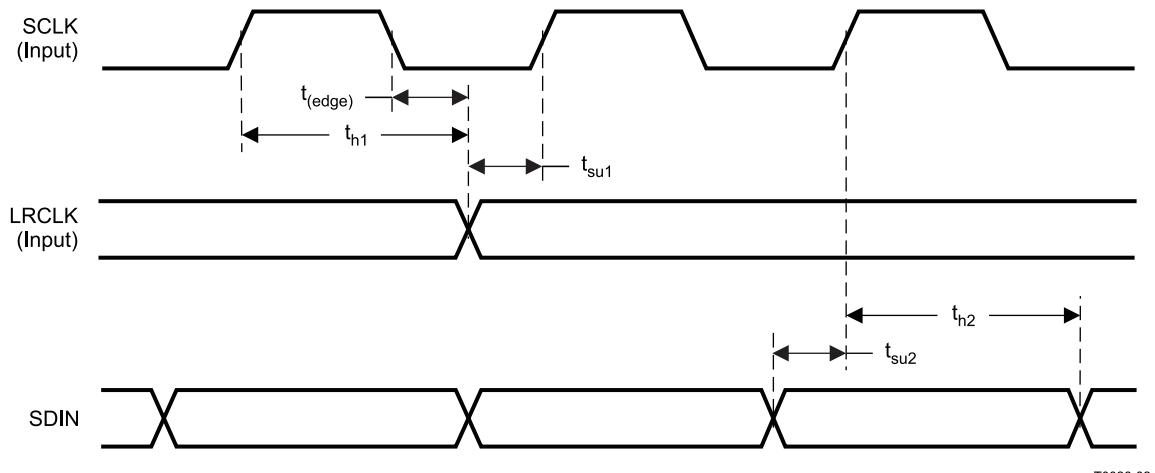

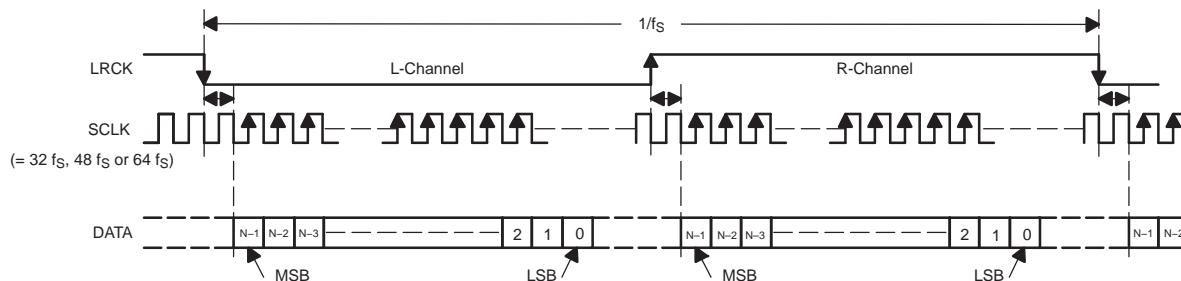

## SERIAL AUDIO PORTS SLAVE MODE

over recommended operating conditions (unless otherwise noted)

| PARAMETER                                                                          | TEST CONDITIONS       | MIN   | TYP    | MAX | UNIT        |

|------------------------------------------------------------------------------------|-----------------------|-------|--------|-----|-------------|

| $f_{SCLKIN}$ Frequency, $SCLK$ $32 \times f_S$ , $48 \times f_S$ , $64 \times f_S$ | $C_L = 30 \text{ pF}$ | 1.024 | 12.288 |     | MHz         |

| $t_{su1}$ Setup time, LRCLK to SCLK rising edge                                    |                       | 10    |        |     | ns          |

| $t_{h1}$ Hold time, LRCLK from SCLK rising edge                                    |                       | 10    |        |     | ns          |

| $t_{su2}$ Setup time, SDIN to SCLK rising edge                                     |                       | 10    |        |     | ns          |

| $t_{h2}$ Hold time, SDIN from SCLK rising edge                                     |                       | 10    |        |     | ns          |

| LRCLK frequency                                                                    |                       | 32    | 48     | 192 | kHz         |

| SCLK duty cycle                                                                    |                       | 40%   | 50%    | 60% |             |

| LRCLK duty cycle                                                                   |                       | 40%   | 50%    | 60% |             |

| SCLK rising edges between LRCLK rising edges                                       |                       | 32    | 64     |     | SCLK edges  |

| $t_{(\text{edge})}$ LRCLK clock edge with respect to the falling edge of SCLK      |                       | -1/4  | 1/4    |     | SCLK period |

T0026-02

**Figure 1. Slave Mode Serial Data Interface Timing**

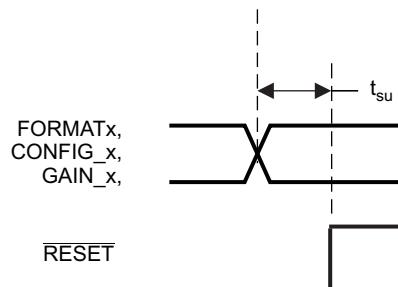

## HARDWARE SELECT PINS

over recommended operating conditions (unless otherwise noted)

| PARAMETER                                                                                                  | MIN | TYP | MAX | UNIT          |

|------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $t_{su}$ Setup time, $\text{FORMAT}_x$ , $\text{CONFIG}_x$ , $\text{GAIN}_x$ to $\text{RESET}$ rising edge | 100 |     |     | $\mu\text{s}$ |

**Figure 2. Mode Pins Setup Time**

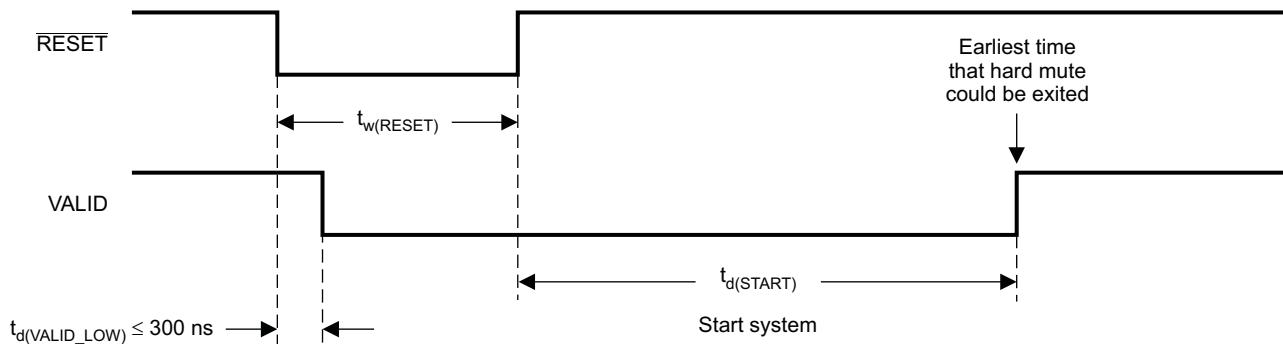

## RESET TIMING (RESET) AND POWER-ON RESET

Control signal parameters over recommended operating conditions (unless otherwise noted)

| PARAMETER                                                                  | MIN | TYP  | MAX | UNIT |

|----------------------------------------------------------------------------|-----|------|-----|------|

| $t_{d(\text{VALID\_LOW})}$ Time to assert VALID (reset to power stage) low |     | 300  |     | ns   |

| $t_w(\text{RESET})$ Pulse duration, $\overline{\text{RESET}}$ active       |     | 1    |     | ms   |

| $t_{d(\text{START})}$ Time to start-up                                     |     | 13.5 |     | ms   |

T0029-05

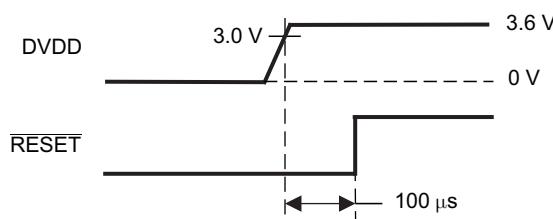

Figure 3. Reset Timing

When power is applied to DVDD, must be held low for at least 100  $\mu$ s after DVDD reaches 3.0 V.

Figure 4. Power-On Reset Timing

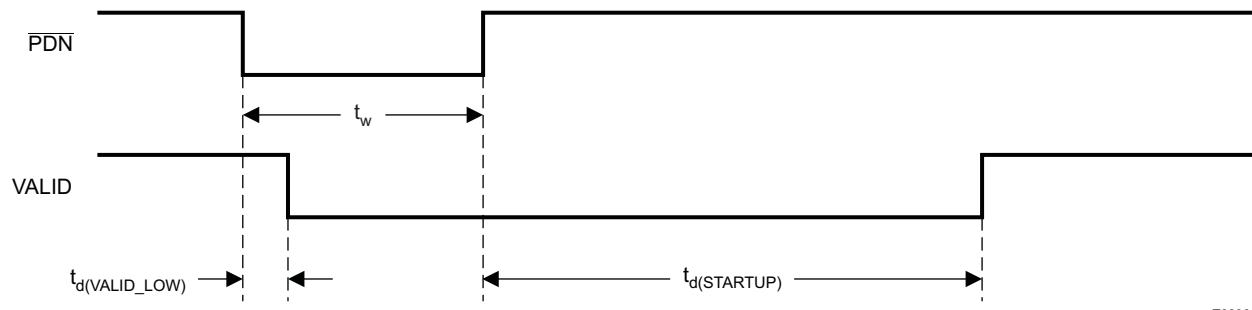

## POWER-DOWN (PDN) TIMING

Control signal parameters over recommended operating conditions (unless otherwise noted)

| PARAMETER                                                                  | MIN | TYP | MAX | UNIT    |

|----------------------------------------------------------------------------|-----|-----|-----|---------|

| $t_{d(\text{VALID\_LOW})}$ Time to assert VALID (reset to power stage) low |     | 725 |     | $\mu$ s |

| $t_{d(\text{STARTUP})}$ Device startup time                                |     | 120 |     | ms      |

| $t_w$ Minimum pulse duration required                                      |     | 800 |     | ns      |

T0030-04

**Figure 5. Power-Down Timing**

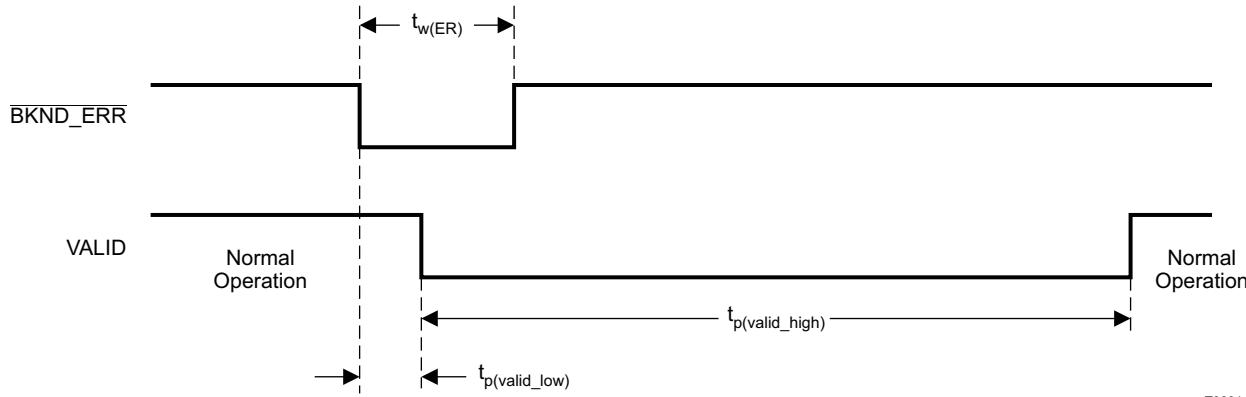

## BACK-END ERROR (BKND\_ERR)

Control signal parameters over recommended operating conditions (unless otherwise noted)

| PARAMETER            |                                                                                                                                                            | MIN | TYP | MAX | UNIT |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $t_{w(ER)}$          | Pulse duration, BKND_ERR active (active-low)                                                                                                               | 350 |     |     | ns   |

| $t_{p(valid\_high)}$ | Time to stay in the OUT_x low state. After $t_{p(valid\_high)}$ , the TAS5704 attempts to bring the system out of the OUT_x low state if BKND_ERR is high. | 300 |     |     | ms   |

| $t_{p(valid\_low)}$  | Time TAS5704 takes to bring OUT_x low after BKND_ERR assertion.                                                                                            | 350 |     |     | ns   |

T0031-04

Figure 6. Error Recovery Timing

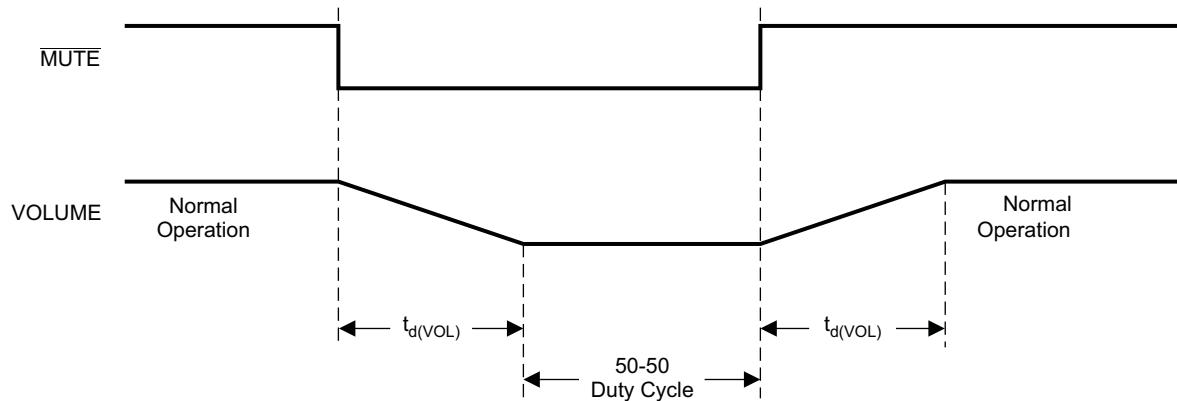

## MUTE TIMING (MUTE)

Control signal parameters over recommended operating conditions (unless otherwise noted)

| PARAMETER    |                                                                                | MIN  | TYP | MAX | UNIT  |

|--------------|--------------------------------------------------------------------------------|------|-----|-----|-------|

| $t_{d(VOL)}$ | Volume ramp time. Ramp Time = Number of Steps $\times$ StepSize <sup>(1)</sup> | 1024 |     |     | steps |

(1) StepSize = 4 LRCLKs (for 32–48 kHz sample rate); 8 LRCLKs (for 88.2–96 kHz sample rate); 16 LRCLKs (for 176.4–192 kHz sample rate)

T0032-03

Figure 7. Mute Timing

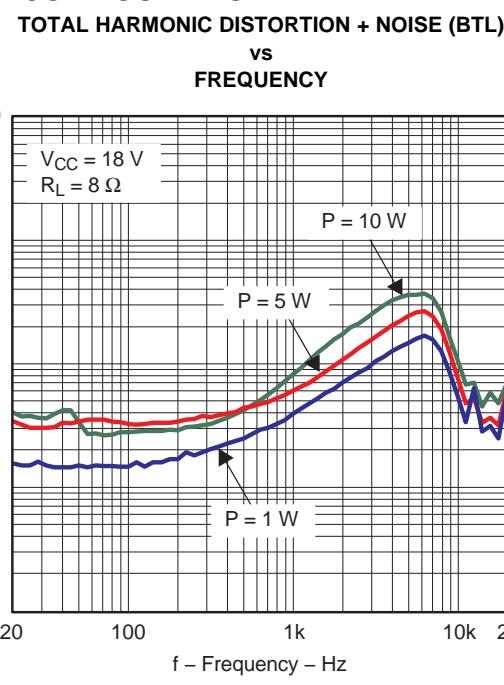

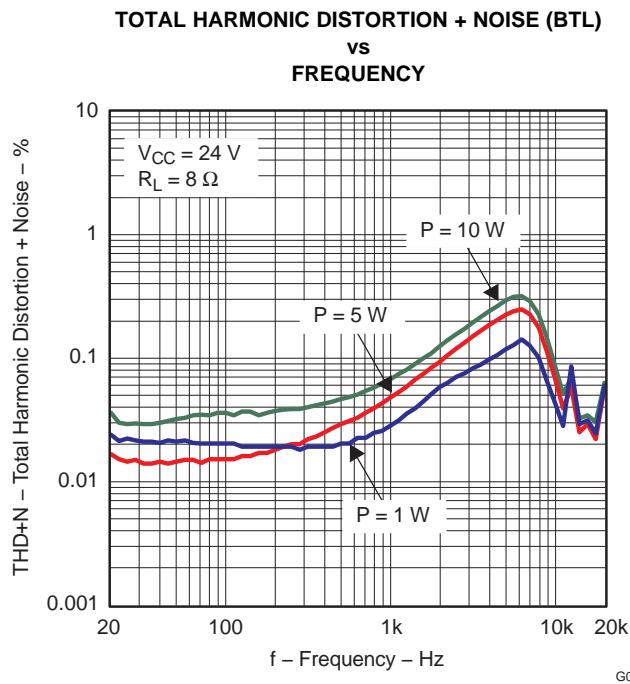

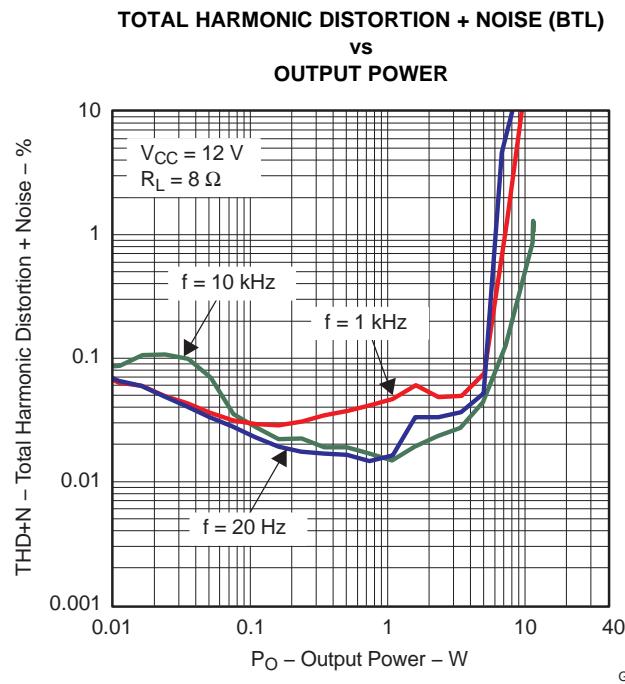

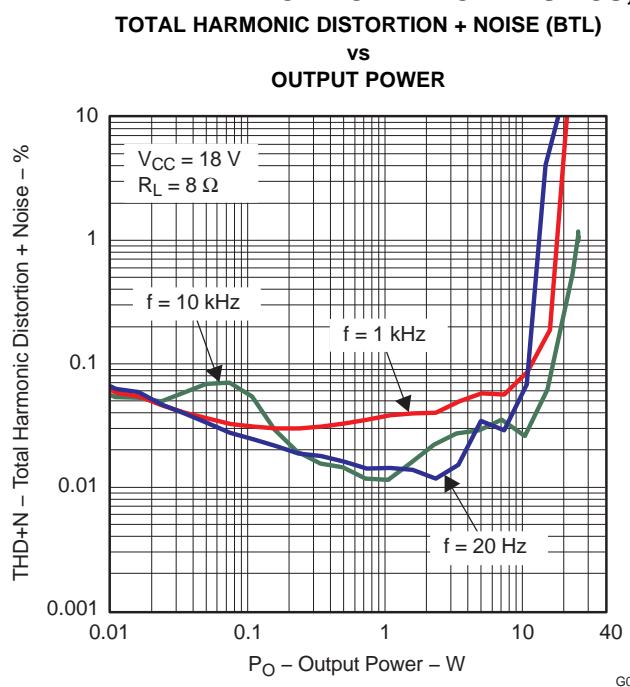

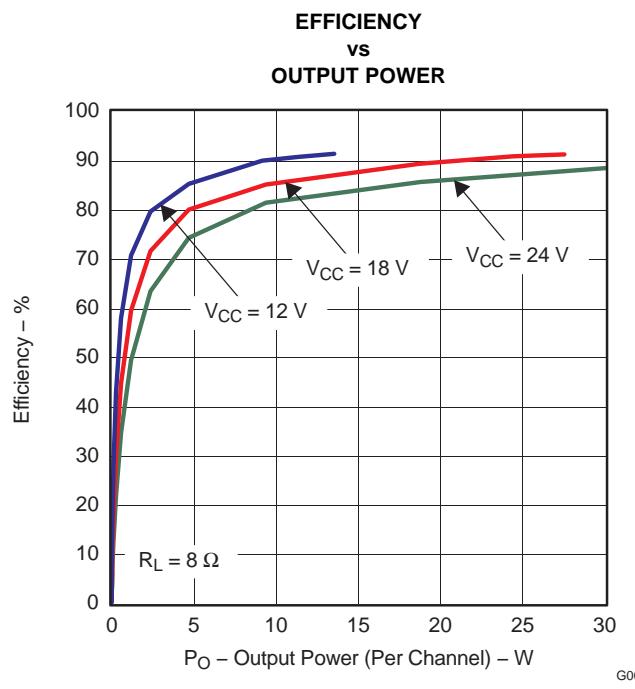

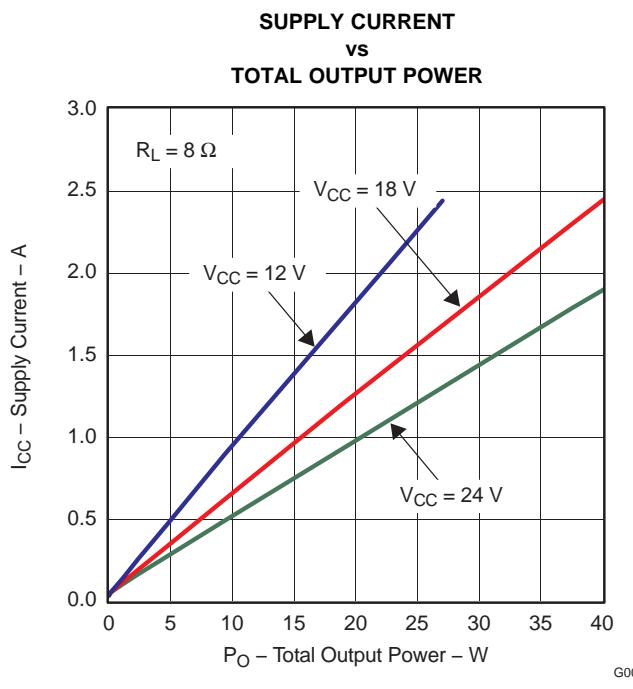

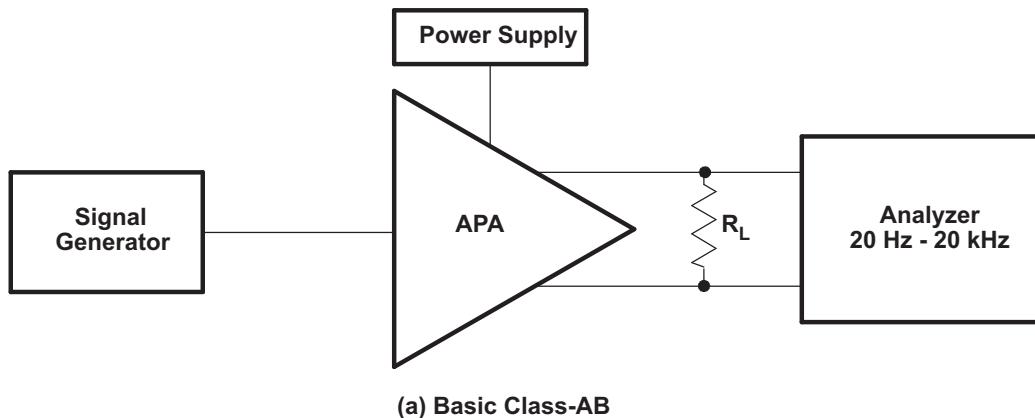

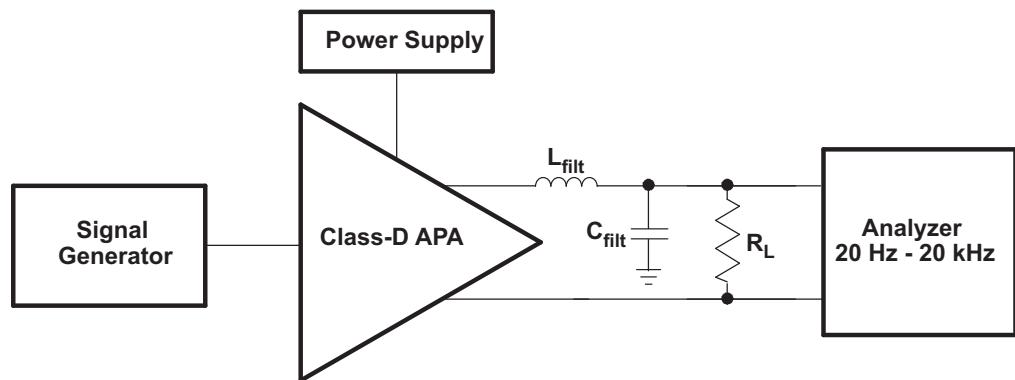

### TYPICAL CHARACTERISTICS, BTL CONFIGURATION

Figure 8.

Figure 9.

Figure 10.

Figure 11.

### TYPICAL CHARACTERISTICS, BTL CONFIGURATION (continued)

Figure 12.

Figure 13.

Figure 14.

Figure 15.

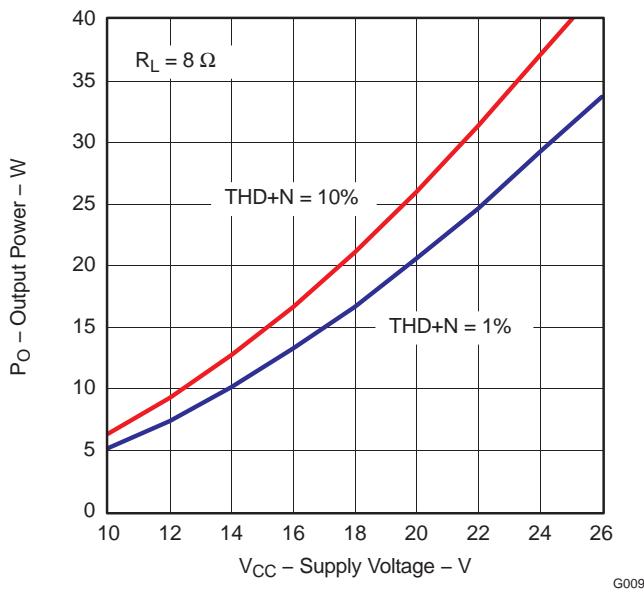

**TYPICAL CHARACTERISTICS, BTL CONFIGURATION (continued)**

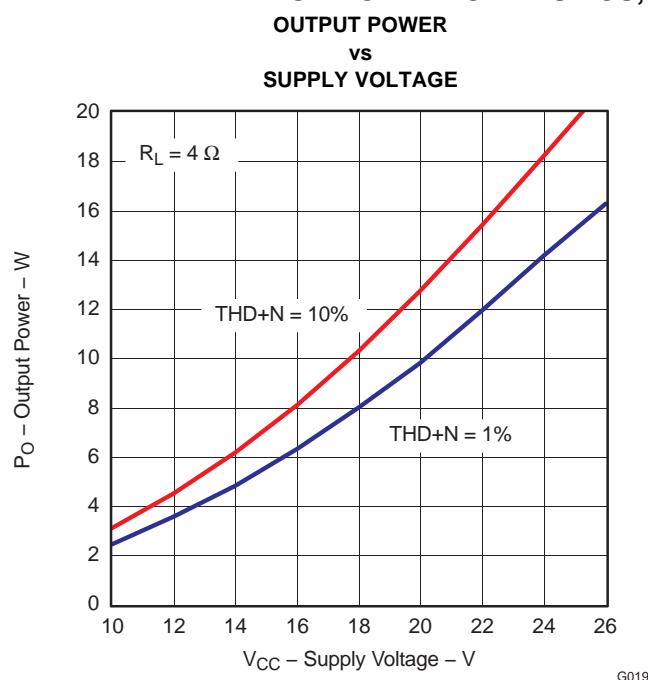

**OUTPUT POWER

vs

SUPPLY VOLTAGE**

**Figure 16.**

**CROSSTALK

vs

FREQUENCY**

**Figure 17.**

**CROSSTALK

vs

FREQUENCY**

**Figure 18.**

**CROSSTALK

vs

FREQUENCY**

**Figure 19.**

### TYPICAL CHARACTERISTICS, SE CONFIGURATION

Figure 20.

Figure 21.

Figure 22.

Figure 23.

**TYPICAL CHARACTERISTICS, SE CONFIGURATION (continued)**

**Figure 24.**

**SUPPLY RIPPLE REJECTION RATIO

vs

FREQUENCY**

**Figure 25.**

## DETAILED DESCRIPTION

### POWER SUPPLY

The digital portion of the chip requires 3.3 V, and the power section operates from a variable range from 10 V to 26 V.

### Clock, Auto Detection, and PLL

The TAS5704 DAP is a clock slave device. It accepts MCLK, SCLK, and LRCLK.

The TAS5704 checks to verify that SCLK is a specific value of  $32-f_s$ ,  $48-f_s$ , or  $64-f_s$ . The DAP only supports a  $1 \times f_s$  LRCLK. The timing relationship of these clocks to SDIN1 and SDIN2 is shown in subsequent sections. The clock section uses MCLK or the internal oscillator clock (when MCLK is unstable or absent) to produce the internal clock.

The DAP can auto-detect and set the internal clock control logic to the appropriate settings for the frequencies of 32 kHz, normal speed (44.1 or 48 kHz), double speed (88.2 kHz or 96 kHz), and quad speed (176.4 kHz or 192 kHz).

### PWM SECTION

The DAP (digital audio processor) has four channels of high-performance digital PWM modulators that are designed to drive bridge-tied output H-bridge configurations with AD or BD modulation and single-ended output configurations with AD modulation.

The DAP uses noise-shaping and sophisticated error correction algorithms to achieve high power efficiency and high-performance digital audio reproduction.

The PWM section accepts 24-bit PCM data from the DAP and outputs up to 4 PWM audio output channels.

The PWM section has individual channel dc blocking filters that are ALWAYS enabled. The filter cutoff frequency is less than 1 Hz.

### SERIAL DATA INTERFACE

Serial data is input on SDIN1 and SDIN2. The PWM outputs are derived from SDIN1 and SDIN2. The TAS5704 DAP accepts 32-, 44.1-, 48-, 88.2-, 96-, 176.4-, and 192-kHz serial data in 16-, 18-, 20-, or 24-bit data in left-justified, right-justified, and I<sup>2</sup>S serial data formats. See [Table 1](#) for format control settings.

### SERIAL INTERFACE CONTROL AND TIMING

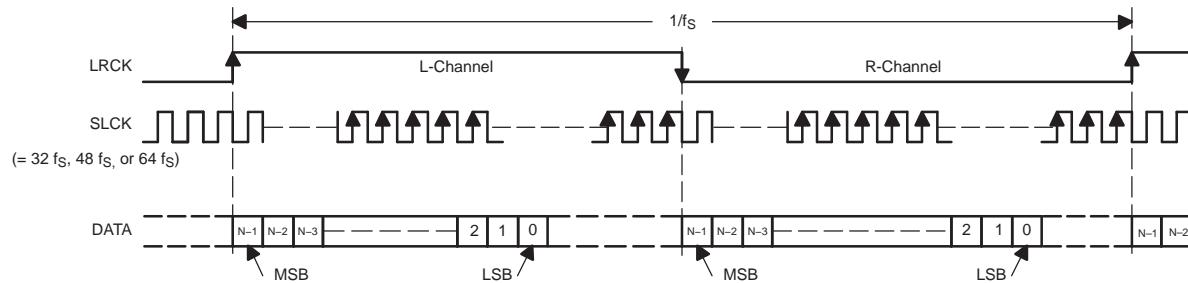

#### I<sup>2</sup>S Timing

I<sup>2</sup>S timing uses LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. LRCLK is low for the left channel and high for the right channel. A system clock (SCLK) running at 32, 48, or  $64 \times f_s$  is used to clock in the data. There is a delay of one bit clock from the time the LRCLK signal changes state to the first bit of data on the data lines. The data is written MSB first and is valid on the rising edge of the bit clock. The DAP masks unused trailing data bit positions.

Figure 26. I<sup>2</sup>S Format

## Left-Justified

Left-justified (LJ) timing uses LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. LRCLK is high for the left channel and low for the right channel. A bit clock running at 32, 48, or  $64 \times f_s$  is used to clock in the data. The first bit of data appears on the data lines at the same time LRCLK toggles. The data is written MSB first and is valid on the rising edge of the bit clock. The DAP masks unused trailing data bit positions.

**Figure 27. Left-Justified Format**

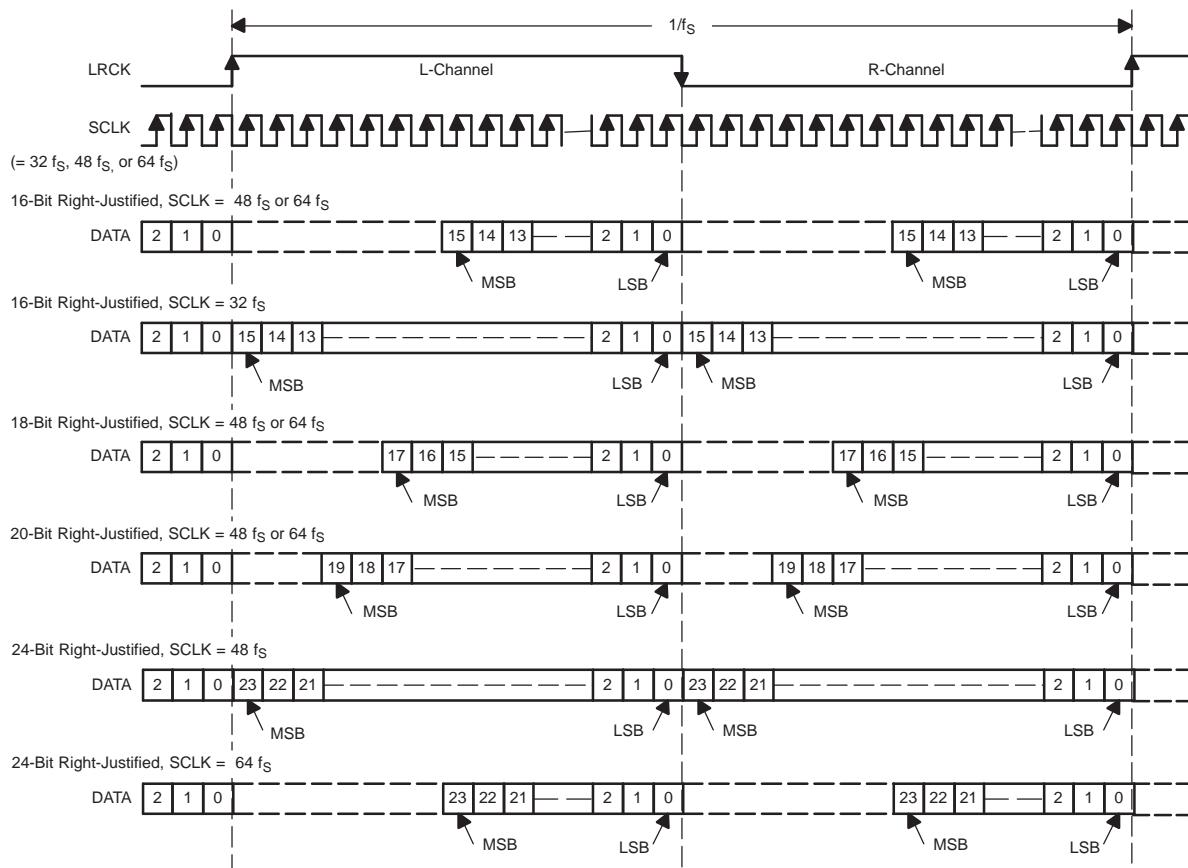

## Right-Justified

Right-justified (RJ) timing uses LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. LRCLK is high for the left channel and low for the right channel. A bit clock running at 32, 48, or  $64 \times f_s$  is used to clock in the data. The first bit of data appears on the data 8 bit-clock periods (for 24-bit data) after LRCLK toggles. In RJ mode the LSB of data is always clocked by the last bit clock before LRCLK transitions. The data is written MSB first and is valid on the rising edge of the bit clock. The DAP masks unused leading data bit positions.

**Figure 28. Right-Justified Format**

## Format Control

The digital data input format is selected via three external terminals (FORMAT0, FORMAT1, and FORMAT2). **Table 1** lists the corresponding data format for SDIN1 and SDIN2. LRCLK and SCLK are shared clocks for SDIN1 and SDIN2. Changes to the FORMATx terminals are latched in immediately on a rising edge of RESET. Changes to the FORMATx terminals while RESET is high are not allowed.

**Table 1. Format Control**

| FORMAT2 | FORMAT1 | FORMAT0 | SERIAL DIGITAL DATA FORMAT        |

|---------|---------|---------|-----------------------------------|

| 0       | 0       | 0       | 16-Bit right-justified            |

| 0       | 0       | 1       | 18-Bit right-justified            |

| 0       | 1       | 0       | 20-Bit right-justified            |

| 0       | 1       | 1       | 24-Bit right-justified            |

| 1       | 0       | 0       | 16-, 24-Bit I <sup>2</sup> S      |

| 1       | 0       | 1       | 16-, 24-Bit left-justified        |

| 1       | 1       | 0       | Reserved. Setting is not allowed. |

| 1       | 1       | 1       | Reserved. Setting is not allowed. |

## Gain Control

The gain of the DAP is selected via two external gain pins (GAIN\_0 and GAIN\_1). **Table 2** lists the corresponding channel gain (for ALL channels) for GAIN\_0 and GAIN\_1 settings. Individual channel gain is not possible. Changes to the GAIN\_x terminals are latched in immediately on a rising edge of RESET. Changes to the GAIN\_x terminals while RESET is high are not allowed.

**Table 2. Gain Control**

| GAIN_1 | GAIN_0 | CHANNEL GAIN (dB) | OUTPUT VOLTAGE WITH FULL SCALE INPUT (V <sub>rms</sub> ) — BTL |

|--------|--------|-------------------|----------------------------------------------------------------|

| 0      | 0      | -3                | 17.56                                                          |

| 0      | 1      | 3                 | 35.04 <sup>(1)</sup>                                           |

| 1      | 0      | 9                 | 70.08 <sup>(1)</sup>                                           |

| 1      | 1      | 12                | 99.00 <sup>(1)</sup>                                           |

(1) Output clipped. See the calculation example in the Application section.

## Output Configuration Control

The PWM outputs can be remapped to allow 2-ch, 2.1-ch, and 4-ch operation. Two terminals are used for this mapping, CONFIG\_1 and CONFIG\_2. **Table 3** lists the output configurations that are supported. Changes to the CONFIG\_x terminals are latched in immediately on a rising edge of RESET. Changes to the CONFIG\_x terminals while RESET is high are not allowed.

**Table 3. Output Configurations**

| CONFIG_2 | CONFIG_1 | OUTPUT CONFIGURATION                                                                                                                                     |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 0        | 2-Ch Mode, BTL, AD modulation. SUB+/- is derived from the SDIN2 input (left channel). SUB+/- is AD modulation with SUB- equal to the compliment of SUB+. |

| 0        | 1        | 2-Ch Mode, BTL, BD modulation. SUB+/- is derived from the SDIN2 input (left channel), and SUB+/- is BD PWM.                                              |

| 1        | 0        | 2.1-Ch Mode (2xSE outputs, 1xBTL output). AD modulation. No SUB+/- PWM output.                                                                           |

| 1        | 1        | 4-Ch Mode (4xSE outputs). AD modulation. No SUB+/- PWM output.                                                                                           |

## APPLICATION INFORMATION

### CLOSED-LOOP POWER STAGE CHARACTERISTICS

The TAS5704 is PWM input power stage with a closed loop architecture. A feedback loop varies the PWM output duty cycle with changes in the supply voltage. This ensures that the output voltage (and output power) remain the same over transitions in the power supply.

Open-loop power stages have an output duty cycle that is equal to the input duty cycle. Since the duty cycle does NOT change to compensate for changes in the supply voltage, the output voltage (and power) change with supply voltage changes. This is undesirable effect that closed-loop architecture of the TAS5704 solves.

The single-ended (SE) gain of the TAS5704 is fixed, and specified below:

$$\text{TAS5704 Gain} = 0.13 / \text{Modulation Level (Vrms/%)}$$

Modulation level = fraction of full-scale modulation of the PWM signal at the input of the power stage.

$$\text{TAS5704 (SE) Voltage Level (in Vrms)} = 0.13 \times \text{Modulation Level}$$

The bridge-tied (BTL) gain of the TAS5704 is equal to 2x the SE gain:

$$\text{TAS5704 (BTL) Voltage Level (in Vrms)} = 0.26 \times \text{Modulation Level}$$

For a digital modulator like the TAS5704, the default maximum modulation limit is 97.7%. For a full scale input, the PWM output switches between 2.3% and 97.7%. This equates to a modulation level of 95.4% for a full scale input (0 dBFS).

For example, calculate the output voltage in RMS volts given a -20 dBFS signal to a digital modulator with a maximum modulation limit of 97.7% in a BTL output configuration:

$$\begin{aligned} \text{TAS5704 Output Voltage} &= 0.1 (-20\text{dB}) \times 0.26 (\text{Gain}) \times 95.4 (\text{Modulation Level}) \\ &= 2.48 \text{ Vrms} \end{aligned}$$

For shutdown and power-down, the PDN terminal should be cycled low for the “turn-off” time specified in the DC Electrical Characteristics table before PVCC falls below 10 V and DVDD/AVDD falls below 3 V. For SE mode, this is approximately 500ms. For BTL mode, the time is much faster, at 30ms. This ensures the best “pop” performance in the system.

### POWER SUPPLIES

To allow simplified system design, the TAS5704 requires only a single supply (PVCC) for the power blocks and a 3.3 V (DVDD/AVDD) supply for PWM input blocks. In addition, the high-side gate drive is provided by built-in bootstrap circuits requiring only an external capacitor for each half-bridge.

DVDD/AVDD must be applied at the same time or before PVCC is applied on power-up. For power-down, PVCC and DVDD/AVDD should remain active while the PDN terminal is cycled low and held low for at least the time specified for  $t_{OFF}$  in the Electrical Characteristics table.

In order for the bootstrap circuit to function properly, it is necessary to connect a small ceramic capacitor from each bootstrap pin (BS<sub>\_</sub>) to the corresponding output pin (OUT<sub>\_</sub>). When the power-stage output is low, the bootstrap capacitor is charged through an internal diode. When the power-stage output is high, the bootstrap capacitor potential is shifted above the output potential and thus provides a suitable voltage supply for the high-side gate drive.

### DEVICE PROTECTION SYSTEM

The TAS5704 contains a complete set of protection circuits carefully designed to make system design efficient as well as to protect the device against any kind of permanent failures due to short circuits, overtemperature, overvoltage, and undervoltage.

## PROTECTION MECHANISMS IN THE TAS5704

- SCP (short-circuit protection) protects against shorts across the load, to GND, and to PVCC.

- OTP turns off the device if  $T_{\text{junction}} \text{ (typical)} > 150^\circ\text{C}$ .

- UVP turns off the device if  $\text{PVCC} \text{ (typical)} < 8.4 \text{ V}$

- OVP turns off the device if  $\text{PVCC} \text{ (typical)} > 27.5 \text{ V}$

A short-circuit condition can be detected also by an external controller. The VALID pin goes low in the event of a short circuit. The VALID pin can be monitored by an external  $\mu\text{C}$ . The TAS5704 initiates a back-end error sequence by itself to recover from the error, which involves settling VALID low for 300 ms and then retrying to check whether the short-circuit condition still exists.

## RECOVERY FROM ERROR

- OTP turns on the device back when  $T_{\text{die}} \text{ (typical)} < 135^\circ\text{C}$ .

- UVP turns on the device if  $\text{PVCC} \text{ (typical)} > 8.5 \text{ V}$ .

- OVP turns on the device if  $\text{PVCC} \text{ (typical)} < 27.2 \text{ V}$ .

- SCP (short-circuit protection) turns on the device if the short-circuit is removed. See the Back-End Error section for the sequence.

## SINGLE-ENDED OUTPUT CAPACITOR, $C_o$

In single-ended (SE) applications, the dc blocking capacitor forms a high-pass filter with the speaker impedance. The frequency response rolls off with decreasing frequency at a rate of 20 dB/decade. The cutoff frequency is determined by

$$f_c = 1/2\pi C_o Z_L \quad (1)$$

[Table 4](#) shows some common component values and the associated cutoff frequencies:

**Table 4. Common Filter Responses**

| SPEAKER IMPEDANCE ( $\Omega$ ) | C <sub>SE</sub> – DC BLOCKING CAPACITOR ( $\mu\text{F}$ ) |                                |                                |

|--------------------------------|-----------------------------------------------------------|--------------------------------|--------------------------------|

|                                | f <sub>c</sub> = 60 Hz (-3 dB)                            | f <sub>c</sub> = 40 Hz (-3 dB) | f <sub>c</sub> = 20 Hz (-3 dB) |

| 4                              | 680                                                       | 1000                           | 2200                           |

| 8                              | 330                                                       | 470                            | 1000                           |

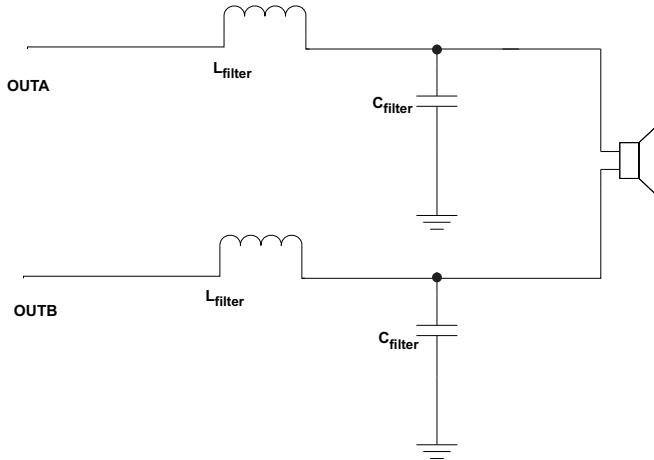

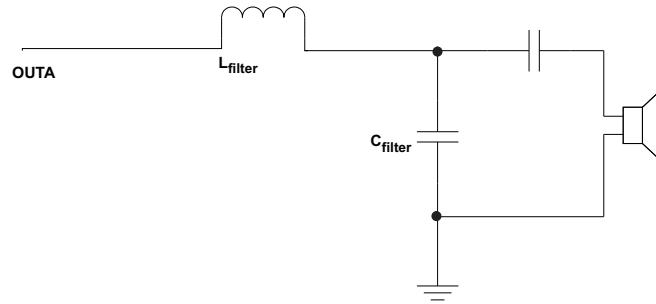

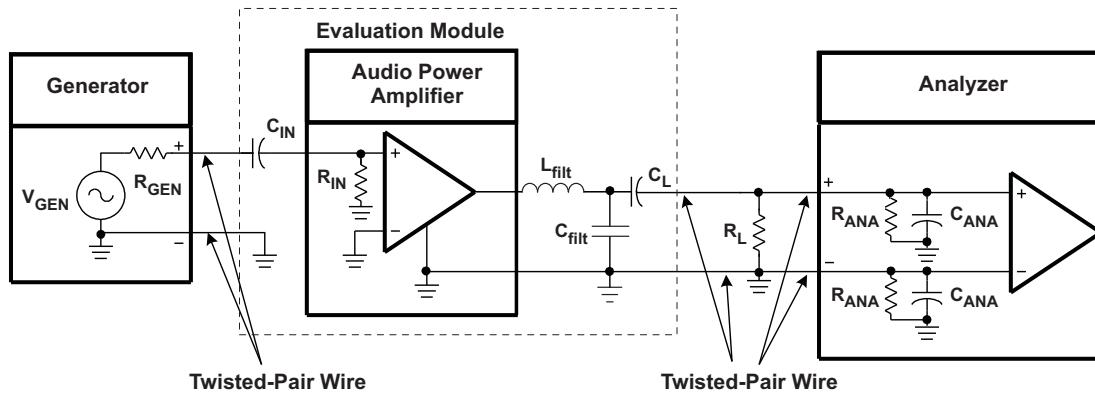

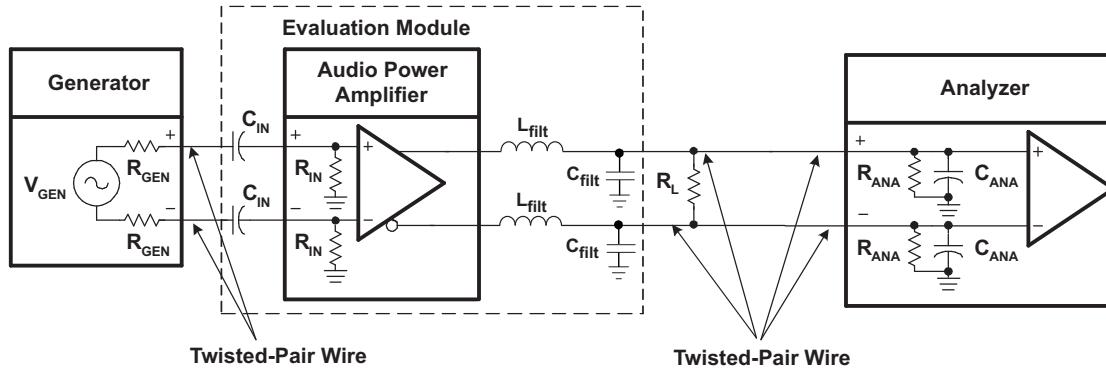

## OUTPUT FILTER AND FREQUENCY RESPONSE

For the best frequency response, a flat-passband output filter (second-order Butterworth) may be used. The output filter components consist of the series inductor and capacitor to ground at the output pins. There are several possible configurations, depending on the speaker impedance and whether the output configuration is single-ended (SE) or bridge-tied load (BTL). [Table 5](#) lists the recommended values for the filter components. It is important to use a high-quality capacitor in this application. A rating of at least X7R is required.

**Table 5. Recommended Filter Output Components**

| OUTPUT CONFIGURATION   | SPEAKER IMPEDANCE ( $\Omega$ ) | FILTER INDUCTOR ( $\mu\text{H}$ ) | FILTER CAPACITOR ( $\text{nF}$ ) |

|------------------------|--------------------------------|-----------------------------------|----------------------------------|

| Single Ended (SE)      | 4                              | 22                                | 680                              |

|                        | 8                              | 47                                | 390                              |

| Bridge Tied Load (BTL) | 4                              | 10                                | 1500                             |

|                        | 8                              | 22                                | 680                              |

Figure 29. BTL Filter Configuration

Figure 30. SE Filter Configuration

## POWER-SUPPLY DECOUPLING, $C_s$