ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

**TAS5613A**

# **150W** 立体声/**300W** 单声道 PurePath™ HD 模拟输入功率级

#### 查询样品: TAS5613A

# 特性

- 有源激活的集成反馈提供: (PurePath™ HD)

- 来自高清源的高频内容,信号带宽高达 80 kHz

- 超低功率 4Ω 负载时提供 1 W连续功率,总谐 波失真(THD)小于 0.03%

- 自然音响所有频率扁平总谐波失真(THD)

- 80dB PSRR (BTL, 无输入信号)

- >100dB (A 加权声级) SNR

- 启动和停止时无可闻杂音

- 与 TAS5630, TAS5615 和 TAS5611引脚兼容

- 在同一 **PCB**上的多重可选配置:

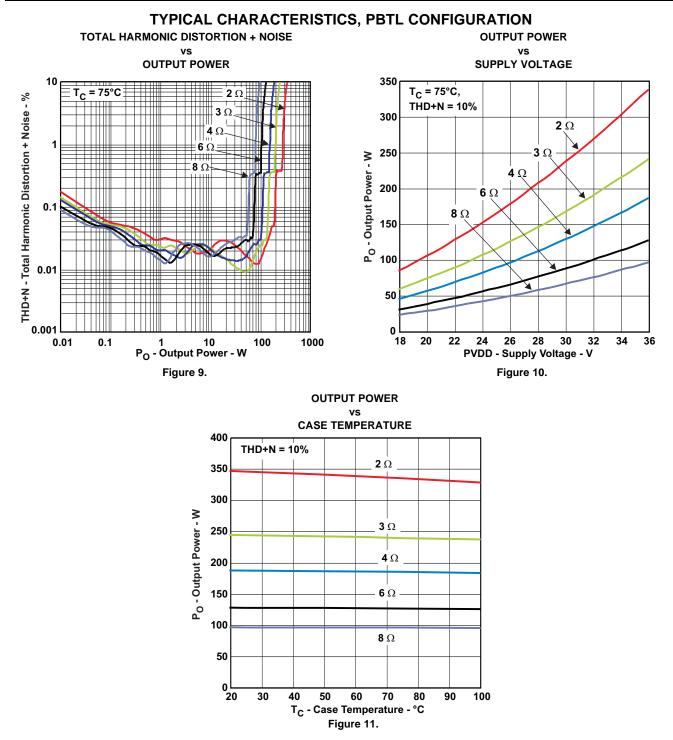

- 单声道并行桥式负载 (PBTL)

- 立体声桥式负载 (BTL)

- 2.1 单端 (SE) 立体声对和桥式负载低音炮

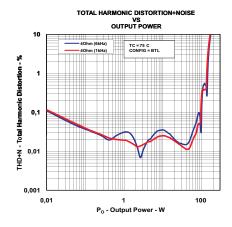

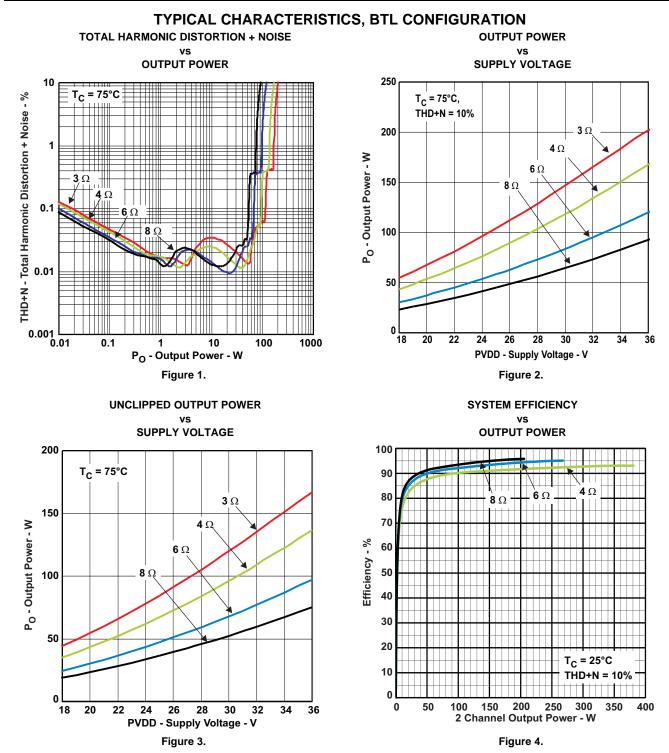

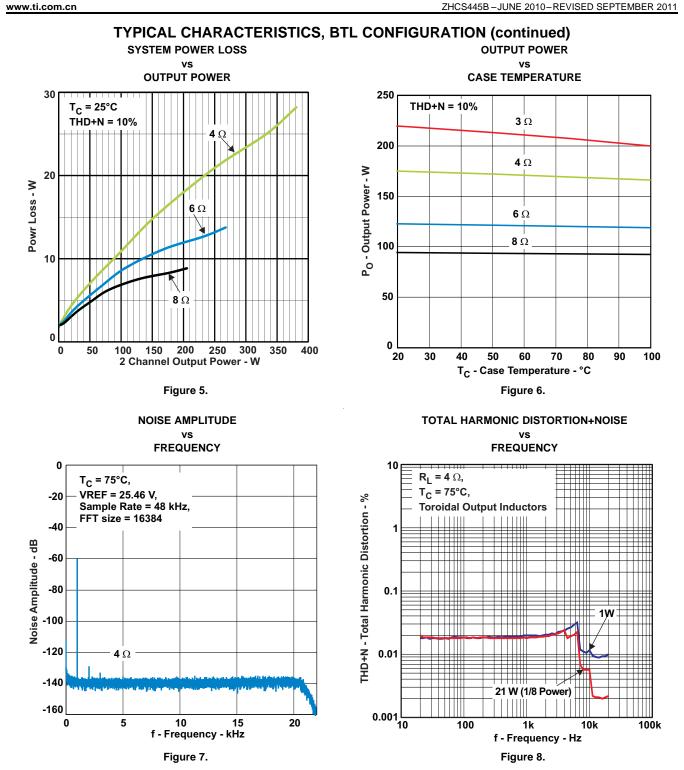

- 总谐波失真(THD)+噪音(N)小于 10%时的全部输出功率

- 在单声道 PBTL 配置时为 300 W

- 在立体声 BTL 配置中每通道的功率为 150 W

- 在立体声 BTL 配置中,全部输出功率的总谐波失 真(THD)+噪音(N)为1%

- 为 3 Ω 负载提供 160 W立体声功率

- 为 4 Ω 负载提供 125 W立体声功率

- 为 6 Ω 负载提供 85 W立体声功率

- 为8Ω负载提供65W立体声功率

- 具有 60-mΩ 输出 MOSFET的大于 90% 的有效功 率级

- 自我保护设计 (包括欠压、温度过高、削波和短路 保护) 并产生错误报告

- 符合 EMI(当与建议的系统设计配合使使用时)

- 耐热增强型封装选项:

- PHD (64-引脚 QFP)

- DKD (44-引脚 PSOP3)

# 应用范围

- 家庭影院系统

- **AV** 接收器

- DVD/ 蓝光光盘™ 接收器

- 迷你型/微型组合音响系统

- 有源扬声器和超低音扬声器

# 说明

TAS5613A是一款高性能模拟输入D类放大器,此放大器具有集成闭环反馈技术(即 PurePath™ HD)。 它的驱动能力高达150W。<sup>(1)</sup> 36 V 单电源供电时,4 Ω负载扬声器提供立体声输出。

PurePath<sup>™</sup> HD 技术实现了传统AB-放大器性能 (<0.03% THD) 水平同时提供了与传统D类放大器一样 的电源效率。

与传统的D类放大器不同,只有输出电平进入削波时, 失真曲线才增加。

**PurePath™ HD** 技术实现了更低的空闲损失,从而使得该设备效率更高。

#### (1) 输出功率水平依赖于目标应用的散热配置。在封装外露散热片 和散热器之间应该使用高性能热界面材料以获得高输出功率水 平。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. 蓝光光盘 is a trademark of Blu-ray Disc Association.

All other trademarks are the property of their respective owners.

# TAS5613A

TEXAS INSTRUMENTS

#### ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **DEVICE INFORMATION**

## **Pin Assignment**

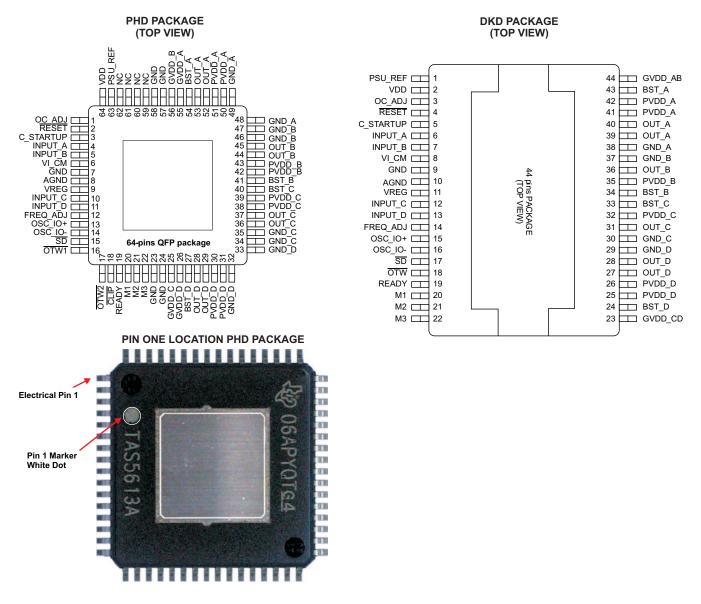

The TAS5613A is available in two thermally enhanced packages:

- 64-Pin QFP (PHD) Power Package

- 44-Pin PSOP3 Package (DKD)

The package type contains a heat slug that is located on the top side of the device for convenient thermal coupling to the heat sink.

ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

www.ti.com.cn

# MODE SELECTION PINS

| M  | MODE PINS |    | ANALOG OUTPUT                                 |                  | DESCRIPTION                 |                        |         |  |

|----|-----------|----|-----------------------------------------------|------------------|-----------------------------|------------------------|---------|--|

| M3 | M2        | M1 | INPUT                                         | CONFIGURATION    |                             | IPTION                 |         |  |

| 0  | 0         | 0  | Differential                                  | 2 × BTL          | AD mode                     | AD mode                |         |  |

| 0  | 0         | 1  | —                                             | —                | Reserved                    |                        |         |  |

| 0  | 1         | 0  | Differential                                  | 2 × BTL          | BD mode                     |                        |         |  |

| 0  | 1         | 1  | Differential<br>(BTL)<br>Single Ended<br>(SE) | 1 × BTL + 2 × SE | BTL = BD mode, SE = AD mode |                        |         |  |

| 1  | 0         | 0  | Single Ended                                  | 4 × SE           | AD mode                     |                        |         |  |

|    |           |    |                                               |                  | INPUT_C <sup>(1)</sup>      | INPUT_D <sup>(1)</sup> |         |  |

| 1  | 0         | 1  | Differential                                  | 1 × PBTL         | 0                           | 0                      | AD mode |  |

|    |           |    |                                               |                  | 1                           | 0                      | BD mode |  |

| 1  | 1         | 0  |                                               |                  |                             |                        |         |  |

| 1  | 1         | 1  |                                               | Reserved         |                             |                        |         |  |

(1) INPUT\_C and D are used to select between a subset of AD and BD mode operations in PBTL mode (1=VREG and 0=GND).

# PACKAGE HEAT DISSIPATION RATINGS (1)

| PARAMETER                                          | TAS5613APHD        | TAS5613ADKD        |

|----------------------------------------------------|--------------------|--------------------|

| $R_{\theta JC}$ (°C/W) – 2 BTL or 4 SE channels    | 3.2                | 2.1                |

| R <sub>0JC</sub> (°C/W) – 1 BTL or 2 SE channel(s) | 5.4                | 3.5                |

| R <sub>θJC</sub> (°C/W) – 1 SE channel             | 7.9                | 5.1                |

| Pad Area <sup>(2)</sup>                            | 64 mm <sup>2</sup> | 80 mm <sup>2</sup> |

(1)  $J_C$  is junction-to-case, CH is case-to-heat sink

(2) R<sub>0H</sub> is an important consideration. Assume a 2-mil thickness of typical thermal grease between the pad area and the heat sink and both channels active. The R<sub>0CH</sub> with this condition is 1.22°C/W for the PHD package and 1.02°C/W for the DKD package.

#### Table 1. ORDERING INFORMATION <sup>(1)</sup>

| T <sub>A</sub> PACKAGE |             | DESCRIPTION  |

|------------------------|-------------|--------------|

| 0°C–70°C               | TAS5613APHD | 64 pin HTQFP |

| 0 0-70 0               | TAS5613ADKD | 44 pin PSOP3 |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted <sup>(1)</sup>

|                                             | TAS5613A                                       |              | UNIT |

|---------------------------------------------|------------------------------------------------|--------------|------|

| VDD to GND                                  |                                                | -0.3 to 13.2 | V    |

| GVDD to GND                                 |                                                | -0.3 to 13.2 | V    |

| PVDD_X to GND_X <sup>(2)</sup>              |                                                | -0.3 to 53   | V    |

| OUT_X to GND_X <sup>(2)</sup>               |                                                | -0.3 to 53   | V    |

| BST_X to GND_X <sup>(2)</sup>               |                                                | -0.3 to 66.2 | V    |

| BST_X to GVDD_X <sup>(2)</sup>              |                                                | -0.3 to 53   | V    |

| VREG to GND                                 |                                                | -0.3 to 4.2  | V    |

| GND_X to GND                                |                                                | -0.3 to 0.3  | V    |

| GND to AGND                                 |                                                | -0.3 to 0.3  | V    |

| OC_ADJ, M1, M2, M3, OSC_IO+, PSU_REF to GND | OSC_IO-, FREQ_ADJ, VI_CM, C_STARTUP,           | -0.3 to 4.2  | V    |

| INPUT_X                                     |                                                | –0.3 to 7    | V    |

| RESET, SD, OTW, OTW1, OTW2,                 | CLIP, READY to GND                             | –0.3 to 7    | V    |

| Continuous sink current (SD, OTW            | , OTW1, OTW2, CLIP, READY)                     | 9            | mA   |

| Operating junction temperature ran          | 0 to 150                                       | °C           |      |

| Storage temperature, T <sub>stg</sub>       | -40 to 150                                     | °C           |      |

| Electrostatio disobarga                     | Human-Body Model <sup>(3)</sup> (all pins)     | ±2           | kV   |

| Electrostatic discharge                     | Charged-Device Model <sup>(3)</sup> (all pins) | ±500         | V    |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) These voltages represents the DC voltage + peak AC waveform measured at the terminal of the device in all conditions.

(3) Failure to follow good anti-static ESD handling during manufacture and rework will contribute to device malfunction. Make sure the operators handling the device are adequately grounded through the use of ground straps or alternative ESD protection.

ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

#### www.ti.com.cn

# **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                         |                                                                                |                                                                       | MIN  | TYP | MAX  | UNIT |  |

|-------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|-----|------|------|--|

| PVDD_x                  | Half-bridge supply                                                             | DC supply voltage                                                     | 18   | 36  | 38   | V    |  |

| GVDD_x                  | Supply for logic regulators and gate-drive circuitry                           | DC supply voltage                                                     | 10.8 | 12  | 13.2 | V    |  |

| VDD                     | Digital regulator supply voltage                                               | DC supply voltage                                                     | 10.8 | 12  | 13.2 | V    |  |

| R <sub>L</sub> (BTL)    |                                                                                |                                                                       | 3.5  | 4   |      |      |  |

| R <sub>L</sub> (SE)     | Load impedance                                                                 | Output filter according to Figure 12 and Figure 13                    | 2.8  | 3   |      | Ω    |  |

| R <sub>L</sub> (PBTL)   |                                                                                |                                                                       | 1.6  | 2   |      |      |  |

| R <sub>L</sub> (BTL)    | Load impedance                                                                 | Output filter according to Figure 12 + Schottky, $R_{OC} = 22k\Omega$ | 2.8  | 3   |      | Ω    |  |

| L <sub>OUT</sub> (BTL)  |                                                                                |                                                                       | 7    | 10  |      | μH   |  |

| L <sub>OUT</sub> (SE)   | Output filter inductance                                                       | Minimum output inductance at I <sub>OC</sub>                          | 7    | 15  |      |      |  |

| L <sub>OUT</sub> (PBTL) |                                                                                |                                                                       | 7    | 10  |      |      |  |

|                         | PWM frame rate selectable for AM interference avoidance; 1% Resistor tolerance | Nominal                                                               | 385  | 400 | 415  | kHz  |  |

| F <sub>PWM</sub>        |                                                                                | AM1                                                                   | 315  | 333 | 350  |      |  |

|                         |                                                                                | AM2                                                                   | 260  | 300 | 335  |      |  |

|                         | PWM frame rate programming resistor                                            | Nominal; Master mode                                                  | 9.9  | 10  | 10.1 | kΩ   |  |

| R <sub>FREQ_ADJ</sub>   |                                                                                | AM1; Master mode                                                      | 19.8 | 20  | 20.2 |      |  |

|                         |                                                                                | AM2; Master mode                                                      | 29.7 | 30  | 30.3 | 1    |  |

| C <sub>PVDD</sub>       | PVDD close decoupling capacitors                                               |                                                                       |      | 2.0 |      | μF   |  |

| R <sub>OC</sub>         | Over-current programming resistor                                              | Resistor tolerance = 5%                                               | 22   | 30  |      | kΩ   |  |

| R <sub>OC_LATCHED</sub> | Over-current programming resistor                                              | Resistor tolerance = 5%                                               | 47   | 64  |      | kΩ   |  |

| V <sub>FREQ_ADJ</sub>   | Voltage on FREQ_ADJ pin for<br>slave mode operation                            | Slave mode                                                            |      | 3.3 |      | V    |  |

| TJ                      | Junction temperature                                                           |                                                                       | 0    |     | 125  | °C   |  |

# **PIN FUNCTIONS**

| PIN       |                      |         | FUNCTION <sup>(1)</sup> | DECODIDION                                                                |

|-----------|----------------------|---------|-------------------------|---------------------------------------------------------------------------|

| NAME      | PHD NO.              | DKD NO. | FUNCTION                | DESCRIPTION                                                               |

| AGND      | 8                    | 10      | Р                       | Analog ground                                                             |

| BST_A     | 54                   | 43      | Р                       | HS bootstrap supply (BST), external 0.033 µF capacitor to OUT_A required. |

| BST_B     | 41                   | 34      | Р                       | HS bootstrap supply (BST), external 0.033 µF capacitor to OUT_B required. |

| BST_C     | 40                   | 33      | Р                       | HS bootstrap supply (BST), external 0.033 µF capacitor to OUT_C required. |

| BST_D     | 27                   | 24      | Р                       | HS bootstrap supply (BST), external 0.033 µF capacitor to OUT_D required. |

| CLIP      | 18                   | -       | 0                       | Clipping warning; open drain; active low                                  |

| C_STARTUP | 3                    | 5       | 0                       | Startup ramp requires a charging capacitor of 4.7nF to GND                |

| FREQ_ADJ  | 12                   | 14      | Ι                       | PWM frame rate programming pin requires resistor to GND                   |

| GND       | 7, 23, 24,<br>57, 58 | 9       | Р                       | Ground                                                                    |

| GND_A     | 48, 49               | 38      | Р                       | Power ground for half-bridge A                                            |

| GND_B     | 46, 47               | 37      | Р                       | Power ground for half-bridge B                                            |

| GND_C     | 34, 35               | 30      | Р                       | Power ground for half-bridge C                                            |

| GND_D     | 32, 33               | 29      | Р                       | Power ground for half-bridge D                                            |

| GVDD_A    | 55                   | -       | Р                       | Gate drive voltage supply requires 0.1 µF capacitor to GND_A              |

| GVDD_B    | 56                   | -       | Р                       | Gate drive voltage supply requires 0.1 µF capacitor to GND_B              |

| GVDD_C    | 25                   | -       | Р                       | Gate drive voltage supply requires 0.1 µF capacitor to GND_C              |

| GVDD_D    | 26                   | -       | Р                       | Gate drive voltage supply requires 0.1 uF capacitor to GND_D              |

| GVDD_AB   | -                    | 44      | Р                       | Gate drive voltage supply requires 0.22 µF capacitor to GND_A/GND_B       |

| GVDD_CD   | -                    | 23      | Р                       | Gate drive voltage supply requires 0.22 µF capacitor to GND_C/GND_D       |

(1) I = Input, O = Output, P = Power

# PIN FUNCTIONS (continued)

| PIN     |         |         | FUNCTION <sup>(1)</sup> | DECODIDION                                                                                                                        |  |  |

|---------|---------|---------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | PHD NO. | DKD NO. | FUNCTION                | DESCRIPTION                                                                                                                       |  |  |

| INPUT_A | 4       | 6       | I                       | Input signal for half bridge A                                                                                                    |  |  |

| INPUT_B | 5       | 7       | I                       | Input signal for half bridge B                                                                                                    |  |  |

| INPUT_C | 10      | 12      | I                       | Input signal for half bridge C                                                                                                    |  |  |

| INPUT_D | 11      | 13      | I                       | Input signal for half bridge D                                                                                                    |  |  |

| M1      | 20      | 20      | I                       | Mode selection                                                                                                                    |  |  |

| M2      | 21      | 21      | I                       | Mode selection                                                                                                                    |  |  |

| М3      | 22      | 22      | I                       | Mode selection                                                                                                                    |  |  |

| NC      | 59-62   | -       | -                       | No connect, pins may be grounded.                                                                                                 |  |  |

| OC_ADJ  | 1       | 3       | 0                       | Analog over current programming pin requires 30kΩ resistor to ground:                                                             |  |  |

| OSC_IO+ | 13      | 15      | I/O                     | Oscillator master/slave output/input.                                                                                             |  |  |

| OSC_IO- | 14      | 16      | I/O                     | Oscillator master/slave output/input.                                                                                             |  |  |

| /OTW    | -       | 18      | 0                       | Overtemperature warning signal, open drain, active low.                                                                           |  |  |

| OTW1    | 16      | -       | 0                       | Overtemperature warning signal, open drain, active low.                                                                           |  |  |

| OTW2    | 17      | -       | 0                       | Overtemperature warning signal, open drain, active low.                                                                           |  |  |

| OUT_A   | 52, 53  | 39, 40  | 0                       | Output, half bridge A                                                                                                             |  |  |

| OUT_B   | 44, 45  | 36      | 0                       | Output, half bridge B                                                                                                             |  |  |

| OUT_C   | 36, 37  | 31      | 0                       | Output, half bridge C                                                                                                             |  |  |

| OUT_D   | 28, 29  | 27, 28  | 0                       | Output, half bridge D                                                                                                             |  |  |

| PSU_REF | 63      | 1       | Р                       | PSU Reference requires close decoupling of 330pF to GND                                                                           |  |  |

| PVDD_A  | 50, 51  | 41, 42  | Р                       | Power supply input for half bridges A requires close decoupling of 2µF capacitor to GND_A.                                        |  |  |

| PVDD_B  | 42, 43  | 35      | Р                       | Power supply input for half bridges B requires close decoupling of 2µF capacitor to GND_B.                                        |  |  |

| PVDD_C  | 38, 39  | 32      | Р                       | Power supply input for half bridges C requires close decoupling of 2µF capacitor to GND_C.                                        |  |  |

| PVDD_D  | 30, 31  | 25, 26  | Р                       | Power supply input for half bridges D requires close decoupling of 2µF capacitor to GND_D.                                        |  |  |

| READY   | 19      | 19      | 0                       | Normal operation; open drain; active high                                                                                         |  |  |

| RESET   | 2       | 4       | I                       | Device reset Input; active low, requires 47kΩ pull up resistor to VREG                                                            |  |  |

| SD      | 15      | 17      | 0                       | Shutdown signal, open drain, active low                                                                                           |  |  |

| VDD     | 64      | 2       | Р                       | Power supply for internal voltage regulator requires a 10- $\mu$ F capacitor with a 0.1- $\mu$ F capacitor to GND for decoupling. |  |  |

| VI_CM   | 6       | 8       | 0                       | Analog comparator reference node requires close decoupling of 1nF to GND                                                          |  |  |

| VREG    | 9       | 11      | Р                       | Internal regulator supply filter pin requires 0.1-µF capacitor to GND                                                             |  |  |

TEXAS INSTRUMENTS

www.ti.com.cn

ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

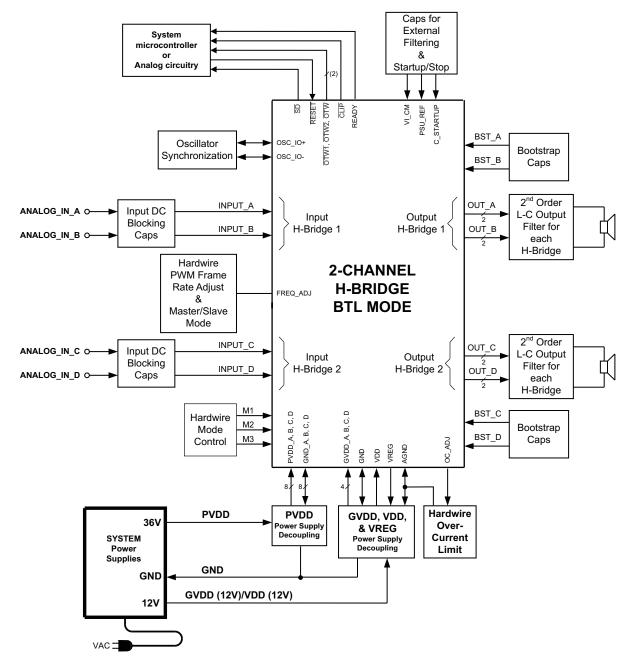

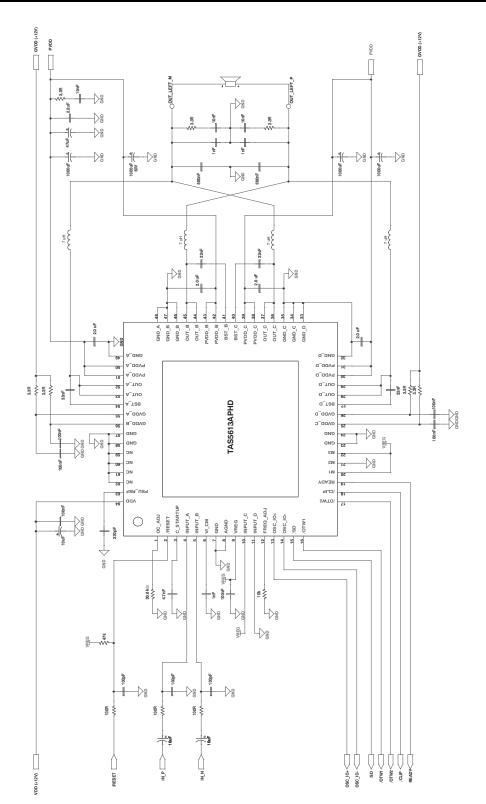

# **TYPICAL SYSTEM BLOCK DIAGRAM**

INSTRUMENTS

**Texas**

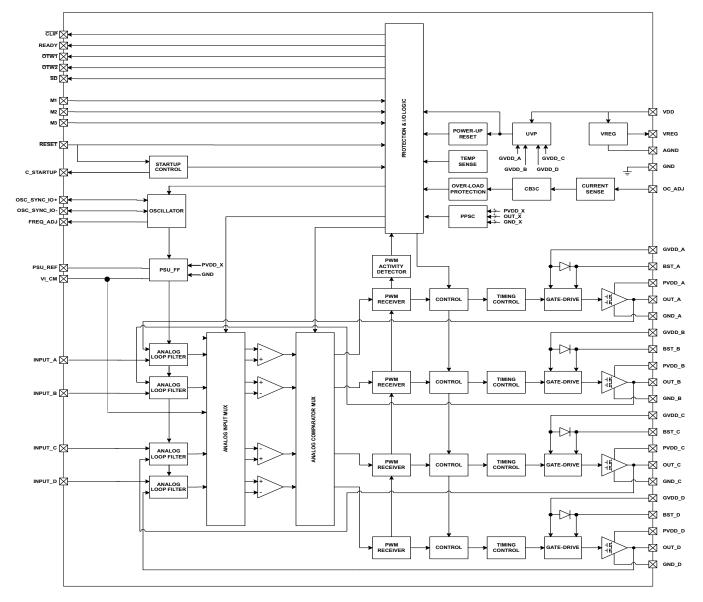

# FUNCTIONAL BLOCK DIAGRAM

ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

www.ti.com.cn

# **AUDIO CHARACTERISTICS (BTL)**

PCB and system configuration are in accordance with recommended guidelines. Audio frequency = 1kHz, PVDD\_X = 36V, GVDD\_X = 12V, R<sub>L</sub> = 4 $\Omega$ , f<sub>S</sub> = 400kHz, R<sub>OC</sub> = 30k $\Omega$ , T<sub>C</sub> = 75°C, Output Filter: L<sub>DEM</sub> = 7 $\mu$ H, C<sub>DEM</sub> = 680nF, mode = 010, unless otherwise noted.

|                   | PARAMETER                                                   | TEST CONDITIONS                                                                                  | MIN TYP I | MAX | UNIT |

|-------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------|-----|------|

|                   |                                                             | $R_L = 3\Omega$ , 10% THD+N ( $R_{OC} = 22k\Omega$ , add<br>Schottky diodes from OUT_X to GND_X) | 200       |     |      |

| <b>D</b>          |                                                             | $R_L = 4\Omega$ , 10% THD+N                                                                      | 150       |     | 14/  |

| Po                | Power output per channel                                    | $R_L = 3\Omega$ , 1% THD+N ( $R_{OC} = 22k\Omega$ , add<br>Schottky diodes from OUT_X to GND_X)  | 160       |     | W    |

|                   |                                                             | $R_L = 4\Omega$ , 1% THD+N                                                                       | 125       |     |      |

| THD+N             | Total harmonic distortion + noise                           | 1 W                                                                                              | 0.03%     |     |      |

| V <sub>n</sub>    | Output integrated noise                                     | A-weighted, AES17 filter, Input Capacitor<br>Grounded                                            | 185       |     | μV   |

| V <sub>OS</sub>   | Output offset voltage                                       | Inputs AC coupled to GND                                                                         | 8         | 25  | mV   |

| SNR               | Signal-to-noise ratio <sup>(1)</sup>                        |                                                                                                  | 100       |     | dB   |

| DNR               | Dynamic range                                               |                                                                                                  | 100       |     | dB   |

| P <sub>idle</sub> | Power dissipation due to Idle losses (I <sub>PVDD_X</sub> ) | $P_0 = 0, 4$ channels switching <sup>(2)</sup>                                                   | 1.8       |     | W    |

(1) SNR is calculated relative to 1% THD+N output level.

(2) Actual system idle losses also are affected by core losses of output inductors.

# **AUDIO CHARACTERISTICS (PBTL)**

PCB and system configuration are in accordance with recommended guidelines. Audio frequency = 1kHz, PVDD\_X = 36V, GVDD\_X = 12V, R<sub>L</sub> =  $2\Omega$ , f<sub>S</sub> = 400 kHz, R<sub>OC</sub> =  $30k\Omega$ , T<sub>C</sub> =  $75^{\circ}$ C, Output Filter: L<sub>DEM</sub> =  $7\mu$ H, C<sub>DEM</sub> = 680nF, MODE = 101-BD, unless otherwise noted.

|                   | PARAMETER                                      | TEST CONDITIONS                                | MIN TYP MAX | UNIT |  |

|-------------------|------------------------------------------------|------------------------------------------------|-------------|------|--|

|                   |                                                | R <sub>L</sub> = 2Ω, 10% THD+N                 |             |      |  |

|                   |                                                | $R_L = 3\Omega$ , 10% THD+N                    | 200         |      |  |

| D                 | Dewer eutput ner ehennel                       | $R_L = 4\Omega$ , 10% THD+N                    | 160         | w    |  |

| Po                | Power output per channel                       | R <sub>L</sub> = 2Ω, 1% THD+N                  | 250         | vv   |  |

|                   |                                                | R <sub>L</sub> = 3Ω, 1% THD+N                  | 160         |      |  |

|                   |                                                | R <sub>L</sub> = 4Ω, 1% THD+N                  | 130         |      |  |

| THD+N             | Total harmonic distortion + noise              | 1 W                                            | 0.05%       |      |  |

| V <sub>n</sub>    | Output integrated noise                        | A-weighted                                     | 182         | μV   |  |

| SNR               | Signal to noise ratio <sup>(1)</sup>           | A-weighted                                     | 100         | dB   |  |

| DNR               | Dynamic range                                  | A-weighted                                     | 100         | dB   |  |

| P <sub>idle</sub> | Power dissipation due to idle losses (IPVDD_X) | $P_O = 0, 4$ channels switching <sup>(2)</sup> | 1.8         | W    |  |

(1) SNR is calculated relative to 1% THD+N output level.

(2) Actual system idle losses are affected by core losses of output inductors.

# **ELECTRICAL CHARACTERISTICS**

$\label{eq:pvdd_x} PVDD_X = 36V, \ GVDD_X = 12V, \ VDD = 12V, \ T_C \ (Case \ temperature) = 75^\circ C, \ f_S = 400 \ kHz, \ unless \ otherwise \ specified.$

|                                      | PARAMETER                                                                             | TEST CONDITIONS                                                                                                               | MIN  | TYP  | MAX  | UNIT |

|--------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| INTERNAL VOLTA                       | GE REGULATOR AND CURRENT CONSUMPTI                                                    | ON                                                                                                                            |      |      |      |      |

| VREG                                 | Voltage regulator, only used as reference node                                        | VDD = 12V                                                                                                                     | 3    | 3.3  | 3.6  | V    |

|                                      | Analog comparator reference node, VI_CM                                               |                                                                                                                               | 1.5  | 1.75 | 1.9  | V    |

| 1                                    |                                                                                       | Operating, 50% duty cycle                                                                                                     |      | 20   |      | 4    |

| I <sub>VDD</sub>                     | VDD supply current                                                                    | Idle, reset mode                                                                                                              |      | 20   |      | mA   |

|                                      |                                                                                       | 50% duty cycle                                                                                                                |      | 10   |      |      |

| I <sub>GVDD_x</sub>                  | Gate-supply current per half-bridge                                                   | Reset mode                                                                                                                    |      | 1.5  |      | mA   |

|                                      |                                                                                       | 50% duty cycle with recommended output filter                                                                                 |      | 12.5 |      | mA   |

| I <sub>PVDD_x</sub>                  | Half-bridge idle current                                                              | Reset mode, No switching                                                                                                      |      | 620  |      | μA   |

| ANALOG INPUTS                        |                                                                                       |                                                                                                                               | 1    |      |      |      |

| R <sub>IN</sub>                      | Input resistance                                                                      | READY = HIGH                                                                                                                  |      | 33   |      | kΩ   |

| V <sub>IN</sub>                      | Maximum input voltage swing                                                           |                                                                                                                               |      | 7    |      | V    |

| I <sub>IN</sub>                      | Maximum input current                                                                 |                                                                                                                               |      |      | 1    | mA   |

| G                                    | Inverting voltage Gain, (V <sub>OUT</sub> /V <sub>IN</sub> )                          |                                                                                                                               |      | 21   |      | dB   |

| OSCILLATOR                           |                                                                                       |                                                                                                                               |      |      |      |      |

|                                      | Nominal, Master Mode                                                                  |                                                                                                                               | 3.85 | 4    | 4.15 |      |

| f <sub>OSC_IO+</sub>                 | AM1, Master Mode                                                                      | F <sub>PWM</sub> × 10                                                                                                         | 3.15 | 3.33 | 3.5  | MHz  |

|                                      | AM2, Master Mode                                                                      | 1                                                                                                                             | 2.6  | 3    | 3.35 |      |

| V <sub>IH</sub>                      | High level input voltage                                                              |                                                                                                                               | 1.86 |      |      | V    |

| V <sub>IL</sub>                      | Low level input voltage                                                               |                                                                                                                               |      |      | 1.45 | V    |

| OUTPUT-STAGE N                       |                                                                                       |                                                                                                                               |      |      | -    |      |

|                                      | Drain-to-source resistance, low side (LS)                                             | $T_{I} = 25^{\circ}C$ , Includes metallization resistance,                                                                    |      | 60   | 100  | mΩ   |

| R <sub>DS(on)</sub>                  | Drain-to-source resistance, high side (HS)                                            | GVDD = 12V                                                                                                                    |      | 60   | 100  | mΩ   |

| I/O PROTECTION                       |                                                                                       |                                                                                                                               |      |      |      |      |

| NOT ROLLOHON                         | Undervoltage protection limit, GVDD_x and                                             |                                                                                                                               |      |      |      |      |

| V <sub>uvp,G</sub>                   | VDD                                                                                   |                                                                                                                               |      | 9.5  |      | V    |

| V <sub>uvp,hyst</sub> <sup>(1)</sup> |                                                                                       |                                                                                                                               |      | 0.6  |      | V    |

|                                      | Overtemperature warning 1, OTW1 <sup>(1)</sup>                                        |                                                                                                                               | 95   | 100  | 105  | °C   |

| OTW                                  | Overtemperature warning 2, OTW, OTW2 <sup>(1)</sup>                                   |                                                                                                                               | 115  | 125  | 135  | °C   |

| OTW <sub>HYST</sub> <sup>(1)</sup>   | Temperature drop needed below OTW temperature for OTW to be inactive after OTW event. |                                                                                                                               |      | 25   |      | °C   |

| OTE <sup>(1)</sup>                   | Overtemperature error                                                                 |                                                                                                                               | 145  | 155  | 165  | °C   |

| OTE-OTW <sub>differential</sub>      | OTE-OTW differential                                                                  |                                                                                                                               |      | 30   |      | °C   |

| OTE <sub>HYST</sub> <sup>(1)</sup>   | A reset needs to occur for $\overline{SD}$ to be released following an OTE event      |                                                                                                                               |      | 25   |      | °C   |

| OLPC                                 | Overload protection counter                                                           | f <sub>PWM</sub> = 400kHz                                                                                                     |      | 2.6  |      | ms   |

|                                      | O comment l'actionation d'                                                            | Resistor – programmable, nominal peak current in 1 $\Omega$ load, $R_{OCP}$ = 30k $\Omega$                                    |      | 14   |      |      |

| l <sub>oc</sub>                      | Overcurrent limit protection                                                          | Resistor – programmable, nominal peak current in $1\Omega$ load, $R_{OCP} = 22k\Omega$ (with Schottky diodes on output nodes) | 18   |      |      | A    |

|                                      |                                                                                       | Resistor – programmable, peak current in 1 $\Omega$ load, $R_{OCP}$ = 64k $\Omega$                                            | 14   |      |      |      |

| I <sub>OC_LATCHED</sub>              | Overcurrent limit protection                                                          | Resistor – programmable, nominal peak current in $1\Omega$ load, $R_{OCP} = 47k\Omega$ (with Schottky diodes on output nodes) |      |      | A    |      |

| I <sub>OCT</sub>                     | Overcurrent response time                                                             | Time from switching transition to flip-state induced by overcurrent.                                                          |      | 150  |      | ns   |

| I <sub>PD</sub>                      | Output pulldown current of each half                                                  | Connected when RESET is active to provide bootstrap charge. Not used in SE mode.                                              |      | 3    |      | mA   |

(1) Specified by design.

TAS5613A

www.ti.com.cn

#### ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

# **ELECTRICAL CHARACTERISTICS (continued)**

$\mathsf{PVDD}_X = 36\mathsf{V}, \ \mathsf{GVDD}_X = 12\mathsf{V}, \ \mathsf{VDD} = 12\mathsf{V}, \ \mathsf{T}_\mathsf{C} \ (\mathsf{Case \ temperature}) = 75^\circ\mathsf{C}, \ \mathsf{f}_\mathsf{S} = 400\mathsf{kHz}, \ \mathsf{unless \ otherwise \ specified}.$

|                     | PARAMETER                                                             | TEST CONDITIONS                       | MIN | TYP | MAX | UNIT    |

|---------------------|-----------------------------------------------------------------------|---------------------------------------|-----|-----|-----|---------|

| STATIC DIGIT        | AL SPECIFICATIONS                                                     |                                       |     |     |     |         |

| V <sub>IH</sub>     | High level input voltage                                              |                                       | 1.9 |     |     | V       |

| V <sub>IL</sub>     | Low level input voltage                                               | INPUT_X, MT, MZ, M3, RESET            |     |     | 0.8 | V       |

| Leakage             | Input leakage current                                                 |                                       |     |     | 100 | μA      |

| OTW/SHUTDO          | DWN (SD)                                                              |                                       |     |     |     |         |

| R <sub>INT_PU</sub> | Internal pullup resistance, OTW1 to VREG,<br>OTW2 to VREG, SD to VREG |                                       | 20  | 26  | 32  | kΩ      |

|                     |                                                                       | Internal pullup resistor              | 3   | 3.3 | 3.6 | N       |

| V <sub>OH</sub>     | High level output voltage                                             | External pullup of $4.7k\Omega$ to 5V | 4.5 |     | 5   | V       |

| V <sub>OL</sub>     | Low level output voltage                                              | I <sub>O</sub> = 4 mA                 |     | 200 | 500 | mV      |

| FANOUT              | Device fanout OTW1, OTW2, SD, CLIP, READY                             | No external pullup                    |     | 30  |     | devices |

TEXAS INSTRUMENTS

www.ti.com.cn

ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

TEXAS INSTRUMENTS

www.ti.com.cn

# **APPLICATION INFORMATION**

#### PCB MATERIAL RECOMMENDATION

FR-4 Glass Epoxy material with 2 oz. (70µm) is recommended for use with the TAS5613A. The use of this material can provide for higher power output, improved thermal performance, and better EMI margin (due to lower PCB trace inductance.

#### **PVDD CAPACITOR RECOMMENDATION**

The large capacitors used in conjunction with each full-bridge, are referred to as the PVDD Capacitors. These capacitors should be selected for proper voltage margin and adequate capacitance to support the power requirements. In practice, with a well designed system power supply, 1000  $\mu$ F, 50V will support more applications. The PVDD capacitors should be low ESR type because they are used in a circuit associated with high-speed switching.

#### **DECOUPLING CAPACITOR RECOMMENDATIONS**

In order to design an amplifier that has robust performance, passes regulatory requirements, and exhibits good audio performance, good quality decoupling capacitors should be used. In practice, X7R should be used in this application.

The voltage of the decoupling capacitors should be selected in accordance with good design practices. Temperature, ripple current, and voltage overshoot must be considered. This fact is particularly true in the selection of the 2µF that is placed on the power supply to each half-bridge. It must withstand the voltage overshoot of the PWM switching, the heat generated by the amplifier during high power output, and the ripple current created by high power output. A minimum voltage rating of 50V is required for use with a 36V power supply.

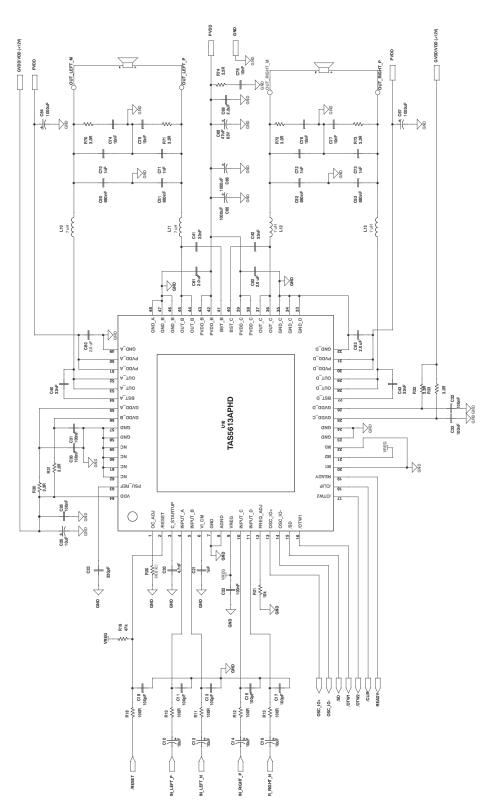

#### SYSTEM DESIGN RECOMMENDATIONS

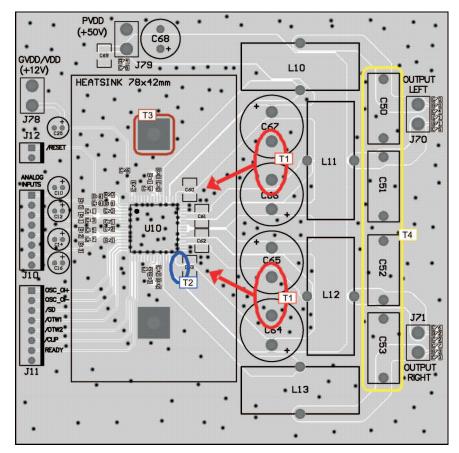

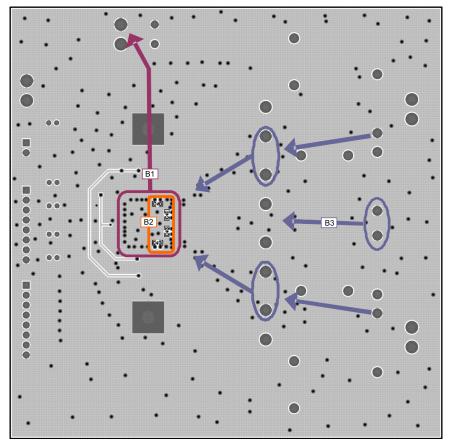

The following schematics and PCB layouts illustrate best practices in the use of the TAS5613A.

ZHCS445B – JUNE 2010 – REVISED SEPTEMBER 2011

www.ti.com.cn

Figure 12. Typical Differential Input BTL Application With BD Modulation Filters

Instruments

Texas

www.ti.com.cn

Figure 13. Typical Differential (2N) PBTL Application With BD Modulation Filters

ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

www.ti.com.cn

# THEORY OF OPERATION

# **POWER SUPPLIES**

To facilitate system design, the TAS5613A needs only a 12V supply in addition to the (typical) 36V power-stage supply. An internal voltage regulator provides suitable voltage levels for the digital and low-voltage analog circuitry. Additionally, all circuitry requiring a floating voltage supply, e.g., the high-side gate drive, is accommodated by built-in bootstrap circuitry requiring only an external capacitor for each half-bridge.

In order to provide outstanding electrical and acoustical characteristics, the PWM signal path including gate drive and output stage is designed as identical, independent half-bridges. For this reason, each half-bridge has separate bootstrap pins (BST\_X), and power-stage supply pins (PVDD\_X). Gate drive supply (GVDD\_X) is separate for each half bridge for the PHD package and separate per full bridge for the DKD package. Furthermore, an additional pin (VDD) is provided as supply for all common circuits. Although supplied from the same 12V source, separating to GVDD\_A, GVDD\_B, GVDD\_C, GVDD\_D, and VDD on the printed-circuit board (PCB) by RC filters (see application diagram for details) is recommended. These RC filters provide the recommended high-frequency isolation. Special attention should be paid to placing all decoupling capacitors as close to their associated pins as possible. In general, inductance between the power supply pins and decoupling capacitors must be avoided. (See reference board documentation for additional information.)

For a properly functioning bootstrap circuit, a small ceramic capacitor must be connected from each bootstrap pin (BST\_X) to the power-stage output pin (OUT\_X). When the power-stage output is low, the bootstrap capacitor is charged through an internal diode connected between the gate-drive power-supply pin (GVDD\_X) and the bootstrap pins. When the power-stage output is high, the bootstrap capacitor potential is shifted above the output potential and thus provides a suitable voltage supply for the high-side gate driver. In an application with PWM switching frequencies in the range from 300kHz to 400kHz, it is recommended to use 33nF ceramic capacitors, size 0603 or 0805, for the bootstrap supply. These 33nF capacitors ensure sufficient energy storage, even during minimal PWM duty cycles, to keep the high-side power stage FET (LDMOS) fully turned on during the remaining part of the PWM cycle.

Special attention should be paid to the power-stage power supply; this includes component selection, PCB placement, and routing. As indicated, each half-bridge has independent power-stage supply pins (PVDD\_X). For optimal electrical performance, EMI compliance, and system reliability, it is important that each PVDD\_X pin is decoupled with a 2-µF ceramic capacitor placed as close as possible to each supply pin. It is recommended to follow the PCB layout of the TAS5613A reference design. For additional information on recommended power supply and required components, see the application diagrams in this data sheet.

The 12V supply should be from a low-noise, low-output-impedance voltage regulator. Likewise, the 36V power-stage supply is assumed to have low output impedance and low noise. The power-supply sequence is not critical as facilitated by the internal power-on-reset circuit. Moreover, the TAS5613A is fully protected against erroneous power-stage turn on due to parasitic gate charging. Thus, voltage-supply ramp rates (dV/dt) are non-critical within the specified range (see the Recommended Operating Conditions table of this data sheet).

#### SYSTEM POWER-UP/POWER-DOWN SEQUENCE

#### Powering Up

The TAS5613A does not require a power-up sequence. The outputs of the H-bridges remain in a high-impedance state until the gate-drive supply voltage (GVDD\_X) and VDD voltage are above the undervoltage protection (UVP) voltage threshold (see the <u>Electrical</u> Characteristics table of this data sheet). Although not specifically required, it is recommended to hold RESET in a low state while powering up the device. This allows an internal circuit to charge the external bootstrap capacitors by enabling a weak pulldown of the half-bridge output.

#### Powering Down

The TAS5613A does not require a power-down sequence. The device remains fully operational as long as the gate-drive supply (GVDD\_X) voltage and VDD voltage are above the undervoltage protection (UVP) voltage threshold (see the Electrical Characteristics table of this data sheet). Although not specifically required, it is a good practice to hold RESET low during power down, thus preventing audible artifacts including pops or clicks.

#### **ERROR REPORTING**

The SD, OTW, OTW1 and OTW2 pins are active-low, open-drain outputs. The function is for protection-mode signaling to a PWM controller or other system-control device.

Any fault resulting in device shutdown is signaled by the  $\overline{SD}$  pin going low. Also,  $\overline{OTW}$  and  $\overline{OTW2}$  go low when the device junction temperature exceeds 125°C, and  $\overline{OTW1}$  goes low when the junction temperature exceeds 100°C (see Table 2).

| SD | OTW1 | <u> </u> | DESCRIPTION                                                                                                                    |

|----|------|----------|--------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0    | 0        | Overtemperature (OTE) or overload (OLP) or undervoltage (UVP) Junction temperature higher than 125°C (overtemperature warning) |

| 0  | 0    | 1        | Overload (OLP) or undervoltage (UVP). Junction temperature higher than 100°C (overtemperature warning)                         |

| 0  | 1    | 1        | Overload (OLP) or undervoltage (UVP). Junction temperature lower than 100°C                                                    |

| 1  | 0    | 0        | Junction temperature higher than 125°C (overtemperature warning)                                                               |

| 1  | 0    | 1        | Junction temperature higher than 100°C (overtemperature warning)                                                               |

| 1  | 1    | 1        | Junction temperature lower than 100°C and no OLP or UVP faults (normal operation)                                              |

#### Table 2. Error Reporting

Note that asserting either **RESET** low forces the SD signal high, independent of faults being present. TI recommends monitoring the OTW signal using the system microcontroller and responding to an overtemperature warning signal by, e.g., turning down the volume to prevent further heating of the device resulting in device shutdown (OTE).

To reduce external component count, an internal pullup resistor to 3.3V is provided on both  $\overline{SD}$  and  $\overline{OTW}$  outputs. Level compliance for 5V logic can be obtained by adding external pullup resistors to 5 V (see the Electrical Characteristics section of this data sheet for further specifications).

#### **DEVICE PROTECTION SYSTEM**

The TAS5613A contains advanced protection circuitry carefully designed to facilitate system integration and ease of use, as well as to safeguard the device from permanent failure due to a wide range of fault conditions such as short circuits, overload, overtemperature, and undervoltage. The TAS5613A responds to a fault by immediately setting the power stage in a high-impedance (Hi-Z) state and asserting the SD pin low. In situations other than overload and overtemperature error (OTE), the device automatically recovers when the fault condition has been removed, i.e., the supply voltage has increased.

The device will function on errors, as shown in Table 3.

| BTL               | MODE      | PBTL              | MODE      | SE                | MODE      |  |

|-------------------|-----------|-------------------|-----------|-------------------|-----------|--|

| LOCAL<br>ERROR IN | TURNS OFF | LOCAL<br>ERROR IN | TURNS OFF | LOCAL<br>ERROR IN | TURNS OFF |  |

| А                 | A : D     | А                 |           | А                 | A+B       |  |

| В                 | A+B       | В                 |           | В                 | A+D       |  |

| С                 |           | С                 | A+B+C+D   | С                 |           |  |

| D                 | C+D       | D                 |           | D                 | C+D       |  |

Bootstrap UVP does not shutdown according to the table, it shuts down the respective halfbridge (non-latching, does not assert SD).

#### **PIN-TO-PIN SHORT CIRCUIT PROTECTION (PPSC)**

The PPSC detection system protects the device from permanent damage in the case that a power output pin (OUT\_X) is shorted to GND\_X or PVDD\_X. For comparison, the OC protection system detects an overcurrent after the demodulation filter where PPSC detects shorts directly at the pin before the filter. PPSC detection is performed at startup i.e. when VDD is supplied, consequently a short to either GND\_X or PVDD\_X after system startup will not activate the PPSC detection system. When PPSC detection is activated by a short on the output, all half bridges are kept in a Hi-Z state until the short is removed, the device then continues the startup sequence

#### ZHCS445B-JUNE 2010-REVISED SEPTEMBER 2011

www.ti.com.cn

and starts switching. The detection is controlled globally by a two step sequence. The first step ensures that there are no shorts from OUT\_X to GND\_X, the second step tests that there are no shorts from OUT\_X to PVDD\_X. The total duration of this process is roughly proportional to the capacitance of the output LC filter. The typical duration is < 15ms/µF. While the PPSC detection is in progress, SD is kept low, and the device will not react to changes applied to the RESET pins. If no shorts are present the PPSC detection passes, and SD is released. A device reset will not start a new PPSC detection. PPSC detection is enabled in BTL and PBTL output configurations, the detection is not performed in SE mode. To make sure not to trip the PPSC detection system it is recommended not to insert resistive load to GND\_X or PVDD\_X.

## OVERTEMPERATURE PROTECTION

#### PHD Package

The TAS5613A PHD package option has a three-level temperature-protection system that asserts an active-low warning signal (OTW1) when the device junction temperature exceeds 100°C (typical), (OTW2) when the device junction temperature exceeds 125°C (typical) and, if the device junction temperature exceeds 155°C (typical), the device is <u>put</u> into thermal shutdown, resulting in all half-bridge outputs being set in the high-impedance (Hi-Z) state and SD being asserted low. OTE is latched in this case. To clear the OTE latch, RESET must be asserted. Thereafter, the device resumes normal operation.

#### **DKD Package**

The TAS5613A <u>DKD</u> package option has a two-level temperature-protection system that asserts an active-low warning signal (OTW) when the device junction temperature exceeds 125°C (typical) and, if the device junction temperature exceeds 155°C (typical), the device is put into thermal shutdown, resulting in all half-bridge outputs being set in the high-impedance (Hi-Z) state and SD being asserted low. OTE is latched in this case. To clear the OTE latch, RESET must be asserted. Thereafter, the device resumes normal operation.

## UNDERVOLTAGE PROTECTION (UVP) AND POWER-ON RESET (POR)

The UVP and POR circuits of the TAS5613A fully protect the device in any power-up/down and brownout situation. While powering up, the POR circuit resets the overload circuit (OLP) and ensures that all circuits are fully operational when the GVDD\_X and VDD supply voltages reach stated in the Electrical Characteristics table. Although GVDD\_X and VDD are independently monitored, a supply voltage drop below the UVP threshold on any VDD or GVDD\_X pin results in all half-bridge outputs immediately being set in the high-impedance (Hi-Z) state and SD being asserted low. The device automatically resumes operation when all supply voltages have increased above the UVP threshold.

#### **DEVICE RESET**

When RESET is asserted low, all power-stage FETs in the four half-bridges are forced into a high-impedance (Hi-Z) state.

In BTL modes, to accommodate bootstrap charging prior to switching start, asserting the reset input low enables weak pulldown of the half-bridge outputs. In the SE mode, the output is forced into a high impedance state when asserting the reset input low.

Asserting reset input low removes any fault information to be signalled on the SD output, i.e., SD is forced high. A rising-edge transition on reset input allows the device to resume operation after an overload fault. To ensure thermal reliability, the rising edge of reset must occur no sooner than 4 ms after the falling edge of SD.

# SYSTEM DESIGN CONSIDERATION

A rising-edge transition on reset input allows the device to execute the startup sequence and starts switching.

Apply only audio when the state of READY is high that will start and stop the amplifier without having audible artifacts that is heard in the output transducers.

The CLIP signal is indicating that the output is approaching clipping. The signal can be used to either an audio volume decrease or intelligent power supply controlling a low and a high rail.

The device is inverting the audio signal from input to output.

The VREG pin is not recommended to be used as a voltage source for external circuitry.

The oscillator frequency can be trimmed by external control of the FREQ\_ADJ pin.

To reduce interference problems while using radio receiver tuned within the AM band, the switching frequency can be changed from nominal to lower values. These values should be chosen such that the nominal and the lower value switching frequencies together results in the fewest cases of interference throughout the AM band. can be selected by the value of the FREQ\_ADJ resistor connected to AGND in master mode.

For slave mode operation, turn of the oscillator by pulling the FREQ\_ADJ pin to VREG. This configures the OSC\_I/O pins as inputs and needs to be slaved from an external differential clock.

#### PRINTED CIRCUIT BOARD RECOMMENDATION

Use an unbroken ground plane to have good low impedance and inductance return path to the power supply for power and audio signals. PCB layout, audio performance and EMI are linked closely together. The circuit contains high fast switching currents; therefore, care must be taken to prevent damaging voltage spikes. Routing the audio input should be kept short and together with the accompanied audio source ground. A local ground area underneath the device is important to keep solid to minimize ground bounce.

Netlist for this printed circuit board is generated from the schematic in Figure 12.

**Note T1**: PVDD decoupling bulk capacitors C60-C64 should be as close as possible to the PVDD and GND\_X pins, the heat sink sets the distance. Wide traces should be routed on the top layer with direct connection to the pins and without going through vias. No vias or traces should be blocking the current path.

**Note T2**: Close decoupling of PVDD with low impedance X7R ceramic capacitors is placed under the heat sink and close to the pins.

Note T3: Heat sink needs to have a good connection to PCB ground.

Note T4: Output filter capacitors must be linear in the applied voltage range preferable metal film types.

#### Figure 14. Printed Circuit Board - Top Layer

**Note B1**: It is important to have a direct low impedance return path for high current back to the power supply. Keep impedance low from top to bottom side of PCB through a lot of ground vias.

**Note B2**: Bootstrap low impedance X7R ceramic capacitors placed on bottom side providing a short low inductance current loop.

Note B3: Return currents from bulk capacitors and output filter capacitors.

Figure 15. Printed Circuit Board - Bottom Layer

#### ZHCS445B – JUNE 2010 – REVISED SEPTEMBER 2011

# **REVISION HISTORY**

| Cł | nanges from Original (June 2010) to Revision A P                                                       | anges from Original (June 2010) to Revision A Page |  |  |  |  |  |  |  |  |  |

|----|--------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|--|--|

| •  | Deleted DKD 44-引脚封装具有的特性                                                                               | 1                                                  |  |  |  |  |  |  |  |  |  |

| •  | Deleted the DKD Package drawing from the Pin Assignment section                                        | 2                                                  |  |  |  |  |  |  |  |  |  |

| •  | Deleted the TAS5613ADKD from the PACKAGE HEAT DISSIPATON RATINGS table                                 | 3                                                  |  |  |  |  |  |  |  |  |  |

| •  | Deleted the TAS5613ADKD from the ORDERING INFORMATION table                                            | 3                                                  |  |  |  |  |  |  |  |  |  |

| •  | Changed the FPWM and RFREQ ADJ values in the RECOMMENDED OPERATING CONDITIONS table                    | 5                                                  |  |  |  |  |  |  |  |  |  |

| •  | Changed the TJ max value From: 150 To: 125 in the ROC table                                            | 5                                                  |  |  |  |  |  |  |  |  |  |

| •  | Deleted the DKD package from the PIN FUNCTIONS table                                                   | 5                                                  |  |  |  |  |  |  |  |  |  |

| •  | Changed the values of the ANALOG INPUTS and OSCILLATOR section of the ELECTRICAL CHARACTERISTICS table | . 10                                               |  |  |  |  |  |  |  |  |  |

| •  | Deleted the DKD Package section from the OVERTEMPERATURE PROTECTION section                            | . 20                                               |  |  |  |  |  |  |  |  |  |

# Changes from Revision A (March 2011) to Revision B

#### Page

| • | Added DKD 44-引脚封装的特性                                                                       | . 1 |

|---|--------------------------------------------------------------------------------------------|-----|

| • | Added the DKD Package drawing to the Pin Assignment section                                | . 2 |

| • | Added the TAS5613ADKD to the PACKAGE HEAT DISSIPATON RATINGS table                         | . 3 |

| • | Added the TAS5613ADKD to the ORDERING INFORMATION table                                    | . 3 |

| • | Added the DKD package to the PIN FUNCTIONS table                                           | . 5 |

| • | Changed Inverting voltage Gain, (V <sub>OUT</sub> /V <sub>IN</sub> ) From: 20 dB To: 21 dB | 10  |

| • | Added text to the Power Supplies section                                                   | 18  |

| • | Added text following Table 3 " (non-latching, does not assert SD)"                         | 19  |

| • | Added the DKD Package section                                                              | 20  |

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                 | (6)                           |                     |              |                         |         |

| TAS5613APHD      | ACTIVE        | HTQFP        | PHD                | 64   | 90             | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | 0 to 70      | TAS5613A                | Samples |

| TAS5613APHDR     | ACTIVE        | HTQFP        | PHD                | 64   | 1000           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | 0 to 70      | TAS5613A                | Samples |

| TAS5613PHD       | NRND          | HTQFP        | PHD                | 64   | 90             | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | 0 to 70      | TAS5613                 |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

www.ti.com

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

TEXAS

NSTRUMENTS

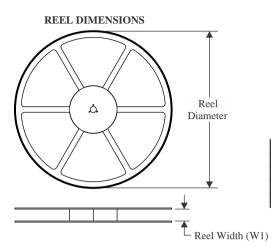

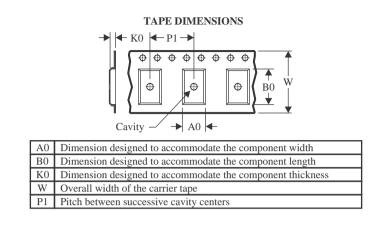

# TAPE AND REEL INFORMATION

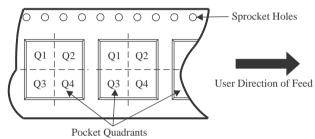

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |  |

|-----------------------------|--|

|                             |  |

|                             |  |

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TAS5613APHDR | HTQFP           | PHD                | 64 | 1000 | 330.0                    | 24.4                     | 17.0       | 17.0       | 1.5        | 20.0       | 24.0      | Q2               |

www.ti.com

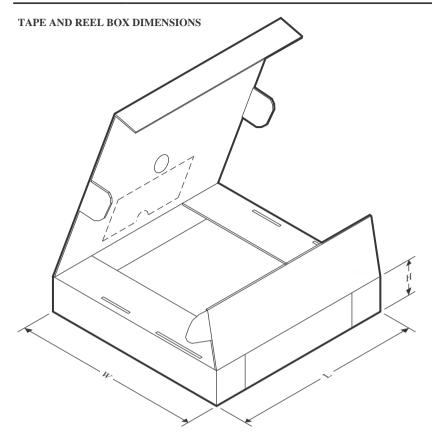

# PACKAGE MATERIALS INFORMATION

2-May-2024

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TAS5613APHDR | HTQFP        | PHD             | 64   | 1000 | 350.0       | 350.0      | 43.0        |

# TEXAS INSTRUMENTS

www.ti.com

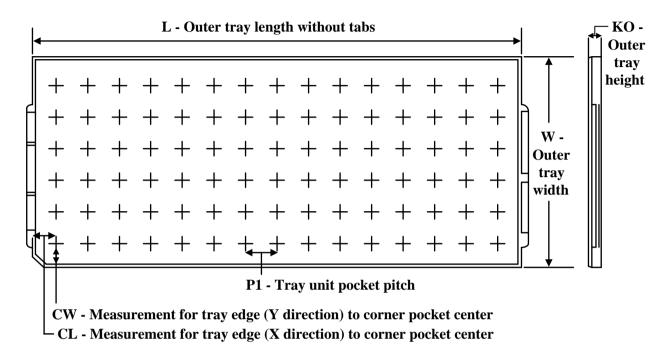

# TRAY

PACKAGE MATERIALS INFORMATION

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

| *All dimensions are nomina | l               |                 |      |     |                      |                            |        |           |            |            |            |            |

|----------------------------|-----------------|-----------------|------|-----|----------------------|----------------------------|--------|-----------|------------|------------|------------|------------|

| Device                     | Package<br>Name | Package<br>Type | Pins | SPQ | Unit array<br>matrix | Max<br>temperature<br>(°C) | L (mm) | W<br>(mm) | K0<br>(µm) | P1<br>(mm) | CL<br>(mm) | CW<br>(mm) |

| TAS5613APHD                | PHD             | HTQFP           | 64   | 90  | 6 X 15               | 150                        | 315    | 135.9     | 7620       | 20.3       | 15.4       | 15.45      |

| TAS5613PHD                 | PHD             | HTQFP           | 64   | 90  | 6 X 15               | 150                        | 315    | 135.9     | 7620       | 20.3       | 15.4       | 15.45      |

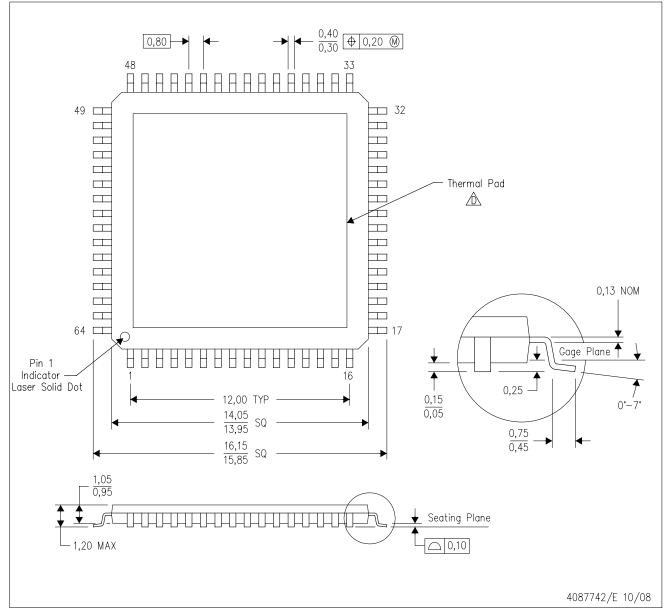

# **PHD 64**

# 14 x 14, 0.8 mm pitch

# **GENERIC PACKAGE VIEW**

HTQFP - 1.2 mm max height

PLASTIC QUAD FLATPACK

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PHD (S-PQFP-G64) PowerPAD<sup>™</sup> PLASTIC QUAD FLATPACK (DIE DOWN)

A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion

- This package is designed to be attached directly to an external heatsink. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. See the product data sheet for details regarding the exposed thermal pad dimensions.

- E. Falls within JEDEC MS-026

PowerPAD is a trademark of Texas Instruments.

NOTES:

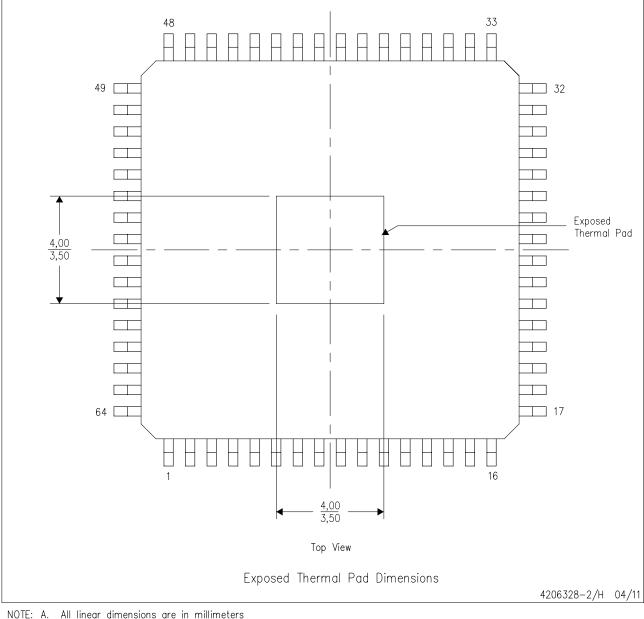

# PHD (S-PQFP-G64) PowerPAD<sup>™</sup> PLASTIC QUAD FLATPACK (DIE DOWN)

# THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NUTE: A. All linear dimensions are in millimete

PowerPAD is a trademark of Texas Instruments

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司