**TAS2553**

ZHCSC44B-SEPTEMBER 2013-REVISED FEBRUARY 2014

#### TAS2553 2.8W D 类单声道音频放大器, 支持 **G** 类升压和扬声器感测

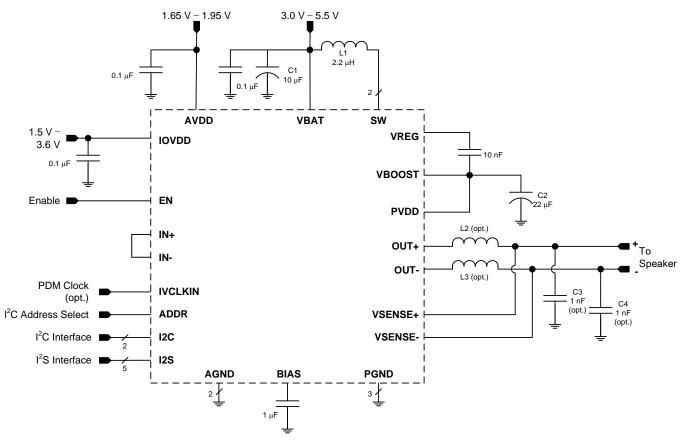

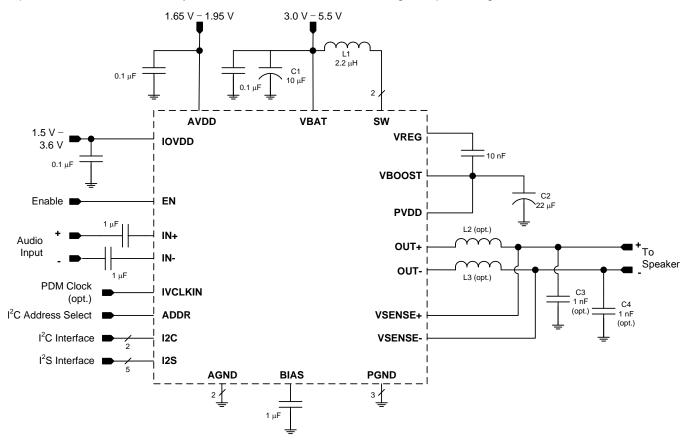

## 特性

- 模拟或数字输入单声道升压 D 类放大器

- 为 8Ω 负载提供 2.8 W 功率, 供电方式为 3.6 V 电 源(1%总谐波失真(THD)+N)

- 额定功率下,效率达到86%

- I2S, 左侧对齐, 右侧对齐, 数字信号处理器 (DSP), 脉冲密度调制 (PDM), 以及时分复用 (TDM) 输入和输出接口

- 输入采样速率从 8kHz 至 192kHz

- 高效 G 类升压转换器

- 自动调节 D 类电源

- 内置扬声器感测

- 测量扬声器电流和电压

- 测量 VBAT 和 VBOOST 电压

- 内置自动增益控制 (AGC)

- 限制电池流耗

- 可调D类开关边缘速率控制

- 电源

- 升压输入: 3.0V 至 5.5V

- 模拟: 1.65V 至 1.95V

- 数字 I/O: 1.5V 至 3.6V

- 过热和短路保护

- 用于寄存器控制的 I<sup>2</sup>C 接口

- 使用两个 TAS2553 的立体声配置

- I<sup>2</sup>C 地址选择端子 (ADDR)

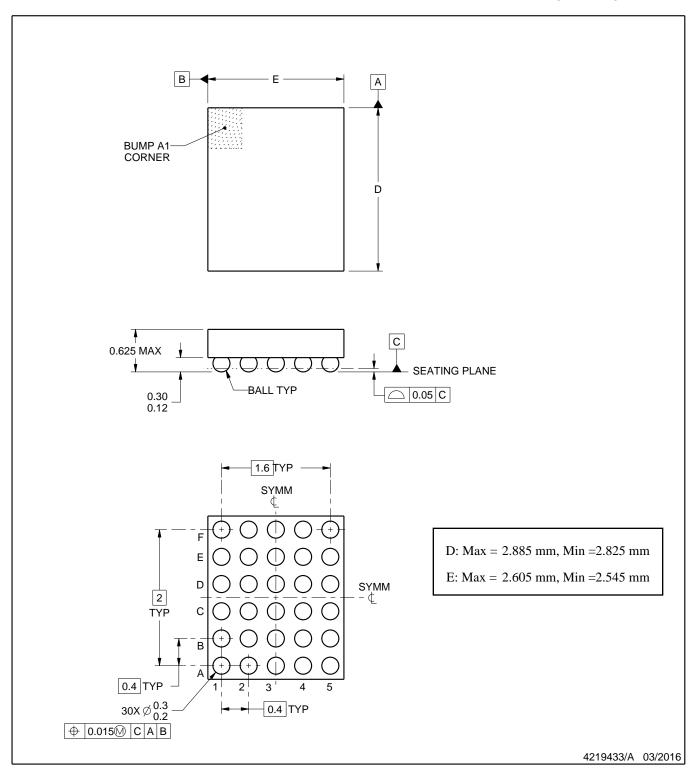

- 2.855mm x 2.575mm, 0.4mm 焊球间距, 30 焊球 晶圆级芯片封装 (WCSP)

## 2 应用范围

- 移动电话

- 便携式导航设备 (PND)

- 便携式音频底座

- 平板电脑

- 游戏设备

## 3 说明

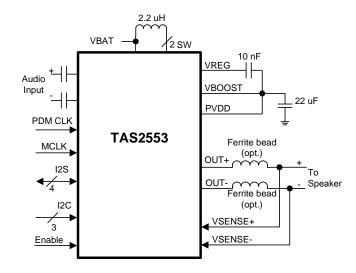

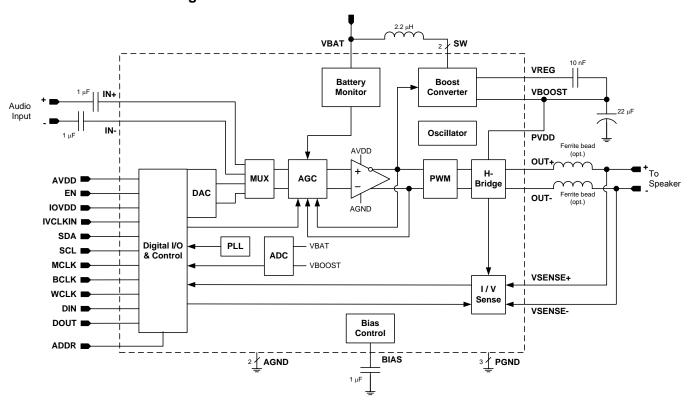

TAS2553 是一款高效 D 类音频功率放大器,此放大器 具有高级电池电流管理功能和集成 G 类升压转换器。 此器件持续测量负载上的电流和电压,并且提供此类信 息的数字流。

G 类升压转换器生成 D 类放大器电源轨。 低 D 类输 出功率期间,此升压转换器通过使 VBAT 无效并将其 直接接至 D 类放大器电源来提升效率。 当需要高功率 音频时, 升压转换器快速激活, 以提供比直接接至电池 的单独放大器高很多的音频。

AGC 自动调节 D 类增益,以减少充电结束电压上的电 池电流, 从而防止输出削波、失真和早期系统关断。 通过 I<sup>2</sup>C 调节固定增益。 增益范围介于 -7dB 至 +24dB 之间(步长 1dB)。

除了差分单声道模拟输入,TAS2553 具有使用数字输 入的内置 16 位数模 (D/A) 转换器。 将 D/A 转换器从 数字主机处理器移至集成放大器的工艺能够以更低的系 统成本提供更佳的动态性能。 此外,由于印刷电路板 (PCB) 传输的是数字信号而非模拟信号,所以系统级 上对于外部干扰(例如 GSM 帧速率噪声)的敏感度被 减少。

#### 器件信息

| 订货编号       | 封装        | 封装尺寸              |

|------------|-----------|-------------------|

| TAS2553YFF | WCSP (30) | 2.855mm x 2.575mm |

Changes from Original (September 2013) to Revision A

Page

|                            | <b>目</b> 录                                        | E             |                        |                                                                |

|----------------------------|---------------------------------------------------|---------------|------------------------|----------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6 | 特性                                                | 9<br>10<br>11 | 10.1 Layout Guidelines | 42<br>42<br>46<br>47<br>47<br>47<br>48<br>48<br>50<br>51<br>51 |

|                            | 修订历史记录                                            |               |                        |                                                                |

| ha                         | nges from Revision A (October 2013) to Revision B |               |                        | Page                                                           |

| Ī                          | 三更改 数据表格式                                         |               |                        | 1                                                              |

|                            |                                                   |               |                        |                                                                |

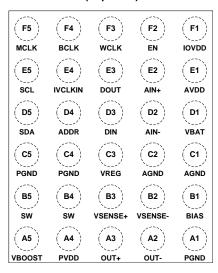

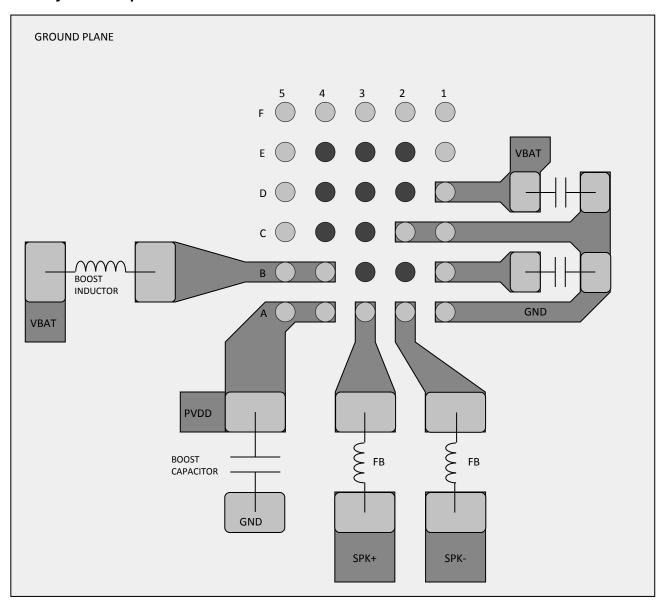

# 5 Terminal Configuration and Functions

#### 30-Ball WCSP YFF Package (Top View)

#### **Terminal Functions**

| TER     | MINAL     | INPUT/OUTPUT/ | DECORPTION                                                                                                                       |  |  |

|---------|-----------|---------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | BALL WCSP | POWER         | DESCRIPTION                                                                                                                      |  |  |

| PGND    | A1        | Р             | Power ground. Connect to high current ground plane.                                                                              |  |  |

| OUT-    | A2        | 0             | Inverting Class D output.                                                                                                        |  |  |

| OUT+    | A3        | 0             | Non-inverting Class D output.                                                                                                    |  |  |

| PVDD    | A4        | Р             | Class-D power supply. Connected internally to VBOOST – do not drive this terminal externally.                                    |  |  |

| VBOOST  | A5        | Р             | 7.5 V boost output. Connected internally to PVDD – do not drive this terminal externally.                                        |  |  |

| BIAS    | B1        | 0             | Mid-rail reference for Class D channel.                                                                                          |  |  |

| VSENSE- | B2        | I             | Inverting voltage sense input.                                                                                                   |  |  |

| VSENSE+ | В3        | 1             | Non-inverting voltage sense input.                                                                                               |  |  |

| SW      | B4,B5     | I/O           | Boost switch terminal.                                                                                                           |  |  |

| AGND    | C1,C2     | Р             | Analog ground. Connect to low noise ground plane.                                                                                |  |  |

| VREG    | C3        | 0             | High-side FET gate drive boost converter.                                                                                        |  |  |

| PGND    | C4,C5     | Р             | Power ground. Connect to high current ground plane.                                                                              |  |  |

| VBAT    | D1        | Р             | Battery power supply. Connect to 3.0 V to 5.5 V battery supply.                                                                  |  |  |

| AIN-    | D2        | 1             | Inverting analog input.                                                                                                          |  |  |

| DIN     | D3        | 1             | Audio serial data input. Format is I2S, LJF, RJF, or TDM data.                                                                   |  |  |

| ADDR    | D4        | I             | I <sup>2</sup> C address select terminal. Set ADDR = GND for device 7-bit address 0x40; set ADDR = IOVDD for 7-bit address 0x41. |  |  |

| SDA     | D5        | I/O           | I <sup>2</sup> C control bus data.                                                                                               |  |  |

| AVDD    | E1        | Р             | Analog low voltage supply terminal. Connect to 1.65 V to 1.95 V supply.                                                          |  |  |

| AIN+    | E2        | 1             | Non-inverting analog input.                                                                                                      |  |  |

| DOUT    | E3        | 0             | Serial I/V digital output. Format is I2S, LJF, RJF, TDM, or undecimated PDM data.                                                |  |  |

| IVCLKIN | E4        | 1             | Serial clock input for undecimated PDM I/V data.                                                                                 |  |  |

| SCL     | E5        | 1             | I <sup>2</sup> C control bus clock.                                                                                              |  |  |

| EN      | F2        | 1             | Device enable (HIGH = Normal Operation, LOW = Standby)                                                                           |  |  |

| WCLK    | F3        | I             | Audio serial word clock.                                                                                                         |  |  |

## **Terminal Functions (continued)**

| TERMINAL   |           | INPUT/OUTPUT/ | DESCRIPTION                                                                  |

|------------|-----------|---------------|------------------------------------------------------------------------------|

| NAME       | BALL WCSP | POWER         | DESCRIPTION                                                                  |

| BCLK       | F4        | I             | Audio serial bit clock.                                                      |

| MCLK       | F5        | 1             | External master clock.                                                       |

| IOVDD F1 P |           | Р             | Supply for digital input and output levels. Voltage range is 1.5 V to 3.6 V. |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range,  $T_A = 25$ °C (unless otherwise noted)

|            |                                           | MIN      | MAX             | UNIT |

|------------|-------------------------------------------|----------|-----------------|------|

| VBAT       | Battery voltage                           | -0.3     | 6.0             | ٧    |

| AVDD       | Analog supply voltage                     | -0.3     | 2.5             | V    |

| IOVDD      | I/O Supply voltage                        | -0.3     | 3.9             | V    |

| AIN+, AIN- | Analog input voltage                      | -0.3     | AVDD + 0.3      | ٧    |

|            | Digital input voltage                     | -0.3     | IOVDD + 0.3     | V    |

|            | Output continuous total power dissipation | See Ther | mal Information | NA   |

6.2 Handling Ratings

| PARAMETER        | DEFINITION                | MIN         | MAX  | UNIT |

|------------------|---------------------------|-------------|------|------|

| T <sub>stg</sub> | Storage temperature range | <b>–</b> 65 | 150  | °C   |

| ESD              | НВМ                       |             | 3000 | \/   |

| E2D              | CDM                       |             | 1500 | V    |

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN  | NOM | MAX  | UNIT |

|----------------|--------------------------------|------|-----|------|------|

| VBAT           | Battery voltage                | 3.0  |     | 5.5  | V    |

| AVDD           | Analog supply voltage          | 1.65 | 1.8 | 1.95 | ٧    |

| IOVDD          | I/O supply voltage             | 1.5  | 1.8 | 3.6  | ٧    |

| T <sub>A</sub> | Operating free-air temperature | -40  |     | 85   | ٥°   |

| $T_{J}$        | Operating junction temperature | -40  |     | 150  | °C   |

#### 6.4 Thermal Information

|                  | THERMAL METRIC <sup>(1)</sup>                | TAS2553            | LINUT |

|------------------|----------------------------------------------|--------------------|-------|

|                  | I THERMAL METRIC                             | YFF (30 TERMINALS) | UNIT  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 76.5               |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 0.2                |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 44.0               | °C/W  |

| ΨЈТ              | Junction-to-top characterization parameter   | 1.6                |       |

| $\Psi_{JB}$      | Junction-to-board characterization parameter | 43.4               |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

VBAT = 3.6 V, AVDD = IOVDD = 1.8 V, EN = IOVDD, SWS = 0, Gain = 15 dB, ERC = 14 ns,  $R_L$  = 8  $\Omega$  + 33  $\mu$ H, 48 kHz sample rate for digital input (unless otherwise noted)

| ample rate for digital input (unless otherwise           | ,                                                                                                                  |      |      |     |           |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|-----|-----------|

| PARAMETER                                                | TEST CONDITIONS                                                                                                    | MIN  | TYP  | MAX | UNIT      |

| BOOST CONVERTER                                          |                                                                                                                    |      |      |     |           |

| Boost Output Voltage                                     | Average voltage (w/o including ripple). Includes load regulation (0-0.6A) and line regulation (VBAT = 3.0 - 4.8V). |      | 7.5  |     | V         |

| Boost Converter Switching Frequency                      |                                                                                                                    |      | 1.8  |     | MHz       |

| LASS-D CHANNEL                                           |                                                                                                                    |      |      |     |           |

| Max Analog Input                                         | For THD+N < 1%                                                                                                     |      | 1    |     | $V_{RMS}$ |

| Full-Scale DAC Output                                    | All digital interface modes                                                                                        |      | 1    |     | $V_{RMS}$ |

| Load Resistance (Load Spec Reisistance)                  |                                                                                                                    | 6    | 8    |     | Ω         |

| Class-D Frequency                                        |                                                                                                                    |      | 764  |     | kHz       |

| Class-D + Boost Efficiency                               | VBAT = 3.0 – 4.8 V, Pout = 1 W (sinewave)                                                                          |      | 67%  |     |           |

| Class-D Output Current Limit (Short Circuit Protection)  | VBOOST = 7.5 V, OUT- shorted to VBAT or VBOOST                                                                     |      | 3.7  |     | Α         |

| Class-D Output Offset Voltage in<br>Analog Input Mode    | VBAT = 3.6 V, AV = 15 dB, RL = 8 $\Omega$ , input shorted to ground through single capacitor                       | -7.4 |      | 4.6 | mV        |

| Class-D Output Offset Voltage in Digital Input Mode      | VBAT = 3.6 V, AV = 15 dB, RL =8 $\Omega$ , 0's data                                                                | -9.8 |      | 5.6 | mV        |

| Programmable Channel Gain Range (PGA + class-D), minimum | Typical value, analog and digital input                                                                            |      | -7   |     | dB        |

| Programmable Channel Gain Range (PGA + class-D), maximum | Typical value, analog and digital input                                                                            |      | 24   |     | dB        |

| Programmable Channel Gain Step (PGA + class-D)           | Typical value, analog and digital input                                                                            |      | 1    |     | dB        |

| Mute Attenuation                                         | Device in shutdown, digital input only                                                                             |      | 103  |     | dB        |

|                                                          | Ripple of 200mVpp @ 217 Hz, Gain = 15 dB, analog and digital input                                                 |      | 63   |     |           |

| VBAT Power Supply Rejection Ratio (PSRR)                 | Ripple of 200mVpp @ 1 kHz, Gain = 15 dB, analog and digital input                                                  |      | 60   |     | dB        |

|                                                          | Ripple of 200mVpp @ 4 kHz, Gain = 15 dB, analog and digital input                                                  |      | 60   |     |           |

|                                                          | Ripple of 200mVpp @ 217 Hz, Gain = 15 dB, analog and digital input                                                 |      | 69   |     |           |

| AVDD Power Supply Rejection Ratio (PSRR)                 | Ripple of 200mVpp @ 1 kHz, Gain = 15 dB, analog and digital input                                                  |      | 67   |     | dB        |

|                                                          | Ripple of 200mVpp @ 4 kHz, Gain = 15 dB, analog and digital input                                                  |      | 62   |     |           |

| Common Mode Rejection Ratio                              | Ripple of 200mVpp @ 217 Hz, Gain = 15 dB, analog input                                                             |      | 59   |     | dB        |

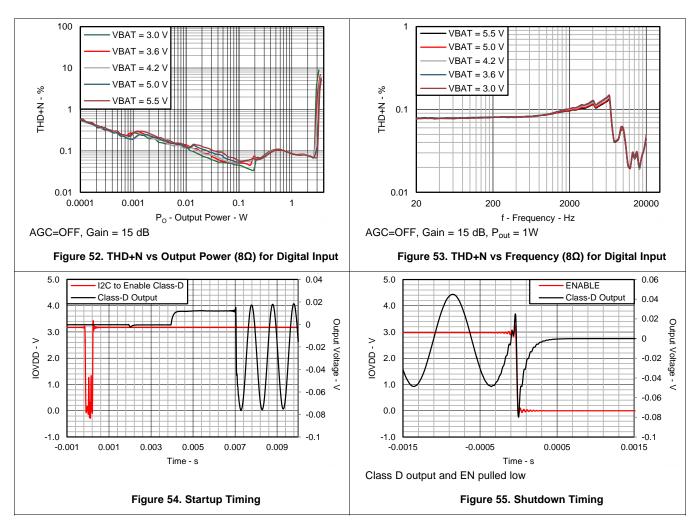

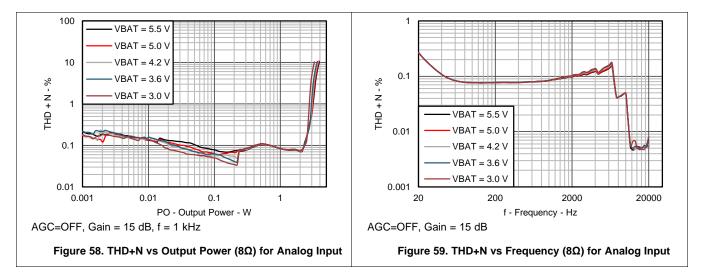

|                                                          | 1 kHz, Po = 0.1W, VBAT = 3.6 V, RL = 8 $\Omega$                                                                    |      | 0.6% |     |           |

| THD+N                                                    | 1 kHz, Po = 0.5W, VBAT = 3.6 V, RL = 8 $\Omega$                                                                    |      | 0.7% |     |           |

|                                                          | 1 kHz, Po = 1 W, VBAT = 3.6 V, RL = 8 Ω                                                                            |      | 0.9% |     |           |

|                                                          | 1 kHz, Po = 2 W, VBAT = 3.6 V, RL = 8 $\Omega$                                                                     |      | 1.3% |     |           |

| Output Integrated Noise (20Hz-20kHz)                     | A-wt Filter, Gain = 15 dB, DAC modulator switching                                                                 |      | 131% |     | μV        |

| - 8Ω                                                     | A-wt Filter, Gain = 15 dB, Analog In, Inputs shorted                                                               |      | 173% |     | μV        |

# **Electrical Characteristics (continued)**

VBAT = 3.6 V, AVDD = IOVDD = 1.8 V, EN = IOVDD, SWS = 0, Gain = 15 dB, ERC = 14 ns,  $R_L$  = 8  $\Omega$  + 33  $\mu$ H, 48 kHz sample rate for digital input (unless otherwise noted)

|                   | PARAMETER                             | TEST CONDITIONS                                                                       | MIN TYP | MAX   | UNIT              |

|-------------------|---------------------------------------|---------------------------------------------------------------------------------------|---------|-------|-------------------|

|                   |                                       | THD+N = 1%, VBAT = 3.0 V                                                              | 2.8     |       | 147               |

|                   | Max Output Power, 8-Ω Load            | THD+N = 1%, VBAT = 3.6 V                                                              | 2.8     |       | W                 |

|                   | Output Impedance in Shutdown          | EN = 0 V                                                                              | 10      |       | kΩ                |

|                   | Startup Time                          | Analog/digital input measured from time when device is taken out of software shutdown | 8       |       | mS                |

|                   | Shutdown Time                         | Measured from time when device is programmed in software shutdown mode                | 1       |       | μS                |

| INPUT SE          | ECTION                                |                                                                                       |         |       |                   |

|                   | Full-scale DAC output                 | All digital interface modes                                                           | 1.0     |       | $V_{RMS}$         |

|                   | Maximum analog input voltage          |                                                                                       | 1.0     |       | $V_{RMS}$         |

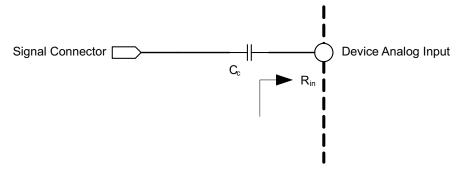

| D                 | Input impedance (terminals AIN+,      | EN = IOVDD, Amplifier active                                                          | 10      |       | kΩ                |

| R <sub>IN</sub>   | AIN-)                                 | EN = 0 V, In shutdown                                                                 | 19      |       | K12               |

| CURREN            | IT SENSE                              |                                                                                       |         | ·     |                   |

|                   | Current Sense Full Scale              | Peak current which will give full scale digital output                                | 1.4     |       | A <sub>PEAK</sub> |

|                   | Current Sense Accuracy                | I <sub>OUT</sub> = 354 mA <sub>RMS</sub> (1 W)                                        | 1%      |       |                   |

|                   | Current Sense Offset                  | Input referred                                                                        | 0.0029  |       | mA                |

|                   | Current Sense Gain Error              |                                                                                       | 0.09    |       | dB                |

| THD+N             | Distortion + Noise                    | Po = 1.0W (Load = $8Ω + 33 μH$ )                                                      | 0.17%   |       |                   |

| VOLTAG            | E SENSE                               |                                                                                       |         |       |                   |

|                   | Voltage Sense Full Scale              | Peak voltage which will give full scale digital output                                | 8.5     |       | $V_{PEAK}$        |

|                   | Voltage Sense Accuracy                | V <sub>OUT</sub> = 2.83 Vrms (1W)                                                     | 2.2%    |       |                   |

|                   | Voltage Sense Offset                  | Input referred                                                                        | 1.45    |       | mV                |

|                   | Voltage Sense Gain Error              |                                                                                       | -0.20   |       | dB                |

| THD+N             | Distortion + Noise                    | Po = 1.0 W (Load = $8\Omega + 33\mu H$ )                                              | 0.08%   |       |                   |

| INTERFA           | CE                                    | ·                                                                                     |         |       |                   |

| F <sub>MCLK</sub> | MCLK frequency                        |                                                                                       | 0.512   | 49.15 | MHz               |

| F <sub>PDM</sub>  | PDM Clock (IVCLK) Frequency Range     |                                                                                       | 1.636   | 3.25  | MHz               |

| PDM <sub>DC</sub> | PDM Clock (IVCLK) Duty Cycle<br>Range |                                                                                       | 40%     | 60%   |                   |

# **Electrical Characteristics (continued)**

VBAT = 3.6 V, AVDD = IOVDD = 1.8 V, EN = IOVDD, SWS = 0, Gain = 15 dB, ERC = 14 ns,  $R_L$  = 8  $\Omega$  + 33  $\mu$ H, 48 kHz sample rate for digital input (unless otherwise noted)

|                 | PARAMETER                                                  | TEST CONDITIONS                 | MIN TYP        | MAX            | UNIT |

|-----------------|------------------------------------------------------------|---------------------------------|----------------|----------------|------|

| POWER           | R CONSUMPTION                                              |                                 |                |                |      |

|                 |                                                            | From VBAT, PLL off, no signal   | 7.10           |                | mA   |

|                 | Power Consumption with Analog Input and IV Sense Disabled  | From AVDD, PLL off, no signal   | 3.73           |                | mA   |

|                 | and iv dense bisabled                                      | From IOVDD, PLL off, no signal  | 0.04           |                | mA   |

|                 |                                                            | From VBAT, PLL off, no signal   | 7.31           |                | mA   |

|                 | Power Consumption with Digital Input and IV Sense Disabled | From AVDD, PLL off, no signal   | 4.05           |                | mA   |

|                 | and IV Conse Disabled                                      | From IOVDD, PLL off, no signal  | 0.32           |                | mA   |

|                 |                                                            | From VBAT, PLL on, no signal    | 5.84           |                | mA   |

|                 | Power Consumption with Analog Input and IV Sense Enabled   | From AVDD, PLL on, no signal    | 7.10           |                | mΑ   |

|                 | and IV Conce Enabled                                       | From IOVDD, PLL on, no signal   | 0.32           |                | mΑ   |

|                 |                                                            | From VBAT, PLL on, no signal    | 7.32           |                | mA   |

|                 | Power Consumption with Digital Input and IV Sense Enabled  | From AVDD, PLL on, no signal    | 8.03           |                | mA   |

|                 | and IV Conce Enabled                                       | From IOVDD, PLL on, no signal   | 0.32           |                | mA   |

|                 |                                                            | From VBAT, EN = 0               | 0.1            |                | μΑ   |

|                 | Snutdown                                                   | From AVDD, EN = 0               | 0.2            |                | μΑ   |

|                 |                                                            | From IOVDD, EN = 0              | 0.0            |                | μΑ   |

|                 |                                                            | From VBAT                       | 11.4           |                | μΑ   |

|                 | Power Consumption in Software Shutdown                     | From AVDD                       | 9.1            |                | μΑ   |

|                 |                                                            | From IOVDD                      | 130            |                | μΑ   |

| DIGITA          | L INPUT / OUTPUT                                           |                                 | •              | ·              |      |

| / <sub>IH</sub> | High-level digital input voltage                           |                                 | 0.7 x<br>IOVDD |                | V    |

| / <sub>IL</sub> | Low-level digital input voltage                            |                                 |                | 0.3 x<br>IOVDD | V    |

| /он             | High-level digital output voltage                          |                                 | 0.9 x<br>IOVDD |                | V    |

| / <sub>OL</sub> | Low-level digital output voltage                           |                                 |                | 0.1 x<br>IOVDD | V    |

| MISCEI          | LLANEOUS                                                   |                                 | ·              |                |      |

|                 | AVDD Supply Under-voltage                                  | Device is in reset state        | 0.9            |                |      |

|                 | Threshold                                                  | Device comes out of reset state |                | 1.4            | V    |

|                 | VBAT Supply Under-voltage                                  | Device is in reset state        | 1.8            |                | ١,,  |

|                 | Threshold                                                  | Device comes out of reset state |                | 2.5            | V    |

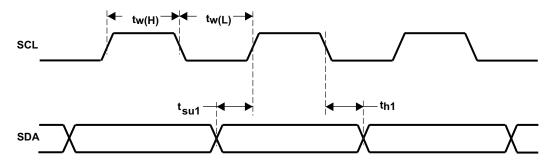

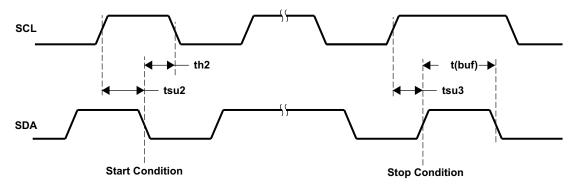

## 6.6 Timing Requirements/Timing Diagrams

For I<sup>2</sup>C interface signals over recommended operating conditions (unless otherwise noted). **Note:** All timing specifications are measured at characterization but not tested at final test.

|                    | PARAMETER                                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|------------------------------------------------|-----------------|-----|-----|-----|------|

| $f_{SCL}$          | Frequency, SCL                                 | No wait states  |     |     | 400 | kHz  |

| $t_{W(H)}$         | Pulse duration, SCL high                       |                 | 0.6 |     |     | μs   |

| $t_{W(L)}$         | Pulse duration, SCL low                        |                 | 1.3 |     |     | μs   |

| t <sub>su1</sub>   | Setup time, SDA to SCL                         |                 | 100 |     |     | ns   |

| t <sub>h1</sub>    | Hold time, SCL to SDA                          |                 | 10  |     |     | ns   |

| t <sub>(buf)</sub> | Bus free time between stop and start condition |                 | 1.3 |     |     | μs   |

| t <sub>su2</sub>   | Setup time, SCL to start condition             |                 | 0.6 |     |     | μs   |

| t <sub>h2</sub>    | Hold time, start condition to SCL              |                 | 0.6 |     |     | μs   |

| t <sub>su3</sub>   | Setup time, SCL to stop condition              |                 | 0.6 |     |     | μs   |

Figure 1. SCL and SDA Timing

Figure 2. Start and Stop Conditions Timing

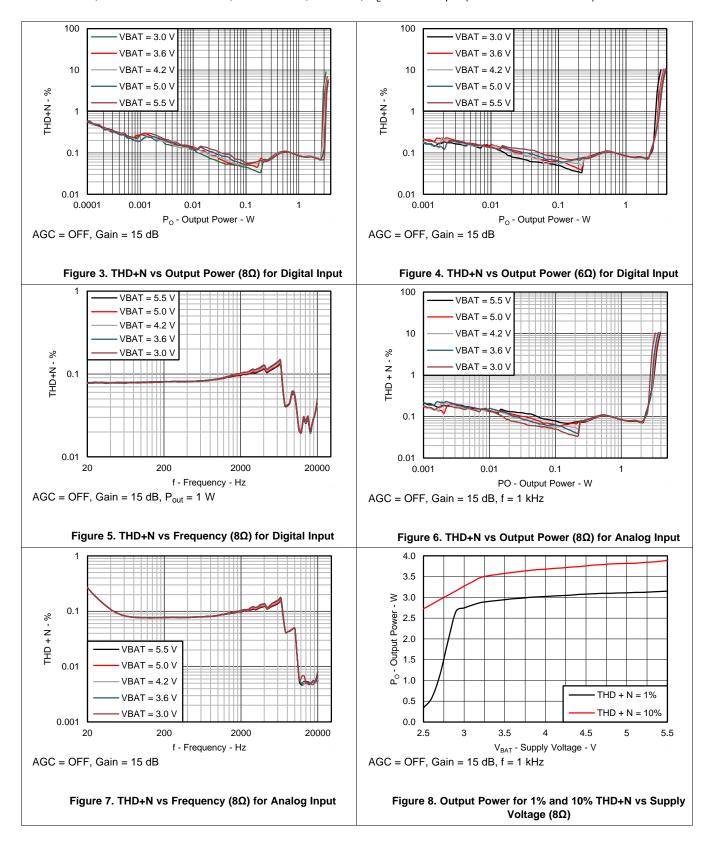

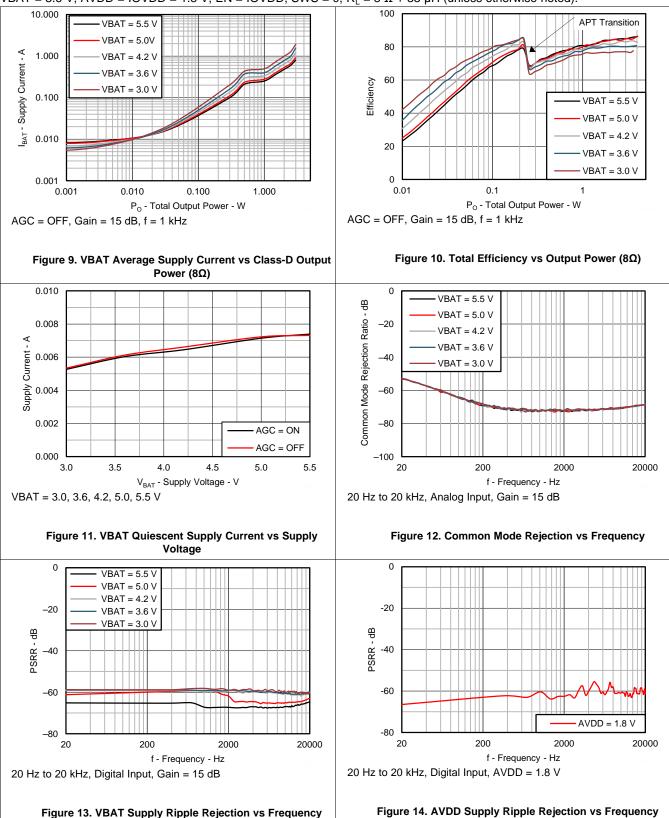

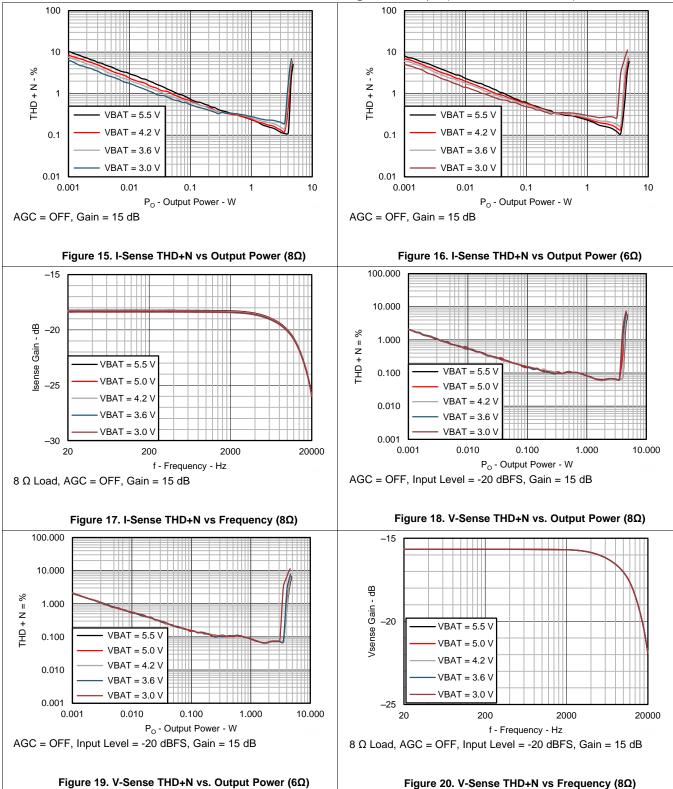

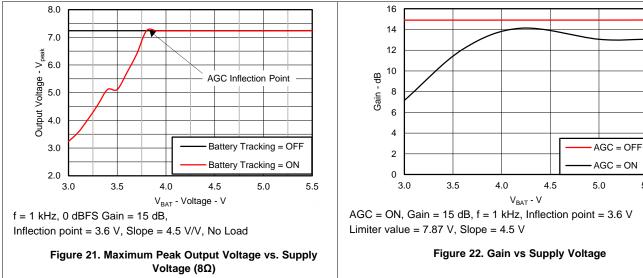

#### 6.7 Typical Characteristics

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

#### **Typical Characteristics (continued)**

5.5

## **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

The TAS2553 is a high efficiency Class-D audio power amplifier with advanced battery current management and an integrated Class-G boost converter. The TAS2553 provides real-time output current and voltage information to the host processor via the I<sup>2</sup>S, LJF, RJF, TDM, DSP, or PDM interface. This output current and voltage information is useful for speaker protection and sound enhancement algorithms, allowing the host to track the speaker impedance and to enable usage of lower-cost, wider tolerance speakers reliably pushed to their rated output power and beyond.

When auto-passthrough mode is enabled, the Class-G boost converter generates the Class-D amplifier supply rail. During low Class-D output power, the boost improves efficiency by deactivating and connecting VBAT directly to the Class-D amplifier supply. When high power audio is required, the boost quickly activates to provide significantly louder audio than a stand-alone amplifier connected directly to the battery.

The battery monitor and AGC work together in the Battery Tracking AGC to automatically adjust the Class-D gain to reduce battery current at end-of-charge voltage levels, preventing output clipping, distortion and early system shutdown. The fixed gain is adjustable via I<sup>2</sup>C. The gain range is -7 dB to +24 dB in 1 dB steps.

In addition to a differential mono analog input, the TAS2553 has built-in a 16-bit D/A converter used with a digital input. The digital audio interface supports I<sup>2</sup>S, Left-Justified, Right-Justified, DSP, PDM and TDM modes. Moving the D/A converter from the digital host processor into the integrated amplifier process provides better dynamic performance at lower system cost. Additionally, since the PCB routing is digital rather than analog, sensitivity to external perturbations such as GSM frame-rate noise is decreased at the system level.

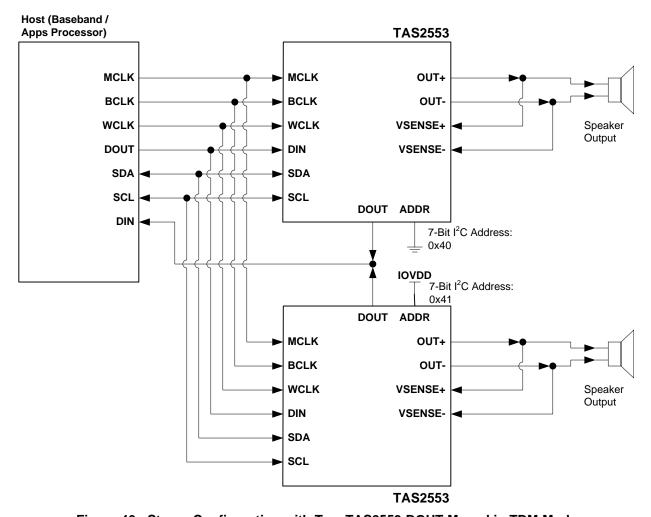

Stereo configuration can be achieved with two TAS2553s by using the ADDR terminal to address each TAS2553 seperately. Set ADDR to ground to configure the device for I<sup>2</sup>C address 0x40 (7-bit). Set ADDR to IOVDD for I<sup>2</sup>C address 0x41 (7-bit). Refer to the General I<sup>2</sup>C Operation section for more details.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

## 7.3.1 General I<sup>2</sup>C Operation

The TAS2553 operates as an I<sup>2</sup>C slave over the IOVDD voltage range. It is adjustable to one of two I<sup>2</sup>C addresses. This allows two TAS2553 devices in a system to connect to the same I<sup>2</sup>C bus.

Set the ADDR terminal to ground to assign the device I<sup>2</sup>C address to 0x40 (7-bit). This is equivalent to 0x80 (8-bit) for writing and 0x81 (8-bit) for reading.

Set ADDR to IOVDD for I<sup>2</sup>C address 0x41 (7-bit). This is equivalent to 0x82 (8-bit) for writing and 0x83 (8-bit) for reading.

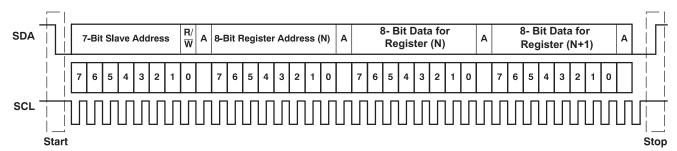

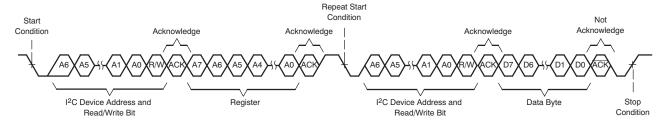

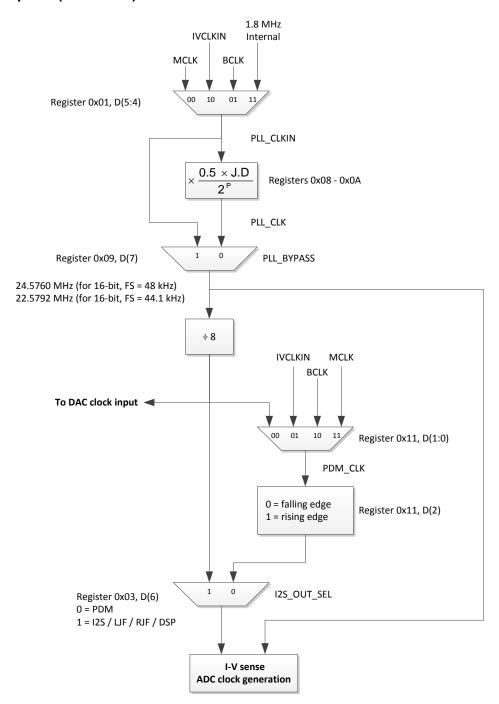

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. The bus transfers data serially, one bit at a time. The address and data 8-bit bytes are transferred most-significant bit (MSB) first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data terminal (SDA) while the clock is at logic high to indicate start and stop conditions. A high-to-low transition on SDA indicates a start, and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period. Figure 23 shows a typical sequence.

The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The TAS2553 holds SDA low during the acknowledge clock period to indicate acknowledgment. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bi-directional bus using a wired-AND connection.

Use external pull-up resistors for the SDA and SCL signals to set the logic-high level for the bus. Use pull-up resistors between 660  $\Omega$  and 4.7 k $\Omega$ . Do not allow the SDA and SCL voltages to exceed the TAS2553 supply voltage, IOVDD.

Figure 23. Typical I<sup>2</sup>C Sequence

There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. Figure 23 shows a generic data transfer sequence.

#### 7.3.2 Single-Byte and Multiple-Byte Transfers

The serial control interface supports both single-byte and multiple-byte read/write operations for all registers. During multiple-byte read operations, the TAS2553 responds with data, a byte at a time, starting at the register assigned, as long as the master device continues to respond with acknowledges.

The TAS2553 supports sequential I<sup>2</sup>C addressing. For write transactions, if a register is issued followed by data for that register and all the remaining registers that follow, a sequential I<sup>2</sup>C write transaction has taken place. For I2C sequential write transactions, the register issued then serves as the starting point, and the amount of data subsequently transmitted, before a stop or start is transmitted, determines to how many registers are written.

#### **Feature Description (continued)**

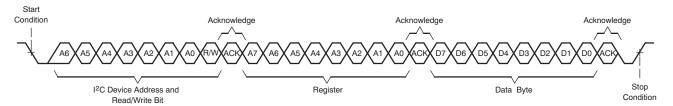

#### 7.3.3 Single-Byte Write

As shown in Figure 24, a single-byte data-write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. The read/write bit determines the direction of the data transfer. For a write-data transfer, the read/write bit must be set to 0. After receiving the correct I<sup>2</sup>C device address and the read/write bit, the TAS2553 responds with an acknowledge bit. Next, the master transmits the register byte corresponding to the TAS2553 internal memory address being accessed. After receiving the register byte, the TAS2553 again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data-write transfer.

Figure 24. Single-Byte Write Transfer

#### 7.3.4 Multiple-Byte Write and Incremental Multiple-Byte Write

A multiple-byte data write transfer is identical to a single-byte data write transfer except that multiple data bytes are transmitted by the master device to the TAS2553 as shown in Figure 25. After receiving each data byte, the TAS2553 responds with an acknowledge bit.

Figure 25. Multiple-Byte Write Transfer

#### 7.3.5 Single-Byte Read

As shown in Figure 26, a single-byte data-read transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. For the data-read transfer, both a write followed by a read are actually done. Initially, a write is done to transfer the address byte of the internal memory address to be read. As a result, the read/write bit is set to a 0.

After receiving the TAS2553 address and the read/write bit, the TAS2553 responds with an acknowledge bit. The master then sends the internal memory address byte, after which the TAS2553 issues an acknowledge bit. The master device transmits another start condition followed by the TAS2553 address and the read/write bit again. This time, the read/write bit is set to 1, indicating a read transfer. Next, the TAS2553 transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the single-byte data read transfer.

The device address is 0x40 (7-bit). This is equivalent to 0x81 (8-bit) for reading.

Figure 26. Single-Byte Read Transfer

## **Feature Description (continued)**

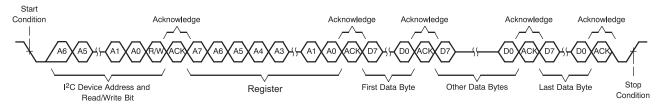

#### 7.3.6 Multiple-Byte Read

A multiple-byte data-read transfer is identical to a single-byte data-read transfer except that multiple data bytes are transmitted by the TAS2553 to the master device as shown in Figure 27. With the exception of the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

Figure 27. Multiple-Byte Read Transfer

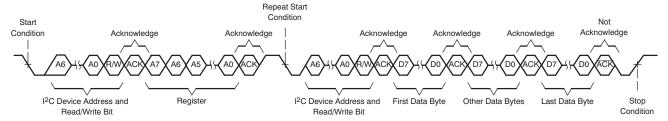

#### 7.3.7 PLL

The TAS2553 has an on-chip PLL to generate the clock frequency for the audio DAC and I-V sensing ADCs. The programmability of the PLL allows operation from a wide variety of clocks that may be available in the system.

The PLL input supports clocks varying from 512 kHz to 24.576 MHz and is register programmable to enable generation of required sampling rates with fine resolution. Set Register 0x02, D(3) = 1 to activate the PLL. When the PLL is enabled, the PLL output clock PLL\_CLK is:

$$PLL\_CLK = \frac{0.5 \times PLL\_CLKIN \times J.D}{2^{P}}$$

(1)

J = 4, 5, 6, ... 96 D = 0, 1, 2, ... 9999 P = 0.1

Choose J, D, P such that PLL\_CLK = 22.5792 MHz (44.1ksps sampling rate) or 24.5760 MHz (48ksps sampling rate). Program variable J in Register 0x08, D(6:0). Program variable D in Register 0x09, D(5:0) and Register 0x0A, D(7:0). The default value for D is 0. Program variable P in Register 0x08, D(7). The default value for P is 0

Register 0x01, D(5:4) sets the PLL\_CLKIN input to MCLK, BCLK, or IVCLKIN. Set Register 0x01, D(5:4) = 00 to use MCLK, 01 to use BCLK, and 10 to use IVCLKIN.

There is also an option to use a 1.8 MHz internal oscillator for PLL\_CLKIN. This is useful for systems using the analog inputs and the I-V sense data returning to a host processor via PDM mode interface. Set Register 0x01, D(5:4) = 11 to use the 1.8 MHz internal oscillator.

To bypass the PLL, set Register 0x09, D(7) = 1. Deactivate the PLL by setting Register 0x02, D(3) = 0.

When the PLL is enabled, the following conditions must be satisfied:

If D = 0, the PLL clock input (PLL\_CLKIN) must satisfy:

$$512 \text{ kHz} \leq \frac{PLL\_CLKIN}{2^P} \leq 12.288 \text{ MHz}$$

• If D ≠ 0, the PLL clock input (PLL\_CLKIN) must satisfy:

$$1.1 \text{ MHz} \ \leq \ \frac{PLL\_CLKIN}{2^P} \leq 9.2 \text{ MHz}$$

Figure 28 shows the clock distribution tree and the registers required to set the audio input DAC and the I-V sense ADC.

#### **Feature Description (continued)**

Figure 28. Clock Distribution Tree

## 7.3.8 Gain Settings

The TAS2553 has one gain register for both analog input and digital input (DAC output) gain. A mux selects only one of these inputs for the Class-D speaker amplifier. The analog and digital inputs cannot be mixed together.

The full-scale DAC output voltage is the same as the maximum analog input voltage (for less than 1% THD): 1  $V_{RMS}$ , or 1.4  $V_{PEAK}$ .

Table 1. TAS2553 Gain Table

| GAIN BYTE:<br>GAIN[4:0] | NOMINAL GAIN                            | GAIN BYTE:<br>GAIN[4:0] | NOMINAL GAIN |

|-------------------------|-----------------------------------------|-------------------------|--------------|

| 00000                   | –7 dB                                   | 10000                   | 9 dB         |

| 00001                   | −6 dB                                   | 10001                   | 10 dB        |

| 00010                   | −5 dB                                   | 10010                   | 11 dB        |

| 00011                   | –4 dB                                   | 10011                   | 12 dB        |

| 00100                   | -3 dB<br>-2 dB<br>-1 dB<br>0 dB<br>1 dB | 10100                   | 13 dB        |

| 00101                   |                                         | 10101                   | 14 dB        |

| 00110                   |                                         | 10110                   | 15 dB        |

| 00111                   |                                         | 10111                   | 16 dB        |

| 01000                   |                                         | 11000                   | 17 dB        |

| 01001                   | 2 dB                                    | 11001                   | 18 dB        |

| 01010                   | 3 dB 11010                              | 3 dB 11010              | 19 dB        |

| 01011                   | 4 dB                                    | 11011                   | 20 dB        |

| 01100                   | 5 dB                                    | 11100                   | 21 dB        |

| 01101                   | 6 dB                                    | 11101                   | 22 dB        |

| 01110                   | 7 dB                                    | 11110                   | 23 dB        |

| 01111                   | 8 dB                                    | 11111                   | 24 dB        |

## 7.3.9 Class-D Edge Rate Control

The edge rate of the Class-D output is controllable via an  $I^2C$  register. This allows users the ability to adjust the switching edge rate of the Class-D amplifier, trading off some efficiency for lower EMI. Table 2 lists the typical edge rates.

Table 2. Class-D Edge Rate Control

| ERC BYTE:<br>EDGE[2:0] | T <sub>R</sub> AND T <sub>F</sub><br>(TYPICAL) |

|------------------------|------------------------------------------------|

| 000                    | 50 ns                                          |

| 001                    | 40 ns                                          |

| 010                    | 30 ns                                          |

| 011                    | 25 ns                                          |

| 100                    | 14 ns                                          |

| 101                    | 13 ns                                          |

| 110                    | 12 ns                                          |

| 111                    | 11 ns                                          |

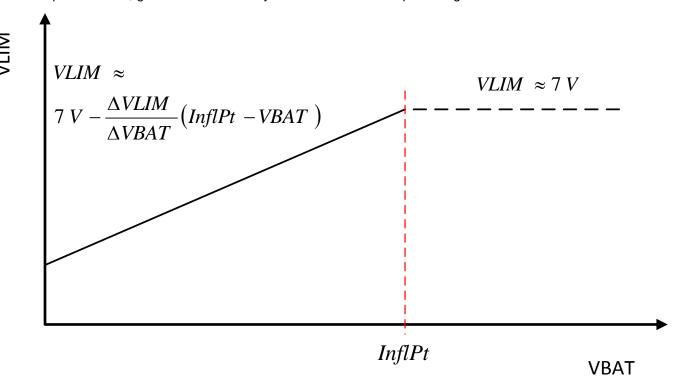

#### 7.3.10 Battery Tracking AGC

The TAS2553 monitors battery voltage and the audio signal to automatically decrease gain when the battery voltage is low and audio output power is high. This finds the optimal gain to maximize loudness and minimize battery current, providing louder audio and preventing early shutdown at end-of-charge battery voltage levels.

This does not mean the battery tracking AGC automatically decreases amplifier gain when VBAT is below the inflection point. Rather, gain is decreased only when the Class-D output voltage exceeds the limiter level.

Figure 29. VLIM versus Supply Voltage (VBAT)

When VBAT is greater than the inflection point, VLIM - the peak allowed output voltage - is set by the boost voltage. The inflection point is set in Register 0x0B, Bits 7-0. The inflection point range is 3.0 V to 5.5 V, adjustable in 17.33 mV steps.

When VBAT is less than the inflection point, the peak output voltage is controlled by the slope. Set the VLIM vs. VBAT slope in Register 0x0C, Bits 7-0. This  $\Delta$ VLIM /  $\Delta$ VBAT range is 1.2 V/V to 10.75 V/V and is adjustable in 37.3 mV/V steps.

If the audio signal is higher than VLIM, then the gain decreases until the audio signal is just below VLIM. The gain decrease rate (attack time) is set via the  $I^2C$  interface. If the audio signal is below VLIM and the gain is below the fixed gain, the gain will increase. The gain increase rate (release time) is set via the  $I^2C$  interface. The attack and release times are selected via  $I^2C$  interface. Eight attack times are available in 350  $\mu$ s / dB steps. Sixteen release times are in 105 ms / dB steps. ATK\_TIME[2:0] is Register 0x0E, Bits 0-2. REL\_TIM[3:0] is Register 0x0F, Bits 3-0.

**Table 3. Attack Time Selection**

| ATTACK TIME REGISTER BYTE: ATK_TIME[2:0] | ATTACK TIME<br>( µS / STEP) |

|------------------------------------------|-----------------------------|

| 000                                      | 20                          |

| 001                                      | 370                         |

| 010                                      | 720                         |

| 011                                      | 1070                        |

| 100                                      | 1420                        |

Table 3. Attack Time Selection (continued)

| ATTACK TIME REGISTER BYTE: ATK_TIME[2:0] | ATTACK TIME<br>( μS / STEP) |

|------------------------------------------|-----------------------------|

| 101                                      | 1770                        |

| 110                                      | 2120                        |

| 111                                      | 2470                        |

**Table 4. Release Time Selection**

| RELEASE TIME REGISTER BYTE: REL_TIME[3:0] | RELEASE TIME<br>( MS / STEP) | RELEASE TIME REGISTER BYTE: REL_TIME[4:0] | RELEASE TIME<br>(MS / STEP) |

|-------------------------------------------|------------------------------|-------------------------------------------|-----------------------------|

| 0000                                      | 50                           | 1000                                      | 890                         |

| 0001                                      | 155<br>260<br>365<br>470     | 1001                                      | 995                         |

| 0010                                      |                              | 1010                                      | 1100                        |

| 0011                                      |                              | 1011                                      | 1205                        |

| 0100                                      |                              | 1100                                      | 1310                        |

| 0101                                      | 575                          | 1101                                      | 1415                        |

| 0110                                      | 680                          | 1110                                      | 1520                        |

| 0111                                      | 785                          | 1111                                      | 1625                        |

#### 7.4 Device Functional Modes

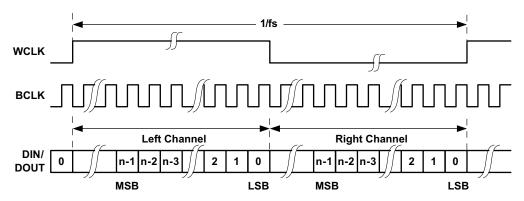

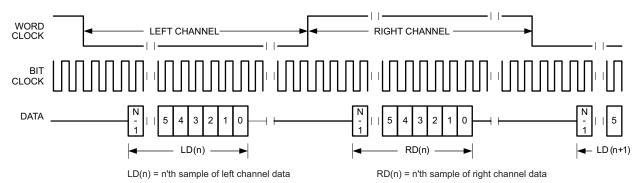

#### 7.4.1 Audio Digital I/O Interface

Audio data is transferred between the host processor and the TAS2553 via the digital audio data serial interface, or audio bus. The audio bus on this device is very flexible, including left or right-justified data options, support for l<sup>2</sup>S or PCM protocols, programmable data length options, a TDM mode for multichannel operation, very flexible master/slave configurability for each bus clock line, and the ability to communicate with multiple devices within a system directly.

The audio bus of the TAS2553 can be configured for left or right-justified, I<sup>2</sup>S, DSP, or TDM modes of operation, where communication with standard telephony PCM interfaces is supported within the TDM mode. These modes are all MSB-first, with data width programmable as 16, 20, 24, or 32 bits by configuring Register 0x05, D(1:0). In addition, the word clock and bit clock can be independently configured in either Master or Slave mode, for flexible connectivity to a wide variety of processors. The word clock is used to define the beginning of a frame, and may be programmed as either a pulse or a square-wave signal. The frequency of this clock corresponds to the maximum of the selected ADC and DAC sampling frequencies.

The bit clock is used to clock in and clock out the digital audio data across the serial bus. This signal can be programmed to generate variable clock pulses by controlling the bit-clock multiply-divide factor in Registers 0x08 through 0x10. The number of bit-clock pulses in a frame may need adjustment to accommodate various word-lengths as well as to support the case when multiple TAS2553 devices may share the same audio bus.

The TAS2553 also includes a feature to offset the position of start of data transfer with respect to the word-clock. This offset is in number of bit-clocks and is programmed in Register 0x06.

To place the DOUT line into a Hi-Z (3-state) condition during all bit clocks when valid data is not being sent, set Register 0x04, D(2) = 1. By combining this capability with the ability to program what bit clock in a frame the audio data begins, time-division multiplexing (TDM) can be accomplished. This enables the use of multiple devices on a single audio serial data bus. When the audio serial data bus is powered down while configured in master mode, the terminals associated with the interface are put into a Hi-Z output state.

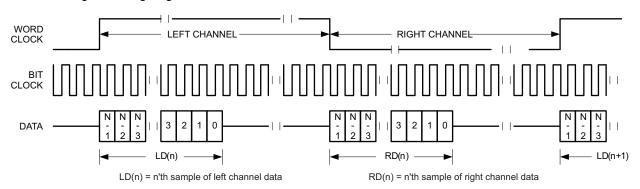

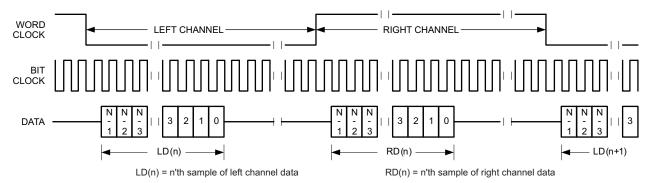

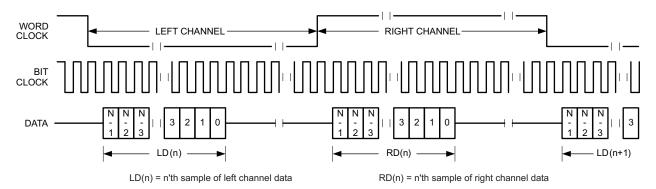

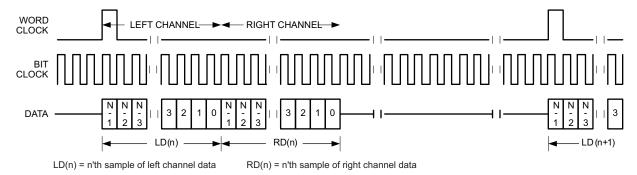

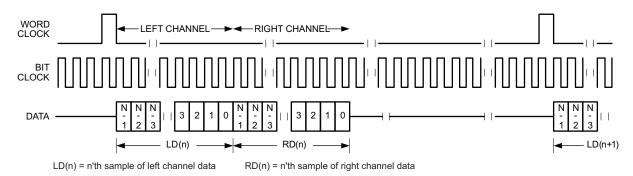

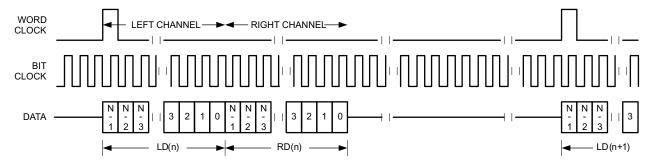

#### 7.4.1.1 Right-Justified Mode

Set Register 0x03, D(6) = 0 and Register 0x05, D(3:2) = 10 to place the TAS2553 audio interface into right-justified mode. In right-justified mode, the LSB of the left channel is valid on the rising edge of the bit clock preceding the falling edge of the word clock. Similarly, the LSB of the right channel is valid on the rising edge of the bit clock preceding the rising edge of the word clock.

## **Device Functional Modes (continued)**

Figure 30. Timing Diagram for Right-Justified Mode

For right-justified mode, the number of bit-clocks per frame should be greater than twice the programmed word-length of the data.

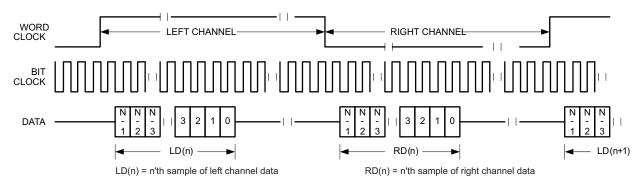

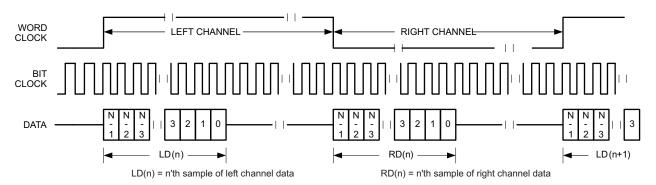

#### 7.4.1.2 Left-Justified Mode

Set Register 0x03, D(7:6) = 01 and Register 0x05, D(3:2) = 11 to place the TAS2553 audio interface into left-justified mode. In left-justified mode, the MSB of the right channel is valid on the rising edge of the bit clock following the falling edge of the word clock. Similarly the MSB of the left channel is valid on the rising edge of the bit clock following the rising edge of the word clock.

Figure 31. Timing Diagram for Left-Justified Mode

Figure 32. Timing Diagram for Light-Left Mode with Offset=1

#### **Device Functional Modes (continued)**

Figure 33. Timing Diagram for Left-Justified Mode with Offset=0 and Inverted Bit Clock

For left-justified mode, the number of bit-clocks per frame should be greater than twice the programmed word-length of the data. Also, the programmed offset value should be less than the number of bit-clocks per frame by at least the programmed word-length of the data.

#### 7.4.1.3 PS Mode

Set Register 0x03, D(7:6) = 01 and Register 0x05, D(3:2) = 00 to place the TAS2553 audio interface into  $I^2S$  mode. In  $I^2S$  mode, the MSB of the left channel is valid on the second rising edge of the bit clock after the falling edge of the word clock. Similarly the MSB of the right channel is valid on the second rising edge of the bit clock after the rising edge of the word clock.

Figure 34. Timing Diagram for I<sup>2</sup>S Mode

Figure 35. Timing Diagram for I<sup>2</sup>S Mode with Offset=2

#### **Device Functional Modes (continued)**

Figure 36. Timing Diagram for I<sup>2</sup>S Mode with Offset=0 and Inverted Bit Clock

For I<sup>2</sup>S mode, the number of bit-clocks per channel should be greater than or equal to the programmed word-length of the data. Also the programmed offset value should be less than the number of bit-clocks per frame by at least the programmed word-length of the data.

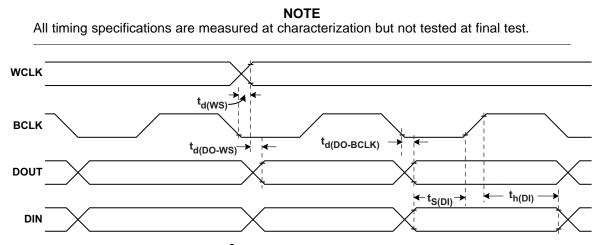

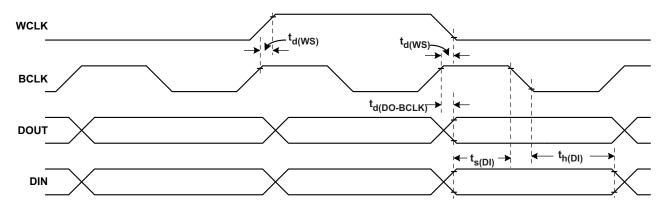

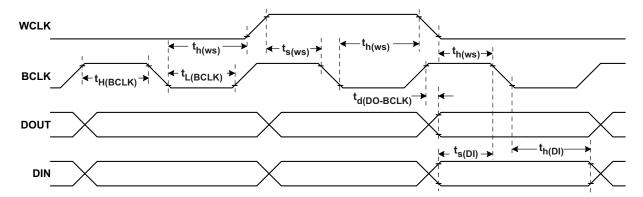

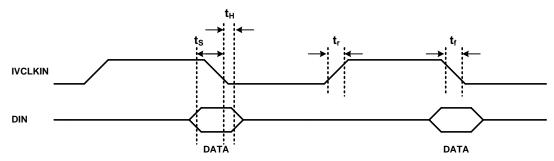

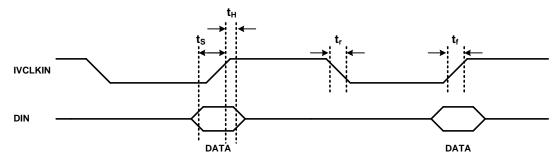

#### 7.4.1.4 Audio Data Serial Interface Timing (l<sup>2</sup>S, Left-Justified, Right-Justified Modes)

All specifications at 25°C, IOVDD = 1.8 V

Figure 37. I<sup>2</sup>S/LJF/RJF Timing in Master Mode

Table 5. I<sup>2</sup>S/LJF/RJF Timing in Master Mode (see Figure 37)

|                          | PARAMETER                              | IOVDD=1.8V |     | IOVDD=3.3V |     | LINUT |

|--------------------------|----------------------------------------|------------|-----|------------|-----|-------|

|                          | PARAMETER                              |            | MAX | MIN        | MAX | UNIT  |

| t <sub>d</sub> (WS)      | WCLK delay                             |            | 30  |            | 20  | ns    |

| t <sub>d</sub> (DO-WS)   | WCLK to DOUT delay (For LJF Mode only) |            | 50  |            | 25  | ns    |

| t <sub>d</sub> (DO-BCLK) | BCLK to DOUT delay                     |            | 50  |            | 25  | ns    |

| t <sub>s</sub> (DI)      | DIN setup                              | 8          |     | 8          |     | ns    |

| t <sub>h</sub> (DI)      | DIN hold                               | 8          |     | 8          |     | ns    |

| t <sub>r</sub>           | Rise time                              |            | 24  |            | 12  | ns    |

| t <sub>f</sub>           | Fall time                              |            | 24  |            | 15  | ns    |

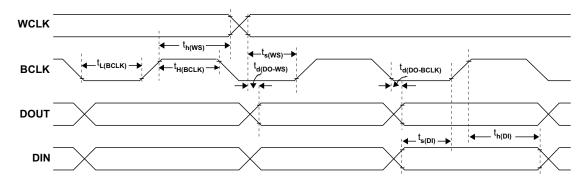

Figure 38. I<sup>2</sup>S/LJF/RJF Timing in Slave Mode

Table 6. I<sup>2</sup>S/LJF/RJF Timing in Slave Mode (see Figure 38)

|                          | PARAMETER                              | IOVDD= | 1.8V | IOVDD=3.3V |     | LINUT |

|--------------------------|----------------------------------------|--------|------|------------|-----|-------|

|                          | PARAMETER                              | MIN    | MAX  | MIN        | MAX | UNIT  |

| t <sub>H</sub> (BCLK)    | BCLK high period                       | 35     |      | 35         |     | ns    |

| $t_L(BCLK)$              | BCLK low period                        | 35     |      | 35         |     | ns    |

| t <sub>s</sub> (WS)      | (WS)                                   | 8      |      | 8          |     | ns    |

| t <sub>h</sub> (WS)      | WCLK hold                              | 8      |      | 8          |     | ns    |

| t <sub>d</sub> (DO-WS)   | WCLK to DOUT delay (For LJF Mode only) |        | 50   |            | 25  | ns    |

| t <sub>d</sub> (DO-BCLK) | BCLK to DOUT delay                     |        | 50   |            | 25  | ns    |

| t <sub>s</sub> (DI)      | DIN setup                              | 8      |      | 8          |     | ns    |

| t <sub>h</sub> (DI)      | DIN hold                               | 8      |      | 8          |     | ns    |

| t <sub>r</sub>           | Rise time                              |        | 4    |            | 4   | ns    |

| t <sub>f</sub>           | Fall time                              |        | 4    |            | 4   | ns    |

#### 7.4.1.5 DSP Mode

Set Register 0x03, D(7:6) = 01 and Register 0x05, D(3:2) = 01 to place the TAS2553 audio interface into DSP mode. In DSP mode, the rising edge of the word clock starts the data transfer with the left channel data first and immediately followed by the right channel data. Each data bit is valid on the falling edge of the bit clock.

Figure 39. Timing Diagram for DSP Mode

Figure 40. Timing Diagram for DSP Mode with Offset=1

Figure 41. Timing Diagram for DSP Mode with Offset=0 and Inverted Bit Clock

For DSP mode, the number of bit-clocks per frame should be greater than twice the programmed word-length of the data. Also the programmed offset value should be less than the number of bit-clocks per frame by at least the programmed word-length of the data.

## 7.4.1.6 **DSP Timing**

All specifications at 25°C, IOVDD = 1.8 V

#### **NOTE**

All timing specifications are measured at characterization but not tested at final test.

Figure 42. DSP Timing in Master Mode

Table 7. DSP Timing in Master Mode (see Figure 42)

|                     | PARAMETER          |   | IOVDD=1.8V |     | IOVDD=3.3V |      |

|---------------------|--------------------|---|------------|-----|------------|------|

|                     |                    |   | MAX        | MIN | MAX        | UNIT |

| $t_d(WS)$           | WCLK delay         |   | 30         |     | 20         | ns   |

| $t_d$ (DO-BCLK)     | BCLK to DOUT delay |   | 40         |     | 20         | ns   |

| t <sub>s</sub> (DI) | DIN setup          | 8 |            | 8   |            | ns   |

| t <sub>h</sub> (DI) | DIN hold           | 8 |            | 8   |            | ns   |

| t <sub>r</sub>      | Rise time          |   | 4          |     | 4          | ns   |

| t <sub>f</sub>      | Fall time          |   | 4          |     | 4          | ns   |

Figure 43. DSP Timing in Slave Mode

| Table 8. DSP Timing in Slave Mode (see F | igure 43) |

|------------------------------------------|-----------|

|                                          | IOVDD=1.8 |

|                       | PARAMETER                              |     | 1.8V | IOVDD | =3.3V | UNIT |

|-----------------------|----------------------------------------|-----|------|-------|-------|------|

|                       | PARAMETER                              | MIN | MAX  | MIN   | MAX   | UNIT |

| t <sub>H</sub> (BCLK) | BCLK high period                       | 35  |      | 35    |       | ns   |

| t <sub>L</sub> (BCLK) | BCLK low period                        | 35  |      | 35    |       | ns   |

| t <sub>s</sub> (WS)   | (WS)                                   | 8   |      | 8     |       | ns   |

| t <sub>h</sub> (WS)   | WCLK hold                              | 8   |      | 8     |       | ns   |

| $t_d$ (DO-WS)         | WCLK to DOUT delay (For LJF Mode only) |     | 40   |       | 22    | ns   |

| t <sub>s</sub> (DI)   | DIN setup                              | 8   |      | 8     |       | ns   |

| t <sub>h</sub> (DI)   | DIN hold                               | 8   |      | 8     |       | ns   |

| t <sub>r</sub>        | Rise time                              |     | 4    |       | 4     | ns   |

| t <sub>f</sub>        | Fall time                              |     | 4    |       | 4     | ns   |

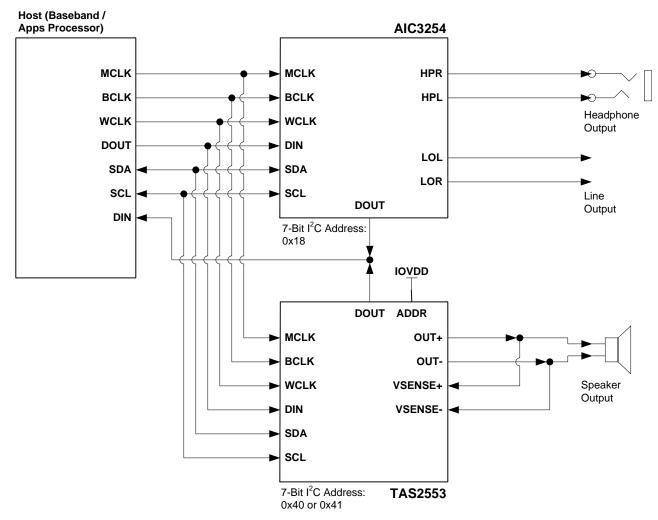

#### 7.4.2 TDM Mode

Time-division multiplexing (TDM) allows two or more devices to share a common DIN connection and a common DOUT connection. Using TDM mode, all devices transmit their DOUT data in user-specified sub-frames within one WCLK period. When one device transmits its DOUT information, the other devices place their DOUT terminals in a high impedance tri-state mode.

TDM mode is useable with I<sup>2</sup>S, LJF, RJF, and DSP interface modes. Refer to the respective sections for a description of how to set the TAS2553 into those modes. TDM cannot be used with PDM mode. This is because the PDM requires a continuous stream of samples from one data source.

Use Register 0x06 to set the clock cycle offset from WCLK to the MSB. Each data bit is valid on the falling edge of the bit clock. Set Register 0x04, D(2) = 1 to force DOUT into tri-state when it is not transmitting data. This allows DOUT terminals from multiple TAS2553 devices to share a common wire to the host.

Figure 44. Timing Diagram for I<sup>2</sup>S in TDM Mode with Offset=2

For TDM mode, the number of bit-clocks per frame should be less than the programmed word-length of the data. Also the programmed offset value should be less than the number of bit-clocks per frame by at least the programmed word-length of the data.

Figure 45 shows how to configure the TAS2553 with the TI codec, AIC3254, with both devices sharing DIN and DOUT

Figure 45. Configuration with TAS2553 and AlC3254 Muxed in TDM Mode

Figure 46. Stereo Configuration with Two TAS2553 DOUT Muxed in TDM Mode

#### 7.4.3 PDM Mode

Set Register 0x03, D(7:6) = 00 to place the TAS2553 audio interface into PDM mode. In PDM mode, the data stream is a continuous stream of undecimated pulse-modulated data that is 64x the sample rate. Because it is a continuous stream, frame synchronization is not required and WCLK is not used. Specifying clocks-per-frame is not required for PDM mode. The PDM input bit clock is IVCLKIN as set in Register 0x11, D(1:0).

The TAS2553 can be configured for I<sup>2</sup>S input mode and PDM output mode. Figure 47 shows the timing diagram for PDM input mode. Timing specifications are listed in Table 9 and Table 10.

The TAS2553 clocks PDM input data on either the rising edge or falling edge of IVCLKIN as set in Register 0x11, D(2). The device does not read concurrent data on both edges. Set the I<sup>2</sup>C register to read either rising clock edge or falling clock edge data.

Figure 47. DIN Timing Diagram in PDM Mode, Register 0x11, D(2) = 0

Figure 48. DIN Timing Diagram in PDM Mode, Register 0x11, D(2) = 1

Table 9. PDM Input Timing<sup>(1)</sup>

|                | DADAMETED | IOVDD=1.8V <sup>(2)</sup> | IOVDD=3.3V | UNIT |

|----------------|-----------|---------------------------|------------|------|

|                | PARAMETER | MIN MAX                   | MIN MAX    | UNIT |

| ts             | DIN setup | 20                        | 20         | ns   |

| t <sub>h</sub> | DIN hold  | 3                         | 3          | ns   |

| t <sub>r</sub> | Rise time | 4                         | 4          | ns   |

| t <sub>f</sub> | Fall time | 4                         | 4          | ns   |

- (1) All timing specifications are measured at characterization but not tested at final test.

- (2) All specifications at 25°C, IOVDD = 1.8 V

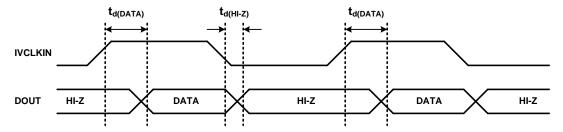

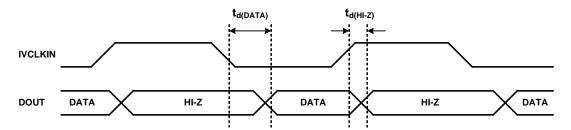

#### 7.4.3.1 DOUT Timing – PDM Output Mode

Set Register 0x03, D(6) = 0 to transmit PDM data on the DOUT terminal. Register 0x07, D(7:6) selects either I Data, V Data, or both for PDM transmission. Register 0x07, D(5) selects whether the data transmits on either the rising edge or the falling edge of IVCLKIN. The DOUT terminal becomes high-impedance on the opposing clock cycle.

Figure 49. DOUT Timing in PDM Mode (Data on IVCLKIN High)

Figure 50. DOUT Timing in PDM Mode (Data on IVCLKIN Low)

Table 10. DOUT Timing in PDM Mode<sup>(1)</sup>

| PARAMETER             |                                       | IOVDD=1.8V <sup>(2)</sup> |     | IOVDD=3.3V |     | LINIT |

|-----------------------|---------------------------------------|---------------------------|-----|------------|-----|-------|

|                       | FARAMETER                             | MIN                       | MAX | MIN        | MAX | UNIT  |

| t <sub>d</sub> (DATA) | IVCLKIN to DOUT delay                 | 30                        |     |            | 30  | ns    |

| t <sub>d</sub> (HI-Z) | IVCLKIN to high impedance state delay | 6                         |     |            | 6   | ns    |

<sup>(1)</sup> All timing specifications are measured at characterization but not tested at final test.

## 7.5 Register Map

The TAS2553  $I^2C$  address is 0x40 (7-bit) when ADDR = 0 and 0x41 (7-bit) when ADDR = 1. See the General  $I^2C$  Operation section for more details.

## 7.5.1 Register Map Summary

| REGISTER |      | DEADAMBITE | DEFAULT | FUNCTION                                   |

|----------|------|------------|---------|--------------------------------------------|

| DEC      | HEX  | READ/WRITE | DEFAULT | FUNCTION                                   |

| 0        | 0x00 | R/W        | 0x00    | Device Status Register                     |

| 1        | 0x01 | R/W        | 0x22    | Configuration Register 1                   |

| 2        | 0x02 | R/W        | 0xFF    | Configuration Register 2                   |

| 3        | 0x03 | R/W        | 0x80    | Configuration Register 3                   |

| 4        | 0x04 | R/W        | 0x00    | DOUT Tristate Mode                         |

| 5        | 0x05 | R/W        | 0x00    | Serial Interface Control Register 1        |

| 6        | 0x06 | R/W        | 0x00    | Serial Interface Control Register 2        |

| 7        | 0x07 | R/W        | 0xC0    | Output Data Register                       |

| 8        | 0x08 | R/W        | 0x10    | PLL Control Register 1                     |

| 9        | 0x09 | R/W        | 0x00    | PLL Control Register 2                     |

| 10       | 0x0A | R/W        | 0x00    | PLL Control Register 3                     |

| 11       | 0x0B | R/W        | 0x8F    | Battery Tracking Inflection Point Register |

| 12       | 0x0C | R/W        | 0x80    | Battery Tracking Slope Control Register    |

| 13       | 0x0D | R/W        | 0xBE    | Limiter Level Control Register             |

| 14       | 0x0E | R/W        | 0x08    | Limiter Attack Rate and Hysteresis Time    |

| 15       | 0x0F | R/W        | 0x05    | Limiter Release Rate                       |

| 16       | 0x10 | R/W        | 0x00    | Limiter Integration Count Control          |

| 17       | 0x11 | R/W        | 0x01    | PDM Configuration Register                 |

| 18       | 0x12 | R/W        | 0x00    | PGA Gain Register                          |

| 19       | 0x13 | R/W        | 0x40    | Class-D Edge Rate Control Register         |

| 20       | 0x14 | R/W        | 0x00    | Boost Auto-Pass Through Control Register   |

| 21       | 0x15 | R/W        | 0x00    | Reserved                                   |

| 22       | 0x16 | R          | 0x00    | Version Number                             |

| 23       | 0x17 | R/W        | 0x00    | Reserved                                   |

<sup>(2)</sup> All specifications at 25°C, IOVDD = 1.8 V

# **Register Map (continued)**

| REGISTER |      | READ/WRITE DEFAULT |         | FUNCTION           |  |

|----------|------|--------------------|---------|--------------------|--|

| DEC      | HEX  | READ/WRITE         | DEFAULT | FUNCTION           |  |

| 24       | 0x18 | R                  | 0x00    | Reserved           |  |

| 25       | 0x19 | R                  | 0x00    | VBAT Data Register |  |

## 7.5.2 Register 0x00: Device Status Register

This register uses latched faults. The fault bits are clear on write. Read-only commands retain the latched value of the fault bit.

| BIT | NAME            | READ/WRITE | DEFAULT | DESCRIPTION                                                                                  |

|-----|-----------------|------------|---------|----------------------------------------------------------------------------------------------|

| 7-6 |                 | R/W        | 00      | Reserved. Write only default values.                                                         |

| 5   | PLL_OUT_OF_LOCK | R/W        | 0       | PLL lock 0 = PLL is locked 1 = PLL is not locked                                             |

| 4-2 |                 | R/W        | 0       | Reserved. Write only default values.                                                         |

| 1   | CLASSD_ILIM     | R/W        | 0       | Class-D over-current 0 = Normal operation 1 = Class-D output current limit has been exceeded |

| 0   | THERMAL         | R/W        | 0       | Thermal limit 0 = Normal operation 1 = Limit exceeded                                        |

## 7.5.3 Register 0x01: Configuration Register 1

| BIT | NAME      | READ/WRITE | DEFAULT | DESCRIPTION                                                                                                                                                         |

|-----|-----------|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6 |           | R/W        | 00      | Reserved. Write only default values.                                                                                                                                |

| 5-4 | PLL_SRC   | R/W        | 10      | PLL Input  00 = MCLK  01 = BCLK  10 = IVCLKIN  11 = 1.8 MHz fixed internal oscillator                                                                               |

| 3   |           | R/W        | 0       | Reserved. Write only default values.                                                                                                                                |

| 2   | MUTE      | R/W        | 0       | Triggers mute of Class-D channel controller.  0 = Not muted  1 = Muted                                                                                              |

| 1   | SWS       | R/W        | 1       | Software shutdown. When high shuts down all blocks and places part in low power mode. THIS BIT MUST BE SET TO ZERO ONLY AFTER THE DEVICE CONFIGURATION IS COMPLETE. |

| 0   | DEV_RESET | R/W        | 0       | Synchronous reset of all digital registers & control circuitry.                                                                                                     |

## 7.5.4 Register 0x02: Configuration Register 2

| BIT | NAME       | READ/WRITE | DEFAULT          | DESCRIPTION                                                                                 |

|-----|------------|------------|------------------|---------------------------------------------------------------------------------------------|

| 7   | CLASSD_EN  | R/W        | 1                | Class D Enable                                                                              |

| 6   | BOOST_EN   | R/W        | 1                | Boost Enable                                                                                |

| 5   | APT_EN     | R/W        | 1                | Auto Pass-Thru Enable                                                                       |

| 4   | RESERVED   | R/W        | 0                | Reserved. Write only default values.                                                        |

| 3   | PLL_EN     | R/W        | 1                | PLL Enable                                                                                  |

| 2   | LIM_EN     | R/W        | 1                | Battery Tracking AGC Enable                                                                 |

| 1   | IVSENSE_EN | R/W        | 1                | I/V Sense Enable                                                                            |

| 0   | RESERVED   | R/W        | 1 <sup>(1)</sup> | Reserved. MUST BE WRITTEN TO ZERO DURING CONFIGURATION SEQUENCE as shown in Initialization. |

<sup>(1)</sup> Register 0x02, Bit 0 defaults to 1, but must be written to 0 during initialization.

## 7.5.5 Register 0x03: Configuration Register 3

| BIT | NAME           | READ /<br>WRITE | DEFAULT | DESCRIPTION                                                                                                                                                                       |

|-----|----------------|-----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ANALOG_IN_SEL  | R/W             | 1       | Selects analog in path for data to class-D. When set to zero (digital in), no signal should be present on the analog terminals.  0 = Digital Audio Input  1 = Analog Audio Input  |

| 6   | I2S_OUT_SEL    | R/W             | 0       | Selects between PDM and I2S for I/V Sense output data format.  0 = PDM  1 = I2S                                                                                                   |

| 5   | PDM_IN_SEL     | R/W             | 0       | Selects PDM as input to modulator<br>0 = PDM is not selected<br>1 = PDM is selected only if Digital Audio Input is selected (Reg 0x03 D[7] =<br>0)                                |

| 4-3 | DIN_SOURCE_SEL | R/W             | 00      | DIN Source Select  00 = Modulator input muted  01 = Use left stream for modulator  10 = Use right stream for modulator  11 = Use average of left and right streams for modulator  |

| 2-0 | WCLK_FREQ      | R/W             | 000     | WCLK Frequency 000 = 8 kHz 001 = 11.025 kHz / 12 kHz 010 = 16 kHz 011 = 22.05 kHz / 24 kHz 100 = 32 kHz 101 = 44.1 kHz / 48 kHz 110 = 88.2 kHz / 96 kHz 111 = 176.4 kHz / 192 kHz |

## 7.5.6 Register 0x04: DOUT Tristate Mode

For systems with multiple devices sharing a common DOUT line with a TDM interface mode, set Bit 2 to 1 to ensure DOUT stays in high-impedance tri-state mode when it is not transmitting data.

| BIT | NAME           | READ /<br>WRITE | DEFAULT | DESCRIPTION                                                                                                                                                       |

|-----|----------------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-3 |                | R/W             | 0000 0  | Reserved. Write only default values.                                                                                                                              |

| 2   | SDOUT_TRISTATE | R/W             | 0       | DOUT Tri-state Mode (for I2S mode only, see Reg 0x03, bit 7) 0 = DOUT set to logic low when not transmitting data 1 = DOUT in tristate when not transmitting data |

| 1-0 |                | R/W             | 00      | Reserved. Write only default values.                                                                                                                              |

## 7.5.7 Register 0x05: Serial Interface Control Register 1

| BIT | NAME         | READ/WRITE | DEFAULT | DESCRIPTION                                                                                                              |

|-----|--------------|------------|---------|--------------------------------------------------------------------------------------------------------------------------|

| 7   | WCLKDIR      | R/W        | 0       | WCLK Direction 0 = WCLK is an input terminal 1 = WCLK is an output terminal                                              |

| 6   | BCLKDIR      | R/W        | 0       | BCLK Direction 0 = BCLK is an input terminal 1 = BCLK is an output terminal                                              |

| 5-4 | CLKSPERFRAME | R/W        | 00      | Clocks per Frame 00 = 32 clocks 01 = 64 clocks 10 = 128 clocks 11 = 256 clocks                                           |

| 3-2 | DATAFORMAT   | R/W        | 00      | Data Format  00 = I2S format  01 = DSP (PCM format)  10 = Right justified format (RJF)  11 = Left justified format (LJF) |

| 1-0 | WORDLENGTH   | R/W        | 00      | Word Length 00 = 16 bits 01 = 20 bits 10 = 24 bits 11 = 32 bits                                                          |

## 7.5.8 Register 0x06: Serial Interface Control Register 2