## 14.2GBPS 双通道、双模线性均衡器

查询样品: [SN65LVCP1412](#)

### 特性

- 背板和线缆连接串行数据速率高达 **14.2Gbps** 的双通道、单向、多速率、双模线性均衡器

- 线性均衡增加了系统执行判决反馈均衡器 (**DFE**) 时的链路裕量

- 针对背板模式或者线缆模式，在具有 **1dB** 阶跃控制的 **7.1GHz** 上可实现 **18dB** 模拟均衡

- 输出线性动态范围: **1200mV**

- 带宽: **>20GHz** - 典型值

- **7.1GHz** 上, 好于 **15dB** 的回波损耗

- 支持带外 (**OOB**) 信令

- 低功耗: **2.5V VCC** 时, 每通道为 **75mW** (典型值)

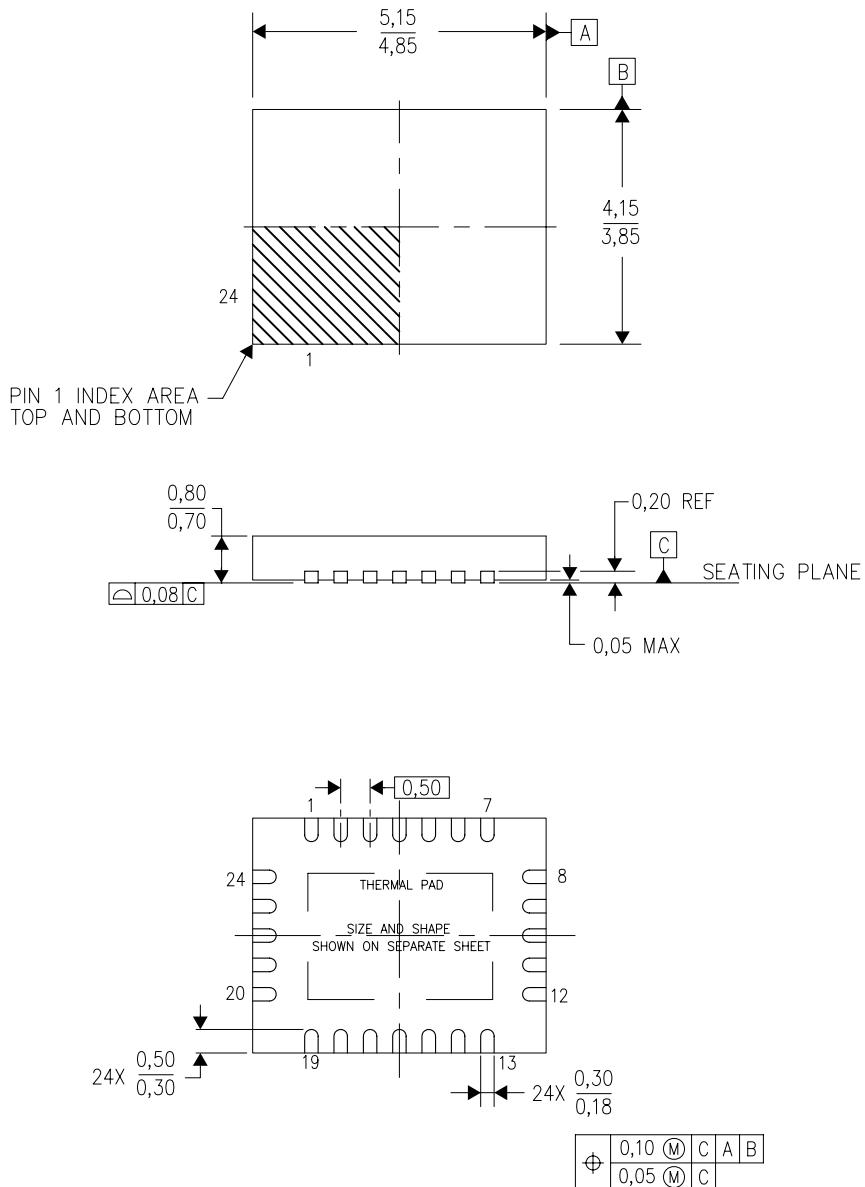

- **24** 端子 **QFN** (四方扁平、无引线)

**4mm x 5mm x 0.75mm; 0.5mm** 端子间距

- 到 **100Ω** 差分印刷电路板 (**PCB**) 传输线路的出色阻抗匹配

- 通用输入输出接口 (**GPIO**) 或者 **I<sup>2</sup>C** 控制

- **2.5V** 和 **3.3V±5%** 单电源

- **2kV** 静电放电 (**ESD**) 人体模型 (**HBM**)

- 流经阳引脚的数据流简化了路由访问

- 小型封装尺寸节省了电路板空间

### 应用范围

- 电信和数据通信中的高速连接

- 针对 **10GbE, 16GFC, 10G SONET, SAS, SATA, CPRI, OBSAI, Infiniband, 10GBase-KR, 和 XFI/SFI** 的背板和线缆连接

### 说明

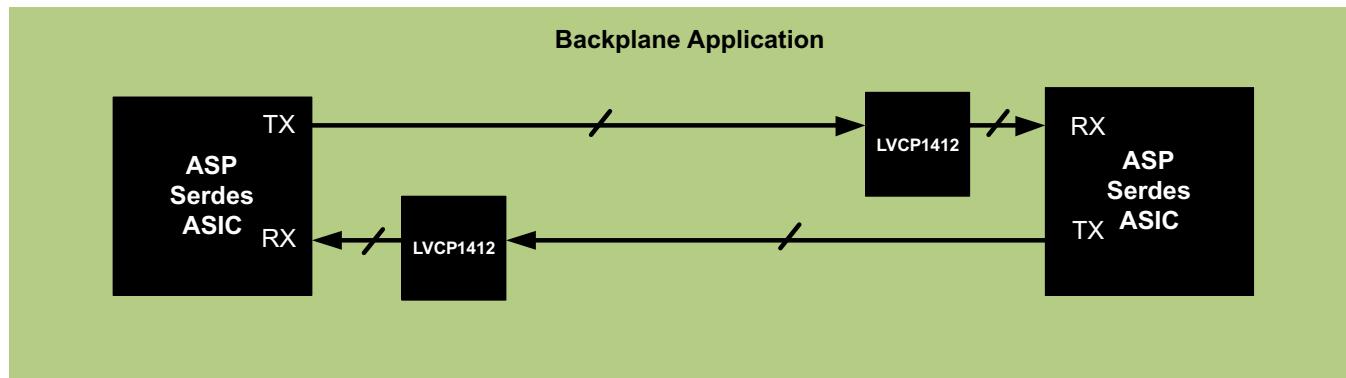

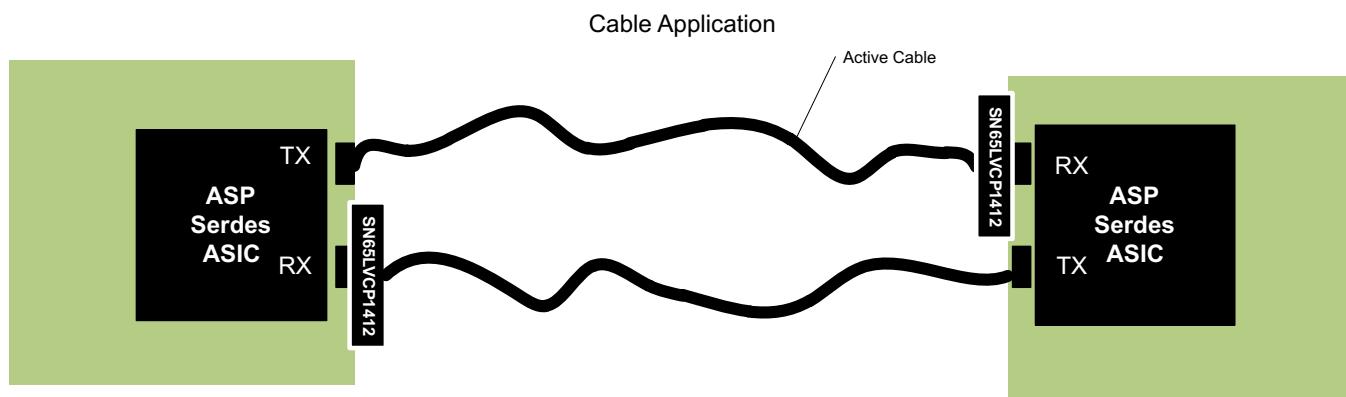

SN65LVCP1412 是一款异步、协议无关、低延迟、两通道线性均衡器，此均衡器针对高达 **14.2Gbps** 的数据速率和为背板或有源线缆应用中损耗的补偿进行了优化。SN65LVCP1412 的架构设计用于与一个特定用途集成电路 (**ASIC**) 或者一个现场可编程栅极阵列 (**FPGA**) (采用判决反馈均衡器 (**DFE**) 来实现数字均衡) 一起运行。

SN65LVCP1412 线性均衡器保持已发送信号的形状以确保最优 **DFE** 性能。SN65LVCP1412 在充分发挥 **DFE** 效率的同时提供了一个低功耗的解决方案。

SN65LVCP1412 可经由 **I<sup>2</sup>C** 或者 **GPIO** 接口进行配置。SN65LVCP1412 的 **I<sup>2</sup>C** 接口使得用户能够针对每个独立通道独立地控制均衡、路径增益和输出动态范围。在 **GPIO** 模式下，通过使用 **GPIO** 输入引脚，可为所有通道设置均衡、路径增益、和输出动态范围。

SN65LVCP1412 输出可由 **I<sup>2</sup>C** 单独禁用。

SN65LVCP1412 在一个 **2.5V** 或者 **3.3V** 单电源下运行。

SN65LVCP1412 采用 **24** 引脚 **4mm x 5mm x 0.75mm QFN** (四方扁平无引线) 无铅 **0.5mm** 焊球间距封装，额定运行温度 **-40°C** 至 **85°C**。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

**Figure 1. Typical Backplane Application – Trace Mode**

**Figure 2. Typical Cable Application – Cable Mode**

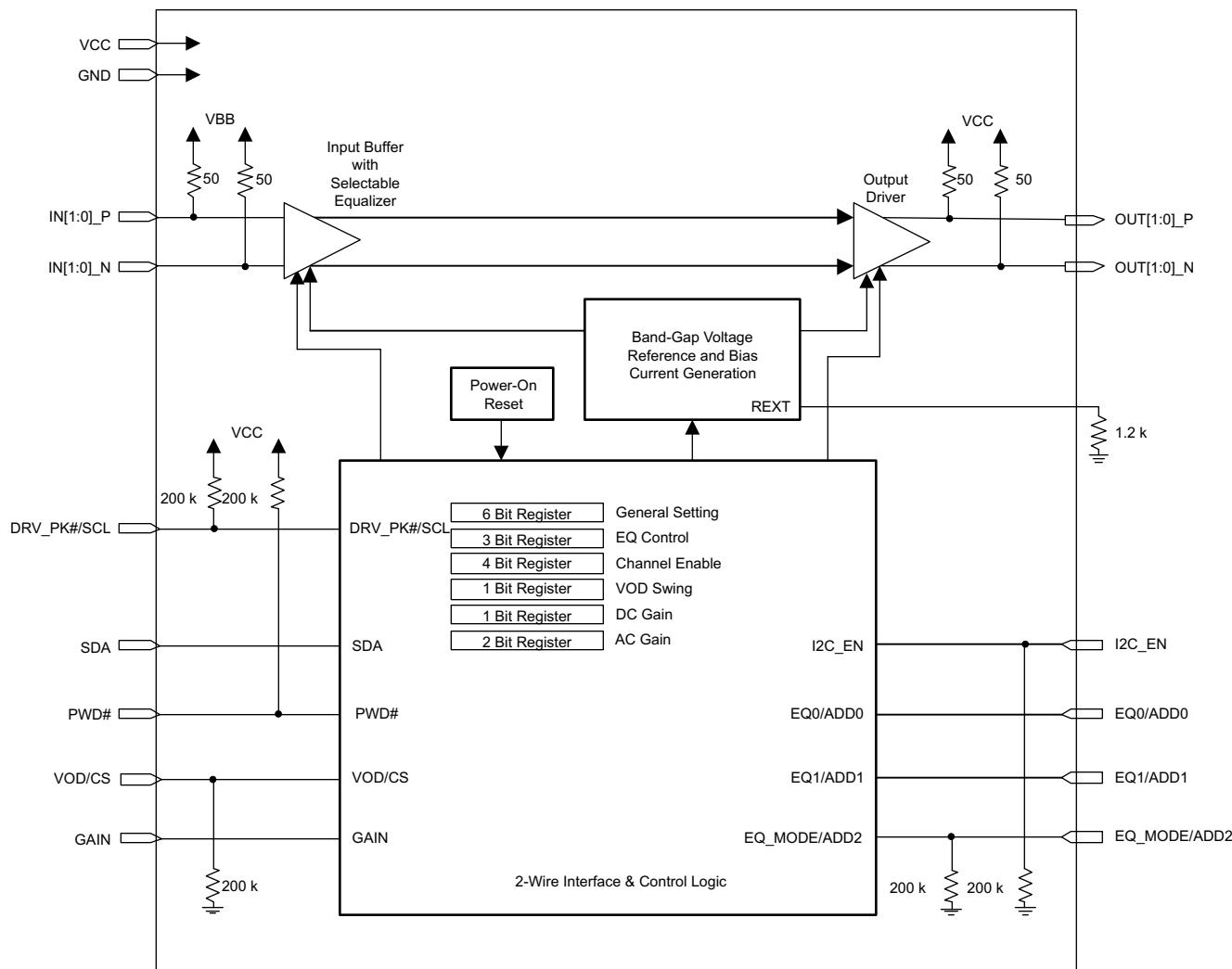

## BLOCK DIAGRAM (GPIO or I<sup>2</sup>C Mode)

A simplified block diagram of the SN65LVCP1412 is shown in [Figure 3](#) for GPIO or I<sup>2</sup>C input control mode. This compact, low power, 14.2Gbps dual-channel dual-mode linear analog equalizer consists of two high-speed data paths and an input GPIO pin logic-control block and a two-wire interface with a control-logic block.

**Figure 3. Simplified Block Diagram of the SN65LVCP1412**

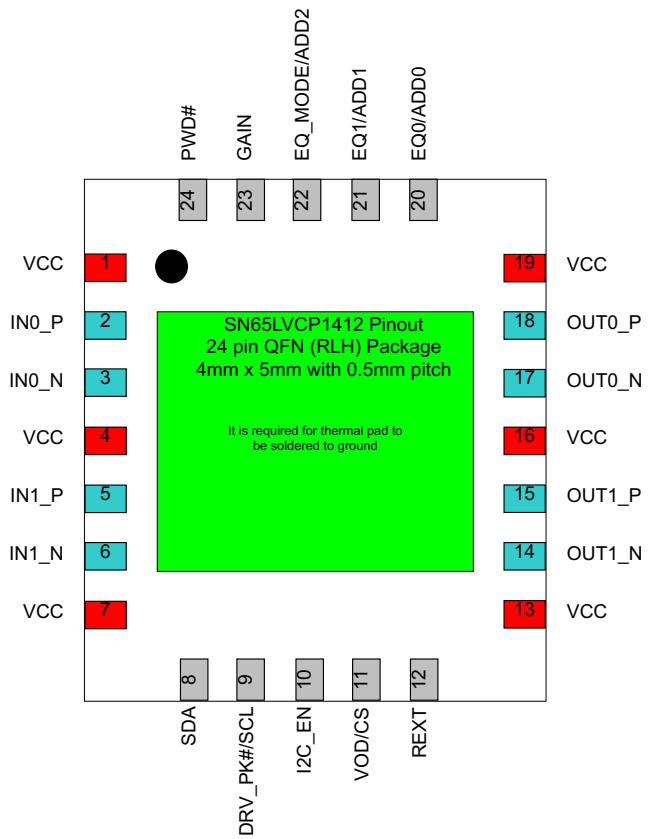

## PACKAGE

The package pin locations and assignments are shown in [Figure 4](#). The SN65LVCP1412 is packaged in a 4mm x 5mm x 0.75mm, 24 pin, 0.5mm pitch lead-free QFN.

**Figure 4. Package Drawing (Top View)**

## PIN DESCRIPTIONS

| PINS                   |     | DIRECTION TYPE<br>SUPPLY                        | DESCRIPTION                                                                                                                                                                                |

|------------------------|-----|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                   | NO. | DIFFERENTIAL HIGH-SPEED I/O                     |                                                                                                                                                                                            |

| <b>CONTROL SIGNALS</b> |     |                                                 |                                                                                                                                                                                            |

| SDA                    | 8   | Input Output, Open drain                        | <b>GPIO mode</b><br>No action needed<br><b>I<sup>2</sup>C mode</b><br>I <sup>2</sup> C data. Connect a 10kΩ pull-up resistor externally                                                    |

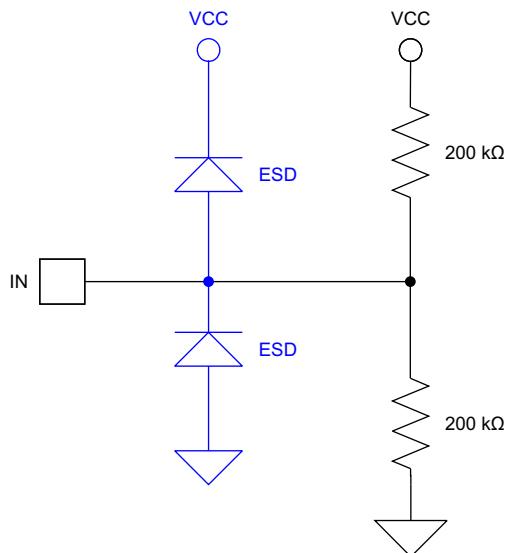

| DRV_PK#/SCL            | 9   | Input. (with 200kΩ pull-up)                     | <b>GPIO mode</b><br>HIGH: disable Driver peaking<br>LOW: enables Driver 6dB AC peaking<br><b>I<sup>2</sup>C mode</b><br>I <sup>2</sup> C clock. Connect a 10kΩ pull-up resistor externally |

| I2C_EN                 | 10  | Input, (with 200kΩ pull-down)<br>2.5V/3.3V CMOS | Configures the device operation for I <sup>2</sup> C or GPIO mode:<br>HIGH: enables I <sup>2</sup> C mode<br>LOW: enables GPIO mode                                                        |

**PIN DESCRIPTIONS (continued)**

| PINS                                                                                                                                                                                                                                                                                                                                                              |                           | DIRECTION TYPE<br>SUPPLY                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|--------------------|-----------------|-----------|-----|-----|-------|-----------|-----|-----|--------|-----------|------|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                              | NO.                       |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| VOD/CS                                                                                                                                                                                                                                                                                                                                                            | 11                        | Input, (with 200kΩ pull-down)<br>2.5V/3.3V CMOS  | <b>GPIO mode</b><br>HIGH: set high VOD range<br>LOW: set low VOD range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>I<sup>2</sup>C mode</b><br>HIGH: acts as Chip Select<br>LOW: disables I <sup>2</sup> C interface                                               |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| REXT                                                                                                                                                                                                                                                                                                                                                              | 12                        | Input, Analog                                    | External Bias Resistor:<br>1,200 Ω to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| EQ0/ADD0                                                                                                                                                                                                                                                                                                                                                          | 20                        | Input, 2.5V/3.3V CMOS - 3-state                  | <b>GPIO mode</b><br>Working with EQ1 to determine input EQ gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>I<sup>2</sup>C mode</b><br>ADD0 along with pins ADD1 and ADD2 comprise the three bits of I <sup>2</sup> C slave address.<br>ADD2:ADD1:ADD0:XXX |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| EQ1/ADD1                                                                                                                                                                                                                                                                                                                                                          | 21                        | Input, 2.5V/3.3V CMOS - 3-state                  | <b>GPIO mode</b><br>Working with EQ0 to determine input EQ gain steps of approximately 2dB<br><br><table border="1" data-bbox="605 633 897 992"> <tr> <th>EQ1</th><th>EQ0</th><th>EQ GAIN</th></tr> <tr><td>GND</td><td>GND</td><td>000</td></tr> <tr><td>GND</td><td>HiZ</td><td>000</td></tr> <tr><td>GND</td><td>VCC</td><td>001</td></tr> <tr><td>HiZ</td><td>GND</td><td>010</td></tr> <tr><td>HiZ</td><td>HiZ</td><td>011</td></tr> <tr><td>HiZ</td><td>VCC</td><td>100</td></tr> <tr><td>VCC</td><td>GND</td><td>101</td></tr> <tr><td>VCC</td><td>HiZ</td><td>110</td></tr> <tr><td>VCC</td><td>VCC</td><td>111</td></tr> </table> | EQ1                                                                                                                                               | EQ0         | EQ GAIN | GND                | GND             | 000       | GND | HiZ | 000   | GND       | VCC | 001 | HiZ    | GND       | 010  | HiZ | HiZ   | 011 | HiZ | VCC | 100 | VCC | GND | 101 | VCC | HiZ | 110 | VCC | VCC | 111 | <b>I<sup>2</sup>C mode</b><br>ADD1 along with pins ADD0 and ADD2 comprise the three bits of I <sup>2</sup> C slave address<br>ADD2:ADD1:ADD0:XXX |

| EQ1                                                                                                                                                                                                                                                                                                                                                               | EQ0                       | EQ GAIN                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| GND                                                                                                                                                                                                                                                                                                                                                               | GND                       | 000                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| GND                                                                                                                                                                                                                                                                                                                                                               | HiZ                       | 000                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| GND                                                                                                                                                                                                                                                                                                                                                               | VCC                       | 001                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| HiZ                                                                                                                                                                                                                                                                                                                                                               | GND                       | 010                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| HiZ                                                                                                                                                                                                                                                                                                                                                               | HiZ                       | 011                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| HiZ                                                                                                                                                                                                                                                                                                                                                               | VCC                       | 100                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| VCC                                                                                                                                                                                                                                                                                                                                                               | GND                       | 101                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| VCC                                                                                                                                                                                                                                                                                                                                                               | HiZ                       | 110                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| VCC                                                                                                                                                                                                                                                                                                                                                               | VCC                       | 111                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| EQ1 and EQ0 work with AC_GAIN and DC_GAIN to determine final EQ gain as this:                                                                                                                                                                                                                                                                                     |                           |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| <table border="1" data-bbox="605 1034 1003 1214"> <tr> <th>EQ1/<br/>EQ0</th><th>GAIN</th><th>DC<br/>GAIN<br/>(dB)</th><th>EQ GAIN<br/>(dB)</th></tr> <tr><td>000 ~ 111</td><td>LOW</td><td>-6</td><td>1 ~ 9</td></tr> <tr><td>000 ~ 111</td><td>HiZ</td><td>-6</td><td>7 ~ 17</td></tr> <tr><td>000 ~ 111</td><td>HIGH</td><td>0</td><td>1 ~ 9</td></tr> </table> |                           |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   | EQ1/<br>EQ0 | GAIN    | DC<br>GAIN<br>(dB) | EQ GAIN<br>(dB) | 000 ~ 111 | LOW | -6  | 1 ~ 9 | 000 ~ 111 | HiZ | -6  | 7 ~ 17 | 000 ~ 111 | HIGH | 0   | 1 ~ 9 |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| EQ1/<br>EQ0                                                                                                                                                                                                                                                                                                                                                       | GAIN                      | DC<br>GAIN<br>(dB)                               | EQ GAIN<br>(dB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| 000 ~ 111                                                                                                                                                                                                                                                                                                                                                         | LOW                       | -6                                               | 1 ~ 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| 000 ~ 111                                                                                                                                                                                                                                                                                                                                                         | HiZ                       | -6                                               | 7 ~ 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| 000 ~ 111                                                                                                                                                                                                                                                                                                                                                         | HIGH                      | 0                                                | 1 ~ 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| EQ_MODE/<br>ADD2                                                                                                                                                                                                                                                                                                                                                  | 22                        | Input, (with 200kΩ pull-down),<br>2.5V/3.3V CMOS | <b>GPIO mode</b><br>HIGH: Trace mode<br>LOW: Cable mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>I<sup>2</sup>C mode</b><br>ADD2 along with pins ADD1 and ADD0 comprise the three bits of I <sup>2</sup> C slave address.<br>ADD2:ADD1:ADD0:XXX |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| GAIN                                                                                                                                                                                                                                                                                                                                                              | 23                        | Input, 2.5V/3.3V CMOS - 3-state                  | <b>GPIO mode</b><br>Work with EQ1/EQ0 to set total EQ Gain. See table above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>I<sup>2</sup>C mode</b><br>No action needed                                                                                                    |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| PWD#                                                                                                                                                                                                                                                                                                                                                              | 24                        | Input, (with 200kΩ pull-up),<br>2.5V/3.3V CMOS   | HIGH: Normal Operation<br>LOW: Powers down the device, inputs off and outputs disabled, resets I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| <b>POWER SUPPLY</b>                                                                                                                                                                                                                                                                                                                                               |                           |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| VCC                                                                                                                                                                                                                                                                                                                                                               | 1, 4, 7,<br>13, 16,<br>19 | Power                                            | Power supply 2.5V±5%, 3.3V±5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

| GND Center<br>Pad                                                                                                                                                                                                                                                                                                                                                 |                           | Ground                                           | The ground center pad is the metal contact at the bottom of the package. This pad must be connected to the GND plane. At least 9 PCB vias are recommended to minimize inductance and provide a solid ground. Refer to the package drawing (RLH-package) for the via placement.                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                   |             |         |                    |                 |           |     |     |       |           |     |     |        |           |      |     |       |     |     |     |     |     |     |     |     |     |     |     |     |     |                                                                                                                                                  |

## ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                               |                                                                          | VALUES                               | UNIT |

|-----------------------------------------------|--------------------------------------------------------------------------|--------------------------------------|------|

| $V_{CC}$                                      | Supply voltage range <sup>(2)</sup>                                      | -0.3 to 4                            | V    |

| $V_{IN,DIFF}$                                 | Differential Voltage between $IN_x_P$ and $IN_x_N$                       | $\pm 2.5$                            | V    |

| $V_{IN+}, IN_-$                               | Voltage at $IN_x_P$ and $fIN_x_N$                                        | -0.5 V to $V_{CC}+0.5$               | V    |

| $V_{IO}$                                      | Voltage on Control IO pins                                               | -0.5 V to $V_{CC}+0.5$               | V    |

| $I_{IN+}, I_{IN-}$                            | Continuous Current at high speed differential data inputs (differential) | -25 to 25                            | mA   |

| $I_{OUT+}, I_{OUT-}$                          | Continuous Current at high speed differential data outputs               | -25 to 25                            | mA   |

| ESD                                           | Human Body Model <sup>(3)</sup> (All Pins)                               | 2.0                                  | kV   |

|                                               | Charged-Device Model <sup>(4)</sup> (All Pins)                           | 500                                  | V    |

| Moisture Sensitivity level                    |                                                                          | 2                                    |      |

| Shelf Life Conditions In Moisture Barrier Bag |                                                                          | 24 Months at <40°C and <90% Humidity |      |

| Reflow Temperature package soldering, 4 sec   |                                                                          | 260                                  | °C   |

- (1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

- (3) Tested in accordance with JEDEC Standard 22, Test Method A114-A.

- (4) Tested in accordance with JEDEC Standard 22, Test Method C101.

## THERMAL INFORMATION

| THERMAL METRIC <sup>(1)</sup> |                                                             | SN65LVCP1412 | UNITS |

|-------------------------------|-------------------------------------------------------------|--------------|-------|

|                               | RLH (24 PINS)                                               |              |       |

| $\theta_{JA}$                 | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 34.7         | °C/W  |

| $\theta_{JCtop}$              | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 33.8         |       |

| $\theta_{JB}$                 | Junction-to-board thermal resistance <sup>(4)</sup>         | 12.5         |       |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.50         |       |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter <sup>(6)</sup> | 12.5         |       |

| $\theta_{JCbot}$              | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 2.00         |       |

- (1) 有关传统和新的热 度量的更多信息 , 请参阅 IC 封装热度量应用报告 , [SPRA953](#)。

- (2) 在 JESD51-2a 描述的环境中 , 按照 JESD51-7 的指定 , 在一个 JEDEC 标准高 K 电路板上进行仿真 , 从而获得自然 对流条件下的结至环境热阻。

- (3) 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳 ( 顶部 ) 的热阻。不存在特定的 JEDEC 标准测试 , 但 可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

- (4) 按照 JESD51-8 中的说明 , 通过 在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真 , 以获得结板热阻。

- (5) 结至顶部特征参数 ,  $\Psi_{JT}$  , 估算真实系统中器件的结温 , 并使用 JESD51-2a ( 第 6 章和第 7 章 ) 中 描述的程序从仿真数据中 提取出该参数以便获得  $\theta_{JA}$ 。

- (6) 结至电路板特征参数 ,  $\Psi_{JB}$  , 估算真实系统中器件的结温 , 并使用 JESD51-2a ( 第 6 章和第 7 章 ) 中 描述的程序从仿真数据中 提取出该参数以便获得  $\theta_{JA}$ 。

- (7) 通过在外露 ( 电源 ) 焊盘上进行冷板测试仿真来获得 结至芯片外壳 ( 底部 ) 热阻。不存在特定的 JEDEC 标准 测试 , 但可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

**RECOMMENDED OPERATING CONDITIONS**

|                               |                           | MIN                  | NOM                  | MAX   | UNIT |

|-------------------------------|---------------------------|----------------------|----------------------|-------|------|

| dR                            | Operating Data Rate       |                      |                      | 14.2  | Gbps |

| V <sub>CC</sub>               | Supply voltage            | 2.375                | 2.5                  | 2.625 | V    |

| V <sub>CC</sub>               | Supply voltage            | 3.135                | 3.3                  | 3.465 | V    |

| TC                            | Junction temperature      | -10                  |                      | 125   | °C   |

| TB                            | Maximum board temperature |                      |                      | 85    | °C   |

| <b>CMOS DC SPECIFICATIONS</b> |                           |                      |                      |       |      |

| V <sub>IH</sub>               | High-level input voltage  | 0.8×V <sub>CC</sub>  |                      |       | V    |

| V <sub>MID</sub>              | Mid-level input voltage   | V <sub>CC</sub> ×0.4 | V <sub>CC</sub> ×0.6 |       | V    |

| V <sub>IL</sub>               | Low-level input voltage   | -0.5                 | 0.2×V <sub>CC</sub>  |       | V    |

| PSNR BG                       | Bandgap Circuit PSNR      | 20                   |                      |       | dB   |

**ELECTRICAL CHARACTERISTICS (VCC 2.5V ±5%)**

over operating free-air temperature range. All parameters are referenced to package pins. (unless otherwise noted)

| PARAMETER                | TEST CONDITIONS                               | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|--------------------------|-----------------------------------------------|-----|--------------------|-----|------|

| <b>POWER CONSUMPTION</b> |                                               |     |                    |     |      |

| PD <sub>L</sub>          | Device power dissipation                      | 150 | 250                |     | mW   |

| PD <sub>H</sub>          | Device power dissipation                      | 225 | 400                |     | mW   |

| PD <sub>OFF</sub>        | Device power with all 4 channels switched off | 5   |                    |     | mW   |

(1) All typical values are at 25°C and with 2.5V supply unless otherwise noted.

**ELECTRICAL CHARACTERISTICS (VCC 3.3V ±5%)**

over operating free-air temperature range. All parameters are referenced to package pins. (unless otherwise noted)

| PARAMETER                | TEST CONDITIONS                               | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|--------------------------|-----------------------------------------------|-----|--------------------|-----|------|

| <b>POWER CONSUMPTION</b> |                                               |     |                    |     |      |

| PD <sub>L</sub>          | Device power dissipation                      | 225 | 375                |     | mW   |

| PD <sub>H</sub>          | Device power dissipation                      | 330 | 525                |     | mW   |

| PD <sub>OFF</sub>        | Device power with all 4 channels switched off | 5   |                    |     | mW   |

(1) All typical values are at 25°C and with 2.5V supply unless otherwise noted.

**ELECTRICAL CHARACTERISTICS (VCC 2.5V ±5%, 3.3V ±5%)**

over operating free-air temperature range. All parameters are referenced to package pins. (unless otherwise noted)

| PARAMETER                                | TEST CONDITIONS                              | MIN                  | TYP <sup>(1)</sup> | MAX | UNIT             |

|------------------------------------------|----------------------------------------------|----------------------|--------------------|-----|------------------|

| <b>CMOS DC SPECIFICATIONS</b>            |                                              |                      |                    |     |                  |

| I <sub>IH</sub>                          | VIN = 0.9 × V <sub>CC</sub>                  | -40                  | 17                 | 40  | µA               |

| I <sub>IL</sub>                          | VIN = 0.1 × V <sub>CC</sub>                  | -40                  | 17                 | 40  | µA               |

| <b>CML INPUTS (IN[3:0]_P, IN[3:0]_N)</b> |                                              |                      |                    |     |                  |

| r <sub>IN</sub>                          | INx_P to INx_N                               | 100                  |                    |     | Ω                |

| V <sub>IN</sub>                          | Gain = 0.5                                   | 1200                 |                    |     | mV <sub>pp</sub> |

| V <sub>ICM</sub>                         | Internally biased                            | V <sub>CC</sub> -0.8 |                    |     | V                |

| SCD11                                    | Input differential to common mode conversion | -20                  |                    |     | dB               |

| SDD11                                    | Differential input return loss               | -15                  |                    |     | dB               |

(1) All typical values are at 25°C and with 2.5V and 3.3V supply unless otherwise noted.

## ELECTRICAL CHARACTERISTICS (VCC 2.5V $\pm$ 5%, 3.3V $\pm$ 5%) (continued)

over operating free-air temperature range. All parameters are referenced to package pins. (unless otherwise noted)

| PARAMETER                                   | TEST CONDITIONS                                                                               | MIN                                                                                                                                                                                                              | TYP <sup>(1)</sup>   | MAX   | UNIT              |

|---------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|-------------------|

| <b>CML OUTPUTS (OUT[3:0]_P, OUT[3:0]_N)</b> |                                                                                               |                                                                                                                                                                                                                  |                      |       |                   |

| V <sub>OD</sub>                             | R <sub>L</sub> = 100 $\Omega$ , V <sub>OD</sub> = HIGH                                        |                                                                                                                                                                                                                  | 1200                 |       | mV <sub>pp</sub>  |

|                                             | R <sub>L</sub> = 100 $\Omega$ , V <sub>OD</sub> = LOW                                         |                                                                                                                                                                                                                  | 600                  |       | mV <sub>pp</sub>  |

| V <sub>OS</sub>                             | R <sub>L</sub> = 100 $\Omega$ , 0 V applied at inputs                                         |                                                                                                                                                                                                                  | 10                   |       | mV <sub>pp</sub>  |

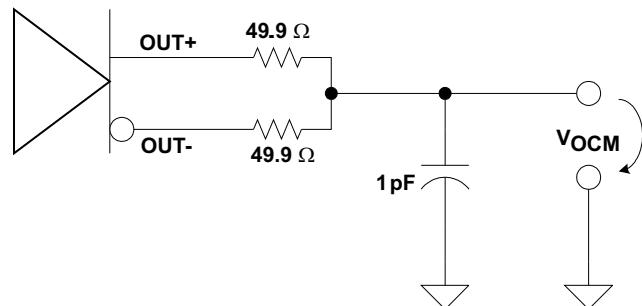

| V <sub>OCM</sub>                            | See <a href="#">Figure 5</a>                                                                  |                                                                                                                                                                                                                  | V <sub>CC</sub> -0.4 |       | V                 |

| V <sub>CM,RIP</sub>                         | K28.5 pattern at 14.2Gbps on all 4 channels, no interconnect loss, VOD = HIGH                 |                                                                                                                                                                                                                  | 10                   | 20    | mV <sub>RMS</sub> |

| V <sub>OD,RIP</sub>                         | K28.5 pattern at 14.2Gbps on all channels, no interconnect loss, VIN = 1200mV <sub>pp</sub> . |                                                                                                                                                                                                                  |                      | 20    | mV <sub>pp</sub>  |

| V <sub>OC(ss)</sub>                         | Change in steady-state common-mode output voltage between logic states                        |                                                                                                                                                                                                                  | $\pm$ 10             |       | mV                |

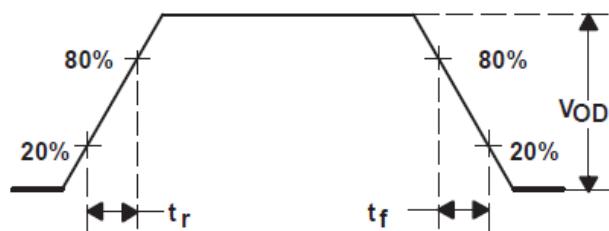

| t <sub>R</sub>                              | Rise time <sup>(2)</sup>                                                                      | Input signal with 30ps rise time. 20% to 80%. See <a href="#">Figure 7</a>                                                                                                                                       | 31                   |       | ps                |

| t <sub>F</sub>                              | Fall time <sup>(2)</sup>                                                                      | Input signal with 30ps fall time. 20% to 80%. See <a href="#">Figure 7</a>                                                                                                                                       | 32                   |       | ps                |

| SDD22                                       | Differential output return loss                                                               | 100MHz to 7.1GHz                                                                                                                                                                                                 |                      | -15   | dB                |

| SCC22                                       | Common-mode output return loss                                                                | 100MHz to 7.1GHz                                                                                                                                                                                                 |                      | -8    | dB                |

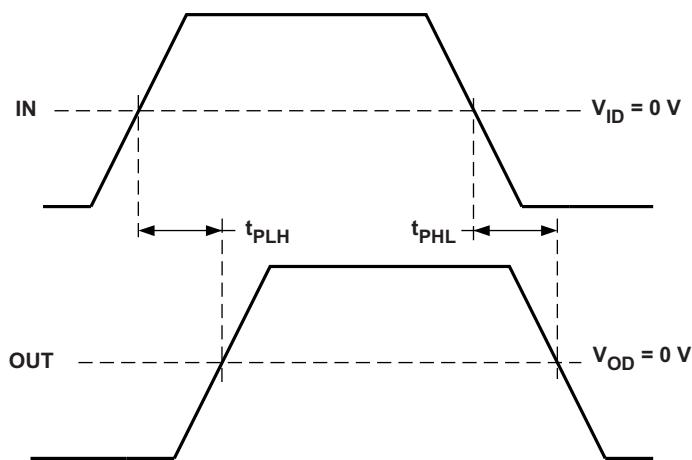

| t <sub>PLH</sub>                            | Low-to-high propagation delay                                                                 | See <a href="#">Figure 6</a>                                                                                                                                                                                     | 65                   |       | ps                |

| t <sub>PHL</sub>                            | High-to-low propagation delay                                                                 |                                                                                                                                                                                                                  | 65                   |       | ps                |

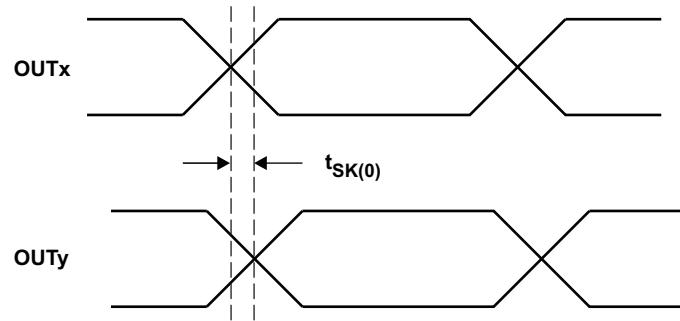

| t <sub>SK(O)</sub>                          | Inter-Pair (lane to lane) output skew <sup>(3)</sup>                                          | All outputs terminated with 100 $\Omega$ , See <a href="#">Figure 8</a>                                                                                                                                          | 3                    |       | ps                |

| t <sub>SK(PP)</sub>                         | Part-to-part skew <sup>(4)</sup>                                                              | All outputs terminated with 100 $\Omega$                                                                                                                                                                         |                      | 50    | ps                |

| r <sub>OT</sub>                             | Single ended output resistance                                                                | Single ended on-chip termination to VCC. Outputs will be AC coupled.                                                                                                                                             |                      | 50    | $\Omega$          |

| r <sub>OM</sub>                             | Output termination mismatch at 1MHz                                                           | $\Delta r_{OM} = 2 \times \frac{rp - rn}{rp + rn} \times 100$                                                                                                                                                    |                      | 5     | %                 |

| Ch <sub>iso</sub>                           | Channel-to-channel isolation                                                                  | Frequency at 7.1GHz                                                                                                                                                                                              | 35                   | 45    | dB                |

| OUT <sub>NOISE</sub>                        | Output referred noise <sup>(5)</sup>                                                          | 10MHz to 7.1GHz. No other noise source present. VOD = LOW                                                                                                                                                        |                      | 400   | $\mu$ VRMS        |

|                                             |                                                                                               | 10MHz to 7.1GHz. No other noise source present. VOD = HIGH                                                                                                                                                       |                      | 500   | $\mu$ VRMS        |

| <b>EQUALIZATION</b>                         |                                                                                               |                                                                                                                                                                                                                  |                      |       |                   |

| EQ <sub>Gain</sub>                          | At 7.1GHz input signal                                                                        | Equalization Gain, EQ = MAX                                                                                                                                                                                      | 15                   | 18    | dB                |

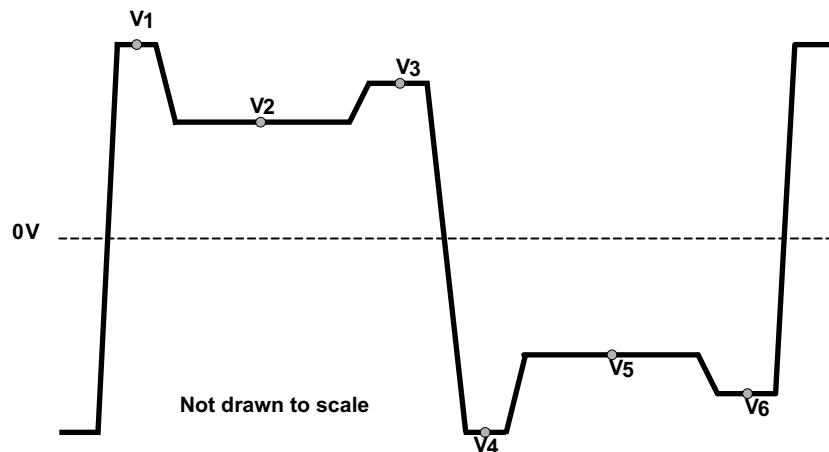

| V <sub>pre</sub>                            | Output pre-cursor pre-emphasis                                                                | Input signal with 3.75 pre-cursor and measure it on the output signal, Refer <a href="#">Figure 9</a> . V <sub>pre</sub> = 20log(V3/V2)                                                                          |                      | 3.75  | dB                |

| V <sub>pst</sub>                            | Output post-cursor pre-emphasis                                                               | Input signal with 12dB post-cursor and measure it on the output signal, Refer <a href="#">Figure 9</a> . V <sub>pst</sub> = 20log(V1/V2)                                                                         |                      | 12    | dB                |

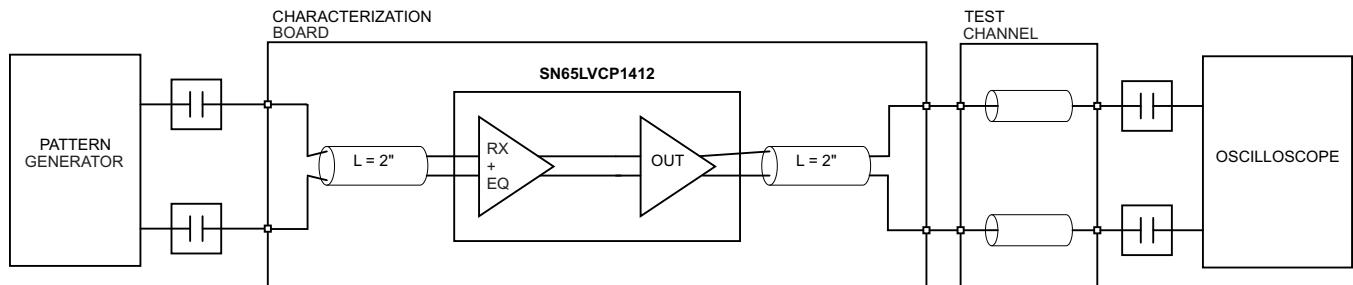

| DJ1                                         | Residual deterministic jitter at 10.3125 Gbps                                                 | Transmit Side application<br>Tx launch Amplitude = 0.6V <sub>pp</sub> , EQ=0, ACGain and DCgain = Low and VOD = High, Trace Mode Test Channel $\rightarrow$ 0". See <a href="#">Figure 11</a>                    |                      | 0.016 | Ulp-p             |

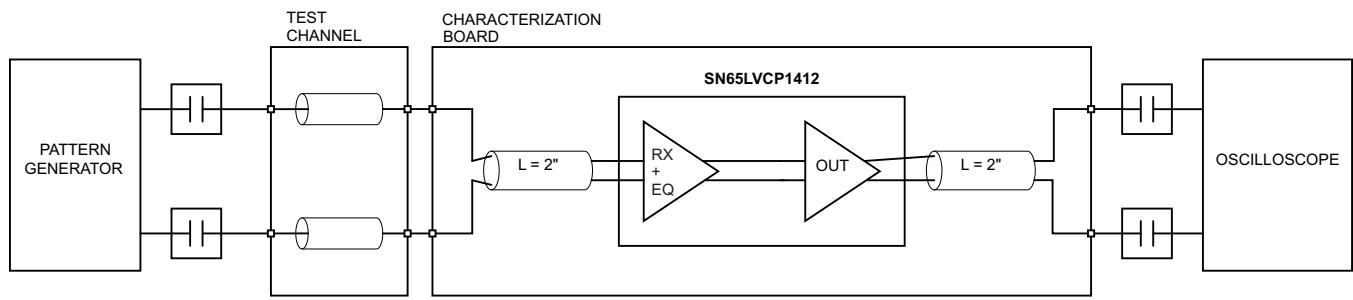

| DJ2                                         | Residual deterministic jitter at 10.3125 Gbps                                                 | Receive Side Application<br>Tx launch Amplitude = 0.6V <sub>pp</sub> , EQ=7, ACGain and VOD = High and DCgain = High, Trace Mode Test Channel $\rightarrow$ 12" (9dB loss at 5GHz) See <a href="#">Figure 10</a> |                      | 0.11  | Ulp-p             |

| DJ3                                         | Residual Deterministic Jitter at 14.2 Gbps                                                    | Transmit Side Application<br>Tx launch Amplitude = 0.6V <sub>pp</sub> , EQ=0, ACGain and DCgain = Low and VOD = High, Trace Mode Test Channel $\rightarrow$ 0". See <a href="#">Figure 11</a>                    |                      | 0.041 | Ulp-p             |

| DJ4                                         | Residual Deterministic Jitter at 14.2 Gbps                                                    | Receive Side Application<br>Tx launch Amplitude = 0.6V <sub>pp</sub> , EQ=7, ACGain and VOD = High and DCgain = High, Trace Mode Test Channel $\rightarrow$ 8" (9dB loss at 7GHz) See <a href="#">Figure 10</a>  |                      | 0.13  | Ulp-p             |

(2) Rise and Fall measurements include board and channel effects of the test environment, refer to [Figure 10](#) and [Figure 11](#)

(3) t<sub>SK(O)</sub> is the magnitude of the time difference between the channels.

(4) t<sub>SK(PP)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

(5) All noise sources added.

## PARAMETER MEASUREMENT INFORMATION

Figure 5. Common Mode Output Voltage Test Circuit

Figure 6. Propagation Delay Input to Output

Figure 7. Output Rise and Fall Time

Figure 8. Output Inter-Pair Skew

**Figure 9. Vpre and Vpost (The test pattern is 1111111100000000 (8-1s, 8-0s))**

**Figure 10. Receive Side Performance Test Circuit**

**Figure 11. Transmit Side Performance Test Circuit**

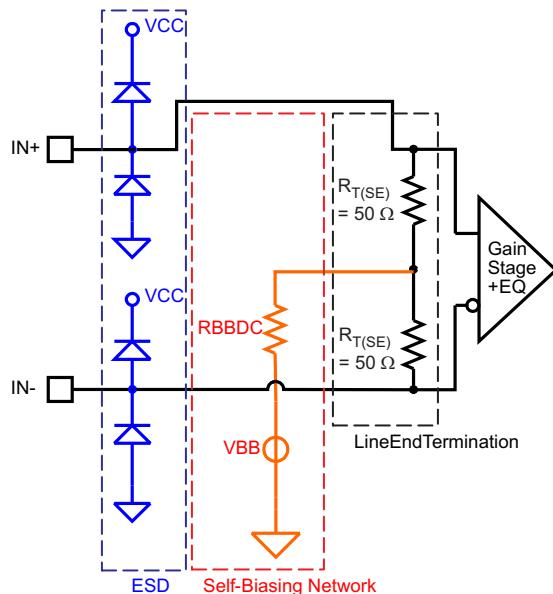

## EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

**Figure 12. Equivalent Input Circuit Design**

**Figure 13. 3-Level Input Biasing Network**

## TYPICAL CHARACTERISTICS

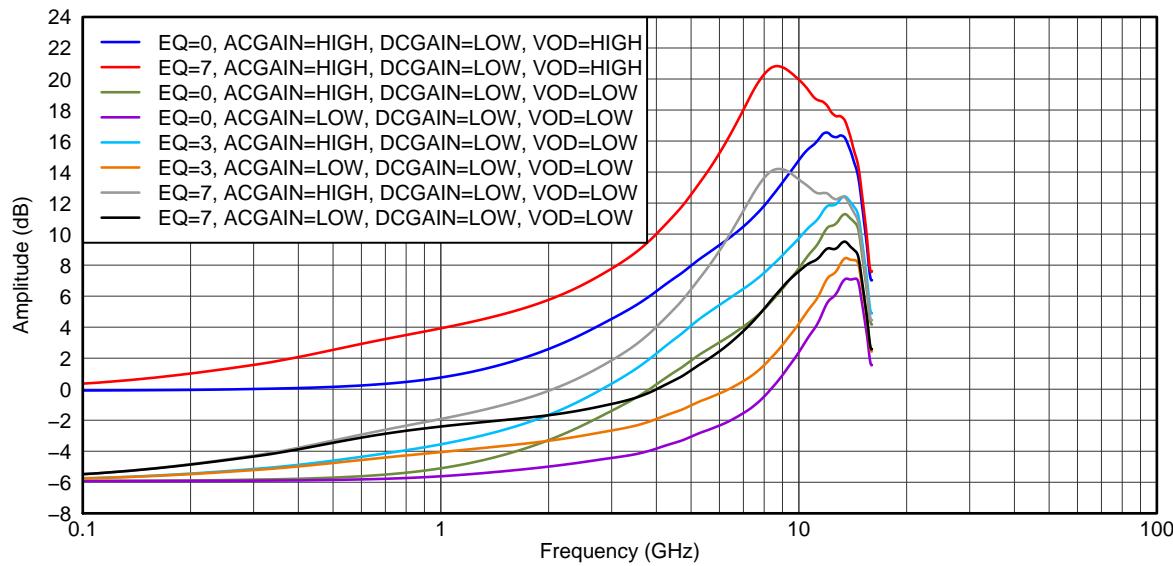

Typical operating condition is at  $V_{CC} = 2.5V$  and  $T_A = 25^\circ C$ , no interconnect line at the output, and with default device settings (unless otherwise noted).

Figure 14. Typical EQ Gain Profile Curve

G001

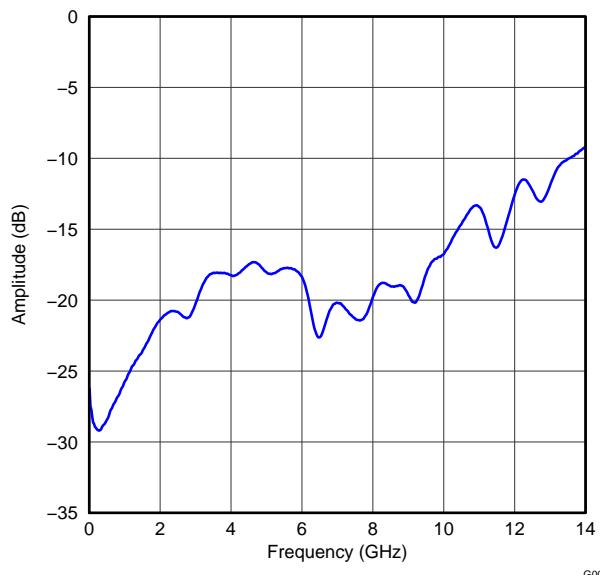

Figure 15. Differential Input Return Loss

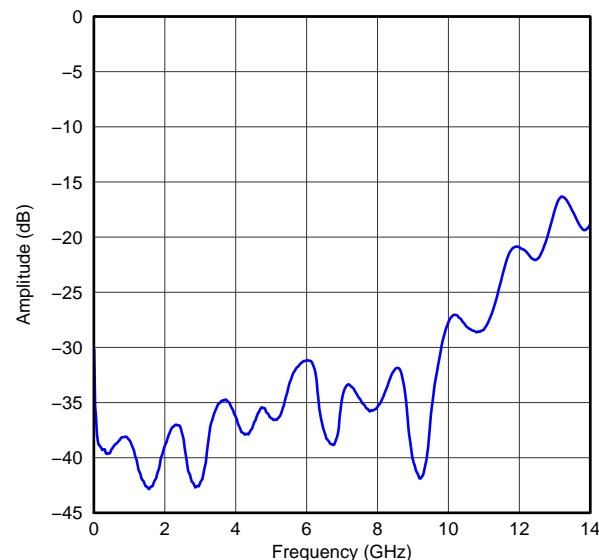

Figure 16. Differential to Common Mode Conversion

G003

### TYPICAL CHARACTERISTICS (continued)

Typical operating condition is at  $V_{CC} = 2.5V$  and  $T_A = 25^\circ C$ , no interconnect line at the output, and with default device settings (unless otherwise noted).

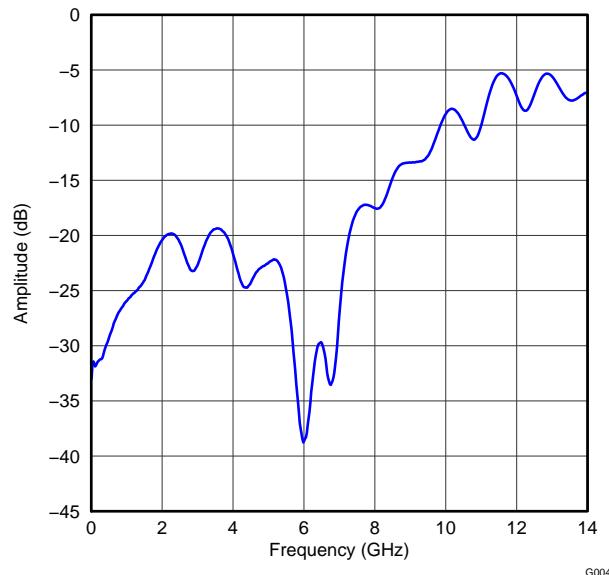

G004

**Figure 17. Differential Output Return Loss**

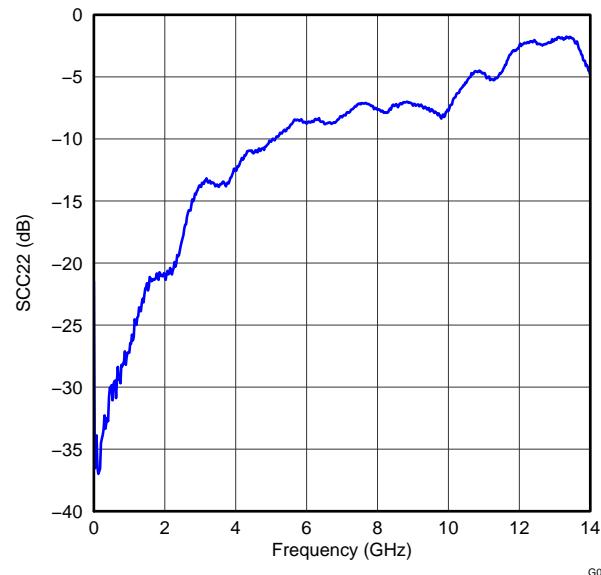

G005

**Figure 18. Common Mode Output Return Loss**

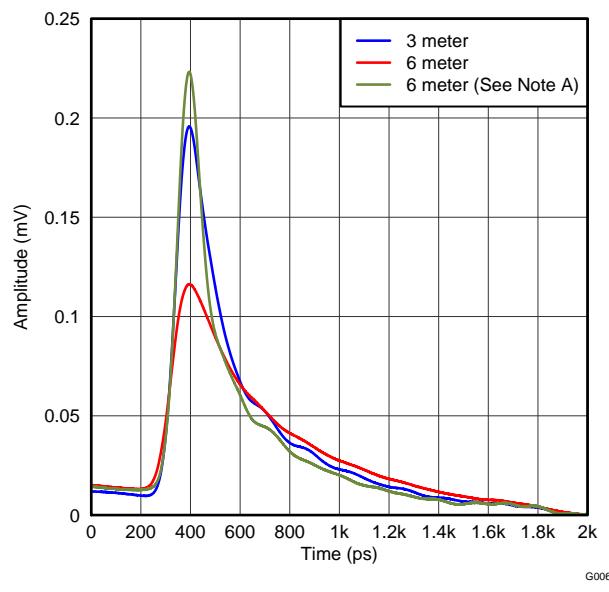

G006

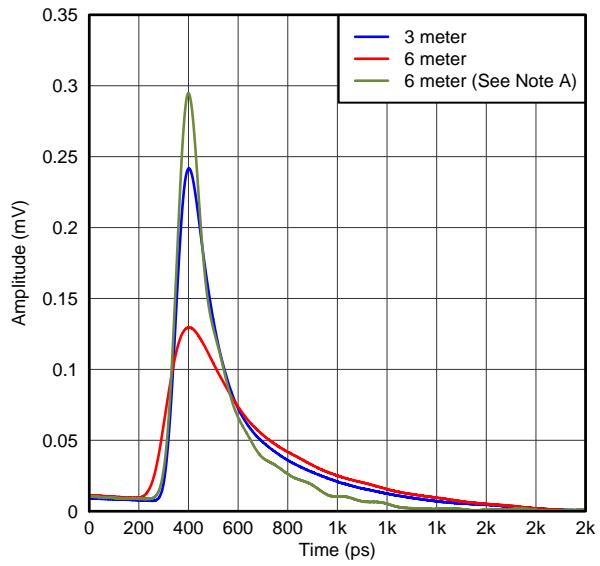

A. With SN65LVCP1412 -> EQ = 4, VOD = High, ACGain = HiZ, DCGain = Low

**Figure 19. Cable Mode – Symbol Response**

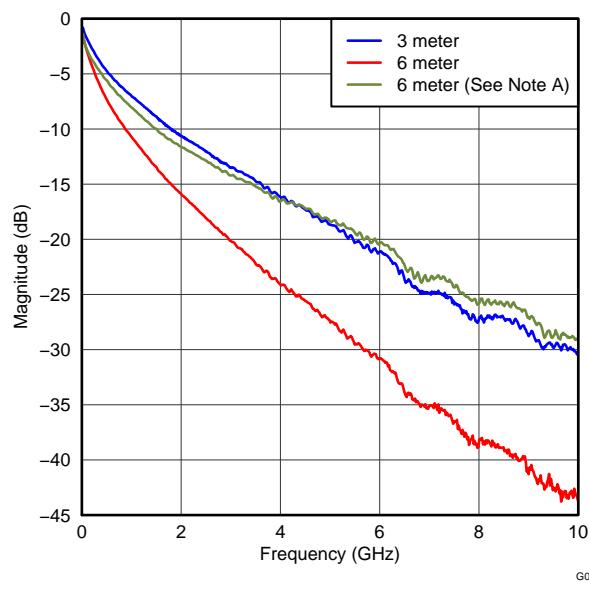

G007

A. With SN65LVCP1412 -> EQ = 4, VOD = High, ACGain = HiZ, DCGain = Low

**Figure 20. Cable Mode – Frequency Domain**

### TYPICAL CHARACTERISTICS (continued)

Typical operating condition is at  $V_{CC} = 2.5V$  and  $T_A = 25^\circ C$ , no interconnect line at the output, and with default device settings (unless otherwise noted).

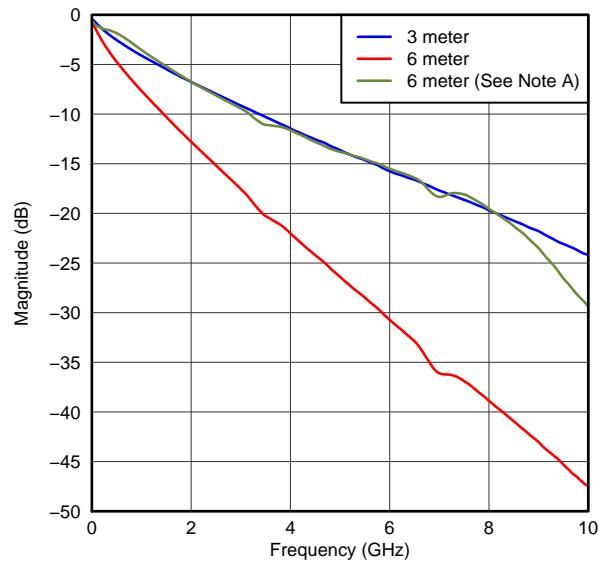

G008

A. With SN65LVCP1412 -> EQ = 7, VOD = High, ACGain = High, DCGain = Low

Figure 21. Trace Mode – Symbol Response

G009

A. With SN65LVCP1412 -> EQ = 7, VOD = High, ACGain = High, DCGain = Low

Figure 22. Trace Mode - Frequency Domain

Table 1. Control Settings Descriptions

| MODE | DCGAIN | ACGAIN<1:0> | EQ<2:0>    | DC GAIN (dB) | EQ GAIN (dB) | APPLICATION                          |

|------|--------|-------------|------------|--------------|--------------|--------------------------------------|

| 0    | 0      | 00          | 000 to 111 | -6           | 1 to 9       | Short Input Trace; Large Input Swing |

| 0    | 0      | 11          | 000 to 111 | -6           | 7 to 17      | Long Input Trace; Large Input Swing  |

| 0    | 1      | 01          | 000 to 111 | 0            | 1 to 9       | Short Input Trace; Small Input Swing |

| 0    | 1      | 11          | 000 to 111 | 0            | 2 to 10      | Short Input Trace; Small Input Swing |

| 1    | 0      | 00          | 000 to 111 | -6           | 1 to 9       | Short Input Cable; Large Input Swing |

| 1    | 0      | 11          | 000 to 111 | -6           | 7 to 17      | Long Input Cable; Large Input Swing  |

| 1    | 1      | 01          | 000 to 111 | 0            | 1 to 9       | Short Input Cable; Small Input Swing |

| 1    | 1      | 11          | 000 to 111 | 0            | 2 to 10      | Short Input Cable; Small Input Swing |

Table 2. Control Settings Descriptions

| GAIN  | DC GAIN | ACGAIN<1:0> |

|-------|---------|-------------|

| Low   | 0       | 00          |

| HighZ | 0       | 11          |

| High  | 1       | 01          |

## TWO-WIRE SERIAL INTERFACE AND CONTROL LOGIC

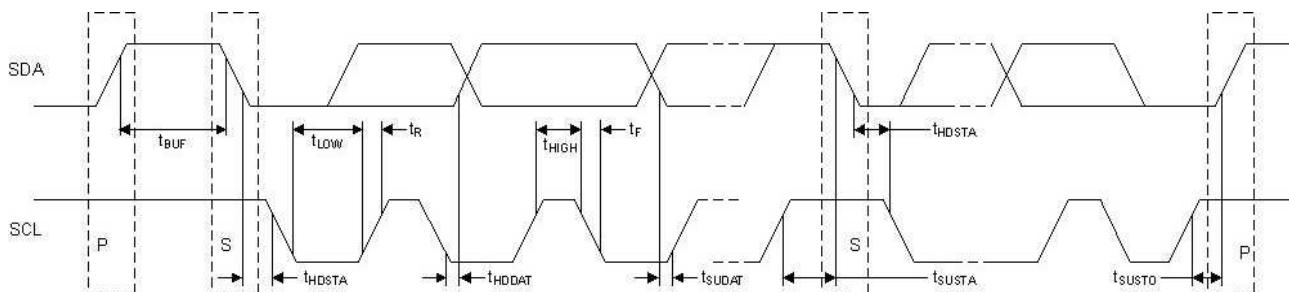

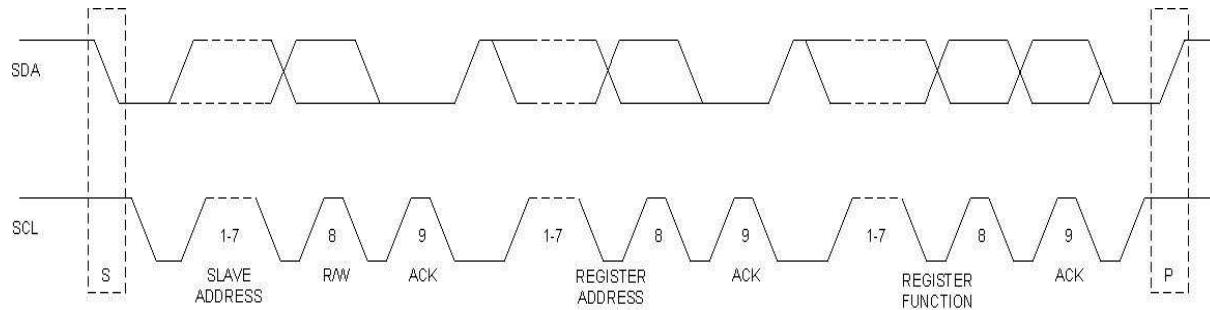

The SN65LVCP1412 uses a 2-wire serial interface for digital control. The two circuit inputs, SDA and SCL, are driven, respectively, by the serial data and serial clock from a microcontroller, for example. The SDA and SCK pins require external  $10\text{k}\Omega$  pull-ups to VCC.

The 2-wire interface allows write access to the internal memory map to modify control registers and read access to read out control and status signals. The SN65LVCP1412 is a slave device only which means that it cannot initiate a transmission itself; it always relies on the availability of the SCK signal for the duration of the transmission. The master device provides the clock signal as well as the START and STOP commands. The protocol for a data transmission is as follows:

1. START command